ADSP-BF531/ADSP-BF532/ADSP-BF533

概要

高达 600 MHz 高性能 Blackfin 处理器

2 个 16 位 MAC,2 个 40 位 ALU,4 个 8 位视频

ALU,以及 1 个 40 位移位器

RISC 式寄存器和指令模型,编程简单,编译环境友好

先进的调试、跟踪和性能监视

内核电压 VDD 0.8V-1.2V

片内调压器支持从 3.3V-2.5V 的输入电压

160 引脚 Mini-BGA 封装;169 引脚 PBGA 封装;176 引脚

LQFP 封装

存储器

高达 148KBytes 片内存储器:

16KBytes 指令 SRAM/Cache

64KBytes 指令 SRAM

32KBytes 数据 SRAM/Cache

32KBytes 数据 SRAM

4KBytes 存放中间结果的 SRAM

两个双通道存储器 DMA 控制器

存储器管理单元提供存储器保护

存储器控制器可与 SDRAM、SRAM、Flash 和 ROM 无缝

连接

灵活的存储器引导模式,可以选择从 SPI 口或外部存储器

导入

外设

并行外设接口(PPI) /GPIO 支持 ITU-R 656 视频数据格式

2 个双通道全双工同步串行接口,支持 8 个立体声 I2S 通道

12 通道 DMA 控制器

SPI 兼容端口

3 个定时/计数器,支持 PWM

支持 IrDA 的 UART

事件处理

实时时钟

“看门狗”定时器

调试 /JTAG 接口

1x-63x 倍频的片内 PLL

内核定时器

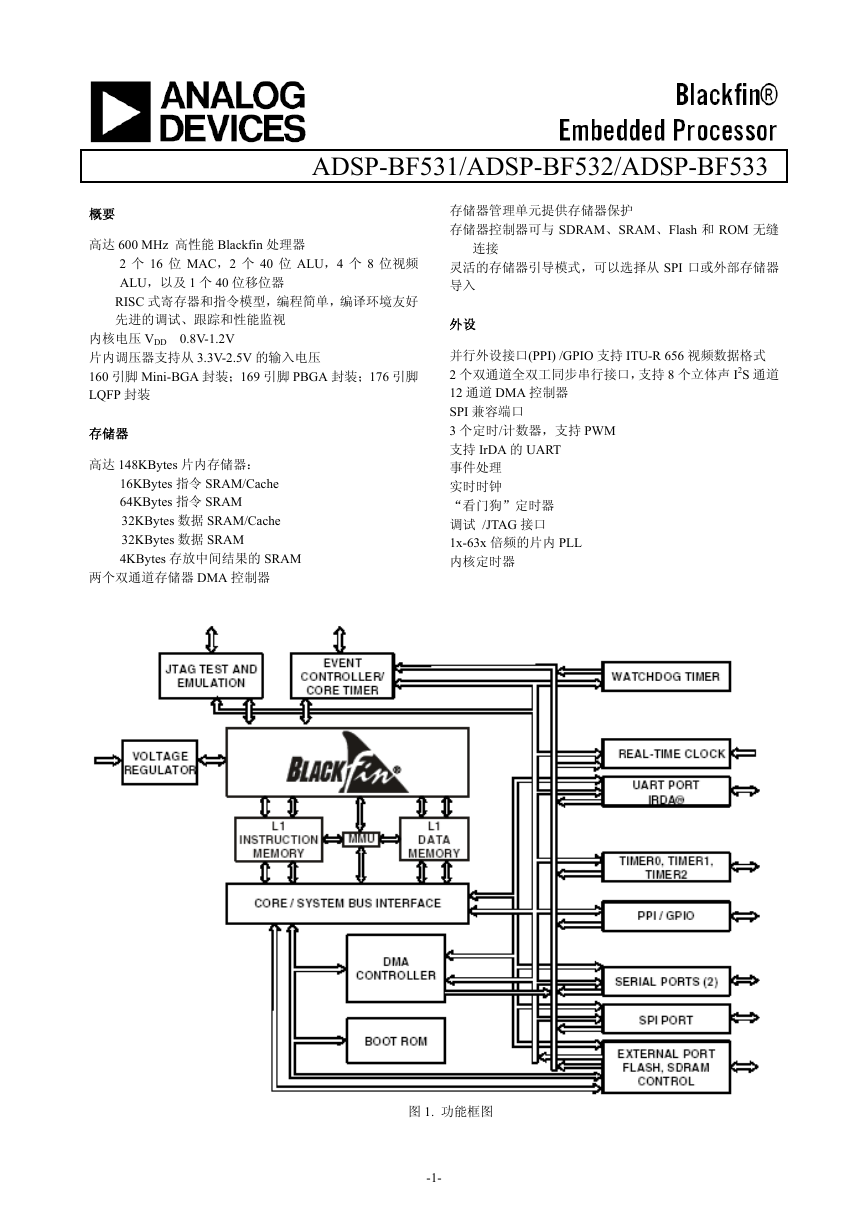

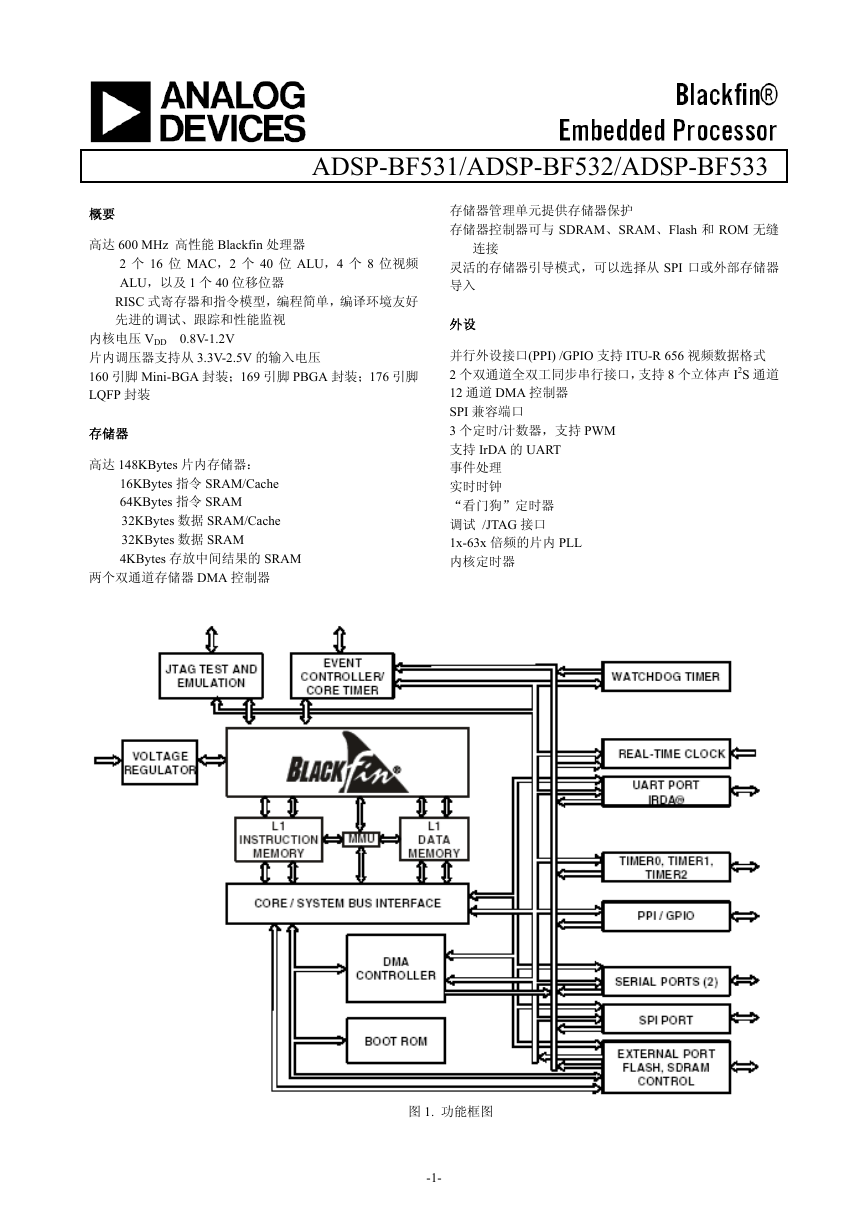

图 1. 功能框图

-1-

�

ADSP-BF531/ADSP-BF532/ADSP-BF533

目录

概 述…………………………………………………………3

便携式低功耗结构....................................................... 3

系统集成....................................................................... 3

ADSP-BF531/2/3 处理器外设...................................... 3

BLACKFIN 处理器内核 ............................................. 3

存储器结构................................................................... 4

DMA 控制器................................................................. 7

实时时钟....................................................................... 8

“看门狗”定时器 ......................................................... 8

定时器........................................................................... 8

串行口(SPORTs)........................................................... 8

串行外设接口(SPI)....................................................... 9

UART 端口 ................................................................... 9

可编程标志(PFx)..................................................... 9

并行外设接口............................................................. 10

动态电源管理............................................................. 10

电压调节..................................................................... 11

时钟信号..................................................................... 11

引导模式..................................................................... 12

指令集描述................................................................. 13

开发工具..................................................................... 13

设计仿真器兼容的 DSP 板........................................ 14

引脚描述……………………………………………………15

技术规格……………………………………………………18

推荐工作条件............................................................. 18

电气特性..................................................................... 18

绝对最大额定值......................................................... 19

ESD 灵敏度 ............................................................... 19

时序规格..................................................................... 20

时钟和复位时序................................................ 21

异步存储器读周期时序.................................... 22

异步存储器写周期时序.................................... 23

SDRAM 接口时序............................................ 24

外部端口总线请求和许可周期时序 ................ 25

并行外设接口时序............................................ 26

串行口................................................................ 27

串行外设接口(SPI)—主时序 ...................... 30

串行外设接口(SPI)—从时序 ...................... 31

通用异步收发器(UART)端口—接收和发送

时序 ................................................................... 32

可编程标志周期时序........................................ 32

定时器周期时序 ................................................33

JTAG 测试和仿真端口时序 ..............................34

输出驱动电流 .............................................................35

功耗 .............................................................................36

测试条件 .....................................................................37

环境条件 .....................................................................40

160-LEAD BGA 引脚…………………………………..…42

169-Ball PBGA 引脚 …………………………………..…45

176-LEAD LQFP 引脚…………………………………..…47

外形尺寸 ………………………………..…..…..…..…..…49

订购指导……………………………………………………50

版本历史

11/04-版本 A: 从版本 0 变到版本 A

删除了片上调压器说明中的电压允许偏差,更换了

(图 7)电压调节电路的元件……………………………11

在推荐工作条件中定义了 ADSP-BF533 新的标称电

压…………………………………………………………18

给出了表 10,表 11 和表 12 的测试电压…………………20

改变了(表 30)内部功耗在 400MHz 时的数据………36

改变了(图 46)160-BALL Mini-BGA(BC-160)

的封装高度………………………………………………49

改变了 ADSP-BF532 和 ADSP-BF533 的工作电压,

订购指导中新增了两个型号……………………………50

11/04-版本 0: 最初版本

-2-

�

概述

ADSP-BF531/ADSP-BF532/ADSP-BF533

ADSP-BF531/2/3 处理器是 Blackfin 系列产品的成员,

融合了 Analog Devices/Intel 的微信号结构(Micro Signal

Architecture) (MSA)。Blackfin 处理器这种体系结构将艺

术级的 dual-MAC 信号处理引擎,简洁的 RISC 式微处理

器指令集的优点,以及单指令多数据(SIMD)多媒体能力结

合起来,形成了一套独特的指令集结构。

ADSP-BF531/2/3 处理器的代码和管脚完全兼容,它们

之间的差别仅仅在于具有不同的性能和片内存储器容量。

详细的性能和存储器区别见表 1:

表 1 处理器比较

ADSP-BF531 ADSP-BF532 ADSP-BF533

最大频率

400MHz

400 MHz

600 MHz

性能

800 MMACs

800 MMACs

1200

MMACs

指

令

SRAM/Cache

16Kbytes

16Kbytes

16Kbytes

指令 SRAM

16Kbytes

32Kbytes

64Kbytes

数

据

SRAM/Cache

16Kbytes

32Kbytes

32Kbytes

数据 SRAM

中间存储器

4Kbytes

4Kbytes

32bytes

4Kbytes

通 过 集 成 业 界领 先 和 丰 富 的系 统 外 设 及 存 储 器 ,

Blackfin 处理器系列成为下一代需要将 RISC 式编程、多

媒体支持和前沿的信号处理等功能集成在单个封装内的选

择平台。

便携式低功耗结构

Blackfin 处理器系列具有世界领先的功率管理和性

能。Blackfin 处理器采用低功耗和低电压的设计方法,具

有动态功率管理的特点,即通过改变工作电压和频率来大

大降低总功耗。与仅改变工作频率相比,既改变电压又改

变频率能够使总功耗明显减少。对于便携式应用来说,这

相当于延长了电池的寿命。

系统集成

对 下 一 代 的 数 字 通 信 和 消 费 多 媒 体 应 用 来 说 ,

ADSP-BF531/2/3 处理器是高度集成的片上系统解决方案。

通过将工业标准接口与高性能的信号处理内核相结合,用

户可以快速开发出节省成本的解决方案,而无需昂贵的外

部组件。ADSP-BF531/2/3 处理器系统外设包括一个 UART

口、一个 SPI 口、两个串行口(SPORTs)、四个通用定时器

(其中三个具有 PWM 功能)、一个实时时钟、一个看门狗

定时器,以及一个并行外设接口。

-3-

ADSP-BF531/2/3 处理器外设

ADSP-BF531/2/3 处理器包含丰富的外设,它们通过不

同的高速宽带总线与内核相连,使系统不但配置灵活而且

有极好的性能(见第 1 页的图 1)。通用外设包括一些功能,

如 UART、带有 PWM(脉冲宽度调制)和脉冲测量能力的

定时器、通用的 I/O 标志引脚、一个实时时钟和一个看门

狗定时器。这些外设满足了典型系统的各种需求,并且通

过它们增强了系统的扩充能力。除了这些通用的外设,

ADSP-BF531/2/3 处理器还包含有用于各种音频、视频和调

制解调编解码功能的高速串行和并行端口;一个用于灵活

地管理来自片内外设和外部信源的中断事件处理器;以及

可根据不同的应用来配置系统的性能和功耗的功率管理控

制功能。

除通用 I/O,实时时钟和定时器外,所有其它的外设都

有一个灵活的 DMA 结构。片内还有一个独立的存储器

DMA 通道,专用于在处理器的不同存储空间,包括外部的

SDRAM 和异步存储器,进行数据传输。多条片内总线能

以 133MHz 的速度运行,提供了足够的带宽以保证处理器

内核能够跟得上片内和片外外设。

ADSP-BF531/2/3 处理器包含支持 ADSP-BF531/2/3 处

理器动态功率管理功能的片上调压器,从 2.25V 到 3.6V

的单输入电压提供内核电压。该调压器也可以由用户旁路。

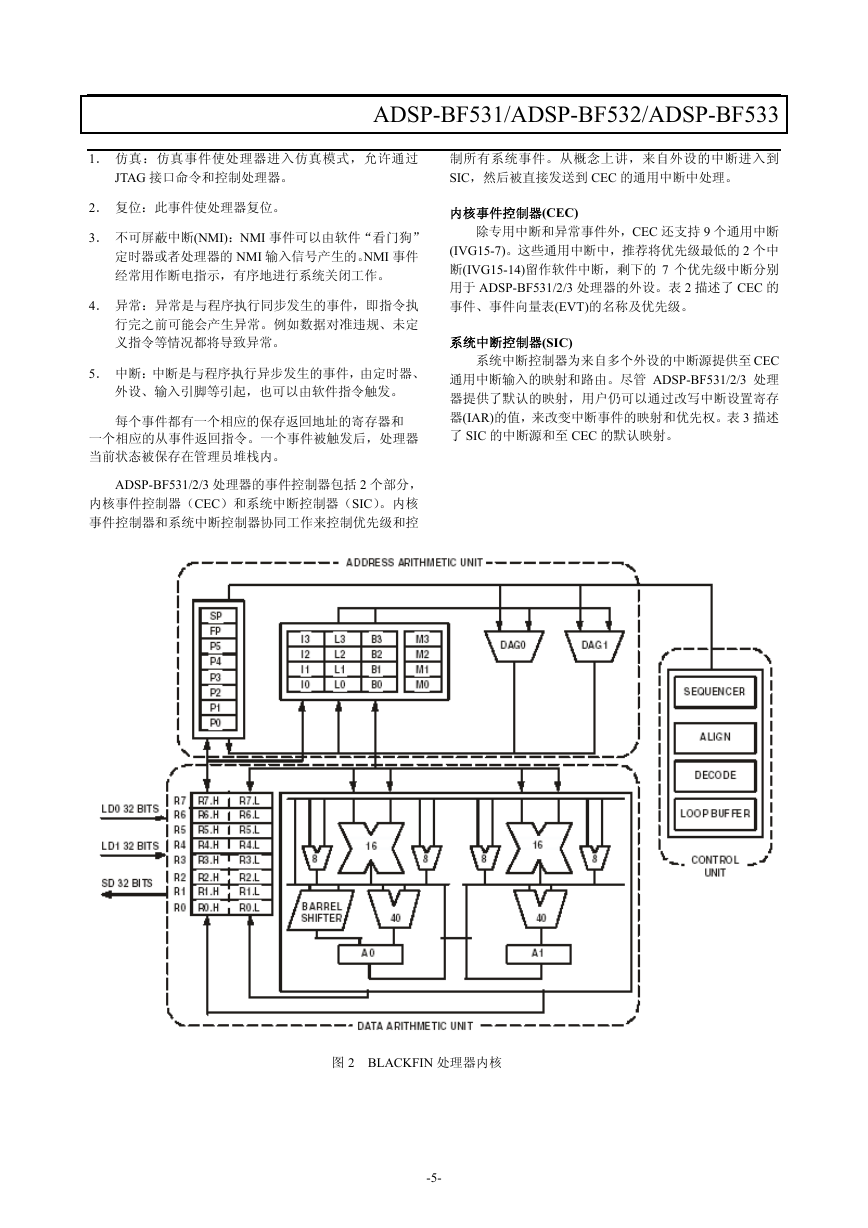

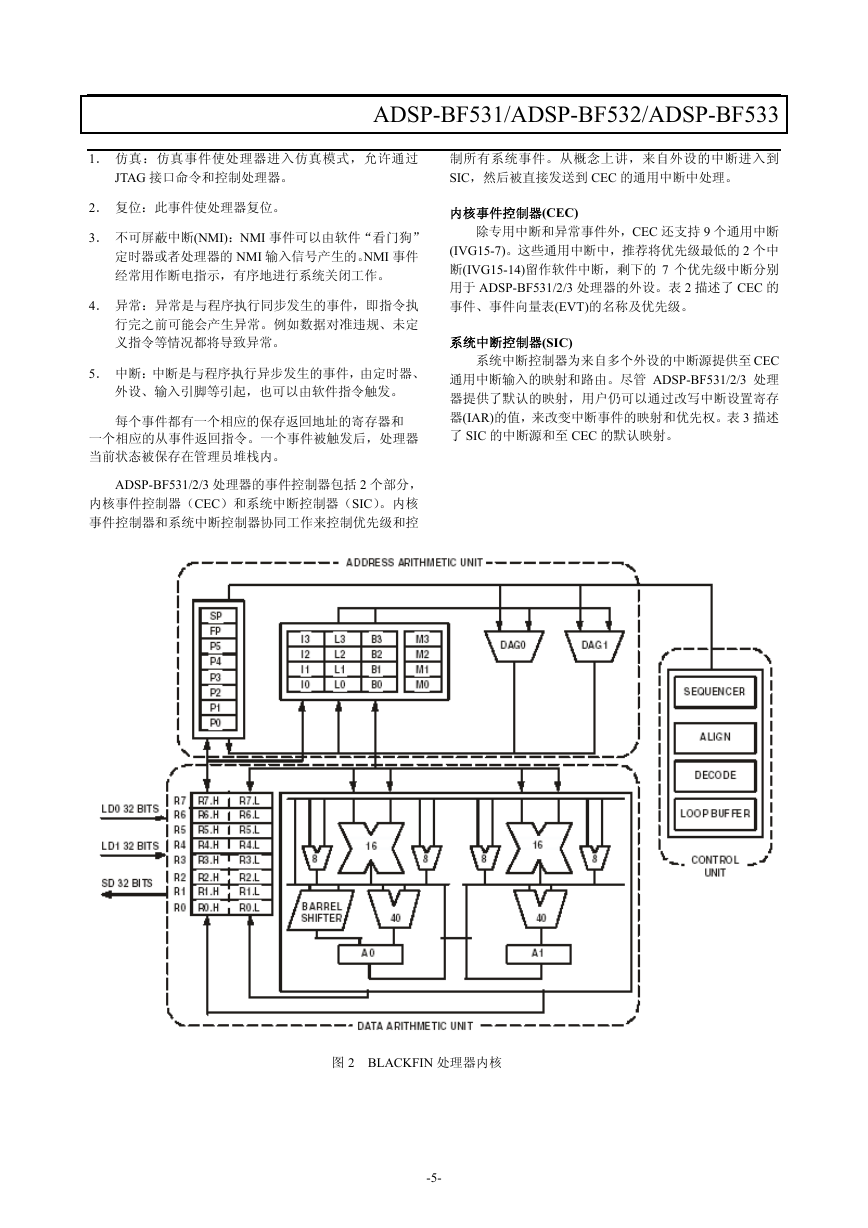

BLACKFIN 处理器内核

如第 5 页的图 2 所示,BLACKFIN 处理器内核包含 2

个 16 位乘法器,2 个 40 位的累加器,2 个 40 位的 ALU,

4 个视频 ALU 和 1 个 40 位移位器。运算单元处理来自寄

存器组的 8 位、16 位或者 32 位数据。

运算寄存器组包括 8 个 32 位寄存器。当执行 16 位操

作数的运算时,寄存器组可作为 16 个独立的 16 位寄存器。

运算的所有操作数都来自多端口寄存器组和指令常量域。

每个 MAC 每周期可完成一个 16 位乘 16 位的乘法运

算,并把结果累加到 40 位的累加器中。支持符号型和无符

号型数据格式,舍入与饱和等操作。

ALU 除执行一套传统的 16 位或 32 位数据的算术和逻

辑运算外,还包含许多特殊指令用于加速不同的信号处理

任务。这些指令包括位操作(例如域提取和计算总数)、模

232 乘法、除法、饱和与舍入、符号/指数检测等;专用的

一套视频指令包括字节对准和压缩操作,16 位和 8 位截断

加,8 位平均操作,8 位减法/绝对值/累加(SAA)操作等;

还提供有比较/选择和矢量搜索指令。

对于某些指令,两个 16 位 ALU 操作可以同时在寄存

器对(运算寄存器的高 16 位和低 16 位)中执行,也可以

使用第二个 ALU,进行四个 16 位运算。

40 位的移位器可以执行移位和循环移位,可以用于标

准化、提取和存储等操作。

程序控制器控制指令执行的顺序,包括指令对准和译

码。对于程序流程,程序控制器支持相对于 PC 的间接条

�

ADSP-BF531/ADSP-BF532/ADSP-BF533

件跳转(支持静态分支预测)和子程序调用。硬件提供对

零耗循环的支持。这种结构是完全互锁的,这就意味着,

当有数据相关的指令时,编程者不用自己管理的流水线。

内部(片内)存储器

ADSP-BF531/2/3 处理器有 3 块片内存储器,提供到内

核的高带宽的访问。

地址算术单元能够提供两套地址,用于从存储器中同

时进行双存取。一个多端口寄存器组由 4 套 32 位的索引、

修改、长度、基地址(用于循环缓冲)寄存器和 8 个另外

的 32 位指针寄存器(用于 C 风格的索引堆栈操作)组成。

Blackfin 处理器采用改进的哈佛结构和分级的存储器

结构。Level 1(L1)存储器一般以全速运行,没有或只有

很少的延迟。在 L1 级,指令存储器只存放指令。2 个数据

存储器存放数据,一个专用的临时数据存储器存放堆栈和

局部变量信息。

此外,由多个 L1 存储器组成的模块,可进行 SRAM

和 CACHE 的混合配置。存储器管理单元(MMU)提供存储

器保护功能,对运行于内核上的独立的任务,可保护系统

寄存器免于意外的存取。

这种体系结构提供了 3 种运行模式:用户模式、管理

员模式和仿真模式。用户模式限制对某些系统资源的访问,

因此提供了一个受保护的软件环境;而管理员模式对系统

和内核资源的访问不受限制。

Blackfin 处理器指令系统经过优化,16 位操作码组成

了最常用的指令,这使得编译后的代码密度非常高。复杂

DSP 指令采用 32 位操作码,体现了多功能指令的全部特

征。Blackfin 处理器支持有限的并行能力,即 1 个 32 位的

指令可以和 2 个 16 位指令并行执行,使编程人员在单指令

周期中使用尽可能多的内核资源。

Blackfin 处理器汇编语言使用易于编程和可读性强的

代数语法,而且在和 C/C++编译器的链接上进行了优化,

给程序员提供了快速有效的软件环境。

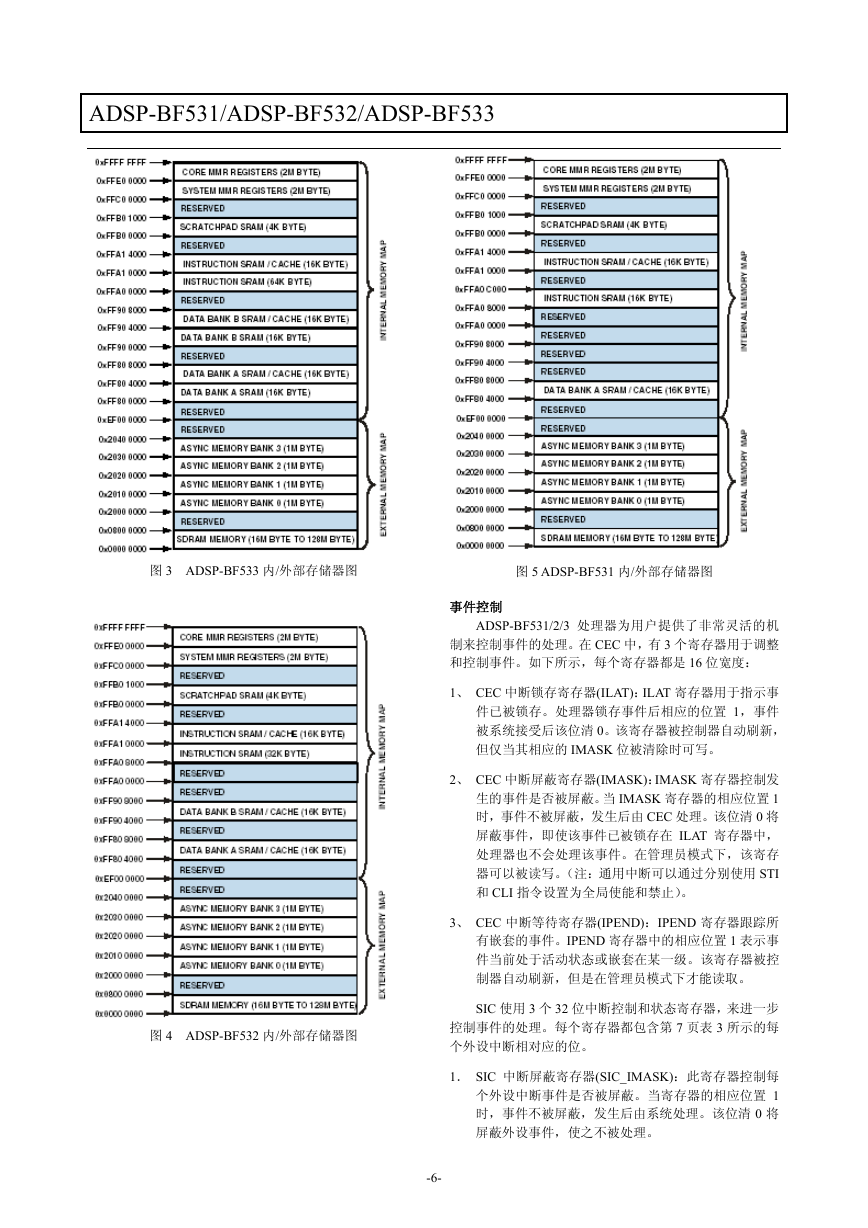

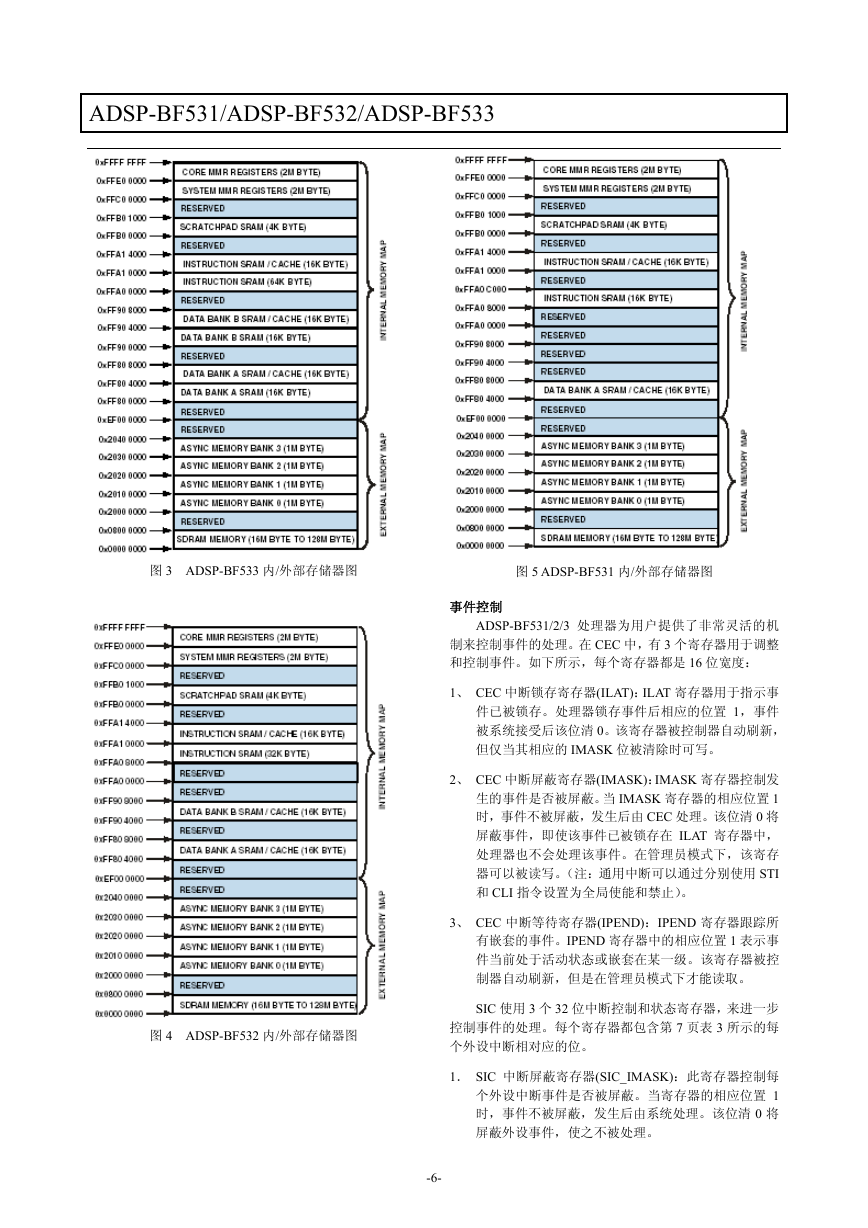

存储器结构

ADSP-BF531/2/3 处 理器 把存储 器 视为 一个统 一 的

4GBytes 的地址空间,使用 32 位地址。所有的资源,包括

内部存储器、外部存储器和 I/O 控制寄存器,都占据公共

地址空间的各自独立的部分。此地址空间的各部分存储器

按分级结构排列,以提供高的性能价格比。一些非常快速、

低延迟的存储器(如 CACHE 或 SRAM)的位置非常接近

处理器,而更大的低成本、低性能的存储器远离处理器。

参见第 6 页图 3、图 4、图 5。

L1 存储器是 Blackfin 处理器内核中性能最高的最重要

的存储器。通过外部总线接口单元(EBIU),片外存储器可

以由 SDRAM、FLASH 和 SRAM 进行扩展,可以访问多达

132MBytes 的物理存储器。

存储器 DMA 控制器提供高带宽的数据传输能力。它

能够在内部存储器和外部存储器空间之间完成代码或数据

的块传输。

第 1 块是 L1 指令存储器, 由高达 80KBytes 的 SRAM

组成,其中 16KBytes 可以配置为一个 4 路组联合的

CACHE。L1 指令存储器以处理器的最快速度访问。

第 2 块片内存储器是 L1 数据存储器,包括分别为

32KBytes 的两个 Bank。每个 Bank 都可配置成 CACHE 或

SRAM。此存储器也以全速度访问。

第 3 块是一个 4KBytes 的临时数据 SRAM,它和 L1

存储器有相同的运行速度,但是只能作为数据 SRAM,不

能配置为 CACHE。

外部(片外)存储器

外部总线接口单元(EBIU)即可以用于异步设备(例如:

FLASH、EPROM、ROM、SRAM 和存储器映射 I/O 设备)

也可以用于同步设备(例如:SDRAM)。它们的总线宽度

均为 16 位,其中 A1 为 16 位字的最低位。8 位的外围设备

必须象 16 位设备一样分配 16 位地址,但只使用其低 8 位

数据。

PC133 兼容的 SDRAM 控制器可以通过编程与高达

128MBytes 的 SDRAM 接口。内部最高可以配有 4 个

SDRAM banks,SDRAM 控制器允许为内部 SDRAM 的每个

banks 同时打开一个通道,从而提高系统性能。

异步存储器的控制器也能够通过编程控制多达 4 个

bank 的时序参数灵活的各种异步存储设备。无论使用设备

的大小如何,每个 bank 的空间都占据 1MByte。这样,只

有装满 4 个 1MByte 的存储器时地址空间才能连续。

I/O 存储器空间

Blackfin 处理器没有定义独立的 I/O 空间。所有的资

源都被映射到统一的 32 位地址空间。片上 I/O 设备的控制

寄存器被映射到靠近 4GByte 地址空间顶端的存储器映射

寄存器(MMR)地址范围内。这个地址空间又被划分为两个

部分,一部分包含完成所有内核功能的控制 MMR,另一

部分包含用于设置和控制内核以外的片内外设的寄存器。

MMR 仅在管理员模式下可被访问,并且被看作是片内外

设的保留空间。

引导

ADSP-BF531/2/3 处理器包括一个小的引导内核,用于

配置的适当的外设来引导。如果 ADSP-BF531/2/3 处理器

被配置为从引导 ROM 存储器引导,那么 DSP 从片内引导

ROM 开始执行。若需要更多信息,请看第 12 页的引导模

式。

事件处理

ADSP-BF531/2/3 处理器的事件控制器处理到达处理

器的所有的同步和异步事件。事件处理支持嵌套和优先级。

嵌套允许同时激活多个事件的服务程序。优先级保证高优

先级事件的响应可以抢占较低优先级事件的响应。控制器

支持 5 种不同类型的事件:

-4-

�

ADSP-BF531/ADSP-BF532/ADSP-BF533

1. 仿真:仿真事件使处理器进入仿真模式,允许通过

JTAG 接口命令和控制处理器。

2. 复位:此事件使处理器复位。

3. 不可屏蔽中断(NMI):NMI 事件可以由软件“看门狗”

定时器或者处理器的 NMI 输入信号产生的。NMI 事件

经常用作断电指示,有序地进行系统关闭工作。

4. 异常:异常是与程序执行同步发生的事件,即指令执

行完之前可能会产生异常。例如数据对准违规、未定

义指令等情况都将导致异常。

5. 中断:中断是与程序执行异步发生的事件,由定时器、

外设、输入引脚等引起,也可以由软件指令触发。

每个事件都有一个相应的保存返回地址的寄存器和

一个相应的从事件返回指令。一个事件被触发后,处理器

当前状态被保存在管理员堆栈内。

ADSP-BF531/2/3 处理器的事件控制器包括 2 个部分,

内核事件控制器(CEC)和系统中断控制器(SIC)。内核

事件控制器和系统中断控制器协同工作来控制优先级和控

制所有系统事件。从概念上讲,来自外设的中断进入到

SIC,然后被直接发送到 CEC 的通用中断中处理。

内核事件控制器(CEC)

除专用中断和异常事件外,CEC 还支持 9 个通用中断

(IVG15-7)。这些通用中断中,推荐将优先级最低的 2 个中

断(IVG15-14)留作软件中断,剩下的 7 个优先级中断分别

用于 ADSP-BF531/2/3 处理器的外设。表 2 描述了 CEC 的

事件、事件向量表(EVT)的名称及优先级。

系统中断控制器(SIC)

系统中断控制器为来自多个外设的中断源提供至 CEC

通用中断输入的映射和路由。尽管 ADSP-BF531/2/3 处理

器提供了默认的映射,用户仍可以通过改写中断设置寄存

器(IAR)的值,来改变中断事件的映射和优先权。表 3 描述

了 SIC 的中断源和至 CEC 的默认映射。

图 2 BLACKFIN 处理器内核

-5-

�

ADSP-BF531/ADSP-BF532/ADSP-BF533

图 3 ADSP-BF533 内/外部存储器图

图 4 ADSP-BF532 内/外部存储器图

图 5 ADSP-BF531 内/外部存储器图

事件控制

ADSP-BF531/2/3 处理器为用户提供了非常灵活的机

制来控制事件的处理。在 CEC 中,有 3 个寄存器用于调整

和控制事件。如下所示,每个寄存器都是 16 位宽度:

1、 CEC 中断锁存寄存器(ILAT):ILAT 寄存器用于指示事

件已被锁存。处理器锁存事件后相应的位置 1,事件

被系统接受后该位清 0。该寄存器被控制器自动刷新,

但仅当其相应的 IMASK 位被清除时可写。

2、 CEC 中断屏蔽寄存器(IMASK):IMASK 寄存器控制发

生的事件是否被屏蔽。当 IMASK 寄存器的相应位置 1

时,事件不被屏蔽,发生后由 CEC 处理。该位清 0 将

屏蔽事件,即使该事件已被锁存在 ILAT 寄存器中,

处理器也不会处理该事件。在管理员模式下,该寄存

器可以被读写。(注:通用中断可以通过分别使用 STI

和 CLI 指令设置为全局使能和禁止)。

3、 CEC 中断等待寄存器(IPEND):IPEND 寄存器跟踪所

有嵌套的事件。IPEND 寄存器中的相应位置 1 表示事

件当前处于活动状态或嵌套在某一级。该寄存器被控

制器自动刷新,但是在管理员模式下才能读取。

SIC 使用 3 个 32 位中断控制和状态寄存器,来进一步

控制事件的处理。每个寄存器都包含第 7 页表 3 所示的每

个外设中断相对应的位。

1. SIC 中断屏蔽寄存器(SIC_IMASK):此寄存器控制每

个外设中断事件是否被屏蔽。当寄存器的相应位置 1

时,事件不被屏蔽,发生后由系统处理。该位清 0 将

屏蔽外设事件,使之不被处理。

-6-

�

ADSP-BF531/ADSP-BF532/ADSP-BF533

EVT 入口

仿真/测试控制 EMU

RST

复位

不可屏蔽中断 NMI

EVX

异常

-

保留

IVHW

硬件错误

IVTMR

内核定时器

IVG7

通用中断 7

IVG8

通用中断 8

IVG9

通用中断 9

IVG10

通用中断 10

IVG11

通用中断 11

IVG12

通用中断 12

IVG13

通用中断 13

IVG14

通用中断 14

IVG15

通用中断 15

事件类

表 2. 内核事件控制器(CEC)

优先级

(0 为最高)

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

表 3. 系统中断控制器(SIC)

外设中断事件

PLL 唤醒

DMA 错误

PPI 错误

SPORT 0 错误

SPORT 1 错误

SPI 错误

UART 错误

实时时钟

DMA 通道 0(PPI)

DMA 通道 1(SPORT 0 RX)

DMA 通道 2(SPORT 0 TX)

DMA 通道 3(SPORT 1 RX)

DMA 通道 4(SPORT 1 TX)

DMA 通道 5(SPI)

DMA 通道 6(UART RX)

DMA 通道 7(UART TX)

定时器 0

定时器 1

定时器 2

PF 中断 A

PF 中断 B

DMA 通道 8 和 9

(存储器 DMA 流 1)

DMA 通道 10 和 11

(存储器 DMA 流 0)

软件看门狗定时器

默认映射

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG8

IVG8

IVG9

IVG9

IVG9

IVG9

IVG10

IVG10

IVG10

IVG11

IVG11

IVG11

IVG12

IVG12

IVG13

IVG13

IVG13

2. SIC 中断状态寄存器(SIC_ISR):由于多个外设可以映

射到同一事件,该寄存器允许软件设置哪个外设事件

源触发该中断。相应位置 1 表明外设发出了中断,为

-7-

0 则表明外设未发出事件。

3. SIC 中断唤醒使能寄存器(SIC_IWR):通过使能该寄存

器中的相应位,当事件发生而处理器处于睡眠(掉电)

模式时,可以设置一个外设唤醒处理器。(更多信息,

见第 10 页动态功率管理。)

由于多个中断源可以映射到同一个通用中断,因此该

中断输入引脚上可能同时出现多个脉冲,这可以发生在对

一个已检测到的中断处理之前或之中。IPEND 寄存器的内

容由 SIC 监控,以检查中断是否得到确认。

当一个中断上升沿被检测到(检测需要 2 个内核时钟

周期),ILAT 寄存器的相应位被置 1。当 IPEND 寄存器的

任一位被置 1 时,该位被清 0。IPEND 的这位表示该事件

已进入处理器流水线。此时,CEC 将在下一个事件到来时

识别其上升沿,并将这一事件排入队列。从通用中断的上

升沿到 IPEND 寄存器的输出置 1,最小的延迟为 3 个内核

时钟周期;然而,由于内部的活动和处理器的状态不同,

延迟可能更长。

DMA 控制器

ADSP-BF531/2/3 处理器有多个独立的 DMA 控制器,

能够以最小的处理器内核开销完成自动的数据传输。DMA

传输可以发生在 ADSP-BF531/2/3 处理器的内部存储器和

任一有 DMA 能力的外设之间。此外,DMA 传输也可以在

任一有 DMA 能力的外设和已连接到外部存储器接口的外

部设备之间完成(包括 SDRAM 控制器、异步存储器控制

器)。有 DMA 传输能力的外设包括 SPORTs、SPI 端口、

UART 和 PPI 端口。每个独立的有 DMA 能力的外设至少

有一个专用 DMA 通道。

ADSP-BF531/2/3 处理器的 DMA 控制器能够支持一

维(1D)或二维(2D)DMA 传输。DMA 传输的初始化可

以由寄存器或名为描述子块的参数来实现。

二维 DMA 支持任意的行列数量,最大可达 64K 乘 64K

单位,支持任意数量的行列的步进,最大可达±32K 单位。

而且,列步进的值可以小于行步进的值,这就允许实现隔

行扫描的数据流。这个特性对于视频应用非常有用,可以

实时进行数据的反隔行存储。

ADSP-BF531/2/3 处理器的 DMA 控制器支持的典型

的 DMA 操作包括:

1. 单一的、传输完成时停止的线性缓冲区

2. 自动刷新的循环缓冲区,当每一个或部分缓冲区满时

中断

3. 一维或二维 DMA,使用描述子链表

4. 二维 DMA,使用一个描述子阵列,仅指定公共页内

的基 DMA 地址

除专用外设的 DMA 通道以外,在 ADSP-BF531/2/3

处理器的不同存储器之间有两个存储器 DMA 通道。这使

�

ADSP-BF531/ADSP-BF532/ADSP-BF533

得任意的存储器(包括外部 SDRAM、ROM、SRAM 和

FLASH)之间的数据块传输成为可能,并使处理器干预降

到最小。存储器 DMA 传输可以通过一套非常灵活的基于

描述子的方法或标准的基于寄存器的自动缓冲机制来控

制。

实时时钟

于执行软件的“看门狗”功能。软件“看门狗”可以提高

系统的可靠性,如果在软件复位前定时器溢出,软件“看

门狗”通过产生一个硬件复位、不可屏蔽中断(NMI)或通用

中断来强迫处理器进入一个已知状态。程序员初始化定时

器计数值,使能相应的中断,然后启动定时器。随后,软

件必须在计数器从给定值计数到 0 前重新装载计数器。这

样防止系统停留在未知状态。在未知状态下,软件由于外

部噪声或者软件错误等停止运行后,通常将定时器复位。

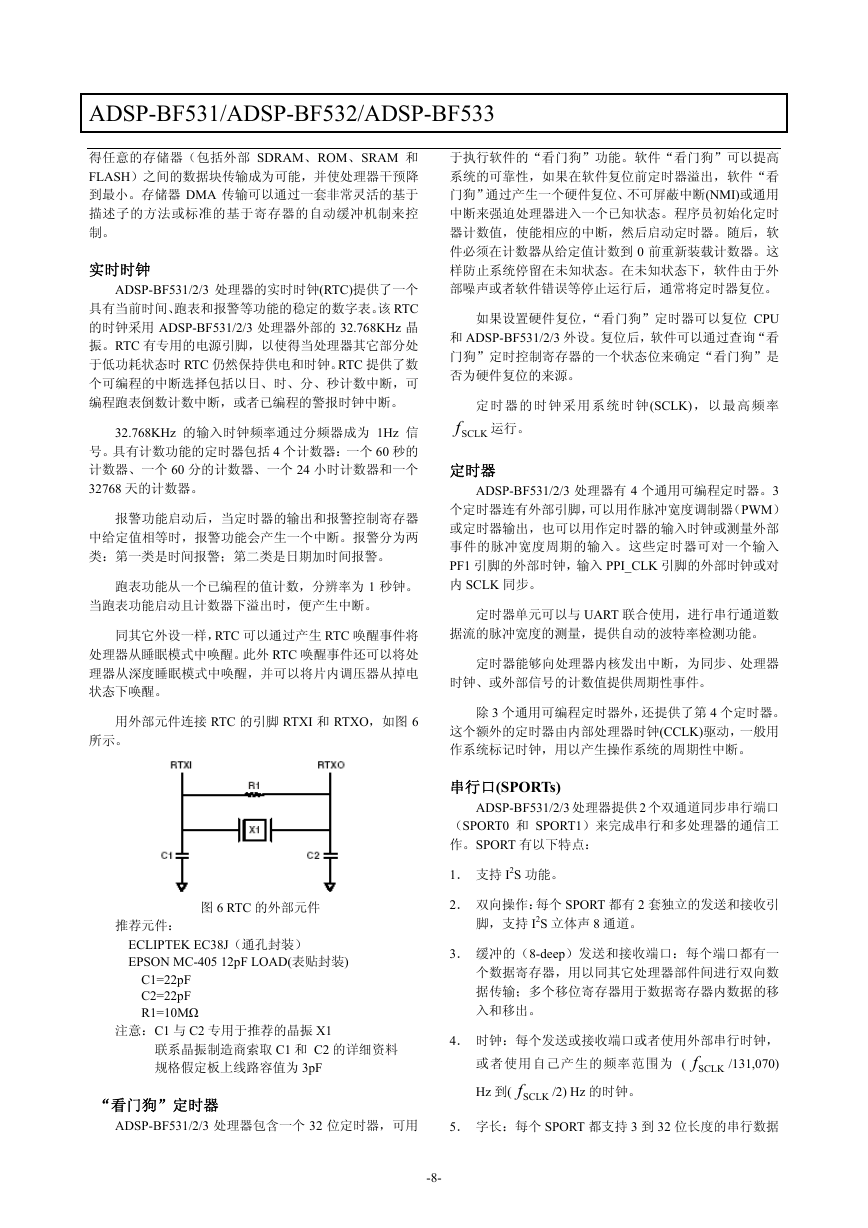

ADSP-BF531/2/3 处理器的实时时钟(RTC)提供了一个

具有当前时间、跑表和报警等功能的稳定的数字表。该 RTC

的时钟采用 ADSP-BF531/2/3 处理器外部的 32.768KHz 晶

振。RTC 有专用的电源引脚,以使得当处理器其它部分处

于低功耗状态时 RTC 仍然保持供电和时钟。RTC 提供了数

个可编程的中断选择包括以日、时、分、秒计数中断,可

编程跑表倒数计数中断,或者已编程的警报时钟中断。

32.768KHz 的输入时钟频率通过分频器成为 1Hz 信

号。具有计数功能的定时器包括 4 个计数器:一个 60 秒的

计数器、一个 60 分的计数器、一个 24 小时计数器和一个

32768 天的计数器。

报警功能启动后,当定时器的输出和报警控制寄存器

中给定值相等时,报警功能会产生一个中断。报警分为两

类:第一类是时间报警;第二类是日期加时间报警。

跑表功能从一个已编程的值计数,分辨率为 1 秒钟。

当跑表功能启动且计数器下溢出时,便产生中断。

同其它外设一样,RTC 可以通过产生 RTC 唤醒事件将

处理器从睡眠模式中唤醒。此外 RTC 唤醒事件还可以将处

理器从深度睡眠模式中唤醒,并可以将片内调压器从掉电

状态下唤醒。

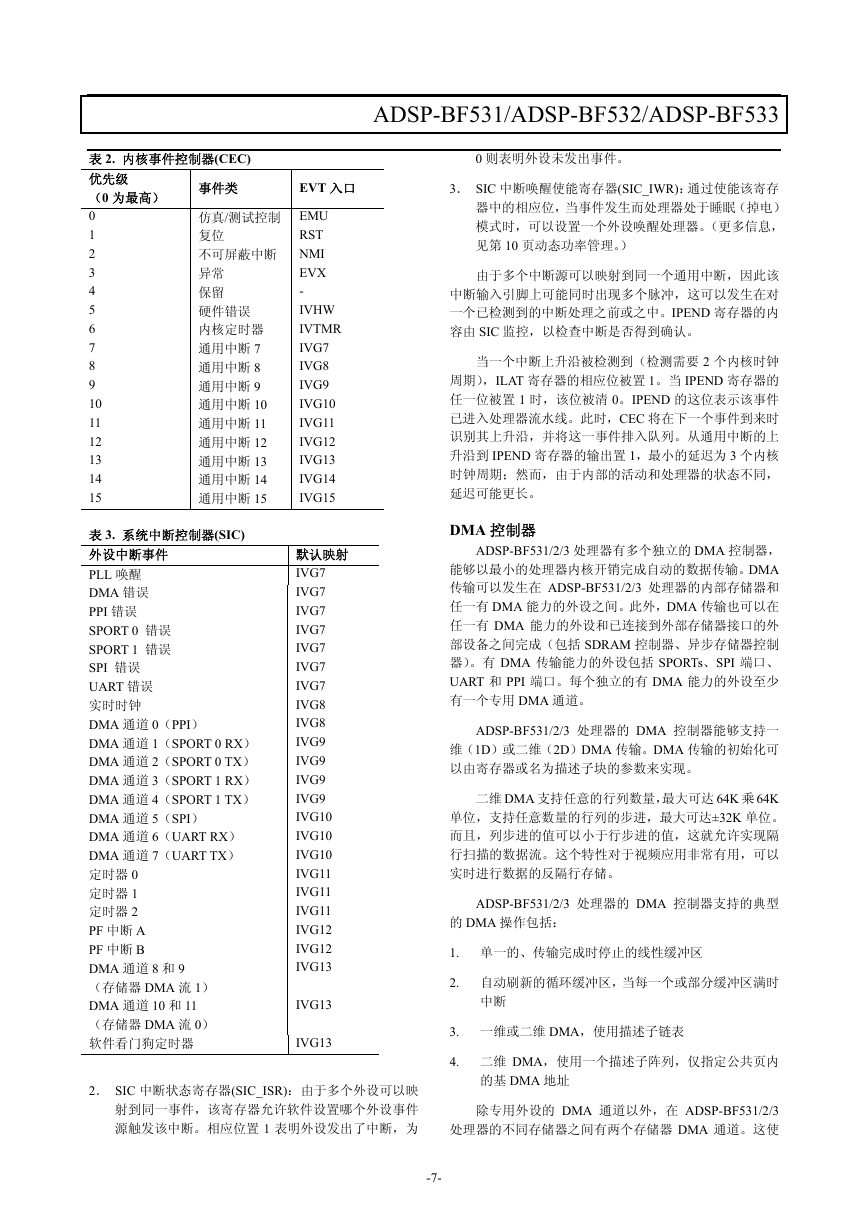

用外部元件连接 RTC 的引脚 RTXI 和 RTXO,如图 6

所示。

图 6 RTC 的外部元件

推荐元件:

ECLIPTEK EC38J(通孔封装)

EPSON MC-405 12pF LOAD(表贴封装)

C1=22pF

C2=22pF

R1=10MΩ

注意:C1 与 C2 专用于推荐的晶振 X1

联系晶振制造商索取 C1 和 C2 的详细资料

规格假定板上线路容值为 3pF

“看门狗”定时器

如果设置硬件复位,“看门狗”定时器可以复位 CPU

和 ADSP-BF531/2/3 外设。复位后,软件可以通过查询“看

门狗”定时控制寄存器的一个状态位来确定“看门狗”是

否为硬件复位的来源。

定 时 器 的 时 钟采 用 系 统 时 钟(SCLK) , 以 最 高 频 率

f

SCLK

运行。

定时器

ADSP-BF531/2/3 处理器有 4 个通用可编程定时器。3

个定时器连有外部引脚,可以用作脉冲宽度调制器(PWM)

或定时器输出,也可以用作定时器的输入时钟或测量外部

事件的脉冲宽度周期的输入。这些定时器可对一个输入

PF1 引脚的外部时钟,输入 PPI_CLK 引脚的外部时钟或对

内 SCLK 同步。

定时器单元可以与 UART 联合使用,进行串行通道数

据流的脉冲宽度的测量,提供自动的波特率检测功能。

定时器能够向处理器内核发出中断,为同步、处理器

时钟、或外部信号的计数值提供周期性事件。

除 3 个通用可编程定时器外,还提供了第 4 个定时器。

这个额外的定时器由内部处理器时钟(CCLK)驱动,一般用

作系统标记时钟,用以产生操作系统的周期性中断。

串行口(SPORTs)

ADSP-BF531/2/3 处理器提供 2 个双通道同步串行端口

(SPORT0 和 SPORT1)来完成串行和多处理器的通信工

作。SPORT 有以下特点:

1. 支持 I2S 功能。

2. 双向操作:每个 SPORT 都有 2 套独立的发送和接收引

脚,支持 I2S 立体声 8 通道。

3. 缓冲的(8-deep)发送和接收端口:每个端口都有一

个数据寄存器,用以同其它处理器部件间进行双向数

据传输;多个移位寄存器用于数据寄存器内数据的移

入和移出。

4. 时钟:每个发送或接收端口或者使用外部串行时钟,

/131,070)

或者使用自己产生的频率范围为 (

f

SCLK

Hz 到( SCLK

f

/2) Hz 的时钟。

ADSP-BF531/2/3 处理器包含一个 32 位定时器,可用

5. 字长:每个 SPORT 都支持 3 到 32 位长度的串行数据

-8-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc