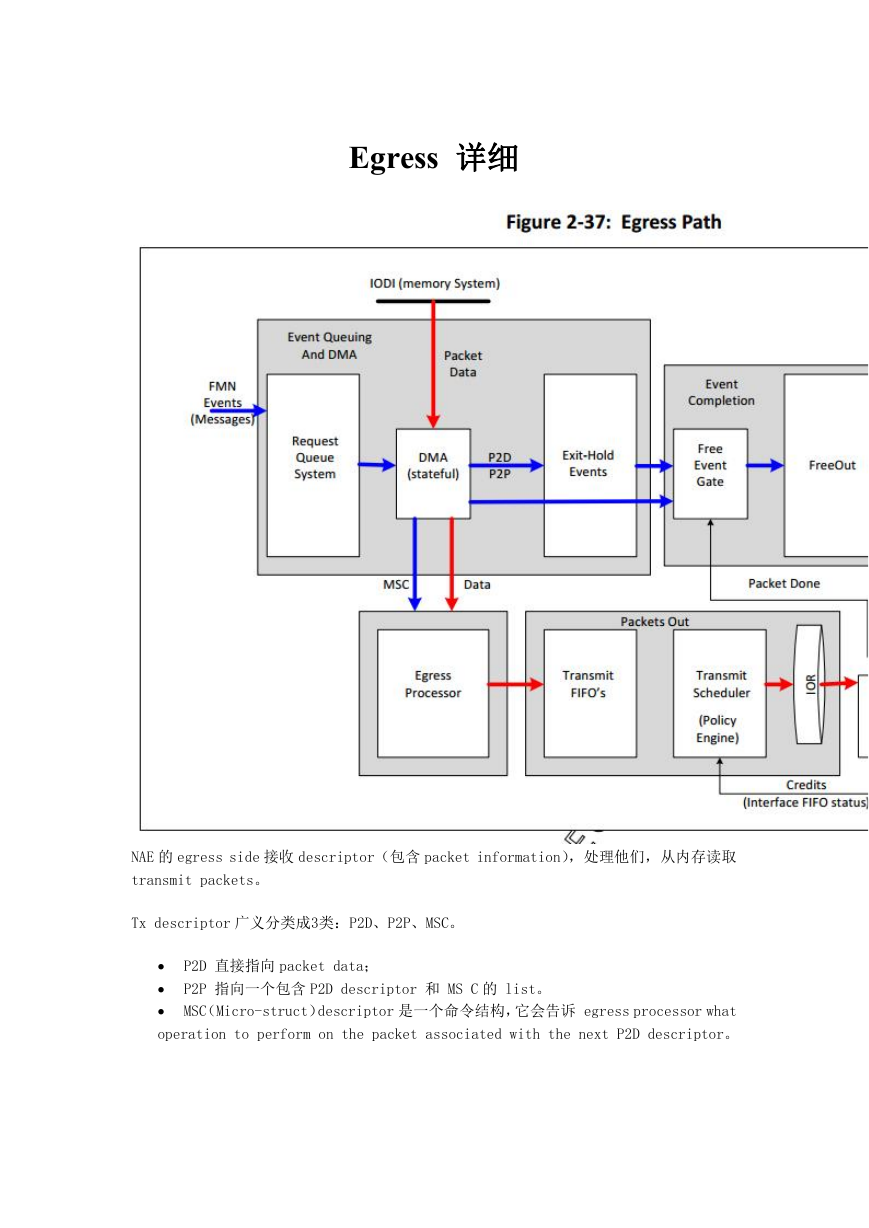

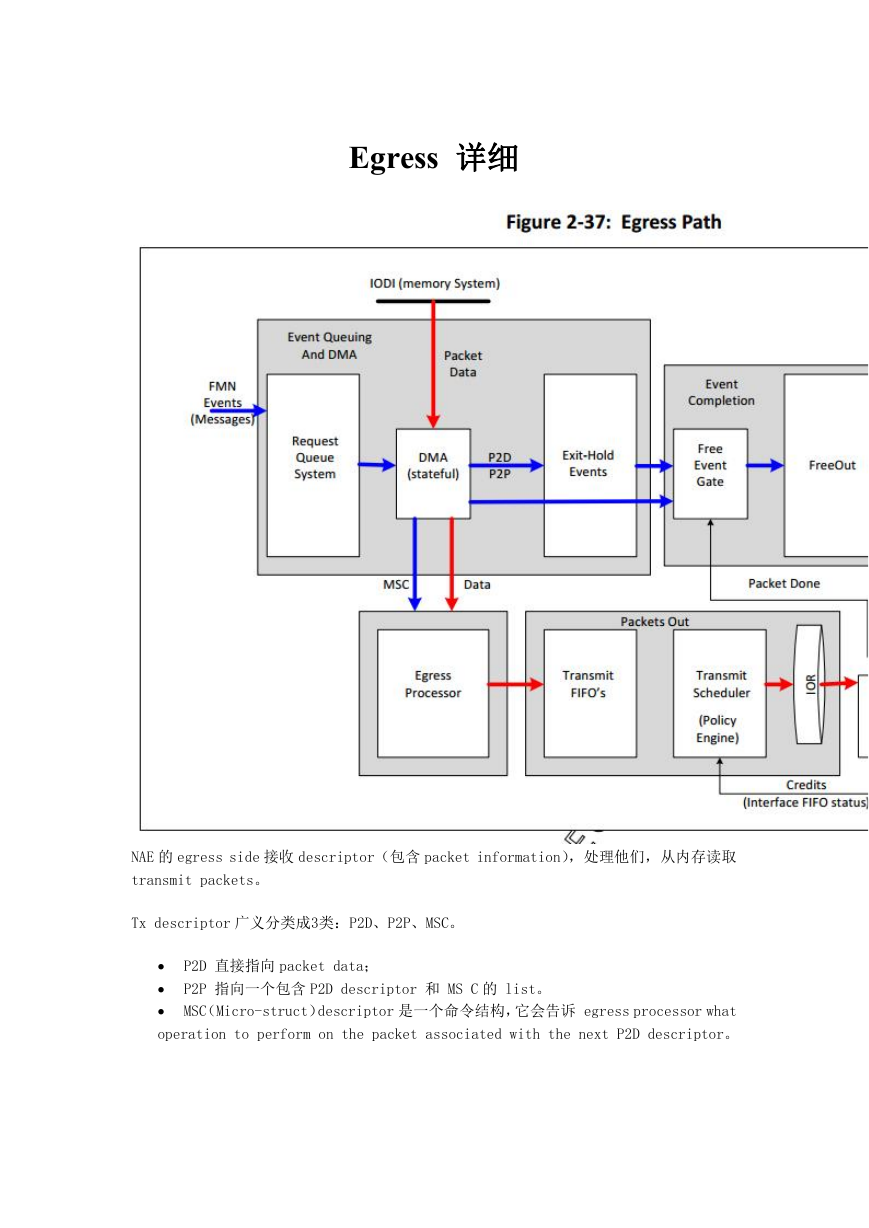

Egress 详细

NAE 的 egress side 接收 descriptor(包含 packet information),处理他们,从内存读取

transmit packets。

Tx descriptor 广义分类成3类:P2D、P2P、MSC。

P2D 直接指向 packet data;

P2P 指向一个包含 P2D descriptor 和 MS C 的 list。

MSC(Micro-struct)descriptor 是一个命令结构,它会告诉 egress processor what

operation to perform on the packet associated with the next P2D descriptor。

�

一般情况 POE block 会使用 enqueue POE 模式 通过 FMN 发送 Tx descriptor 给 NAE,

不过 nxCPU 也可以自己生成一个 transmit packet 通过 POE bypass 模式发送。micro-core

也可以直接转发一个接收 packet 给 egress。

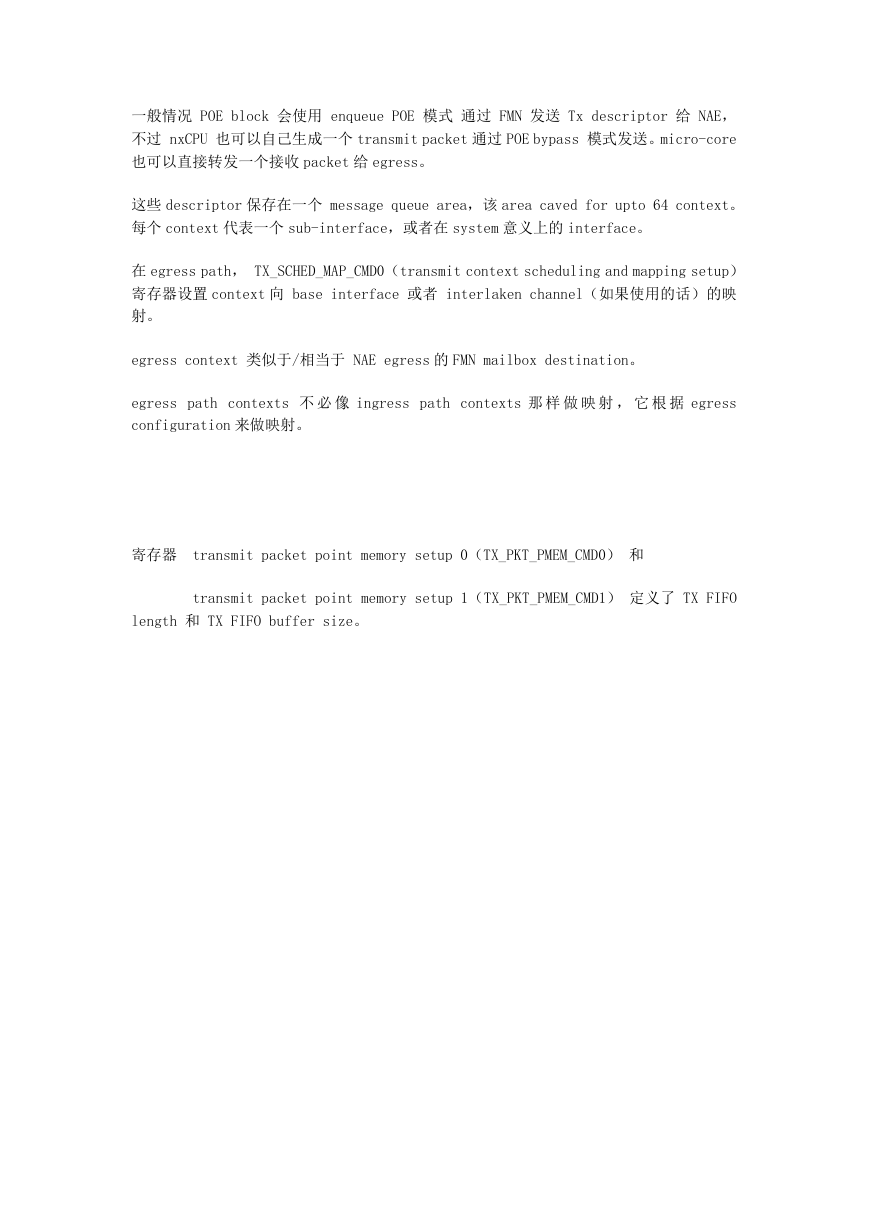

这些 descriptor 保存在一个 message queue area,该 area caved for upto 64 context。

每个 context 代表一个 sub-interface,或者在 system 意义上的 interface。

在 egress path, TX_SCHED_MAP_CMD0(transmit context scheduling and mapping setup)

寄存器设置 context 向 base interface 或者 interlaken channel(如果使用的话)的映

射。

egress context 类似于/相当于 NAE egress 的 FMN mailbox destination。

egress path contexts 不 必 像 ingress path contexts 那 样 做 映 射 , 它 根 据 egress

configuration 来做映射。

寄存器 transmit packet point memory setup 0(TX_PKT_PMEM_CMD0) 和

transmit packet point memory setup 1(TX_PKT_PMEM_CMD1) 定义了 TX FIFO

length 和 TX FIFO buffer size。

�

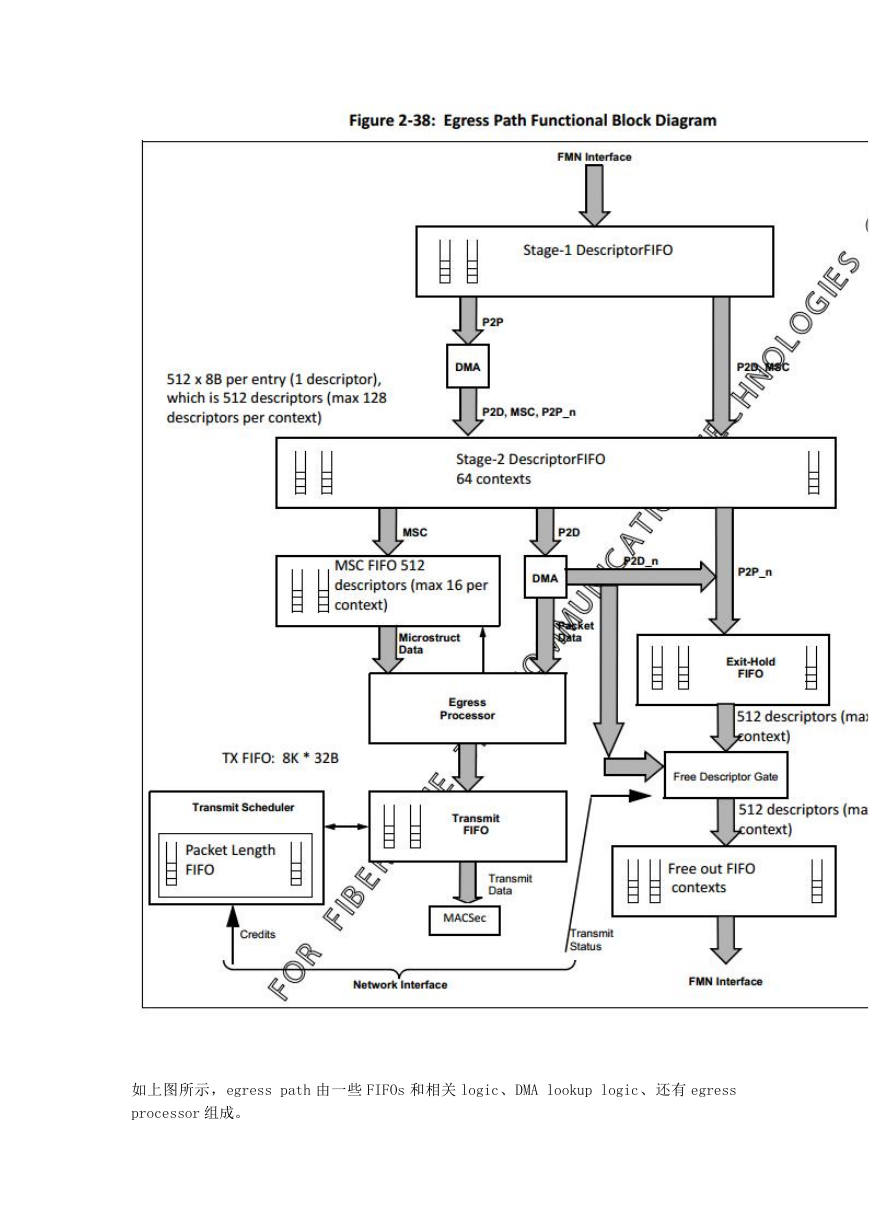

如上图所示,egress path 由一些 FIFOs 和相关 logic、DMA lookup logic、还有 egress

processor 组成。

�

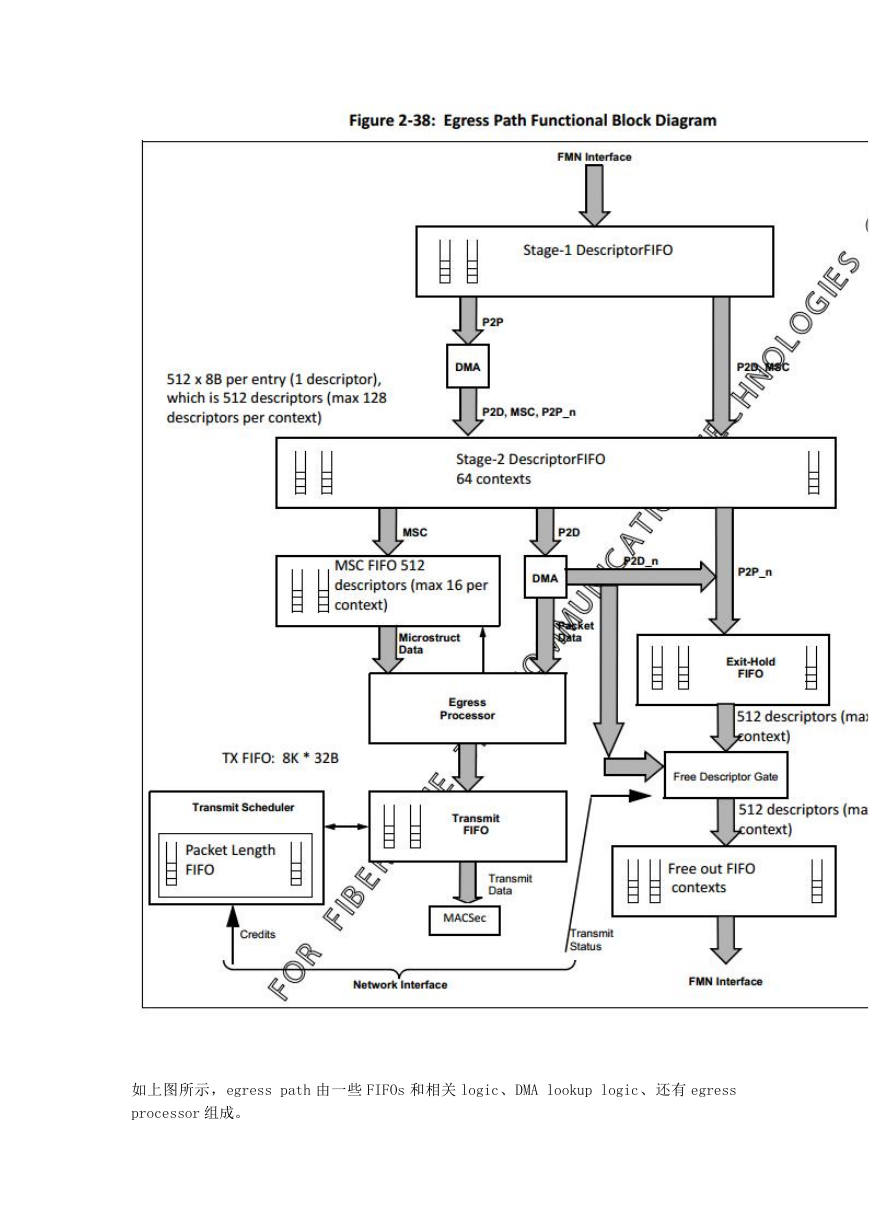

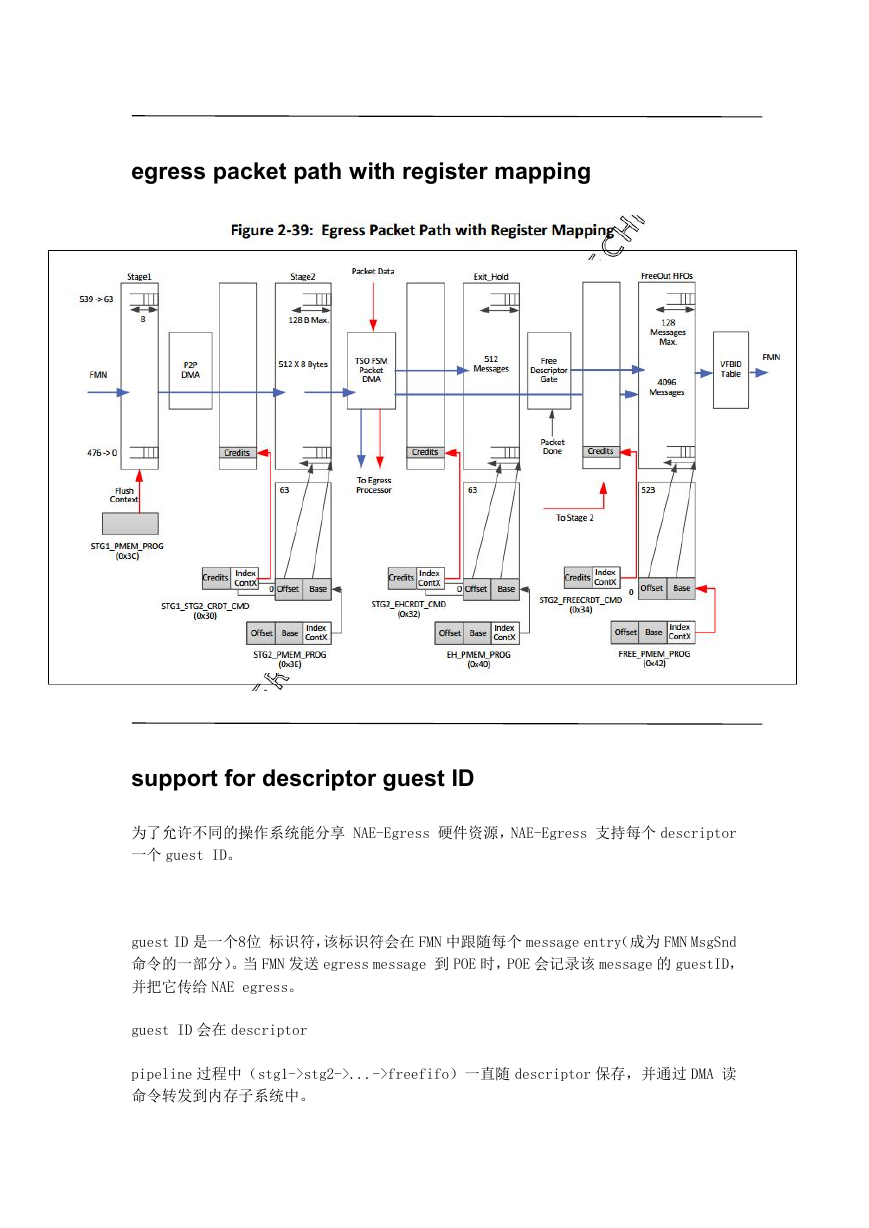

egress packet path with register mapping

support for descriptor guest ID

为了允许不同的操作系统能分享 NAE-Egress 硬件资源,NAE-Egress 支持每个 descriptor

一个 guest ID。

guest ID 是一个8位 标识符,该标识符会在 FMN 中跟随每个 message entry(成为 FMN MsgSnd

命令的一部分)。当 FMN 发送 egress message 到 POE 时,POE 会记录该 message 的 guestID,

并把它传给 NAE egress。

guest ID 会在 descriptor

pipeline 过程中(stg1->stg2->...->freefifo)一直随 descriptor 保存,并通过 DMA 读

命令转发到内存子系统中。

�

guest ID 也可以插入到 每个 freeback descriptor 的 Guest_ID field。在 freeback path

中,所有的 message 是 single-entry messages。

如果一个 pakcet 包含 p2p descriptor,该 p2p descriptor 的 guest ID 会被附到该 p2p

指向的列表中每个 descriptor。注意,同一个 packet 的所有 descriptor 有相同的 guestID。

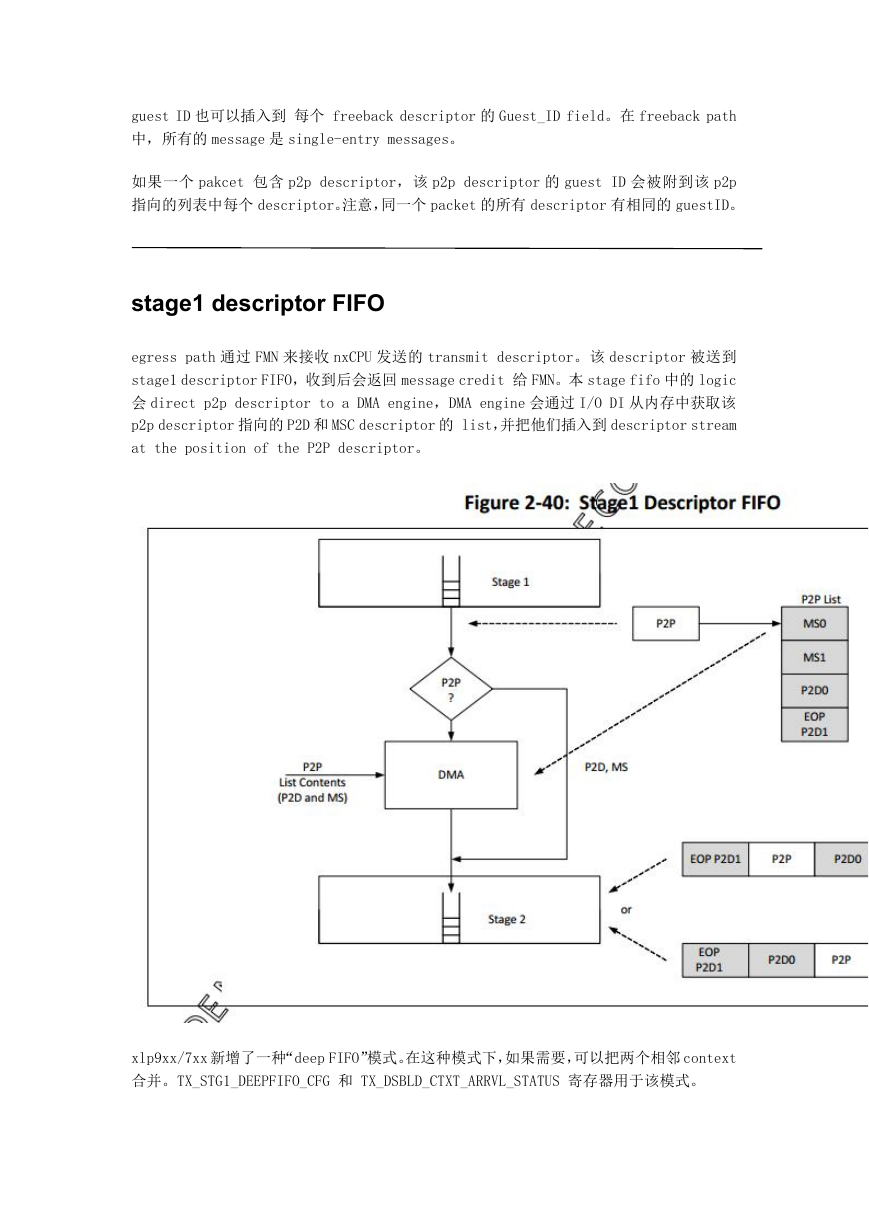

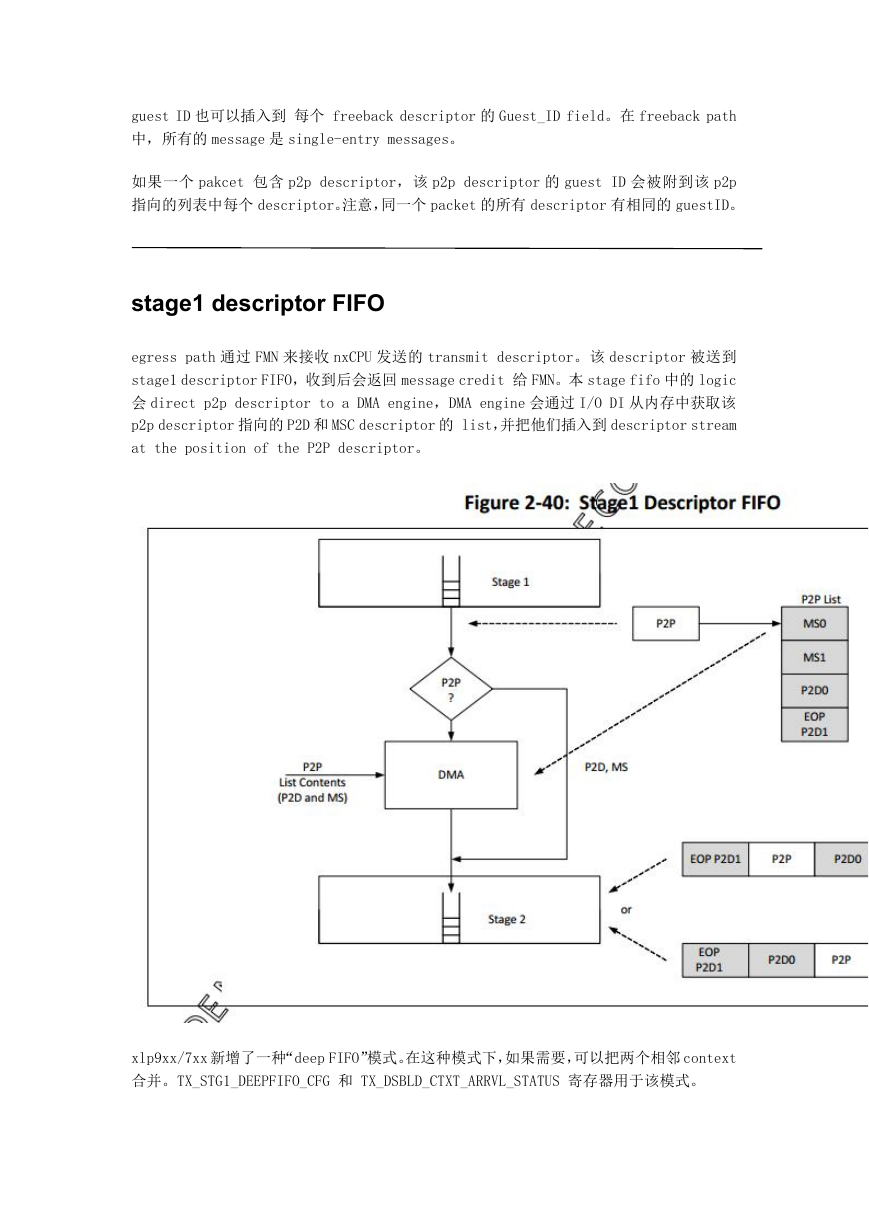

stage1 descriptor FIFO

egress path 通过 FMN 来接收 nxCPU 发送的 transmit descriptor。该 descriptor 被送到

stage1 descriptor FIFO,收到后会返回 message credit 给 FMN。本 stage fifo 中的 logic

会 direct p2p descriptor to a DMA engine,DMA engine 会通过 I/O DI 从内存中获取该

p2p descriptor 指向的 P2D 和 MSC descriptor 的 list,并把他们插入到 descriptor stream

at the position of the P2P descriptor。

xlp9xx/7xx 新增了一种“deep FIFO”模式。在这种模式下,如果需要,可以把两个相邻 context

合并。TX_STG1_DEEPFIFO_CFG 和 TX_DSBLD_CTXT_ARRVL_STATUS 寄存器用于该模式。

�

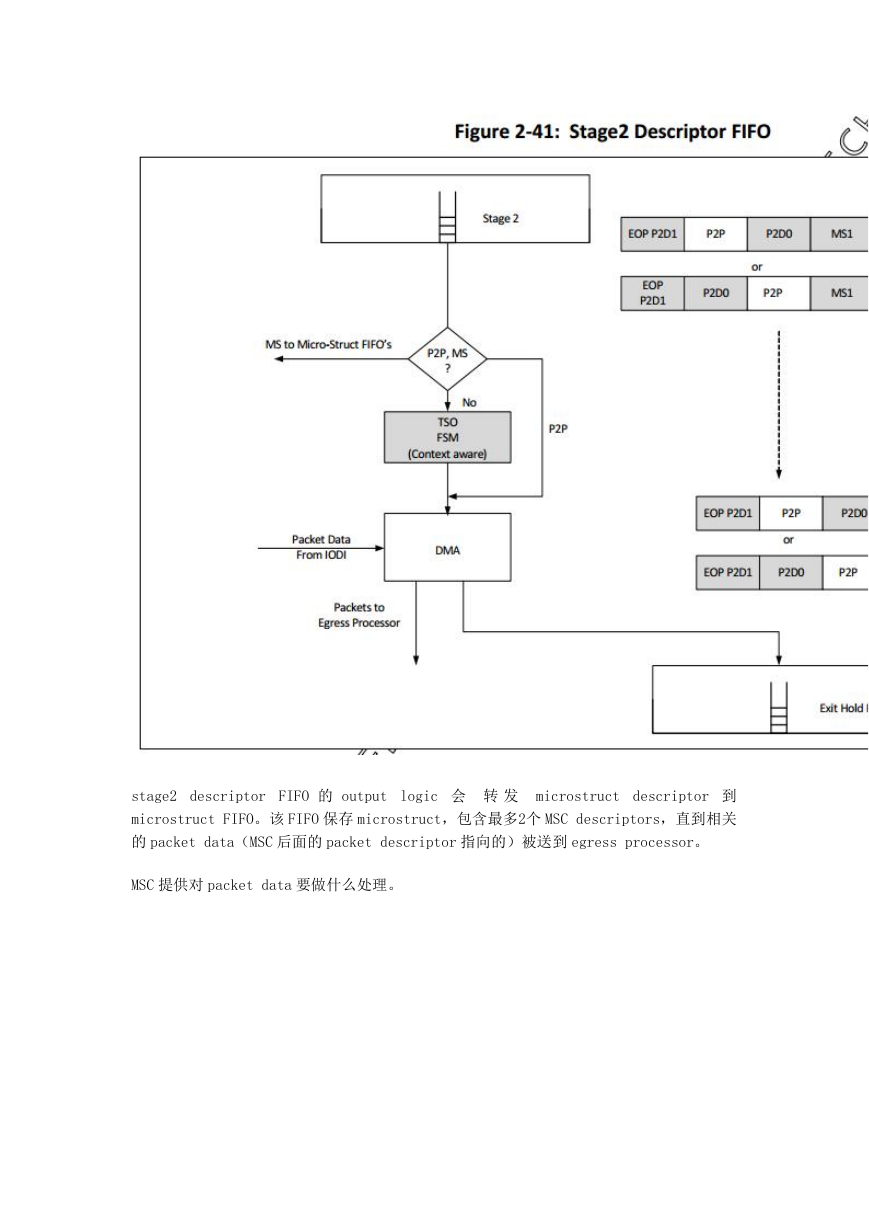

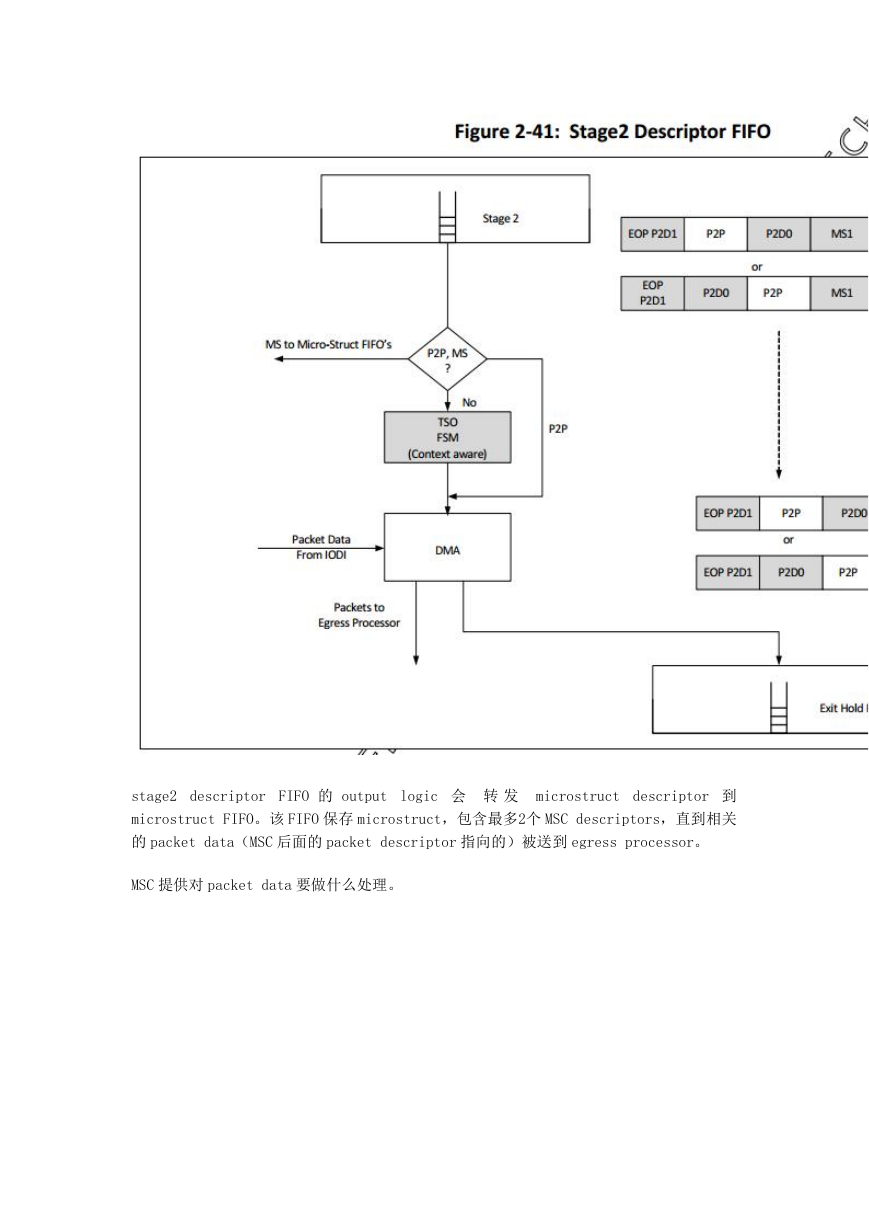

stage2 descriptor FIFO

为了 enable FMN to stage1 to stage2 transfer,必须 establish credits。credits 应

该等于 the size of respective stage2 context FIFO register STG1_STG2CRDT_CMD when

used。stage2的 FIFO 使用 STG2_PMEM_PROG 寄存器内划分 context。

stage2 descriptor FIFO direct P2D descriptors to DMA blocks,DMA block 从内存取

出 packet data 并发送到 egress processor。

P2D 和 P2P descriptor 被发送到 exit hold FIFO,他们会在 exit hold FIFO 里呆到 packet

data 被送到 network interface 为止。

在 early freeout 模式,一旦相关的 data 被 DMA 取走,非 EOP descriptor 被 free back。

credits 必须被 established from STG2->Exit hold 、STG2->FreeFIFO to enbale stage2

to send further packets。stage2会使用 STG2->EH、STG2->FREE credits 的最小值来决

定 STG2 transmission。

credits 的设置使用 STG2_EHCRDT_CMD 和 STG2_FREECRDT_CMD。

�

stage2 descriptor FIFO 的 output logic 会 转 发 microstruct descriptor 到

microstruct FIFO。该 FIFO 保存 microstruct,包含最多2个 MSC descriptors,直到相关

的 packet data(MSC 后面的 packet descriptor 指向的)被送到 egress processor。

MSC 提供对 packet data 要做什么处理。

�

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc