Single Phase, Bi-directional Power/Energy IC

CS5463

Features

Energy Data Linearity: ±0.1% of Reading

over 1000:1 Dynamic Range

On-chip Functions:

- Instantaneous Voltage, Current, and Power

- IRMS and VRMS, Apparent, Reactive, and Active

(Real) Power

- Active Fundamental and Harmonic Power

- Reactive Fundamental, Power Factor, and Line

Frequency

- Energy-to-pulse Conversion

- System Calibrations and Phase Compensation

- Temperature Sensor

Meets accuracy spec for IEC, ANSI, JIS.

Low Power Consumption

Current Input Optimized for Sense Resistor.

GND-referenced Signals with Single Supply

On-chip 2.5 V Reference (25 ppm/°C typ)

Power Supply Monitor

Simple Three-wire Digital Serial Interface

“Auto-boot” Mode from Serial E2PROM

Power Supply Configurations:

VA+ = +5 V; AGND = 0 V; VD+ = +3.3 V to +5 V

combines

Description

The CS5463 is an integrated power measure-

ment device which

two ∆Σ

analog-to-digital converters, power calculation

engine, energy-to-frequency converter, and a

serial interface on a single chip. It is designed to

accurately measure instantaneous current and

voltage, and calculate VRMS, IRMS, instanta-

neous power, apparent power, active power, and

reactive power for single-phase, 2- or 3-wire

power metering applications.

The CS5463 is optimized to interface to shunt re-

sistors or current

for current

measurement, and to resistive dividers or poten-

tial transformers for voltage measurement.

The CS5463 features a bi-directional serial inter-

face for communication with a processor and a

programmable energy-to-pulse output function.

Additional features include on-chip functionality

to facilitate system-level calibration, temperature

sensor, voltage sag detection, and phase

compensation.

transformers

ORDERING INFORMATION:

See Page 44.

VA+

RESET

VD+

IIN+

IIN-

PGA

4th Order ∆Σ

Modulator

Digital

Filter

HPF

Option

VREFIN

x1

Temperature

Sensor

VIN+

VIN-

x10

2nd Order ∆Σ

Modulator

Digital

Filter

HPF

Option

Power

Calculation

Engine

MODE

CS

SDI

SDO

SCLK

INT

E1

E2

E3

Serial

Interface

E-to-F

VREFOUT

Voltage

Reference

Power

Monitor

System

Clock

/K

Clock

Generator

Calibration

AGND

PFMON

XIN XOUT CPUCLK

DGND

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2005

(All Rights Reserved)

AUG ‘05

DS678PP1

�

CS5463

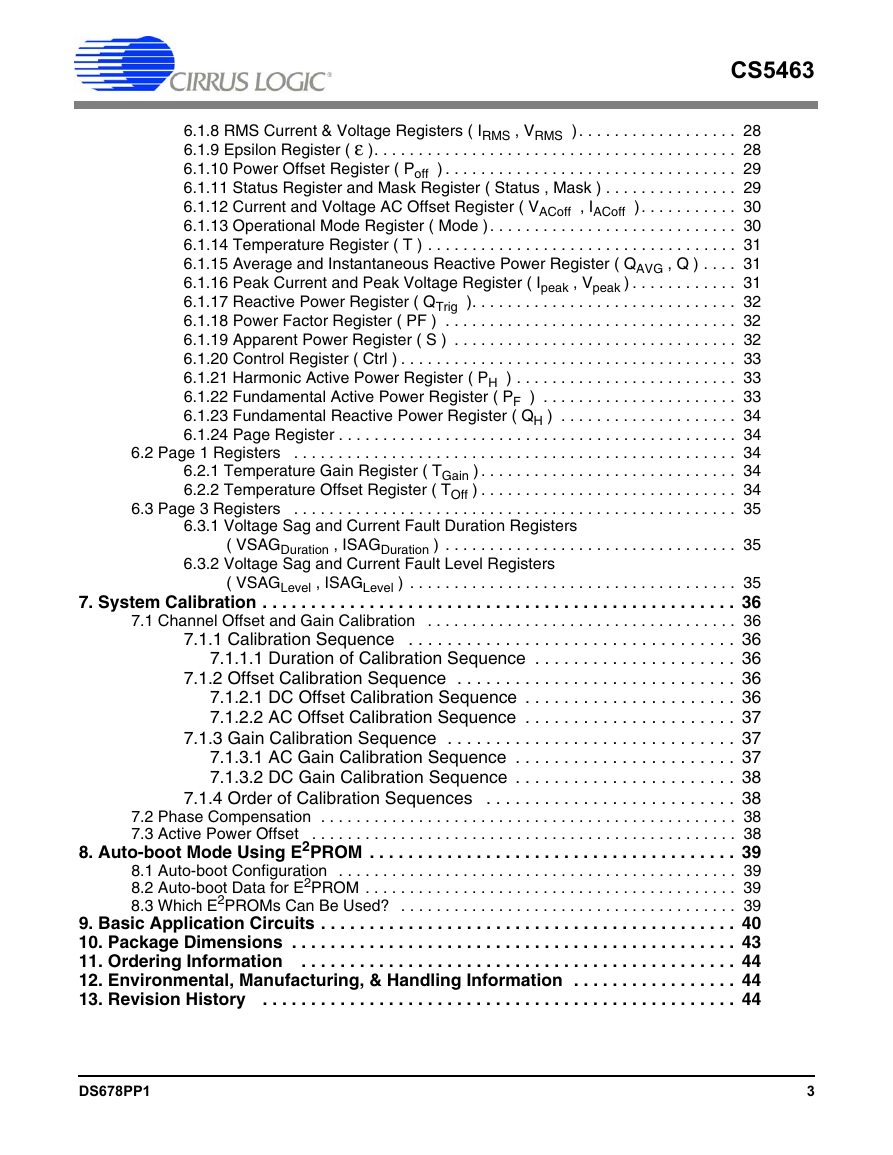

TABLE OF CONTENTS

1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2. Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3. Characteristics & Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4. Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.1 Digital Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.2 Voltage and Current Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.3 Power Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.4 Linearity Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.1 Analog Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.1.1 Voltage Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.1.2 Current Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.2 IIR Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.3 High-pass Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.4 Performing Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.5 Energy Pulse Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.5.1 Active Energy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.5.2 Apparent Energy Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.5.3 Reactive Energy Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.5.4 Voltage Channel Sign Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.5.5 PFMON Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

5.5.6 Design Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

5.6 Sag and Fault Detect Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

5.7 On-chip Temperature Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

5.8 Voltage Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.9 System Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.10 Power-down States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.11 Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.12 Event Handler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.12.1 Typical Interrupt Handler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.13 Serial Port Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.13.1 Serial Port Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.14 Register Paging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.15 Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.15.1 Start Conversions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.15.2 SYNC0 and SYNC1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.15.3 Power-up/Halt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.15.4 Power-down and Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.15.5 Register Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.15.6 Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

6. Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6.1 Page 0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6.1.1 Configuration Register ( Config ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6.1.2 Current and Voltage DC Offset Register ( IDCoff , VDCoff ) . . . . . . . . . . . . 27

6.1.3 Current and Voltage Gain Register ( Ign , Vgn ) . . . . . . . . . . . . . . . . . . . . 27

6.1.4 Cycle Count Register ( Cycle Count ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1.5 PulseRateE Register ( PulseRateE ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1.6 Instantaneous Current, Voltage, and Power Registers ( I , V , P ) . . . . . . 28

6.1.7 Active (Real) Power Register ( PActive ) . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2

DS678PP1

�

CS5463

6.1.8 RMS Current & Voltage Registers ( IRMS , VRMS ). . . . . . . . . . . . . . . . . . 28

6.1.9 Epsilon Register ( ε ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.1.10 Power Offset Register ( Poff ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

6.1.11 Status Register and Mask Register ( Status , Mask ) . . . . . . . . . . . . . . . 29

6.1.12 Current and Voltage AC Offset Register ( VACoff , IACoff ). . . . . . . . . . . 30

6.1.13 Operational Mode Register ( Mode ). . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

6.1.14 Temperature Register ( T ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

6.1.15 Average and Instantaneous Reactive Power Register ( QAVG , Q ) . . . . 31

6.1.16 Peak Current and Peak Voltage Register ( Ipeak , Vpeak ) . . . . . . . . . . . . 31

6.1.17 Reactive Power Register ( QTrig ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.1.18 Power Factor Register ( PF ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.1.19 Apparent Power Register ( S ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.1.20 Control Register ( Ctrl ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.1.21 Harmonic Active Power Register ( PH ) . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.1.22 Fundamental Active Power Register ( PF ) . . . . . . . . . . . . . . . . . . . . . . 33

6.1.23 Fundamental Reactive Power Register ( QH ) . . . . . . . . . . . . . . . . . . . . 34

6.1.24 Page Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2 Page 1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2.1 Temperature Gain Register ( TGain ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2.2 Temperature Offset Register ( TOff ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.3 Page 3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.3.1 Voltage Sag and Current Fault Duration Registers

( VSAGDuration , ISAGDuration ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.3.2 Voltage Sag and Current Fault Level Registers

( VSAGLevel , ISAGLevel ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

7. System Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.1 Channel Offset and Gain Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.1.1 Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.1.1.1 Duration of Calibration Sequence . . . . . . . . . . . . . . . . . . . . . 36

7.1.2 Offset Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.1.2.1 DC Offset Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . 36

7.1.2.2 AC Offset Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . 37

7.1.3 Gain Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

7.1.3.1 AC Gain Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . 37

7.1.3.2 DC Gain Calibration Sequence . . . . . . . . . . . . . . . . . . . . . . . 38

7.1.4 Order of Calibration Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . 38

7.2 Phase Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

7.3 Active Power Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

8. Auto-boot Mode Using E2PROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.1 Auto-boot Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.2 Auto-boot Data for E2PROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.3 Which E2PROMs Can Be Used? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

9. Basic Application Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10. Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

11. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

12. Environmental, Manufacturing, & Handling Information . . . . . . . . . . . . . . . . . 44

13. Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

DS678PP1

3

�

CS5463

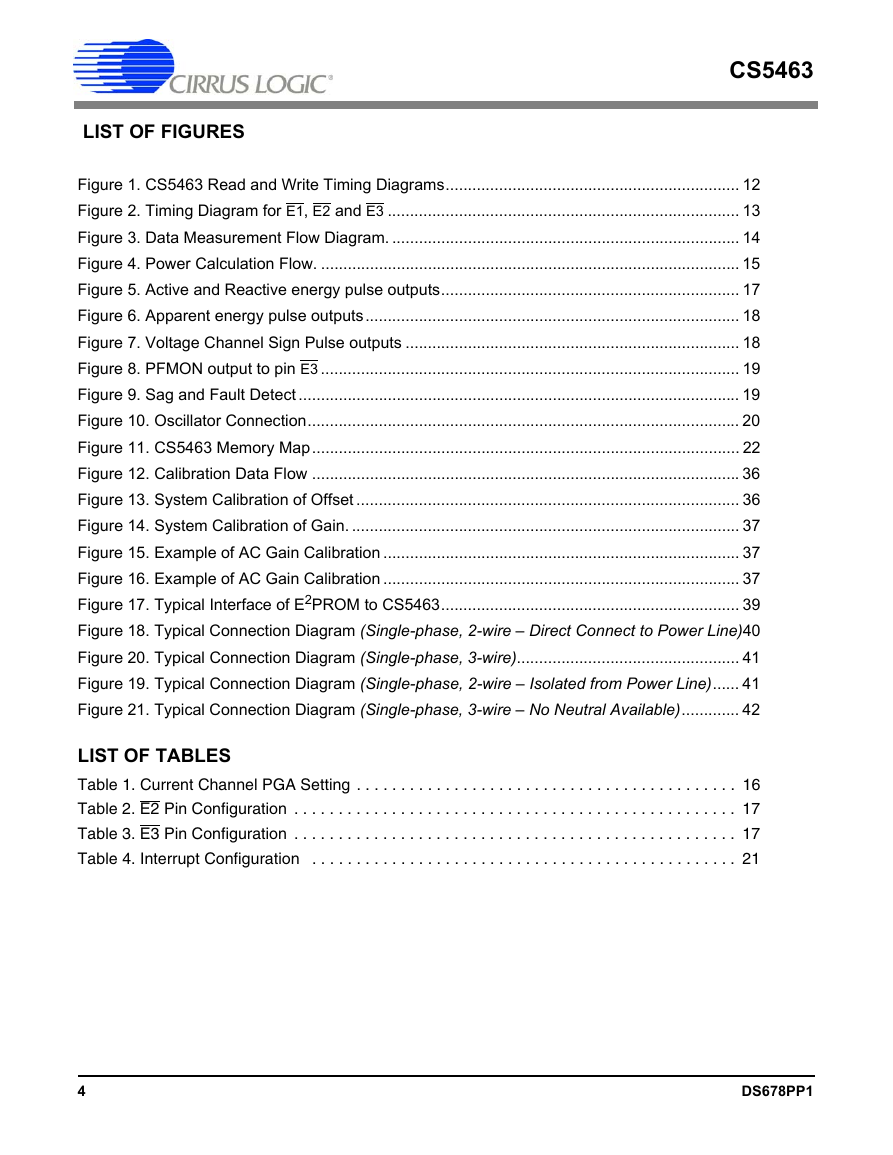

LIST OF FIGURES

Figure 1. CS5463 Read and Write Timing Diagrams.................................................................. 12

Figure 2. Timing Diagram for E1, E2 and E3 ............................................................................... 13

Figure 3. Data Measurement Flow Diagram. .............................................................................. 14

Figure 4. Power Calculation Flow. .............................................................................................. 15

Figure 5. Active and Reactive energy pulse outputs................................................................... 17

Figure 6. Apparent energy pulse outputs.................................................................................... 18

Figure 7. Voltage Channel Sign Pulse outputs ........................................................................... 18

Figure 8. PFMON output to pin E3 .............................................................................................. 19

Figure 9. Sag and Fault Detect ................................................................................................... 19

Figure 10. Oscillator Connection................................................................................................. 20

Figure 11. CS5463 Memory Map................................................................................................ 22

Figure 12. Calibration Data Flow ................................................................................................ 36

Figure 13. System Calibration of Offset ...................................................................................... 36

Figure 14. System Calibration of Gain. ....................................................................................... 37

Figure 15. Example of AC Gain Calibration ................................................................................ 37

Figure 16. Example of AC Gain Calibration ................................................................................ 37

Figure 17. Typical Interface of E2PROM to CS5463................................................................... 39

Figure 18. Typical Connection Diagram (Single-phase, 2-wire – Direct Connect to Power Line)40

Figure 20. Typical Connection Diagram (Single-phase, 3-wire).................................................. 41

Figure 19. Typical Connection Diagram (Single-phase, 2-wire – Isolated from Power Line)...... 41

Figure 21. Typical Connection Diagram (Single-phase, 3-wire – No Neutral Available)............. 42

LIST OF TABLES

Table 1. Current Channel PGA Setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2. E2 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 3. E3 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 4. Interrupt Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4

DS678PP1

�

CS5463

1. OVERVIEW

The CS5463 is a CMOS monolithic power measurement device with a computation engine and an ener-

gy-to-frequency pulse output. The CS5463 combines a programmable gain amplifier, two ∆Σ Ana-

log-to-Digital Converters (ADCs), system calibration and a computation engine on a single chip.

The CS5463 is designed for power measurement applications and is optimized to interface to a current

sense resistor or transformer for current measurement, and to a resistive divider or potential transformer

for voltage measurement. The current channel provides programmable gains to accommodate various in-

put levels from a multitude of sensing elements. With single +5 V supply on VA+/AGND, both of the

CS5463’s input channels can accommodate common mode plus signal levels between (AGND - 0.25 V)

and VA+.

The CS5463 also is equipped with a computation engine that calculates instantaneous power, IRMS,

VRMS, apparent power, active (real) power, reactive power, harmonic active power, active and reactive

fundamental power, and power factor. The CS5463 additional features include line frequency, current and

voltage sag detection, zero-cross detection, positive-only accumulation mode, and three programmable

pulse output pins. To facilitate communication to a microprocessor, the CS5463 includes a simple

three-wire serial interface which is SPI™ and Microwire™ compatible. The CS5463 provides three out-

puts for energy registration. E1, E2 and E3 are designed to interface to a microprocessor.

DS678PP1

5

�

CS5463

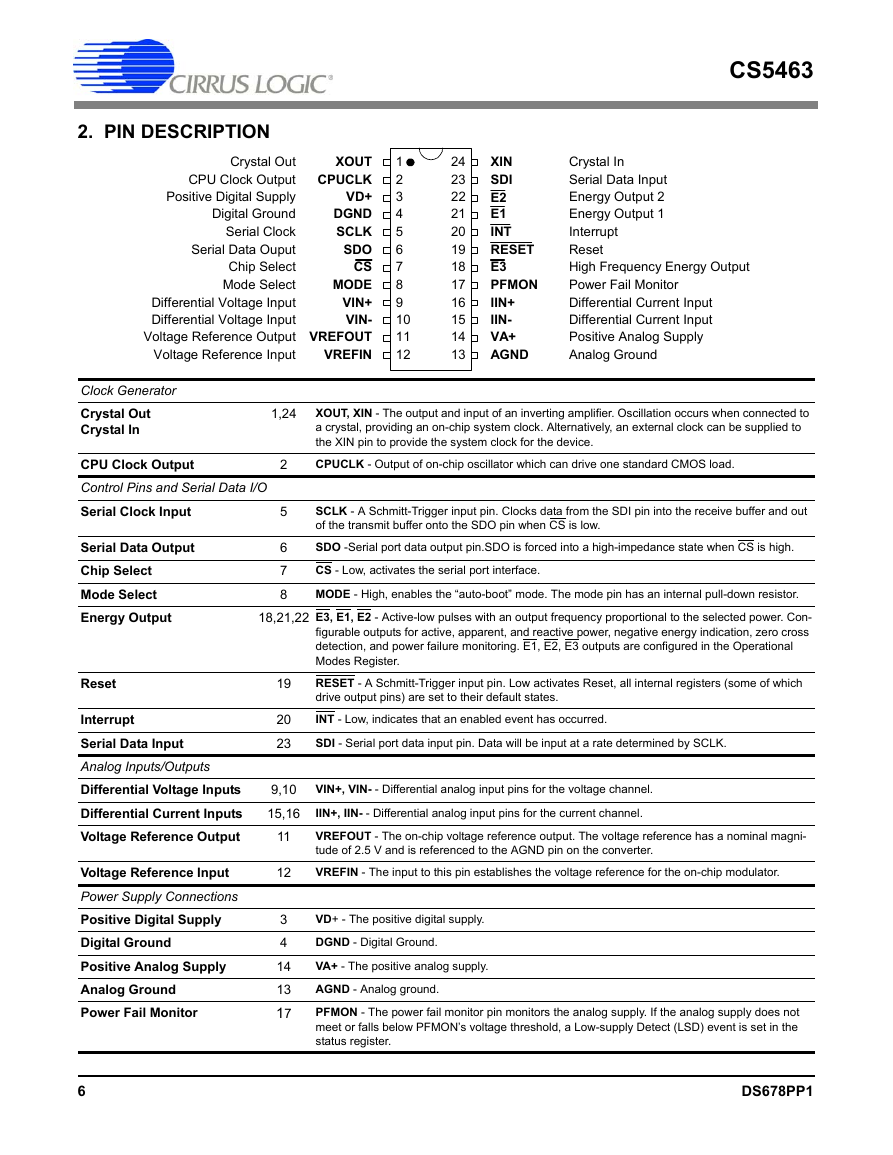

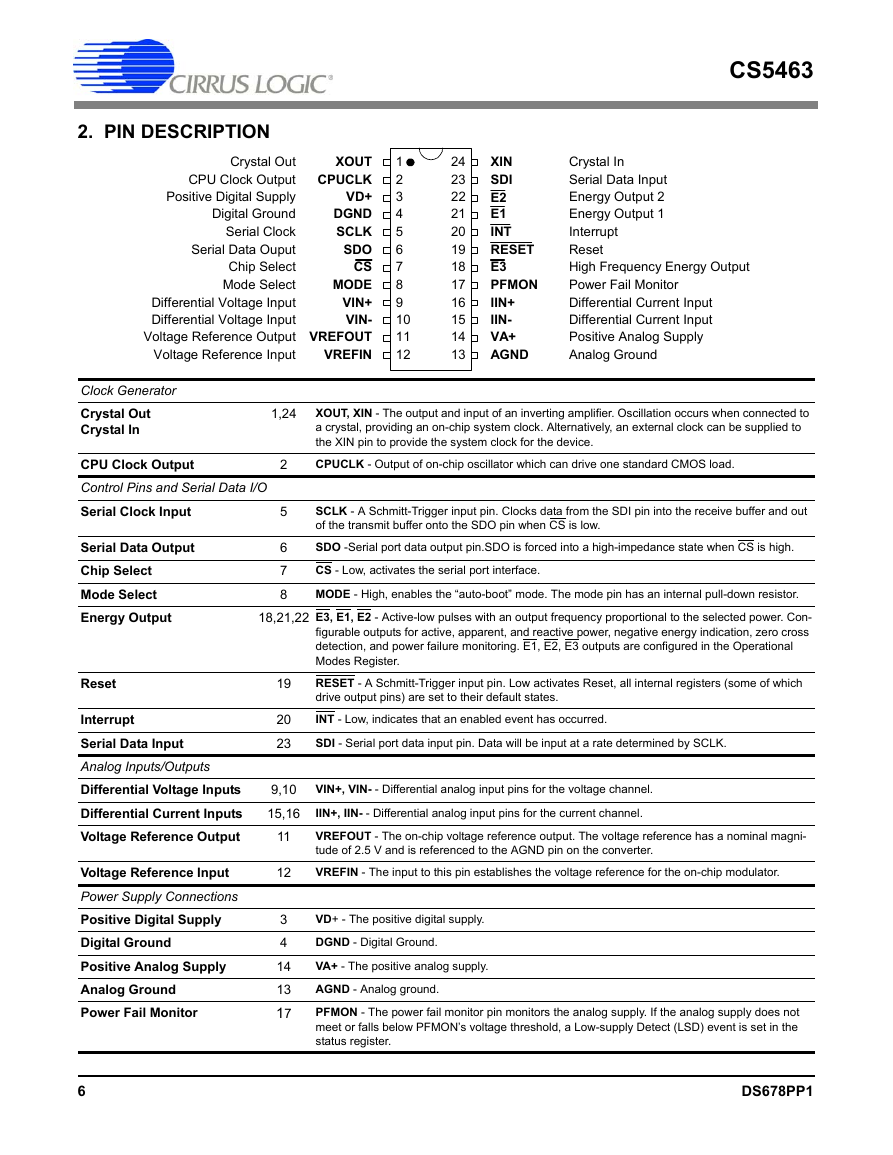

2. PIN DESCRIPTION

Crystal Out

CPU Clock Output

Positive Digital Supply

Digital Ground

Serial Clock

Serial Data Ouput

Chip Select

Mode Select

Differential Voltage Input

Differential Voltage Input

Voltage Reference Output

Voltage Reference Input

XOUT

CPUCLK

VD+

DGND

SCLK

SDO

CS

MODE

VIN+

VIN-

VREFOUT

VREFIN

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

XIN

SDI

E2

E1

INT

RESET

E3

PFMON

IIN+

IIN-

VA+

AGND

Crystal In

Serial Data Input

Energy Output 2

Energy Output 1

Interrupt

Reset

High Frequency Energy Output

Power Fail Monitor

Differential Current Input

Differential Current Input

Positive Analog Supply

Analog Ground

Clock Generator

Crystal Out

Crystal In

CPU Clock Output

Control Pins and Serial Data I/O

Serial Clock Input

Serial Data Output

Chip Select

Mode Select

Energy Output

Reset

Interrupt

Serial Data Input

Analog Inputs/Outputs

Differential Voltage Inputs

Differential Current Inputs

Voltage Reference Output

Voltage Reference Input

Power Supply Connections

Positive Digital Supply

Digital Ground

Positive Analog Supply

Analog Ground

Power Fail Monitor

1,24

2

5

6

7

8

XOUT, XIN - The output and input of an inverting amplifier. Oscillation occurs when connected to

a crystal, providing an on-chip system clock. Alternatively, an external clock can be supplied to

the XIN pin to provide the system clock for the device.

CPUCLK - Output of on-chip oscillator which can drive one standard CMOS load.

SCLK - A Schmitt-Trigger input pin. Clocks data from the SDI pin into the receive buffer and out

of the transmit buffer onto the SDO pin when CS is low.

SDO -Serial port data output pin.SDO is forced into a high-impedance state when CS is high.

CS - Low, activates the serial port interface.

MODE - High, enables the “auto-boot” mode. The mode pin has an internal pull-down resistor.

18,21,22 E3, E1, E2 - Active-low pulses with an output frequency proportional to the selected power. Con-

figurable outputs for active, apparent, and reactive power, negative energy indication, zero cross

detection, and power failure monitoring. E1, E2, E3 outputs are configured in the Operational

Modes Register.

RESET - A Schmitt-Trigger input pin. Low activates Reset, all internal registers (some of which

drive output pins) are set to their default states.

INT - Low, indicates that an enabled event has occurred.

SDI - Serial port data input pin. Data will be input at a rate determined by SCLK.

19

20

23

9,10

15,16

11

12

3

4

14

13

17

VIN+, VIN- - Differential analog input pins for the voltage channel.

IIN+, IIN- - Differential analog input pins for the current channel.

VREFOUT - The on-chip voltage reference output. The voltage reference has a nominal magni-

tude of 2.5 V and is referenced to the AGND pin on the converter.

VREFIN - The input to this pin establishes the voltage reference for the on-chip modulator.

VD+ - The positive digital supply.

DGND - Digital Ground.

VA+ - The positive analog supply.

AGND - Analog ground.

PFMON - The power fail monitor pin monitors the analog supply. If the analog supply does not

meet or falls below PFMON’s voltage threshold, a Low-supply Detect (LSD) event is set in the

status register.

6

DS678PP1

�

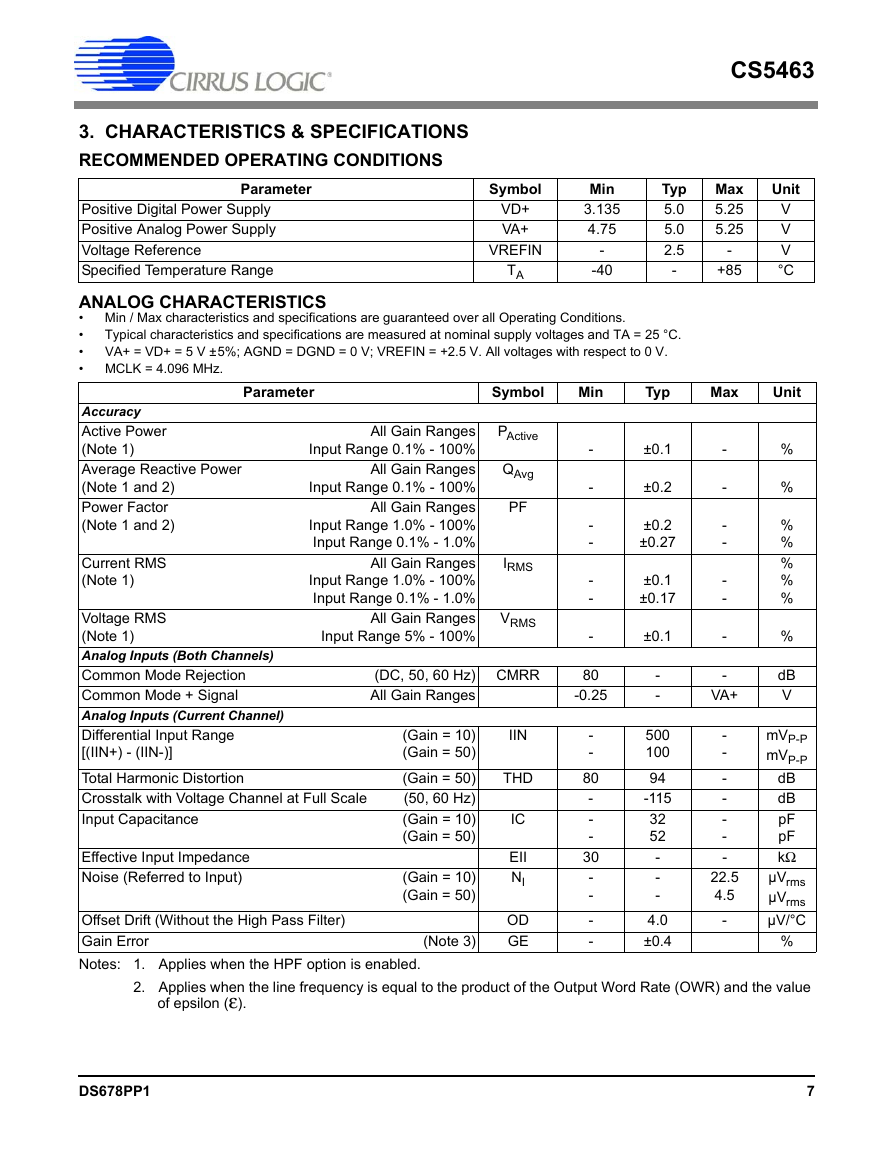

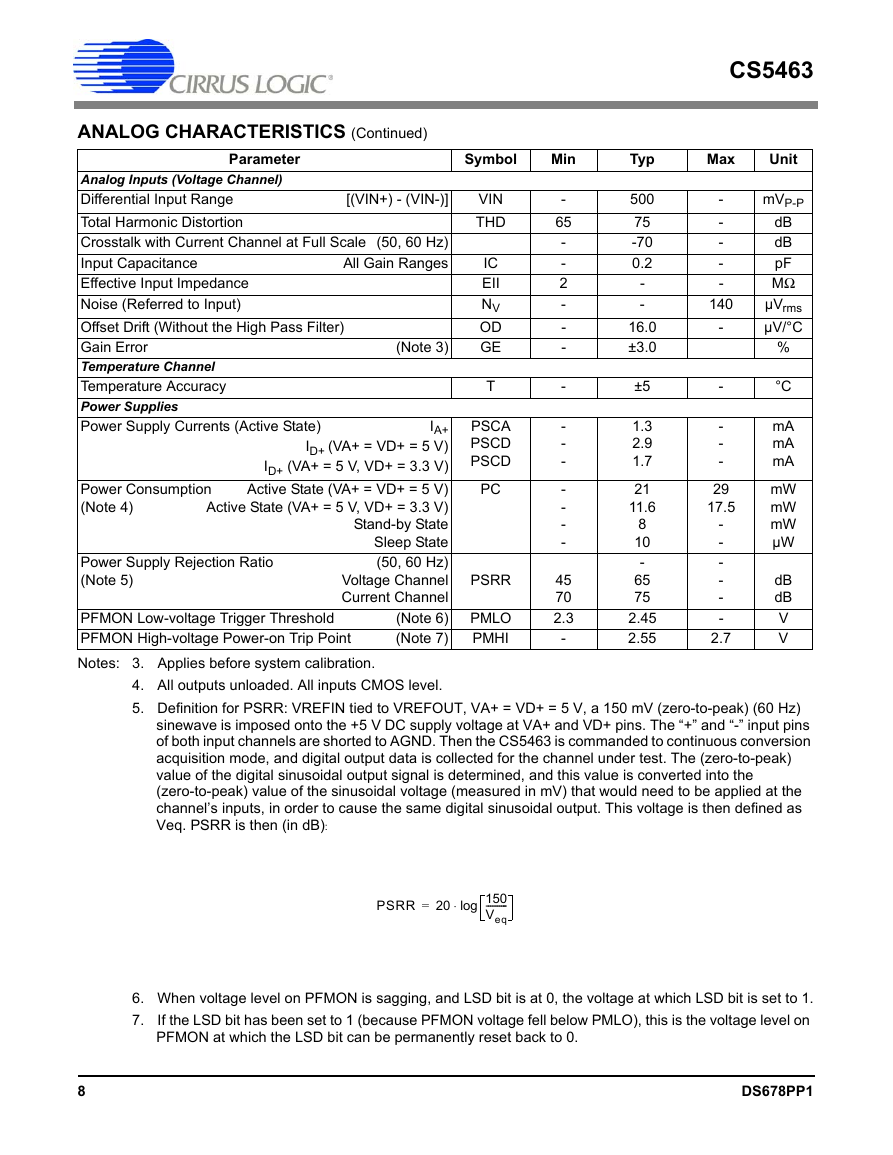

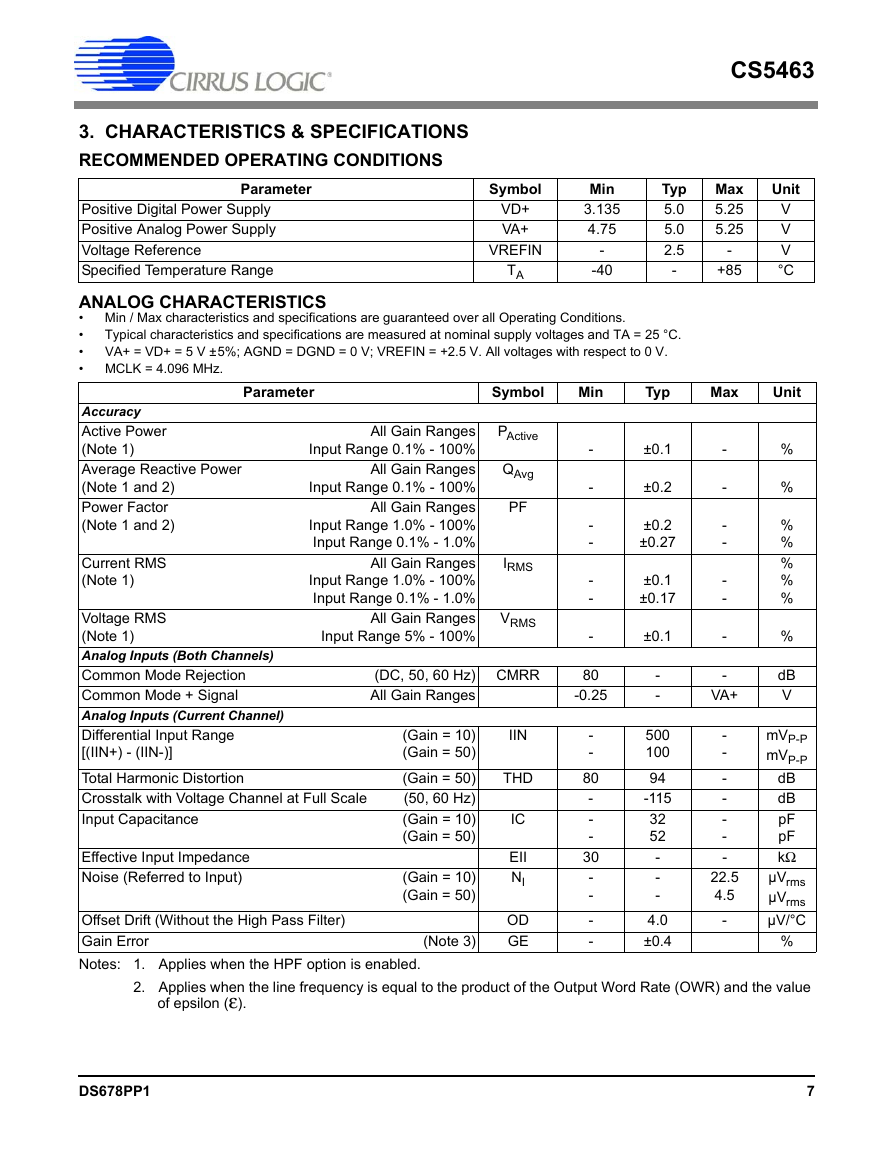

3. CHARACTERISTICS & SPECIFICATIONS

RECOMMENDED OPERATING CONDITIONS

Parameter

Symbol

Positive Digital Power Supply

Positive Analog Power Supply

Voltage Reference

Specified Temperature Range

ANALOG CHARACTERISTICS

• Min / Max characteristics and specifications are guaranteed over all Operating Conditions.

•

•

• MCLK = 4.096 MHz.

Typical characteristics and specifications are measured at nominal supply voltages and TA = 25 °C.

VA+ = VD+ = 5 V ±5%; AGND = DGND = 0 V; VREFIN = +2.5 V. All voltages with respect to 0 V.

VD+

VA+

VREFIN

TA

Min

3.135

4.75

-

-40

CS5463

Typ

5.0

5.0

2.5

-

Max

5.25

5.25

-

+85

Unit

V

V

V

°C

Parameter

Symbol

Min

Typ

Max

Unit

Accuracy

Active Power

(Note 1)

Average Reactive Power

(Note 1 and 2)

Power Factor

(Note 1 and 2)

Current RMS

(Note 1)

Voltage RMS

(Note 1)

Analog Inputs (Both Channels)

Common Mode Rejection

Common Mode + Signal

Analog Inputs (Current Channel)

Differential Input Range

[(IIN+) - (IIN-)]

Total Harmonic Distortion

Crosstalk with Voltage Channel at Full Scale

Input Capacitance

Effective Input Impedance

Noise (Referred to Input)

All Gain Ranges

Input Range 0.1% - 100%

All Gain Ranges

Input Range 0.1% - 100%

All Gain Ranges

Input Range 1.0% - 100%

Input Range 0.1% - 1.0%

All Gain Ranges

Input Range 1.0% - 100%

Input Range 0.1% - 1.0%

All Gain Ranges

Input Range 5% - 100%

PActive

QAvg

PF

IRMS

VRMS

-

-

-

-

-

-

-

(DC, 50, 60 Hz) CMRR

All Gain Ranges

80

-0.25

(Gain = 10)

(Gain = 50)

(Gain = 50)

(50, 60 Hz)

(Gain = 10)

(Gain = 50)

(Gain = 10)

(Gain = 50)

IIN

THD

IC

EII

NI

OD

GE

-

-

80

-

-

-

30

-

-

-

-

±0.1

±0.2

±0.2

±0.27

±0.1

±0.17

±0.1

-

-

500

100

94

-115

32

52

-

-

-

4.0

±0.4

-

-

-

-

-

-

-

-

VA+

-

-

-

-

-

-

-

22.5

4.5

-

%

%

%

%

%

%

%

%

dB

V

mVP-P

mVP-P

dB

dB

pF

pF

kΩ

µVrms

µVrms

µV/°C

%

Offset Drift (Without the High Pass Filter)

Gain Error

Notes: 1. Applies when the HPF option is enabled.

(Note 3)

2. Applies when the line frequency is equal to the product of the Output Word Rate (OWR) and the value

of epsilon (ε).

DS678PP1

7

�

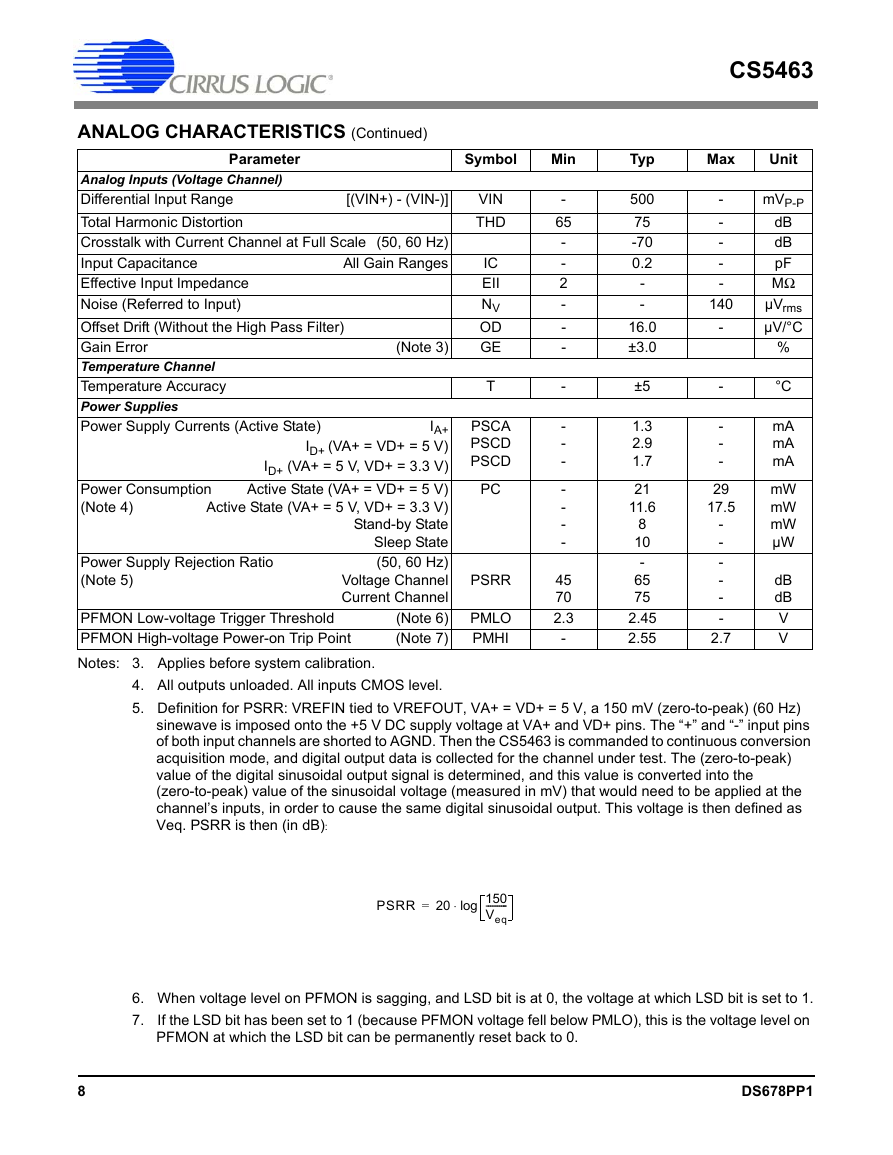

ANALOG CHARACTERISTICS (Continued)

Parameter

Symbol

Min

[(VIN+) - (VIN-)]

Analog Inputs (Voltage Channel)

Differential Input Range

Total Harmonic Distortion

Crosstalk with Current Channel at Full Scale (50, 60 Hz)

Input Capacitance

All Gain Ranges

Effective Input Impedance

Noise (Referred to Input)

Offset Drift (Without the High Pass Filter)

Gain Error

Temperature Channel

Temperature Accuracy

Power Supplies

Power Supply Currents (Active State)

(Note 3)

Power Consumption

(Note 4)

Power Supply Rejection Ratio

(Note 5)

IA+

ID+ (VA+ = VD+ = 5 V)

ID+ (VA+ = 5 V, VD+ = 3.3 V)

Active State (VA+ = VD+ = 5 V)

Active State (VA+ = 5 V, VD+ = 3.3 V)

Stand-by State

Sleep State

(50, 60 Hz)

Voltage Channel

Current Channel

(Note 6)

(Note 7)

CS5463

Max

Unit

-

-

-

-

-

140

-

-

-

-

-

29

17.5

-

-

-

-

-

-

2.7

mVP-P

dB

dB

pF

MΩ

µVrms

µV/°C

%

°C

mA

mA

mA

mW

mW

mW

µW

dB

dB

V

V

Typ

500

75

-70

0.2

-

-

16.0

±3.0

±5

1.3

2.9

1.7

21

11.6

8

10

-

65

75

2.45

2.55

VIN

THD

IC

EII

NV

OD

GE

T

PSCA

PSCD

PSCD

PC

PSRR

PMLO

PMHI

-

65

-

-

2

-

-

-

-

-

-

-

-

-

-

-

45

70

2.3

-

PFMON Low-voltage Trigger Threshold

PFMON High-voltage Power-on Trip Point

Notes: 3. Applies before system calibration.

4. All outputs unloaded. All inputs CMOS level.

5. Definition for PSRR: VREFIN tied to VREFOUT, VA+ = VD+ = 5 V, a 150 mV (zero-to-peak) (60 Hz)

sinewave is imposed onto the +5 V DC supply voltage at VA+ and VD+ pins. The “+” and “-” input pins

of both input channels are shorted to AGND. Then the CS5463 is commanded to continuous conversion

acquisition mode, and digital output data is collected for the channel under test. The (zero-to-peak)

value of the digital sinusoidal output signal is determined, and this value is converted into the

(zero-to-peak) value of the sinusoidal voltage (measured in mV) that would need to be applied at the

channel’s inputs, in order to cause the same digital sinusoidal output. This voltage is then defined as

Veq. PSRR is then (in dB):

PSRR

=

20

log⋅

150

----------

Veq

6. When voltage level on PFMON is sagging, and LSD bit is at 0, the voltage at which LSD bit is set to 1.

If the LSD bit has been set to 1 (because PFMON voltage fell below PMLO), this is the voltage level on

7.

PFMON at which the LSD bit can be permanently reset back to 0.

8

DS678PP1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc