HW-U1-KCU116_REV1_0 Sheet Title Page (1)

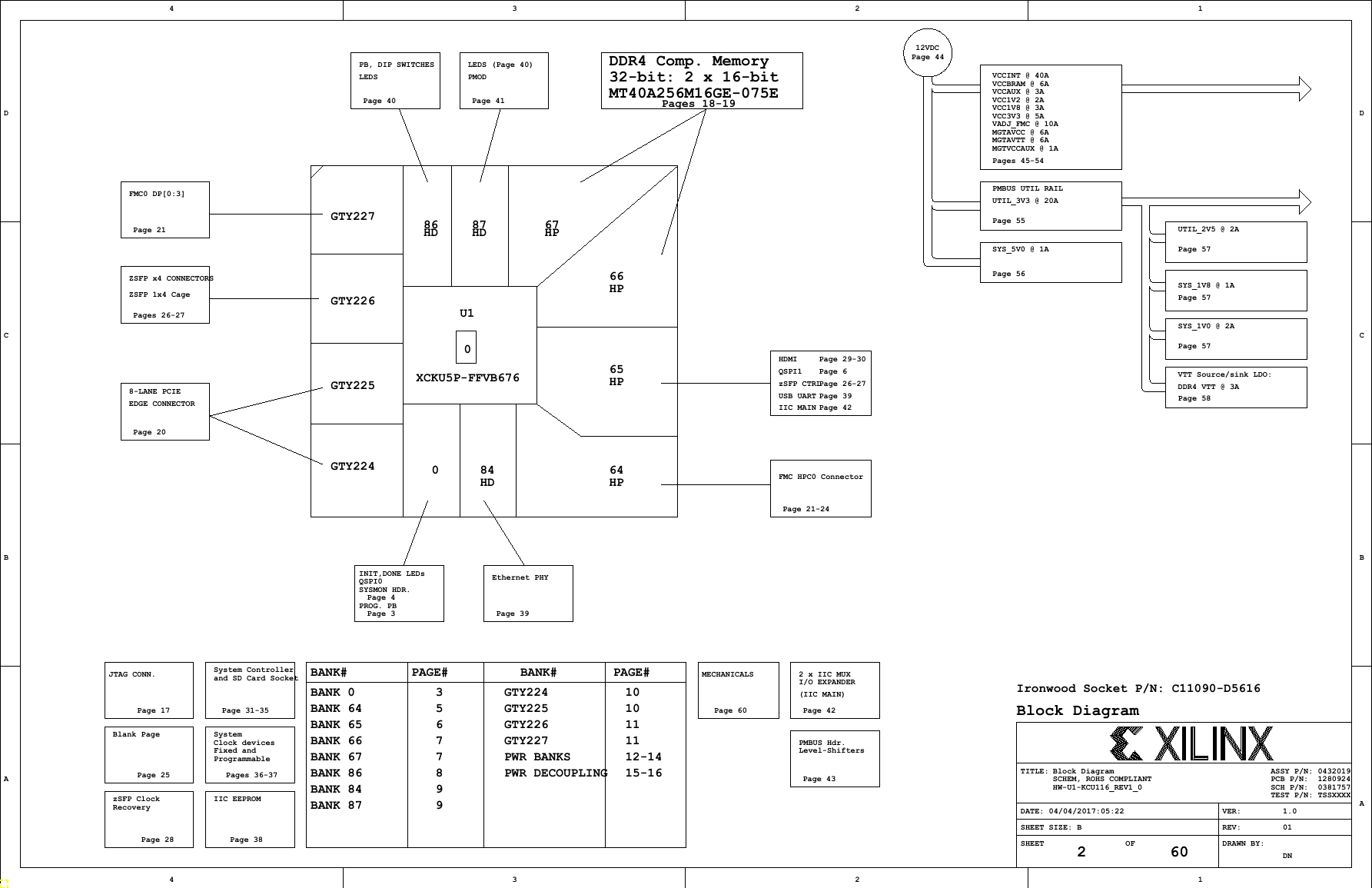

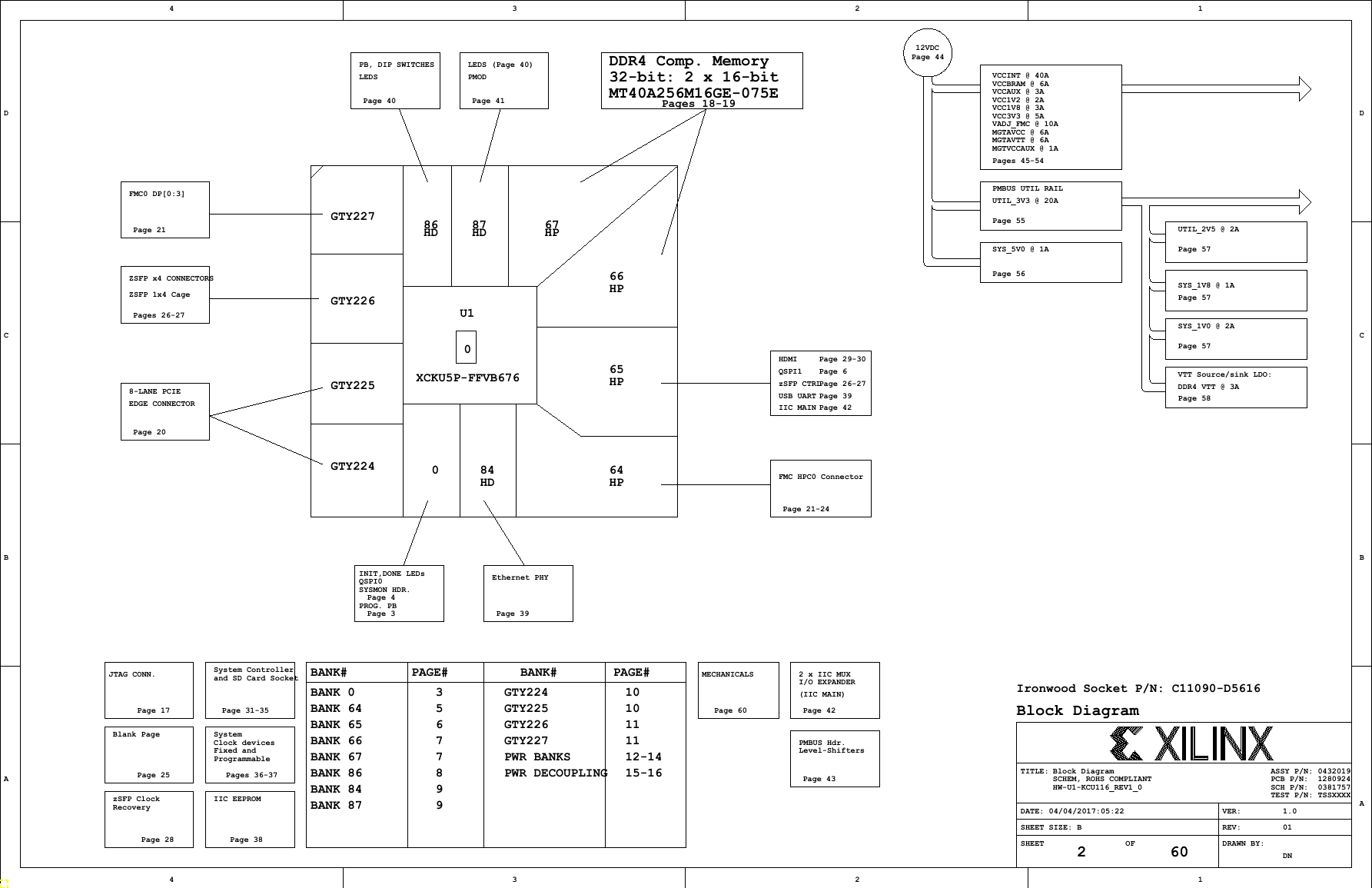

HW-U1-KCU116_REV1_0 Sheet Block Diagram (2)

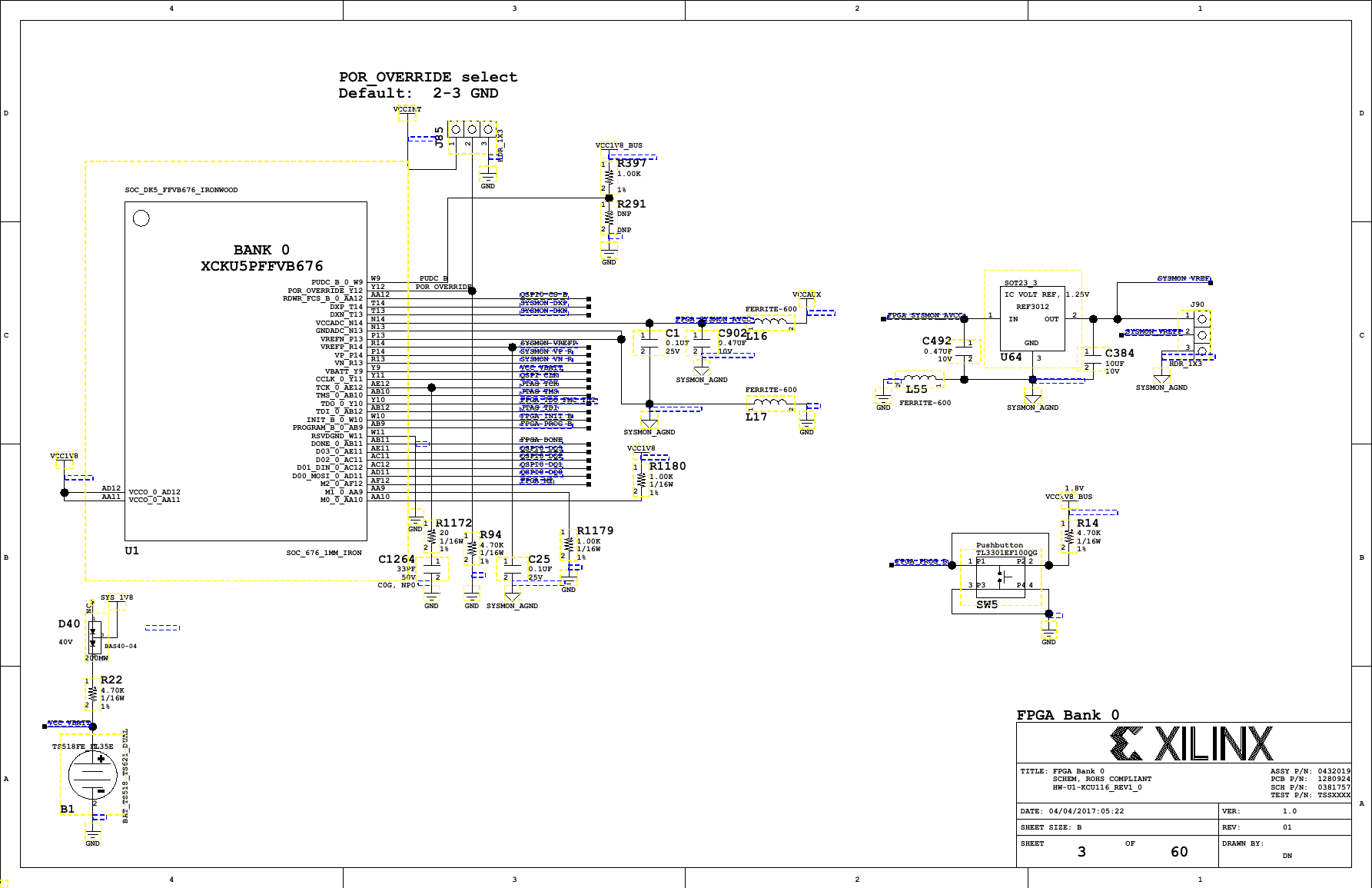

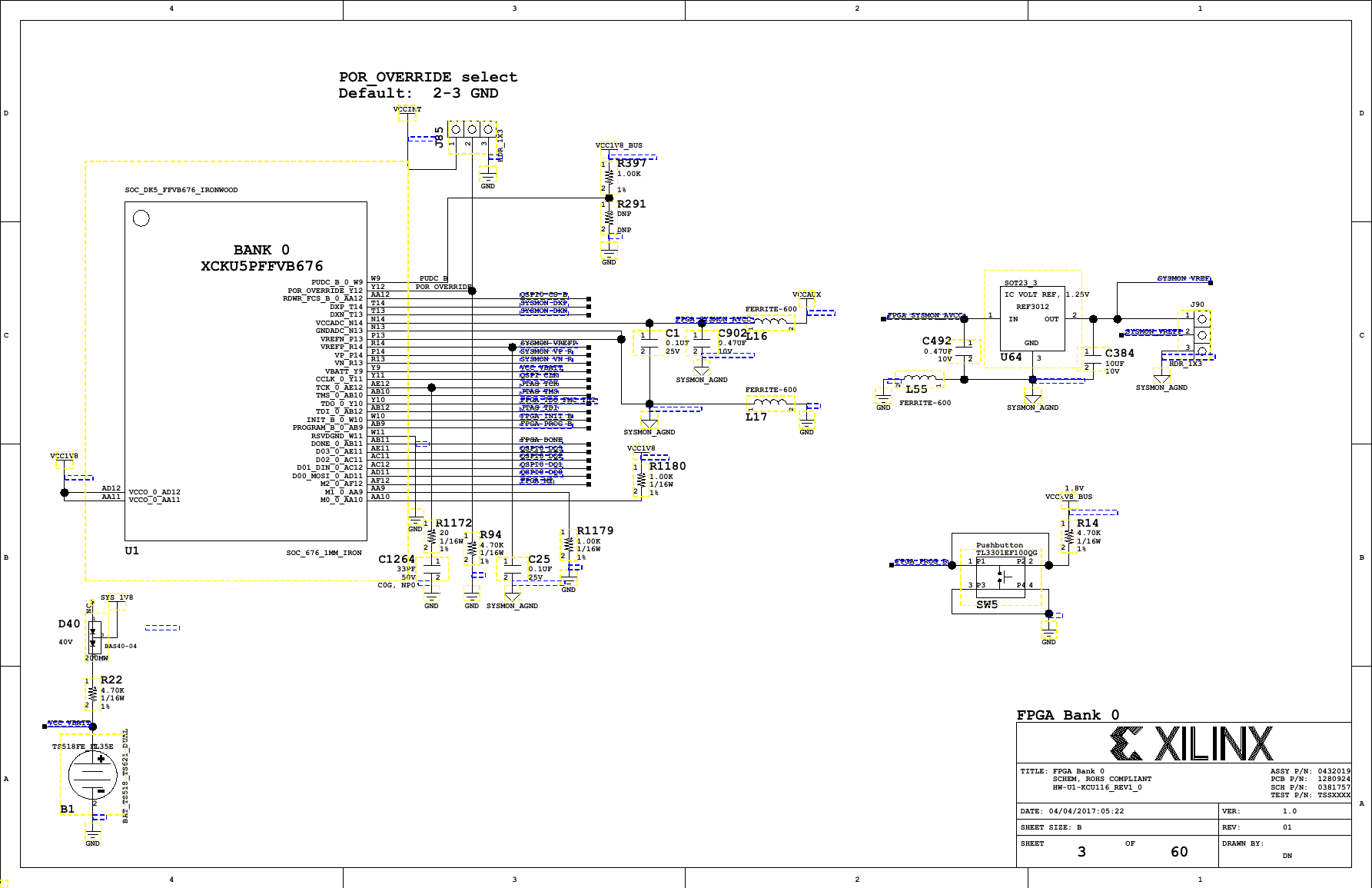

HW-U1-KCU116_REV1_0 Sheet FPGA Bank 0 (3)

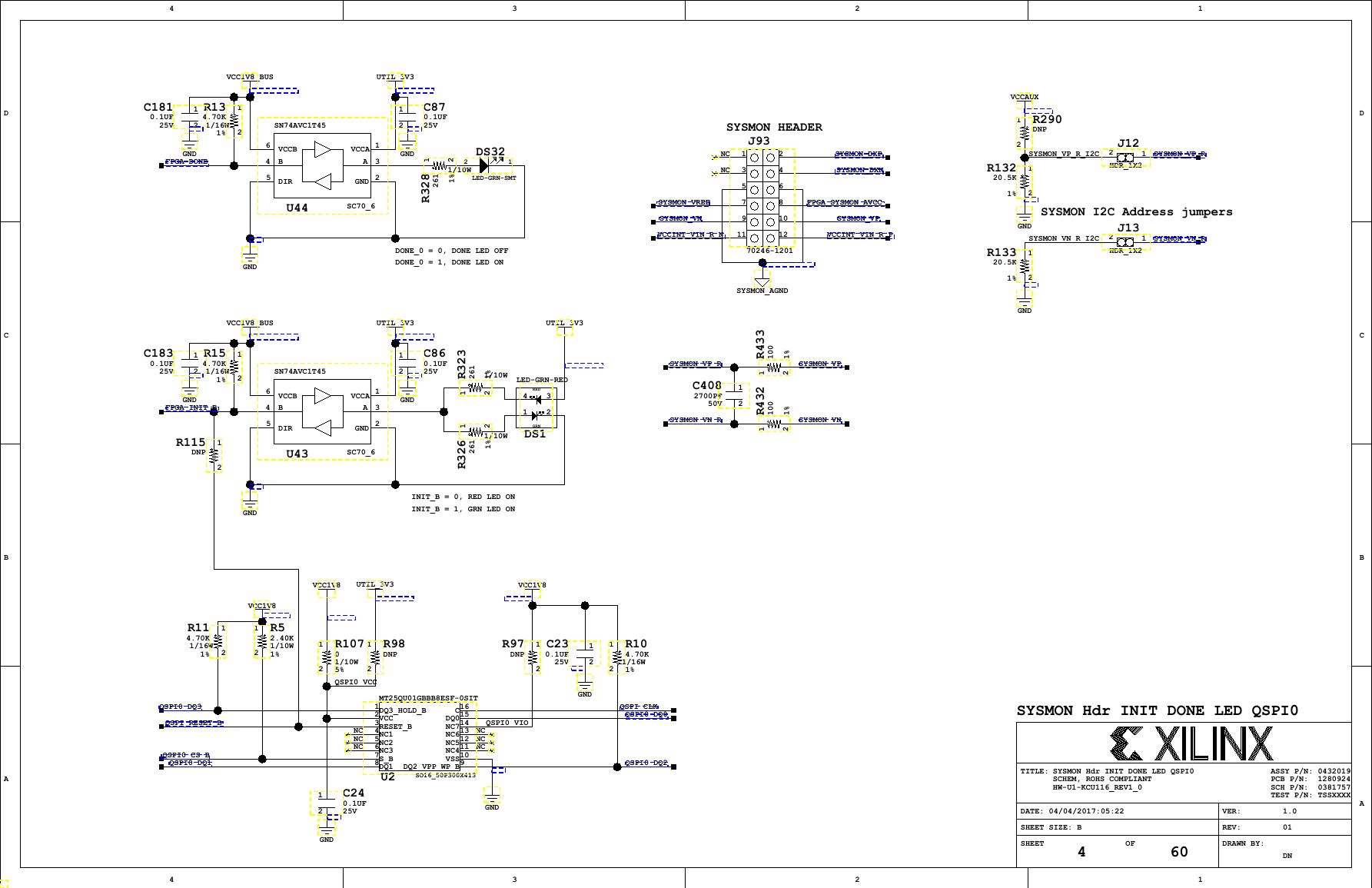

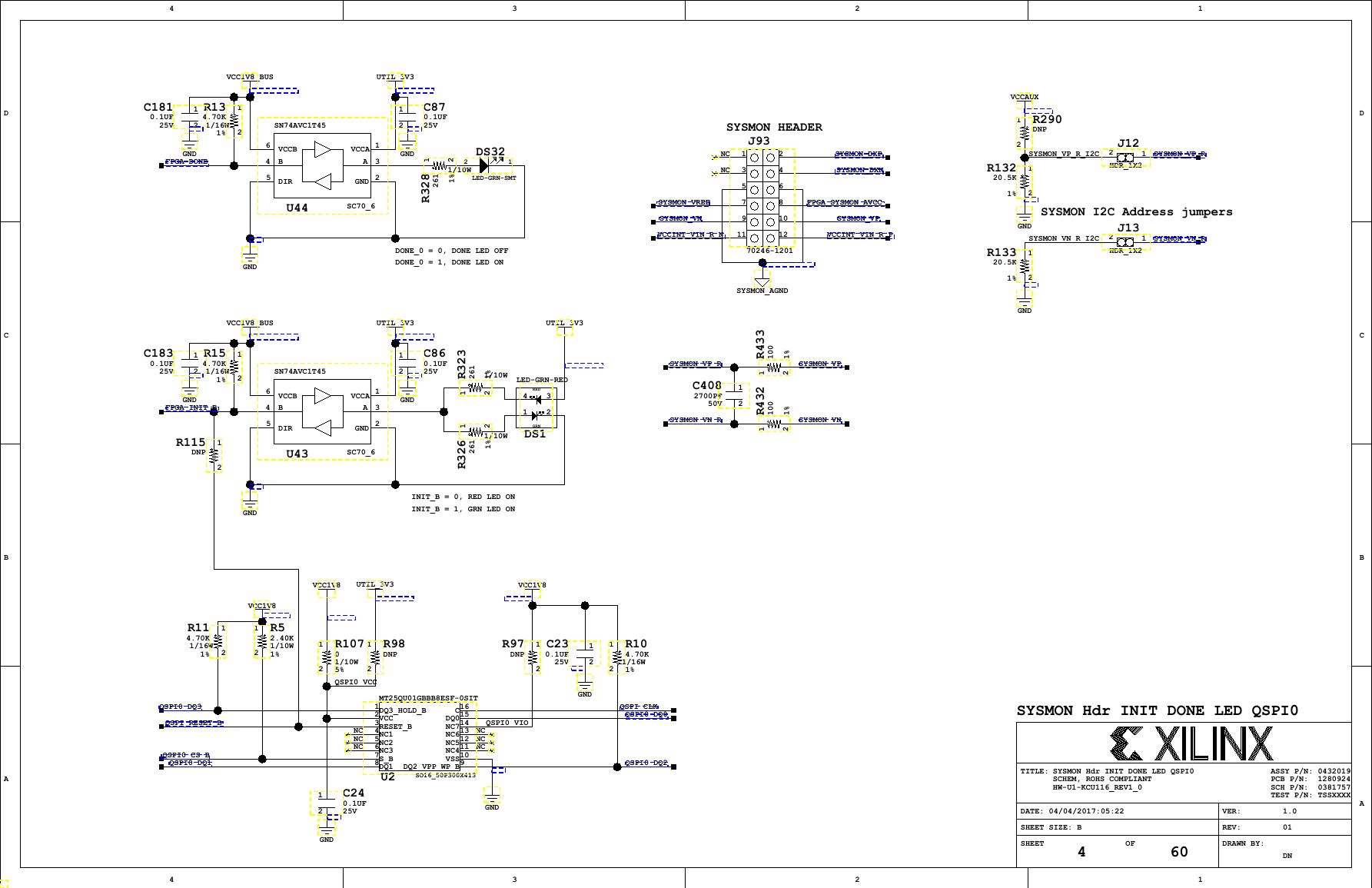

HW-U1-KCU116_REV1_0 Sheet SYSMON Hdr INIT DONE LED QSPI0 (4)

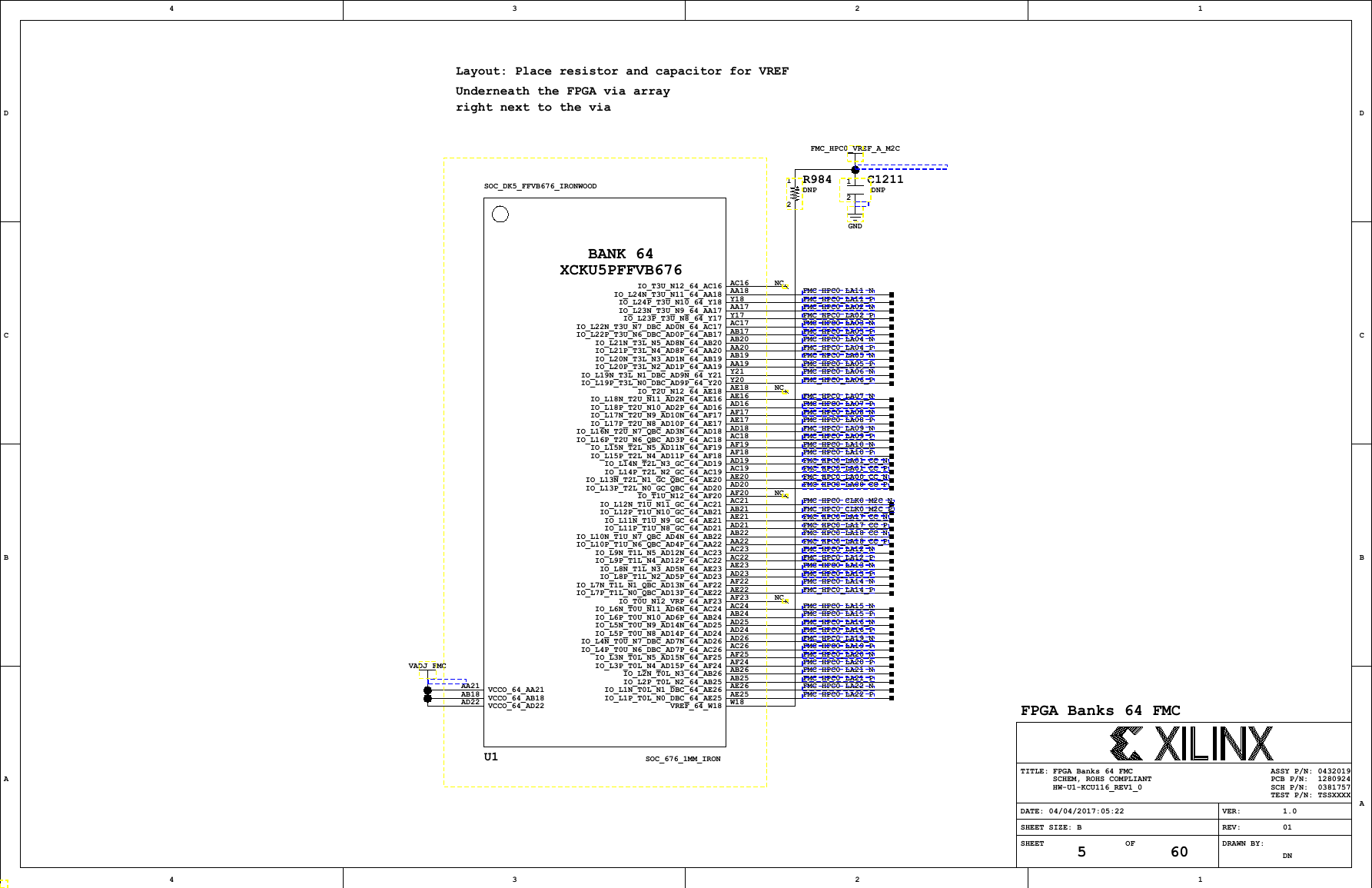

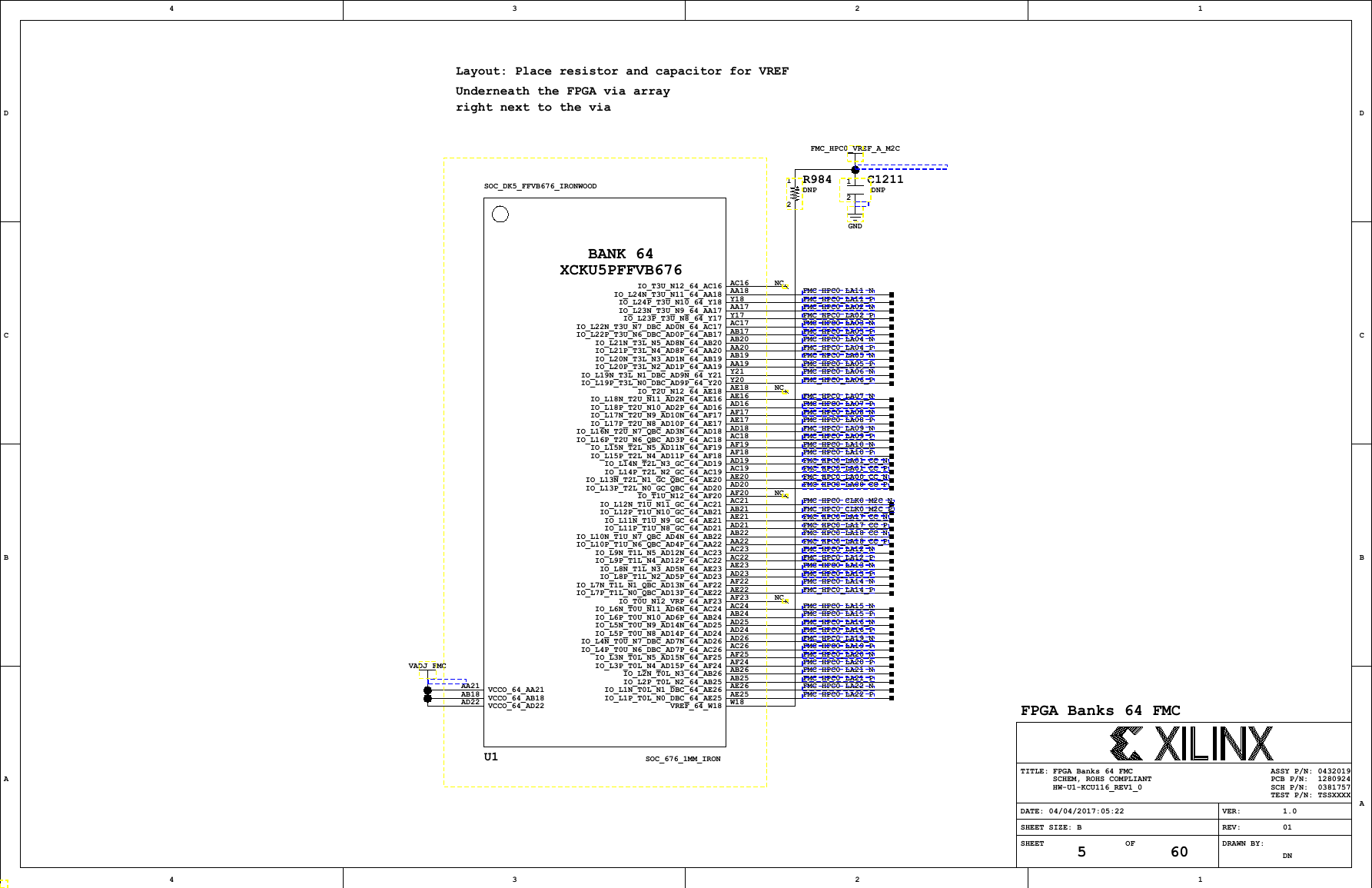

HW-U1-KCU116_REV1_0 Sheet FPGA Banks 64 FMC (5)

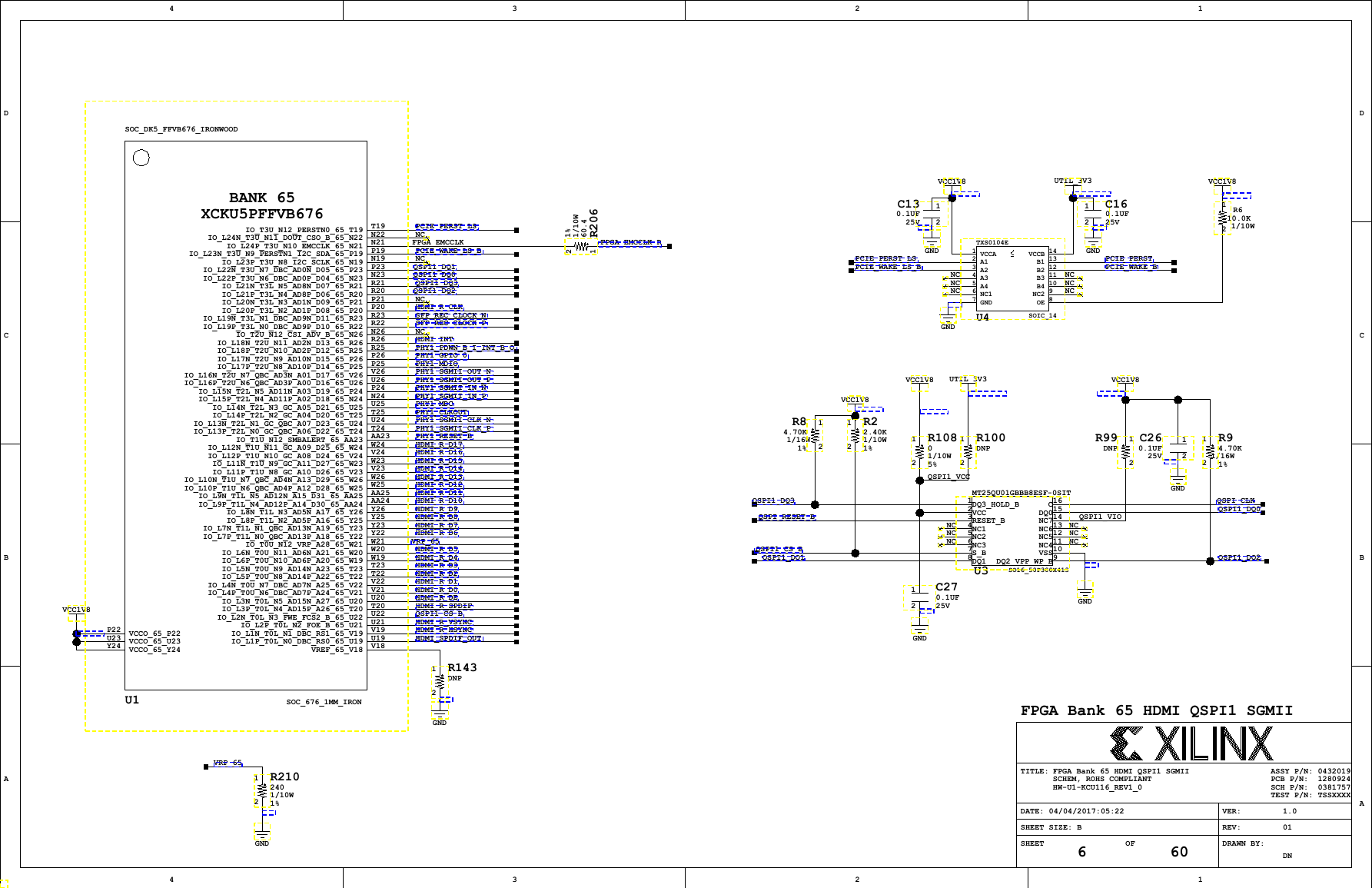

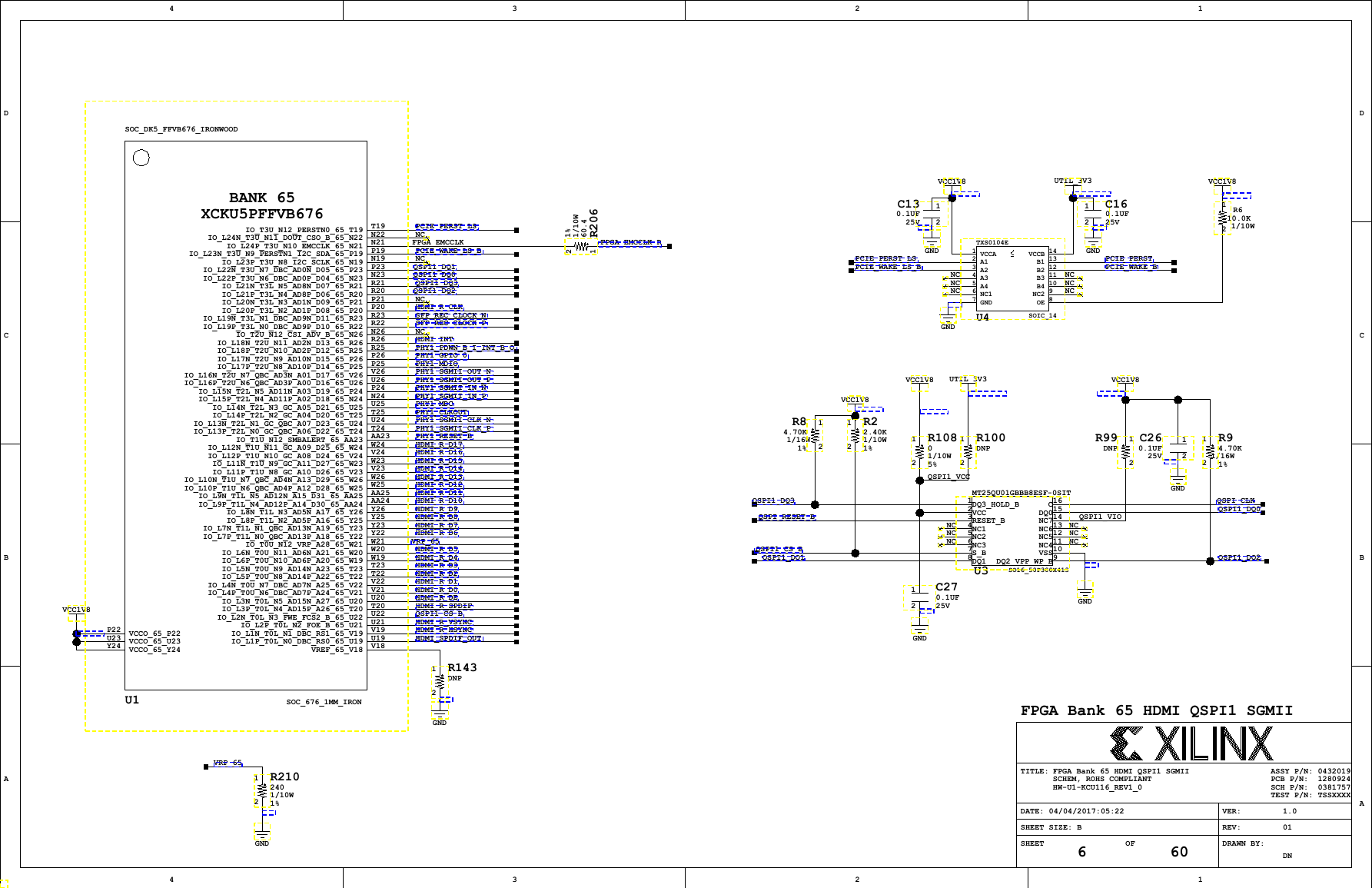

HW-U1-KCU116_REV1_0 Sheet FPGA Bank 65 HDMI QSPI1 SGMII (6)

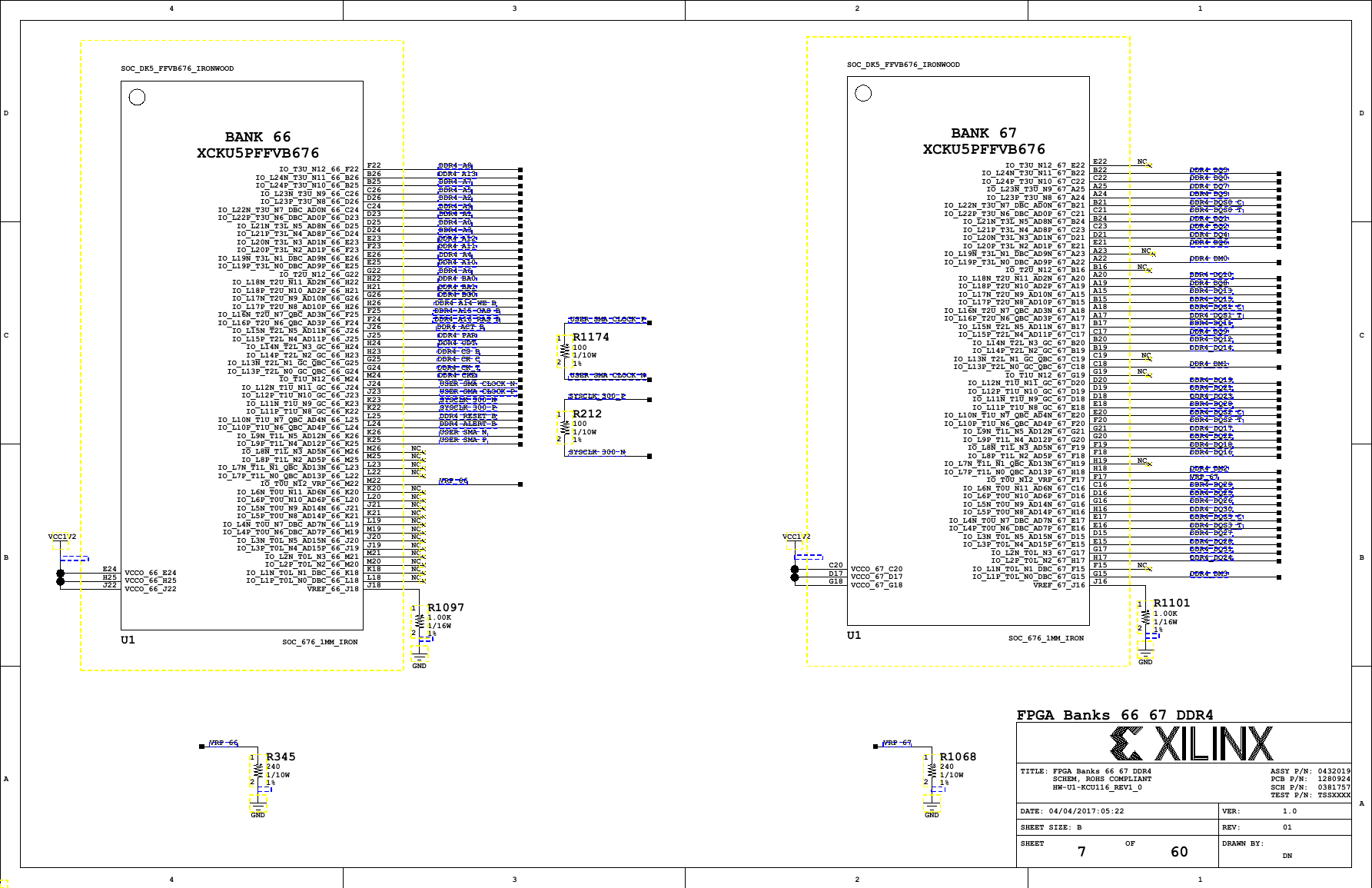

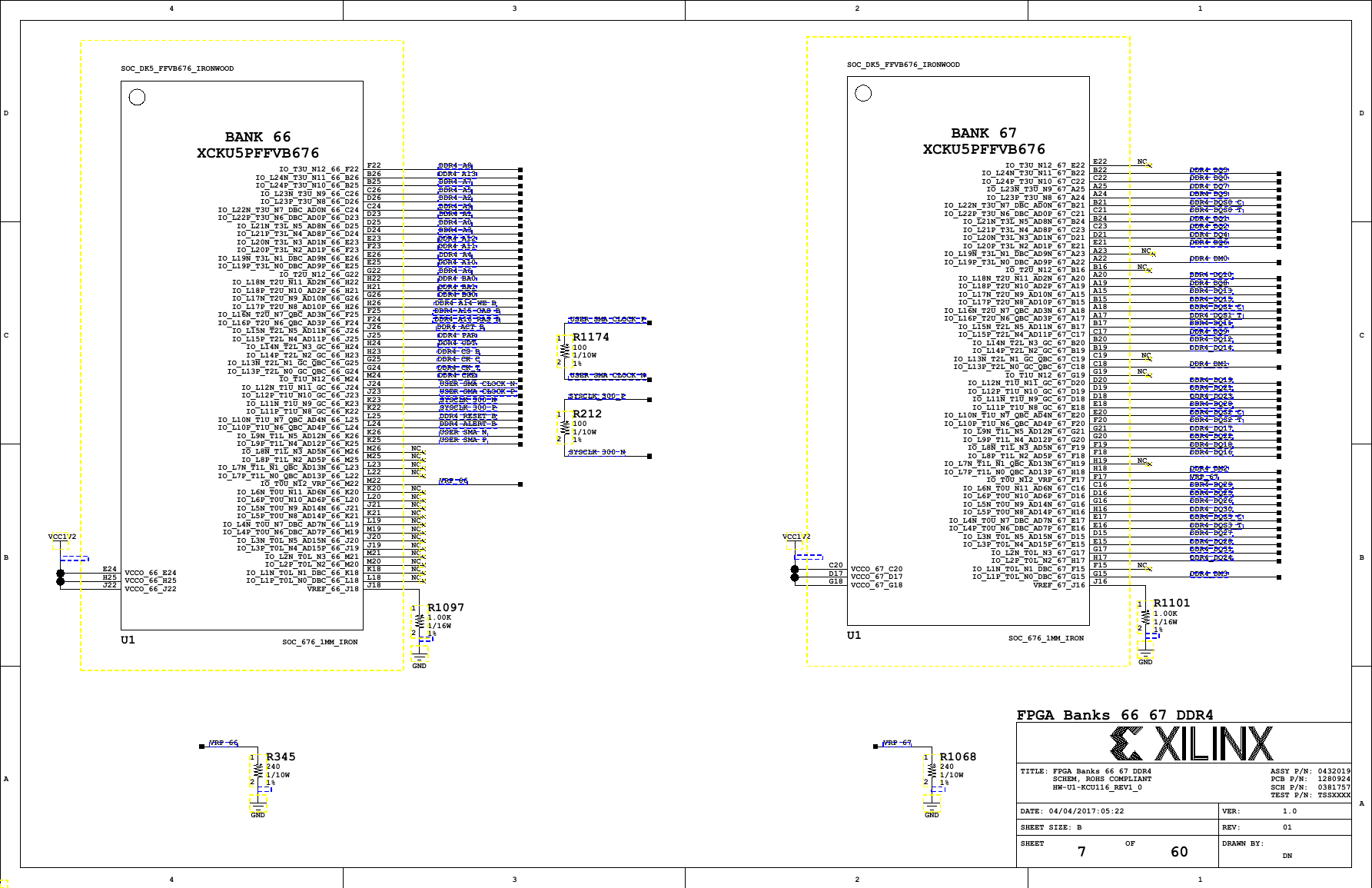

HW-U1-KCU116_REV1_0 Sheet FPGA Banks 66 67 DDR4 (7)

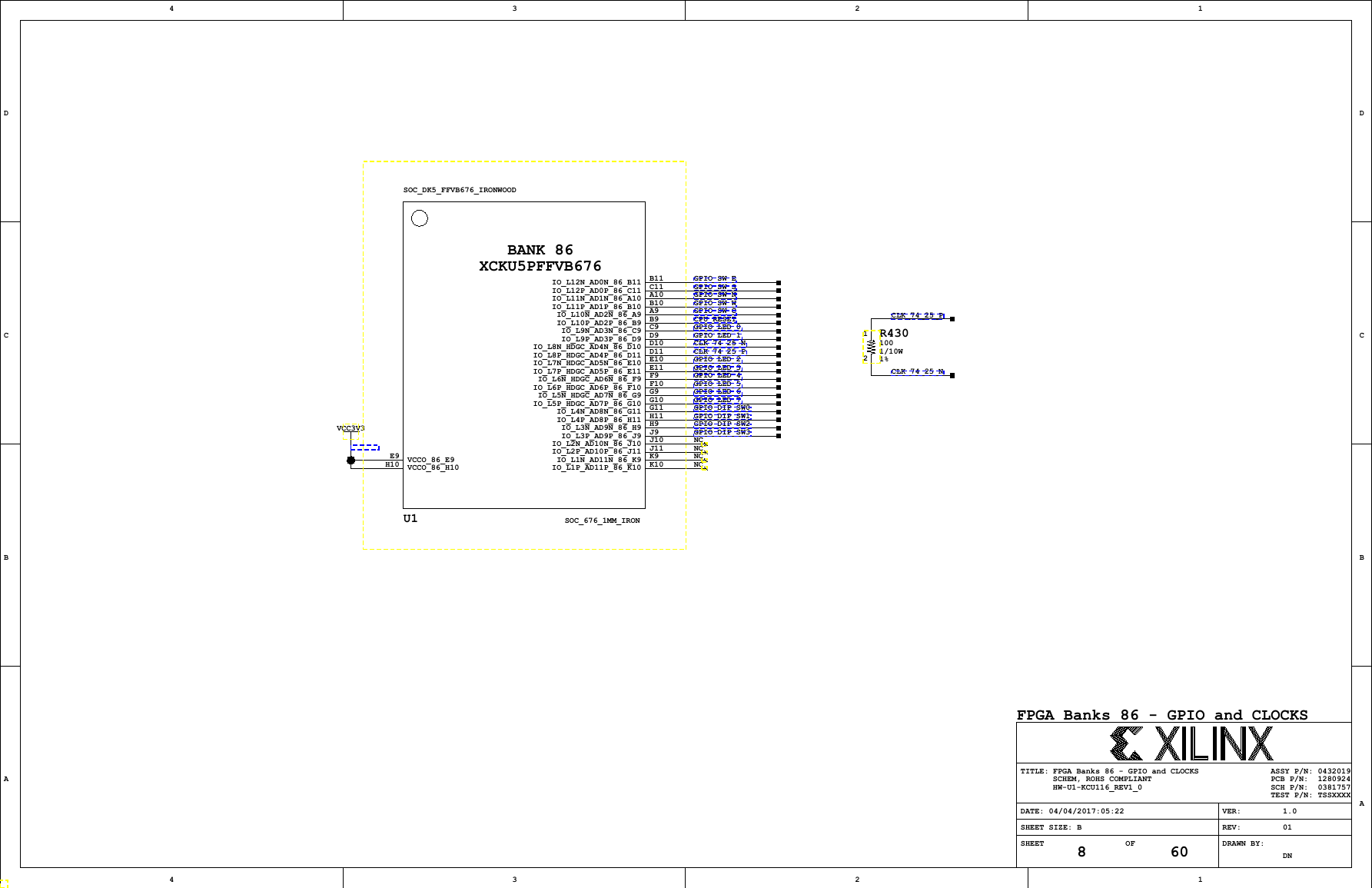

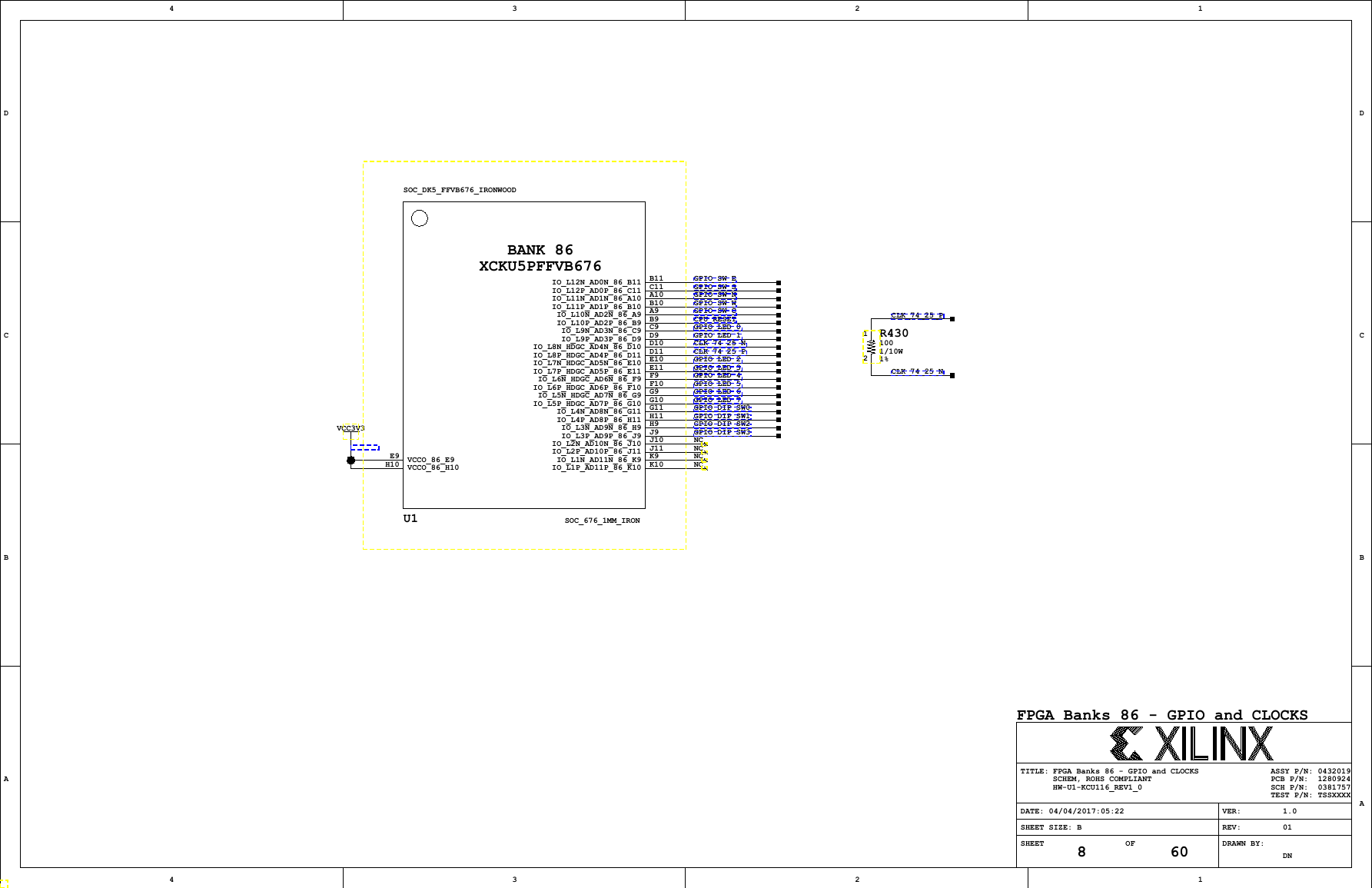

HW-U1-KCU116_REV1_0 Sheet FPGA Banks 86 - GPIO and CLOCKS (8)

HW-U1-KCU116_REV1_0 Sheet FPGA Banks 87 PMOD 84 UART ZSFP SMA (9)

HW-U1-KCU116_REV1_0 Sheet FPGA GTY224 GTY225 PCIE (10)

HW-U1-KCU116_REV1_0 Sheet FPGA GTY226 - ZSFP GTY227 - FMC DP (11)

HW-U1-KCU116_REV1_0 Sheet FPGA Power 1 (12)

HW-U1-KCU116_REV1_0 Sheet FPGA Power 2 (13)

HW-U1-KCU116_REV1_0 Sheet FPGA GND (14)

HW-U1-KCU116_REV1_0 Sheet FPGA Decoupling 1 (15)

HW-U1-KCU116_REV1_0 Sheet FPGA Decoupling 2 (16)

HW-U1-KCU116_REV1_0 Sheet JTAG Headers (17)

HW-U1-KCU116_REV1_0 Sheet DDR4 Data [15-0] (18)

HW-U1-KCU116_REV1_0 Sheet DDR4 Data [31:16] (19)

HW-U1-KCU116_REV1_0 Sheet PCIE EDGE CONNECTOR 8-LANE (20)

HW-U1-KCU116_REV1_0 Sheet FMC+ HPC0 Header Rows A B C D (21)

HW-U1-KCU116_REV1_0 Sheet FMC+ HPC0 Header Rows E F G (22)

HW-U1-KCU116_REV1_0 Sheet FMC+ HPC0 Header Rows H J K (23)

HW-U1-KCU116_REV1_0 Sheet FMC+ HPC0 Header_GND (24)

HW-U1-KCU116_REV1_0 Sheet Blank (25)

HW-U1-KCU116_REV1_0 Sheet ZSFP0 and ZSFP1 (26)

HW-U1-KCU116_REV1_0 Sheet ZSFP2 and ZSPF3 (27)

HW-U1-KCU116_REV1_0 Sheet SFP Clock Recovery (28)

HW-U1-KCU116_REV1_0 Sheet HDMI CODEC (29)

HW-U1-KCU116_REV1_0 Sheet HDMI CONNECTOR (30)

HW-U1-KCU116_REV1_0 Sheet System Controller 1 (31)

HW-U1-KCU116_REV1_0 Sheet System Controller 2 (32)

HW-U1-KCU116_REV1_0 Sheet System Controller 3 (33)

HW-U1-KCU116_REV1_0 Sheet System Controller 4 - Config DIP (34)

HW-U1-KCU116_REV1_0 Sheet Micro SD Card Connector (35)

HW-U1-KCU116_REV1_0 Sheet Fixed Clocks (36)

HW-U1-KCU116_REV1_0 Sheet MGT Programmable Clock - SMAs (37)

HW-U1-KCU116_REV1_0 Sheet Dual USB UART - EEPROM (38)

HW-U1-KCU116_REV1_0 Sheet SGMII 10/100/1000 Ethernet PHY (39)

HW-U1-KCU116_REV1_0 Sheet Buttons - Switches - LEDs (40)

HW-U1-KCU116_REV1_0 Sheet PMODs (41)

HW-U1-KCU116_REV1_0 Sheet I2C MUXes - IO Expander (42)

HW-U1-KCU116_REV1_0 Sheet PMBUS Header - I2C Level Shifters (43)

HW-U1-KCU116_REV1_0 Sheet 12V Power Connectors Switch (44)

HW-U1-KCU116_REV1_0 Sheet VCCINT 40A Regulator (45)

HW-U1-KCU116_REV1_0 Sheet VCCBRAM 6A Regulator (46)

HW-U1-KCU116_REV1_0 Sheet VCCAUX 3A Regulator (47)

HW-U1-KCU116_REV1_0 Sheet VCC1V2 2A Regulator (48)

HW-U1-KCU116_REV1_0 Sheet VCC1V8 3A Regulator (49)

HW-U1-KCU116_REV1_0 Sheet VCC3V3 5A Regulator (50)

HW-U1-KCU116_REV1_0 Sheet VADJ_FMC 10A Regulator (51)

HW-U1-KCU116_REV1_0 Sheet MGTAVCC 6A Regulator (52)

HW-U1-KCU116_REV1_0 Sheet MGTAVTT 6A Regulator (53)

HW-U1-KCU116_REV1_0 Sheet MGTVCCAUX 1A Regulator (54)

HW-U1-KCU116_REV1_0 Sheet UTIL_3V3 20A Regulator (55)

HW-U1-KCU116_REV1_0 Sheet SYS_5V0 1A Regulator (56)

HW-U1-KCU116_REV1_0 Sheet SYS_2V5 SYS_1V8 SYS_1V0 Regulators (57)

HW-U1-KCU116_REV1_0 Sheet DDR4 Termination Supply (58)

HW-U1-KCU116_REV1_0 Sheet Power Status LEDs - Fan Ctrl (59)

HW-U1-KCU116_REV1_0 Sheet Mechanical Components (60)

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc