ARM® Compiler armasm User Guide

Contents

Preface

About this book

Using this book

Glossary

Typographic conventions

Feedback

Feedback on this product

Feedback on content

Other information

1: Overview of the Assembler

1.1: About the ARM Compiler toolchain assemblers

1.2: Key features of the assembler

1.3: How the assembler works

1.4: Directives that can be omitted in pass 2 of the assembler

2: Overview of the ARM Architecture

2.1: About the ARM architecture

2.2: ARM, Thumb, and ThumbEE instruction sets

2.3: Changing between ARM, Thumb, and ThumbEE state

2.4: Processor modes, and privileged and unprivileged software execution

2.5: Processor modes in ARMv6-M and ARMv7-M

2.6: NEON technology

2.7: VFP hardware

2.8: ARM registers

2.9: General-purpose registers

2.10: Register accesses

2.11: Predeclared core register names

2.12: Predeclared extension register names

2.13: Predeclared XScale register names

2.14: Predeclared coprocessor names

2.15: Program Counter

2.16: Application Program Status Register

2.17: The Q flag

2.18: Current Program Status Register

2.19: Saved Program Status Registers

2.20: ARM and Thumb instruction set overview

2.21: Access to the inline barrel shifter

3: Structure of Assembly Language Modules

3.1: Syntax of source lines in assembly language

3.2: Literals

3.3: ELF sections and the AREA directive

3.4: An example ARM assembly language module

4: Writing ARM Assembly Language

4.1: About the Unified Assembler Language

4.2: Register usage in subroutine calls

4.3: Load 32-bit immediates into registers

4.4: Load immediate values using MOV and MVN

4.5: Load 32-bit values to a register using MOV32

4.6: Load 32-bit immediate values to a register using LDR Rd, =const

4.7: Literal pools

4.8: Load addresses into registers

4.9: Load addresses to a register using ADR

4.10: Load addresses to a register using ADRL

4.11: Load addresses to a register using LDR Rd, =label

4.12: Other ways to load and store registers

4.13: Load and store multiple register instructions

4.14: Load and store multiple register instructions in ARM and Thumb

4.15: Stack implementation using LDM and STM

4.16: Stack operations for nested subroutines

4.17: Block copy with LDM and STM

4.18: Memory accesses

4.19: The Read-Modify-Write operation

4.20: Optional hash with immediate constants

4.21: About macros

4.22: Test-and-branch macro example

4.23: Unsigned integer division macro example

4.24: Instruction and directive relocations

4.25: Symbol versions

4.26: Frame directives

4.27: Exception tables and Unwind tables

4.28: Assembly language changes after RVCT v2.1

5: Condition Codes

5.1: Conditional instructions

5.2: Conditional execution in ARM state

5.3: Conditional execution in Thumb state

5.4: Updates to the condition flags

5.5: Condition code suffixes

5.6: Comparison of condition code meanings

5.7: Benefits of using conditional execution

5.8: Illustration of the benefits of using conditional instructions

5.9: Optimization for execution speed

6: Using the Assembler

6.1: Assembler command-line syntax

6.2: Specify command-line options with an environment variable

6.3: Overview of via files

6.4: Via file syntax rules

6.5: Using stdin to input source code to the assembler

6.6: Built-in variables and constants

6.7: Identifying versions of armasm in source code

6.8: Diagnostic messages

6.9: Interlocks diagnostics

6.10: Automatic IT block generation

6.11: Thumb branch target alignment

6.12: Thumb code size diagnostics

6.13: ARM and Thumb instruction portability diagnostics

6.14: Instruction width

6.15: Two pass assembler diagnostics

6.16: Conditional assembly

6.17: Using the C preprocessor

6.18: Address alignment

6.19: Instruction width selection in Thumb

7: Symbols, Literals, Expressions, and Operators

7.1: Symbol naming rules

7.2: Variables

7.3: Numeric constants

7.4: Assembly time substitution of variables

7.5: Register-relative and PC-relative expressions

7.6: Labels

7.7: Labels for PC-relative addresses

7.8: Labels for register-relative addresses

7.9: Labels for absolute addresses

7.10: Numeric local labels

7.11: Syntax of numeric local labels

7.12: String expressions

7.13: String literals

7.14: Numeric expressions

7.15: Syntax of numeric literals

7.16: Syntax of floating-point literals

7.17: Logical expressions

7.18: Logical literals

7.19: Unary operators

7.20: Binary operators

7.21: Multiplicative operators

7.22: String manipulation operators

7.23: Shift operators

7.24: Addition, subtraction, and logical operators

7.25: Relational operators

7.26: Boolean operators

7.27: Operator precedence

7.28: Difference between operator precedence in assembly language and C

8: NEON and VFP Programming

8.1: Architecture support for NEON and VFP

8.2: Half-precision extension

8.3: Fused Multiply-Add extension

8.4: Extension register bank mapping

8.5: NEON views of the register bank

8.6: VFP views of the extension register bank

8.7: Load values to VFP and NEON registers

8.8: Conditional execution of NEON and VFP instructions

8.9: Floating-point exceptions

8.10: NEON and VFP data types

8.11: NEON vectors

8.12: Normal, long, wide, and narrow NEON operation

8.13: Saturating NEON instructions

8.14: NEON scalars

8.15: Extended notation

8.16: Polynomial arithmetic over {0,1}

8.17: NEON and VFP system registers

8.18: Flush-to-zero mode

8.19: When to use flush-to-zero mode

8.20: The effects of using flush-to-zero mode

8.21: Operations not affected by flush-to-zero mode

8.22: VFP vector mode

8.23: Vectors in the VFP extension register bank

8.24: VFP vector wrap-around

8.25: VFP vector stride

8.26: Restriction on vector length

8.27: Control of scalar, vector, and mixed operations

8.28: Overview of VFP directives and vector notation

8.29: Pre-UAL VFP syntax and mnemonics

8.30: Vector notation

8.31: VFPASSERT SCALAR

8.32: VFPASSERT VECTOR

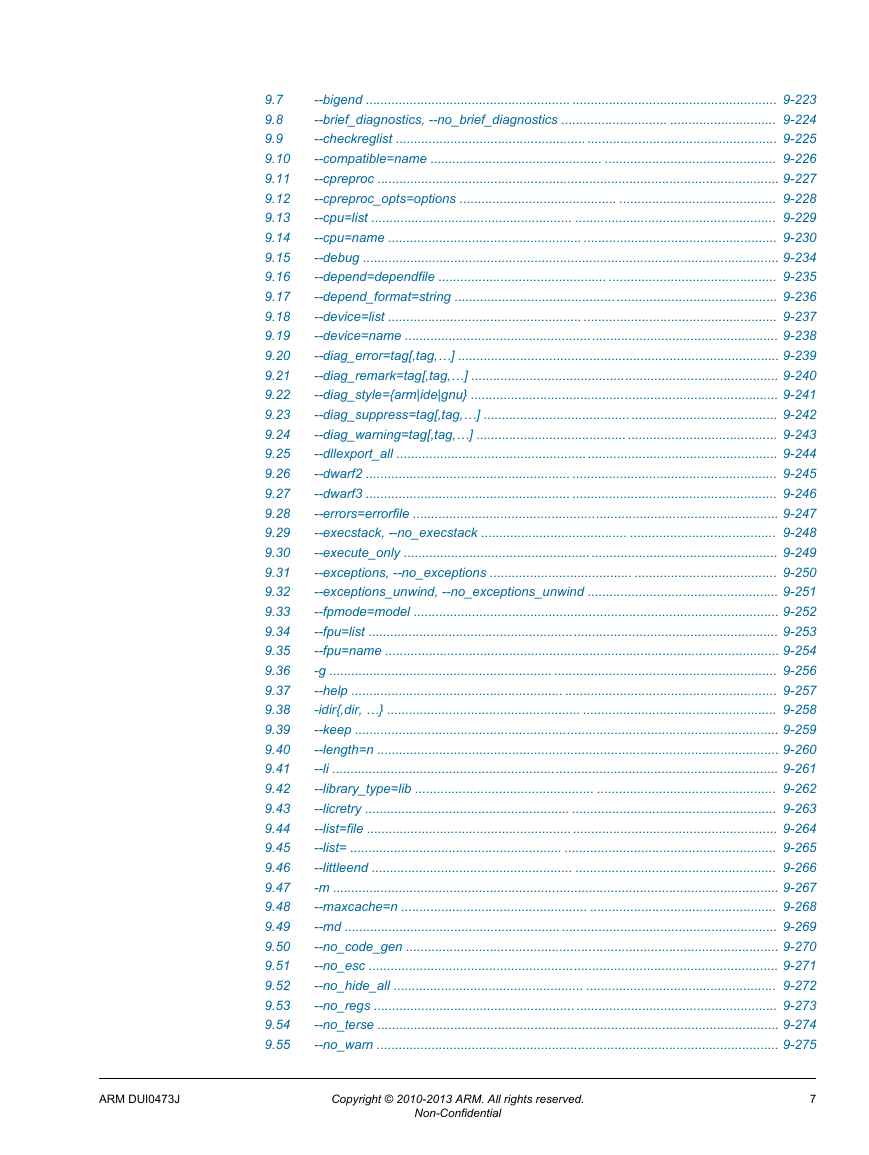

9: Assembler Command-line Options

9.1: --16

9.2: --32

9.3: --apcs=qualifier…qualifier

9.4: --arm

9.5: --arm_only

9.6: --bi

9.7: --bigend

9.8: --brief_diagnostics, --no_brief_diagnostics

9.9: --checkreglist

9.10: --compatible=name

9.11: --cpreproc

9.12: --cpreproc_opts=options

9.13: --cpu=list

9.14: --cpu=name

9.15: --debug

9.16: --depend=dependfile

9.17: --depend_format=string

9.18: --device=list

9.19: --device=name

9.20: --diag_error=tag[,tag,…]

9.21: --diag_remark=tag[,tag,…]

9.22: --diag_style={arm|ide|gnu}

9.23: --diag_suppress=tag[,tag,…]

9.24: --diag_warning=tag[,tag,…]

9.25: --dllexport_all

9.26: --dwarf2

9.27: --dwarf3

9.28: --errors=errorfile

9.29: --execstack, --no_execstack

9.30: --execute_only

9.31: --exceptions, --no_exceptions

9.32: --exceptions_unwind, --no_exceptions_unwind

9.33: --fpmode=model

9.34: --fpu=list

9.35: --fpu=name

9.36: -g

9.37: --help

9.38: -idir{,dir, …}

9.39: --keep

9.40: --length=n

9.41: --li

9.42: --library_type=lib

9.43: --licretry

9.44: --list=file

9.45: --list=

9.46: --littleend

9.47: -m

9.48: --maxcache=n

9.49: --md

9.50: --no_code_gen

9.51: --no_esc

9.52: --no_hide_all

9.53: --no_regs

9.54: --no_terse

9.55: --no_warn

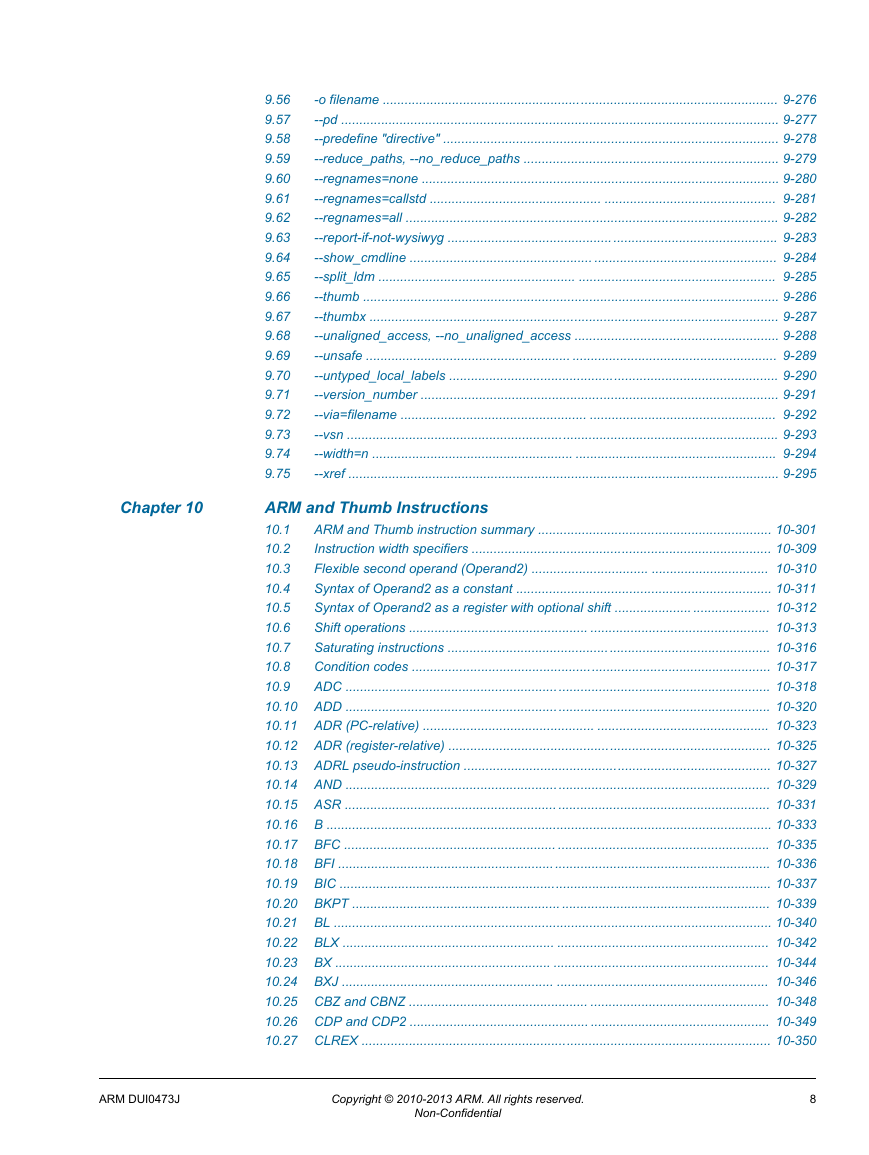

9.56: -o filename

9.57: --pd

9.58: --predefine "directive"

9.59: --reduce_paths, --no_reduce_paths

9.60: --regnames=none

9.61: --regnames=callstd

9.62: --regnames=all

9.63: --report-if-not-wysiwyg

9.64: --show_cmdline

9.65: --split_ldm

9.66: --thumb

9.67: --thumbx

9.68: --unaligned_access, --no_unaligned_access

9.69: --unsafe

9.70: --untyped_local_labels

9.71: --version_number

9.72: --via=filename

9.73: --vsn

9.74: --width=n

9.75: --xref

10: ARM and Thumb Instructions

10.1: ARM and Thumb instruction summary

10.2: Instruction width specifiers

10.3: Flexible second operand (Operand2)

10.4: Syntax of Operand2 as a constant

10.5: Syntax of Operand2 as a register with optional shift

10.6: Shift operations

10.7: Saturating instructions

10.8: Condition codes

10.9: ADC

10.10: ADD

10.11: ADR (PC-relative)

10.12: ADR (register-relative)

10.13: ADRL pseudo-instruction

10.14: AND

10.15: ASR

10.16: B

10.17: BFC

10.18: BFI

10.19: BIC

10.20: BKPT

10.21: BL

10.22: BLX

10.23: BX

10.24: BXJ

10.25: CBZ and CBNZ

10.26: CDP and CDP2

10.27: CLREX

10.28: CLZ

10.29: CMP and CMN

10.30: CPS

10.31: CPY pseudo-instruction

10.32: DBG

10.33: DMB

10.34: DSB

10.35: EOR

10.36: ERET

10.37: ISB

10.38: IT

10.39: LDC and LDC2

10.40: LDM

10.41: LDR (immediate offset)

10.42: LDR (PC-relative)

10.43: LDR (register offset)

10.44: LDR (register-relative)

10.45: LDR pseudo-instruction

10.46: LDR, unprivileged

10.47: LDREX

10.48: LSL

10.49: LSR

10.50: MAR

10.51: MCR and MCR2

10.52: MCRR and MCRR2

10.53: MIA, MIAPH, and MIAxy

10.54: MLA

10.55: MLS

10.56: MOV

10.57: MOV32 pseudo-instruction

10.58: MOVT

10.59: MRA

10.60: MRC and MRC2

10.61: MRRC and MRRC2

10.62: MRS (PSR to general-purpose register)

10.63: MRS (system coprocessor register to ARM register)

10.64: MSR (ARM register to system coprocessor register)

10.65: MSR (general-purpose register to PSR)

10.66: MUL

10.67: MVN

10.68: NEG pseudo-instruction

10.69: NOP

10.70: ORN (Thumb only)

10.71: ORR

10.72: PKHBT and PKHTB

10.73: PLD, PLDW, and PLI

10.74: POP

10.75: PUSH

10.76: QADD

10.77: QADD8

10.78: QADD16

10.79: QASX

10.80: QDADD

10.81: QDSUB

10.82: QSAX

10.83: QSUB

10.84: QSUB8

10.85: QSUB16

10.86: RBIT

10.87: REV

10.88: REV16

10.89: REVSH

10.90: RFE

10.91: ROR

10.92: RRX

10.93: RSB

10.94: RSC

10.95: SADD8

10.96: SADD16

10.97: SASX

10.98: SBC

10.99: SBFX

10.100: SDIV

10.101: SEL

10.102: SETEND

10.103: SEV

10.104: SHADD8

10.105: SHADD16

10.106: SHASX

10.107: SHSAX

10.108: SHSUB8

10.109: SHSUB16

10.110: SMC

10.111: SMLAxy

10.112: SMLAD

10.113: SMLAL

10.114: SMLALD

10.115: SMLALxy

10.116: SMLAWy

10.117: SMLSD

10.118: SMLSLD

10.119: SMMLA

10.120: SMMLS

10.121: SMMUL

10.122: SMUAD

10.123: SMULxy

10.124: SMULL

10.125: SMULWy

10.126: SMUSD

10.127: SRS

10.128: SSAT

10.129: SSAT16

10.130: SSAX

10.131: SSUB8

10.132: SSUB16

10.133: STC and STC2

10.134: STM

10.135: STR (immediate offset)

10.136: STR (register offset)

10.137: STR, unprivileged

10.138: STREX

10.139: SUB

10.140: SUBS pc, lr

10.141: SVC

10.142: SWP and SWPB

10.143: SXTAB

10.144: SXTAB16

10.145: SXTAH

10.146: SXTB

10.147: SXTB16

10.148: SXTH

10.149: SYS

10.150: TBB and TBH

10.151: TEQ

10.152: TST

10.153: UADD8

10.154: UADD16

10.155: UASX

10.156: UBFX

10.157: UDIV

10.158: UHADD8

10.159: UHADD16

10.160: UHASX

10.161: UHSAX

10.162: UHSUB8

10.163: UHSUB16

10.164: UMAAL

10.165: UMLAL

10.166: UMULL

10.167: UND pseudo-instruction

10.168: UQADD8

10.169: UQADD16

10.170: UQASX

10.171: UQSAX

10.172: UQSUB8

10.173: UQSUB16

10.174: USAD8

10.175: USADA8

10.176: USAT

10.177: USAT16

10.178: USAX

10.179: USUB8

10.180: USUB16

10.181: UXTAB

10.182: UXTAB16

10.183: UXTAH

10.184: UXTB

10.185: UXTB16

10.186: UXTH

10.187: WFE

10.188: WFI

10.189: YIELD

11: ThumbEE Instructions

11.1: ThumbEE instruction differences

11.2: Instruction summary

11.3: CHKA

11.4: ENTERX and LEAVEX

11.5: HB, HBL, HBLP, and HBP

12: NEON and VFP Instructions

12.1: Summary of NEON instructions

12.2: Summary of shared NEON and VFP instructions

12.3: Summary of VFP instructions

12.4: Interleaving provided by load and store element and structure instructions

12.5: Alignment restrictions in load and store element and structure instructions

12.6: VABA and VABAL

12.7: VABD and VABDL

12.8: VABS

12.9: VABS (floating-point)

12.10: VACLE, VACLT, VACGE and VACGT

12.11: VADD (floating-point)

12.12: VADD

12.13: VADDHN

12.14: VADDL and VADDW

12.15: VAND (immediate)

12.16: VAND (register)

12.17: VBIC (immediate)

12.18: VBIC (register)

12.19: VBIF

12.20: VBIT

12.21: VBSL

12.22: VCEQ (immediate #0)

12.23: VCEQ (register)

12.24: VCGE (immediate #0)

12.25: VCGE (register)

12.26: VCGT (immediate #0)

12.27: VCGT (register)

12.28: VCLE (immediate #0)

12.29: VCLE (register)

12.30: VCLS

12.31: VCLT (immediate #0)

12.32: VCLT (register)

12.33: VCLZ

12.34: VCMP, VCMPE

12.35: VCNT

12.36: VCVT (between fixed-point or integer, and floating-point)

12.37: VCVT (between half-precision and single-precision floating-point)

12.38: VCVT (between single-precision and double-precision)

12.39: VCVT (between floating-point and integer)

12.40: VCVT (between floating-point and fixed-point)

12.41: VCVTB, VCVTT (half-precision extension)

12.42: VDIV

12.43: VDUP

12.44: VEOR

12.45: VEXT

12.46: VFMA, VFMS

12.47: VFMA, VFMS, VFNMA, VFNMS

12.48: VHADD

12.49: VHSUB

12.50: VLDn (single n-element structure to one lane)

12.51: VLDn (single n-element structure to all lanes)

12.52: VLDn (multiple n-element structures)

12.53: VLDM

12.54: VLDR

12.55: VLDR (post-increment and pre-decrement)

12.56: VLDR pseudo-instruction

12.57: VMAX and VMIN

12.58: VMLA

12.59: VMLA (by scalar)

12.60: VMLA (floating-point)

12.61: VMLAL (by scalar)

12.62: VMLAL

12.63: VMLS (by scalar)

12.64: VMLS

12.65: VMLS (floating-point)

12.66: VMLSL

12.67: VMLSL (by scalar)

12.68: VMOV (floating-point)

12.69: VMOV (immediate)

12.70: VMOV (register)

12.71: VMOV (between one ARM register and single precision VFP)

12.72: VMOV (between two ARM registers and an extension register)

12.73: VMOV (between an ARM register and a NEON scalar)

12.74: VMOVL

12.75: VMOVN

12.76: VMOV2

12.77: VMRS

12.78: VMSR

12.79: VMUL

12.80: VMUL (floating-point)

12.81: VMUL (by scalar)

12.82: VMULL

12.83: VMULL (by scalar)

12.84: VMVN (register)

12.85: VMVN (immediate)

12.86: VNEG (floating-point)

12.87: VNEG

12.88: VNMLA (floating-point)

12.89: VNMLS (floating-point)

12.90: VNMUL (floating-point)

12.91: VORN (register)

12.92: VORN (immediate)

12.93: VORR (register)

12.94: VORR (immediate)

12.95: VPADAL

12.96: VPADD

12.97: VPADDL

12.98: VPMAX and VPMIN

12.99: VPOP

12.100: VPUSH

12.101: VQABS

12.102: VQADD

12.103: VQDMLAL and VQDMLSL (by vector or by scalar)

12.104: VQDMULH (by vector or by scalar)

12.105: VQDMULL (by vector or by scalar)

12.106: VQMOVN and VQMOVUN

12.107: VQNEG

12.108: VQRDMULH (by vector or by scalar)

12.109: VQRSHL (by signed variable)

12.110: VQRSHRN and VQRSHRUN (by immediate)

12.111: VQSHL (by signed variable)

12.112: VQSHL and VQSHLU (by immediate)

12.113: VQSHRN and VQSHRUN (by immediate)

12.114: VQSUB

12.115: VRADDHN

12.116: VRECPE

12.117: VRECPS

12.118: VREV16, VREV32, and VREV64

12.119: VRHADD

12.120: VRSHL (by signed variable)

12.121: VRSHR (by immediate)

12.122: VRSHRN (by immediate)

12.123: VRSQRTE

12.124: VRSQRTS

12.125: VRSRA (by immediate)

12.126: VRSUBHN

12.127: VSHL (by immediate)

12.128: VSHL (by signed variable)

12.129: VSHLL (by immediate)

12.130: VSHR (by immediate)

12.131: VSHRN (by immediate)

12.132: VSLI

12.133: VSQRT

12.134: VSRA (by immediate)

12.135: VSRI

12.136: VSTM

12.137: VSTn (multiple n-element structures)

12.138: VSTn (single n-element structure to one lane)

12.139: VSTR

12.140: VSTR (post-increment and pre-decrement)

12.141: VSUB (floating-point)

12.142: VSUB

12.143: VSUBHN

12.144: VSUBL and VSUBW

12.145: VSWP

12.146: VTBL and VTBX

12.147: VTRN

12.148: VTST

12.149: VUZP

12.150: VZIP

13: Wireless MMX Technology Instructions

13.1: About Wireless MMX Technology instructions

13.2: WRN and WCN directives to support Wireless MMX Technology

13.3: Frame directives and Wireless MMX Technology

13.4: Wireless MMX load and store instructions

13.5: Wireless MMX Technology and XScale instructions

13.6: Wireless MMX instructions

13.7: Wireless MMX pseudo-instructions

14: Directives Reference

14.1: Alphabetical list of directives

14.2: About assembly control directives

14.3: About frame directives

14.4: ALIAS

14.5: ALIGN

14.6: AREA

14.7: ARM, THUMB, THUMBX, CODE16, and CODE32

14.8: ASSERT

14.9: ATTR

14.10: CN

14.11: COMMON

14.12: CP

14.13: DATA

14.14: DCB

14.15: DCD and DCDU

14.16: DCDO

14.17: DCFD and DCFDU

14.18: DCFS and DCFSU

14.19: DCI

14.20: DCQ and DCQU

14.21: DCW and DCWU

14.22: END

14.23: ENTRY

14.24: EQU

14.25: EXPORT or GLOBAL

14.26: EXPORTAS

14.27: FRAME ADDRESS

14.28: FRAME POP

14.29: FRAME PUSH

14.30: FRAME REGISTER

14.31: FRAME RESTORE

14.32: FRAME RETURN ADDRESS

14.33: FRAME SAVE

14.34: FRAME STATE REMEMBER

14.35: FRAME STATE RESTORE

14.36: FRAME UNWIND ON

14.37: FRAME UNWIND OFF

14.38: FUNCTION or PROC

14.39: ENDFUNC or ENDP

14.40: FIELD

14.41: GBLA, GBLL, and GBLS

14.42: GET or INCLUDE

14.43: IF, ELSE, ENDIF, and ELIF

14.44: IMPORT and EXTERN

14.45: INCBIN

14.46: INFO

14.47: KEEP

14.48: LCLA, LCLL, and LCLS

14.49: LTORG

14.50: MACRO and MEND

14.51: MAP

14.52: MEXIT

14.53: NOFP

14.54: OPT

14.55: QN, DN, and SN

14.56: RELOC

14.57: REQUIRE

14.58: REQUIRE8 and PRESERVE8

14.59: RLIST

14.60: RN

14.61: ROUT

14.62: SETA, SETL, and SETS

14.63: SPACE or FILL

14.64: TTL and SUBT

14.65: WHILE and WEND

A: Assembler Document Revisions

A.1: Revisions for armasm User Guide

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc