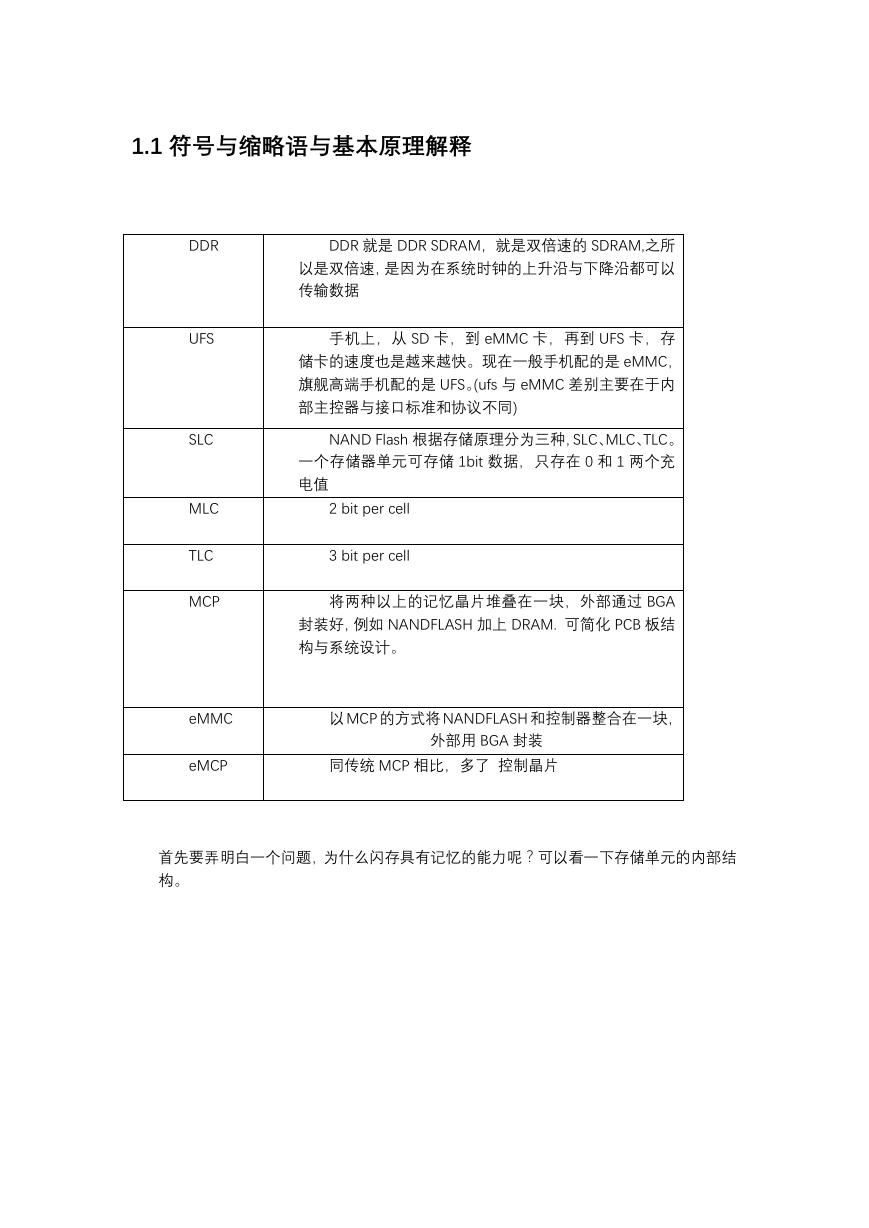

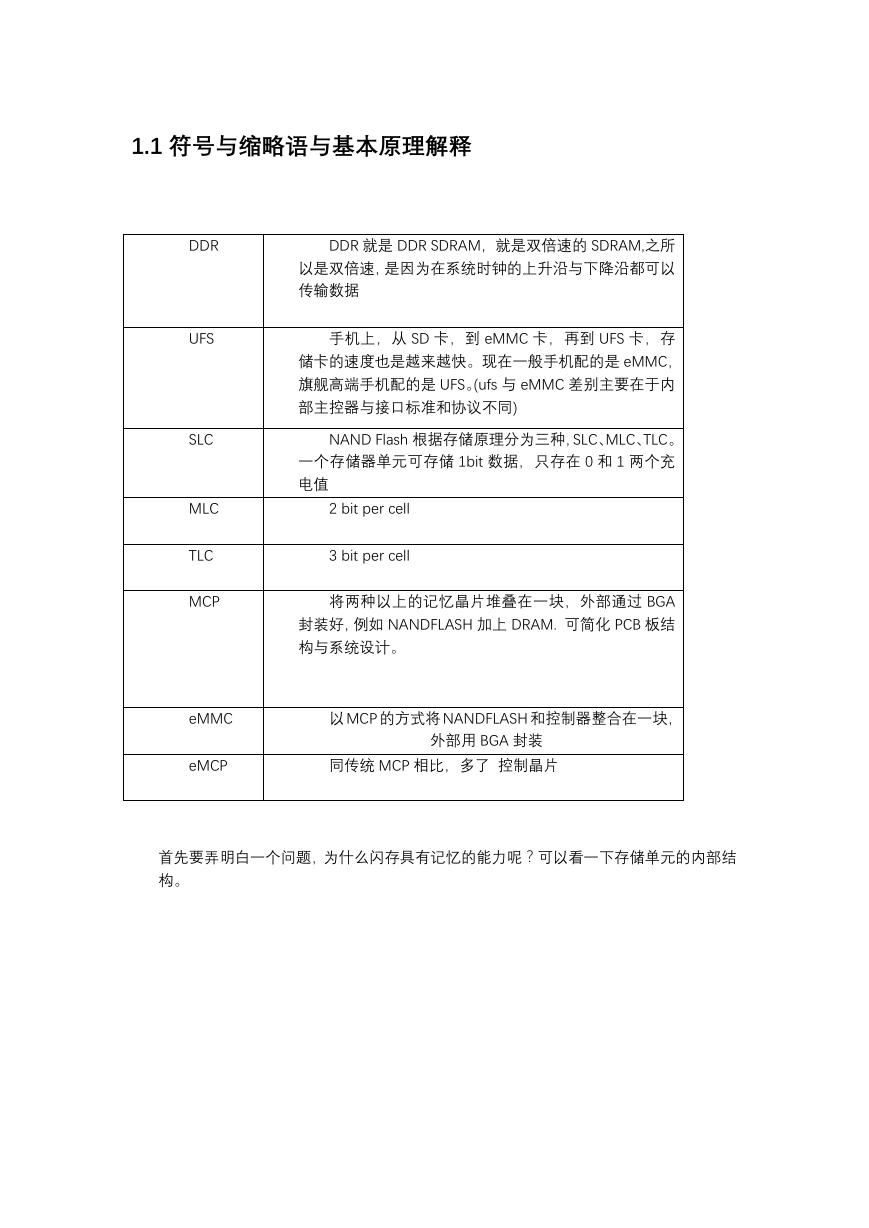

1.1 符号与缩略语与基本原理解释

DDR

UFS

SLC

MLC

TLC

MCP

DDR 就是 DDR SDRAM,就是双倍速的 SDRAM,之所

以是双倍速,是因为在系统时钟的上升沿与下降沿都可以

传输数据

手机上,从 SD 卡,到 eMMC 卡,再到 UFS 卡,存

储卡的速度也是越来越快。现在一般手机配的是 eMMC,

旗舰高端手机配的是 UFS。(ufs 与 eMMC 差别主要在于内

部主控器与接口标准和协议不同)

NAND Flash 根据存储原理分为三种,SLC、MLC、TLC。

一个存储器单元可存储 1bit 数据,只存在 0 和 1 两个充

电值

2 bit per cell

3 bit per cell

将两种以上的记忆晶片堆叠在一块,外部通过 BGA

封装好,例如 NANDFLASH 加上 DRAM. 可简化 PCB 板结

构与系统设计。

eMMC

eMCP

以 MCP 的方式将 NANDFLASH 和控制器整合在一块,

外部用 BGA 封装

同传统 MCP 相比,多了 控制晶片

首先要弄明白一个问题,为什么闪存具有记忆的能力呢?可以看一下存储单元的内部结

构。

�

用通俗语言解释就是说,NAND 的存储单单元 gate 极与衬底之间有二氧化硅绝缘层,用来

保护浮置栅极中的电荷不会泄漏。根据 NAND 的物理结构,NAND 是通过绝缘层存储数据

的。当你要写入数据,需要施加电压并形成一个电场,这样电子就可以通过绝缘体进入到存

储单元,此时完成写入数据。如果要删除存储单元(数据),则要再次施加电压让电子穿过

绝缘层,从而离开存储单元。 所以,NAND 闪存在重新写入新数据之前必须要删除原来数

据。

那么 TLC 是怎么实现的呢?答案是通过控制不同数量的电子进入到存储单元来实现。见下

图:

可以推测,TLC 的寿命比 SLC 和 MLC 短的多,原因是由于 TLC 采用不同的电压状态,加

上存储容量多,击穿绝缘层次数也比其他介质多,于是加速了绝缘层的损耗过程。所以,TLC

SSD 的寿命比 SLC、MLC 短得多。

�

1.2 RAM 与 NANDFLASH 和 NORFLASH 的区别

首先,不要问我为什么没有 ROM,因为 ROM 特么的就是个垃圾,就跟学习 MOS 管你还去

学耗尽型 MOS 管一样,大家都不用的东西,就不用去管它了。

1. NOR 内部可以直接跑程序(专业术语叫带 XIP: 芯片内执行),这是和 NAND 最大的

区别。很多 boot 都直接放在 NOR 里面,开机后直接跑起来。这就意味着 NOR 可以替

代 SRAM 了。

2. 断电后 RAM 里的数据就没有了,flash 仍然有,所以这就是为啥 boot 放 NOR 里面的原

因。

3. NAND 写入的速度比 NOR 快,并且容量大,价格便宜。所以 NAND 适合做替代磁盘做

存储器。NOR 读出速度快。

4. NOR 带 SRAM 接口,有足够的多的地址引脚来访问每一个存储单元,NAND 只能按块

来访问。

5. NAND 的最大擦写次数比 NOR 强,大概 100 万次,NOR 只有 10 万次左右。

6. NAND 容量大

1.3 NANDFLASH 的硬件连接

先来看看 NANDflash 的布线:

可以看出,就 data0~data7 八根数据线。那么,问题来了,站在硬件工程师的角度来说,

就八根数据线,外部是怎么对 flash 进行地址操作,以及发送命令操作的呢?

所以诀窍就在这几根线:

总结一下来说就是这样子工作的:

�

那么问题又来了,很多时候 MCU 的这几根数据线可不止光接 NANDFLASH 这一个外设,还

会同时接 NORFALASH, SDRAM 等,那么是怎么避免相互间干扰的呢?

答案很简单,就是靠的就是这根片选信号线:

假如把 数据 地址 命令 这三个都发给了 flash 后,怎么判断 flash 的执行状态呢?

答案仍然很简单,靠的就是 RnB 这根状态判断引脚来判断。

总结一下就是下面的表格:

RE WE 就是 读写信号。

�

1.4 NANDFLASH 的操作顺序

一般操作 NANDFLASH 的顺序都是三步走: 发出命令,给出地址,再读写数据

现在来看看具体的操作 NANDFLASH 的实例(读取 NANDFLASH 内部的 ID 值):

�

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc