基于 SystemView 软件的

二进制差分相位键控(2DPSK)的调制与解调

一:实验目的

1. 了解 2DPSK 系统的电路组成、工作原理和特点;

2. 从时域、频域视角观测 2DPSK 系统中的基带信号、载波及已调信号;

3. 熟悉系统中信号功率谱的特点。

二:仿真内容

以 PN 码作为系统输入信号,码速率 Rb=64kbit/s。

1. 采用键控法实现 2DPSK 的调制;分别观测绝对码序列、差分编码序列,比较

两序列的波形;观察调制信号、载波及 2DPSK 等信号的波形。

2. 获取主要信号的功率谱密度。

3. 采用相干解调法实现 2DPSK 的解调,分别观察系统各点波形。

4. 获取解调模块的各个主要信号的功率谱密度。

三:实验原理

调制:

2DPSK 方式是用前后相邻码元的载波相对相位变化来表示数字信息。假设前

后相邻码元的载波相位差为,可定义一种数字信息与之间的关系为

表示数字信息“ ”

0,

, 表示数字信息“ ”

0

1

则一组二进制数字信息与其对应的 2DPSK 信号的载波相位关系如下表所示

二进制数字信息:

2DPSK

1 1 0 1 0 0 1 1

0

0 0 0

0

0 0

数字信息与 之间的关系也可以定义为

之间的关系也可以定义为

数字信息与

信号相位:

或

0

0 0

0

0,

表示数字信息“ ”

, 表示数字信息“ ”

1

0

�

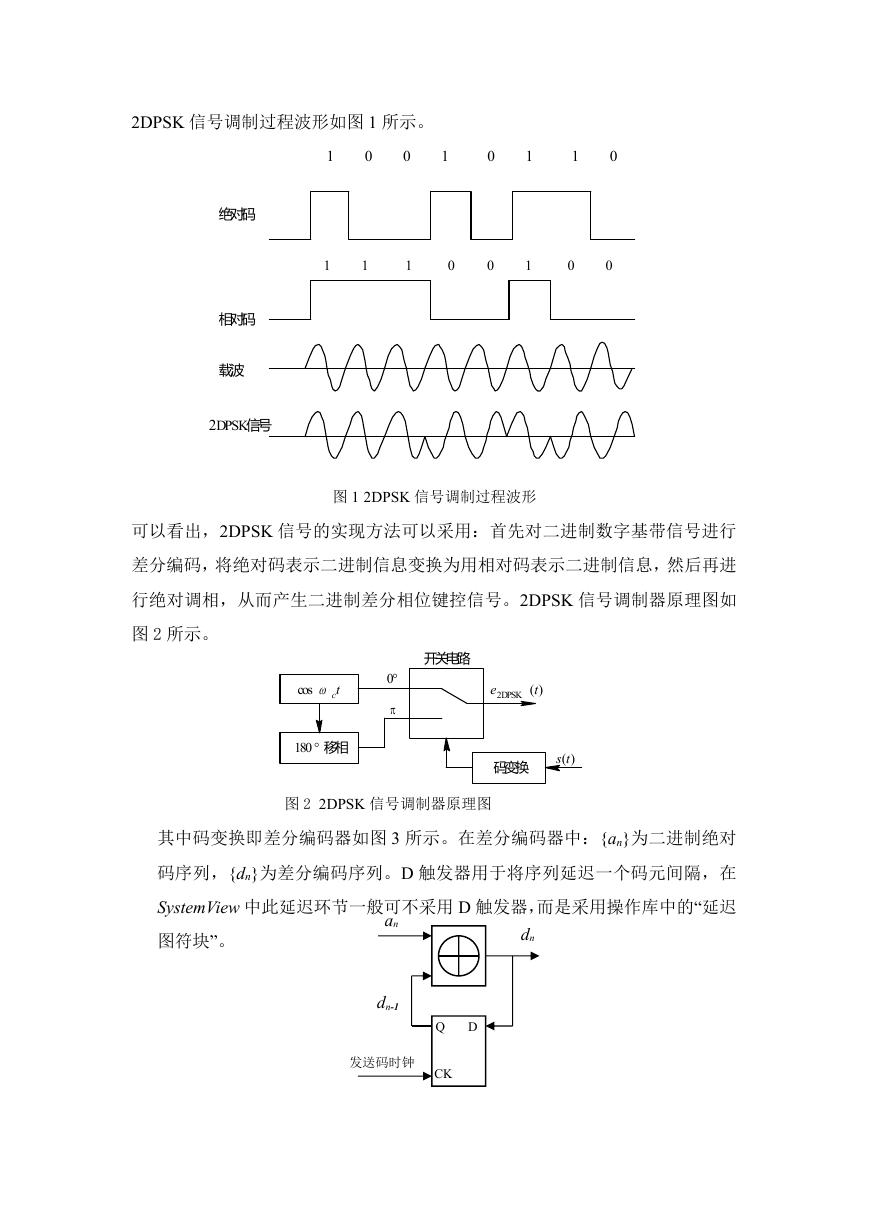

2DPSK 信号调制过程波形如图 1 所示。

1

0

0

1

0

1

1

0

1

1

1

0

0

1

0

0

绝对码

相对码

载波

2

DPSK信号

图 1 2DPSK 信号调制过程波形

可以看出,2DPSK 信号的实现方法可以采用:首先对二进制数字基带信号进行

差分编码,将绝对码表示二进制信息变换为用相对码表示二进制信息,然后再进

行绝对调相,从而产生二进制差分相位键控信号。2DPSK 信号调制器原理图如

图 2 所示。

cos ct

180 ° 移相

开关电路

e2DPSK (t)

0°

码变换

s(t)

图 2 2DPSK 信号调制器原理图

其中码变换即差分编码器如图 3 所示。在差分编码器中:{an}为二进制绝对

码序列,{dn}为差分编码序列。D 触发器用于将序列延迟一个码元间隔,在

SystemView 中此延迟环节一般可不采用 D 触发器,而是采用操作库中的“延迟

图符块”。

an

dn

dn-1

Q

D

发送码时钟

CK

�

解调:

相干解调法:

图 3 差分编码器

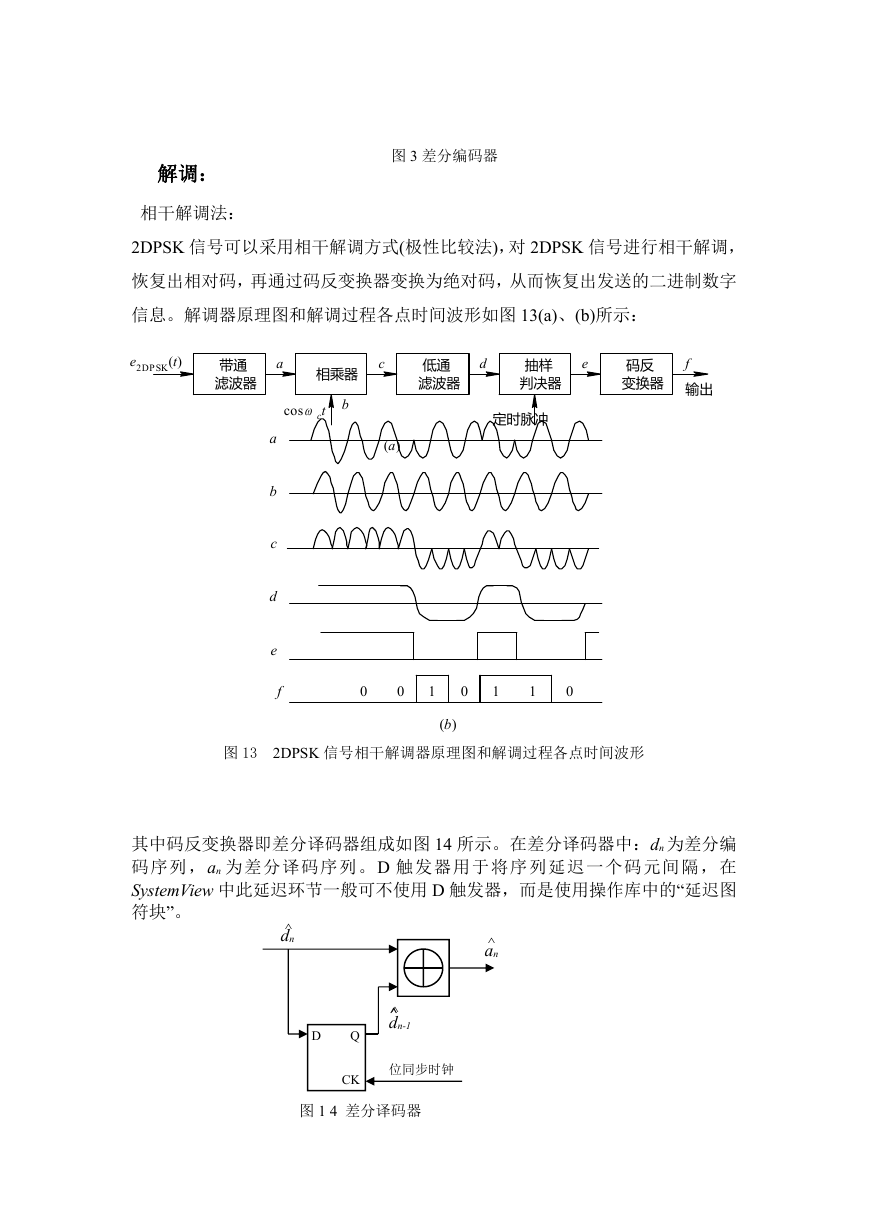

2DPSK 信号可以采用相干解调方式(极性比较法),对 2DPSK 信号进行相干解调,

恢复出相对码,再通过码反变换器变换为绝对码,从而恢复出发送的二进制数字

e2DPSK(t)

c

信息。解调器原理图和解调过程各点时间波形如图 13(a)、(b)所示:

相乘器

d

低通

滤波器

抽样

判决器

e

a

带通

滤波器

码反

变换器

f

输出

e2DPSK(t)

带通

滤波器

图 13

b

cosct

a

相乘器

cosct

b

a

b

a

b

c

c

d

d

e

f

e

低通

滤波器

d

定时脉冲

抽样

判决器

e

码反

变换器

f

输出

定时脉冲

c

(a)

(a)

0

0

1

0

1

1

0

f

0

0

0

1

1

0

2DPSK 信号相干解调器原理图和解调过程各点时间波形

(b)

1

(b)

其中码反变换器即差分译码器组成如图 14 所示。在差分译码器中:dn 为差分编

码序列,an 为差分译码序列。D 触发器用于将序列延迟一个码元间隔,在

SystemView 中此延迟环节一般可不使用 D 触发器,而是使用操作库中的“延迟图

符块”。

^

dn

^

an

^

^

dn-1

D

Q

位同步时钟

CK

图 1 4 差分译码器

�

四、系统组成、图符块参数设置及仿真结果:

键控法:

采用键控法进行调制的组成如图 4 所示。

图 4 键控法调制的系统组成

表 1:键控法图符参数设置表

编号

库/名称

参 数

Source: Sinusoid Amp = 1 v

Freq = 40e+3 Hz

t18

t1

Phase = 0 deg

Output 0 = Sine

Output 1 = Cosine

Max Rate (Port 0) = 600e+3 Hz

t4

0

1

2

3

Operator: Negate

Max Rate = 600e+3 Hz

Source: PN Seq Amp = 1 v

Operator: Delay

Rate = 20e+3 Hz

Non-Interpolating

Offset = 0 v

Levels = 2

Delay = 50.e-6 sec

Phase = 0 deg

Output 0 = Delay

Output 1 = Delay - dT t5

�

4

Logic: SPDT

Switch Delay = 0 sec

Threshold = 500.e-3 v

Input 0 = t0 Output 0

Input 1 = t1 Output 0

Control = t5 Output 0

5

Logic: XOR

Gate Delay = 0 sec

Threshold = 0 v

True Output = 1 v

False Output = -1 v

Rise Time = 0 sec

Fall Time = 0 sec

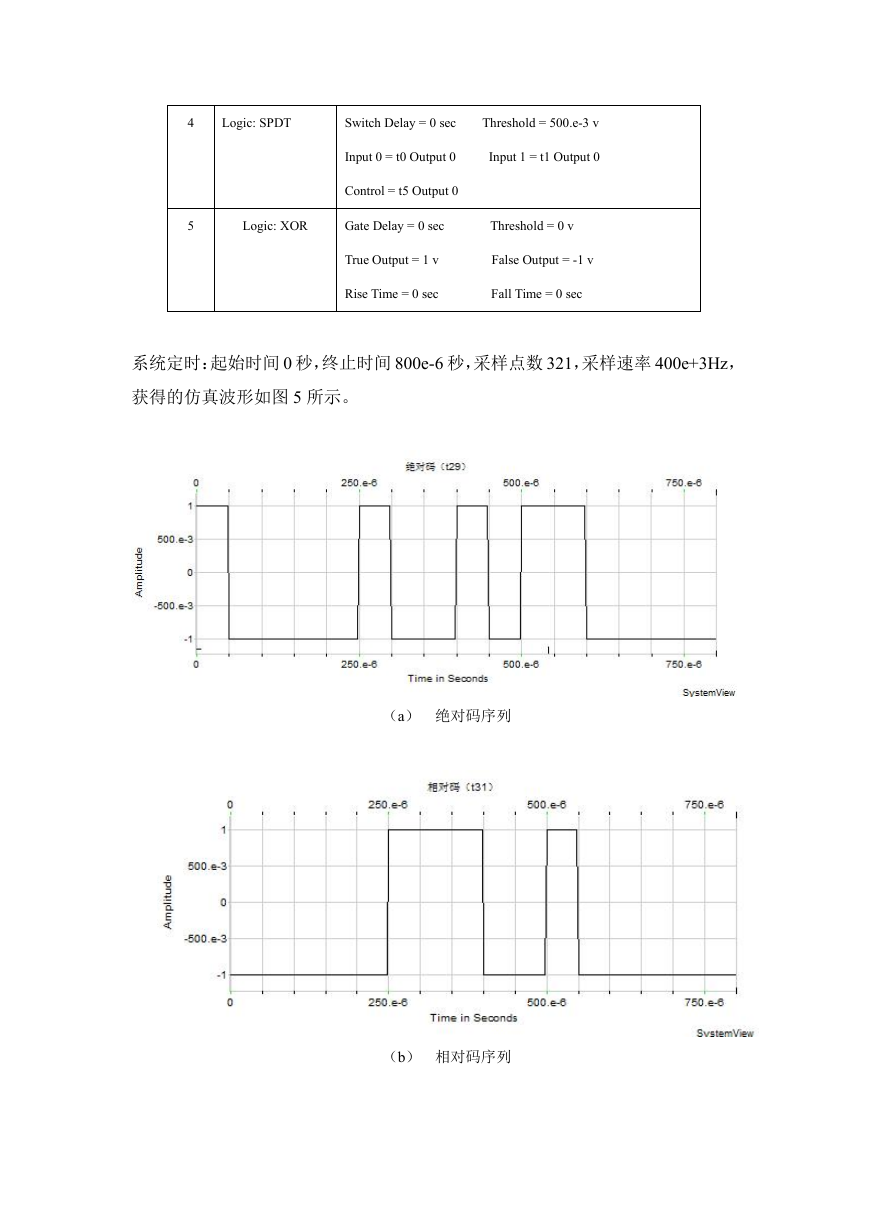

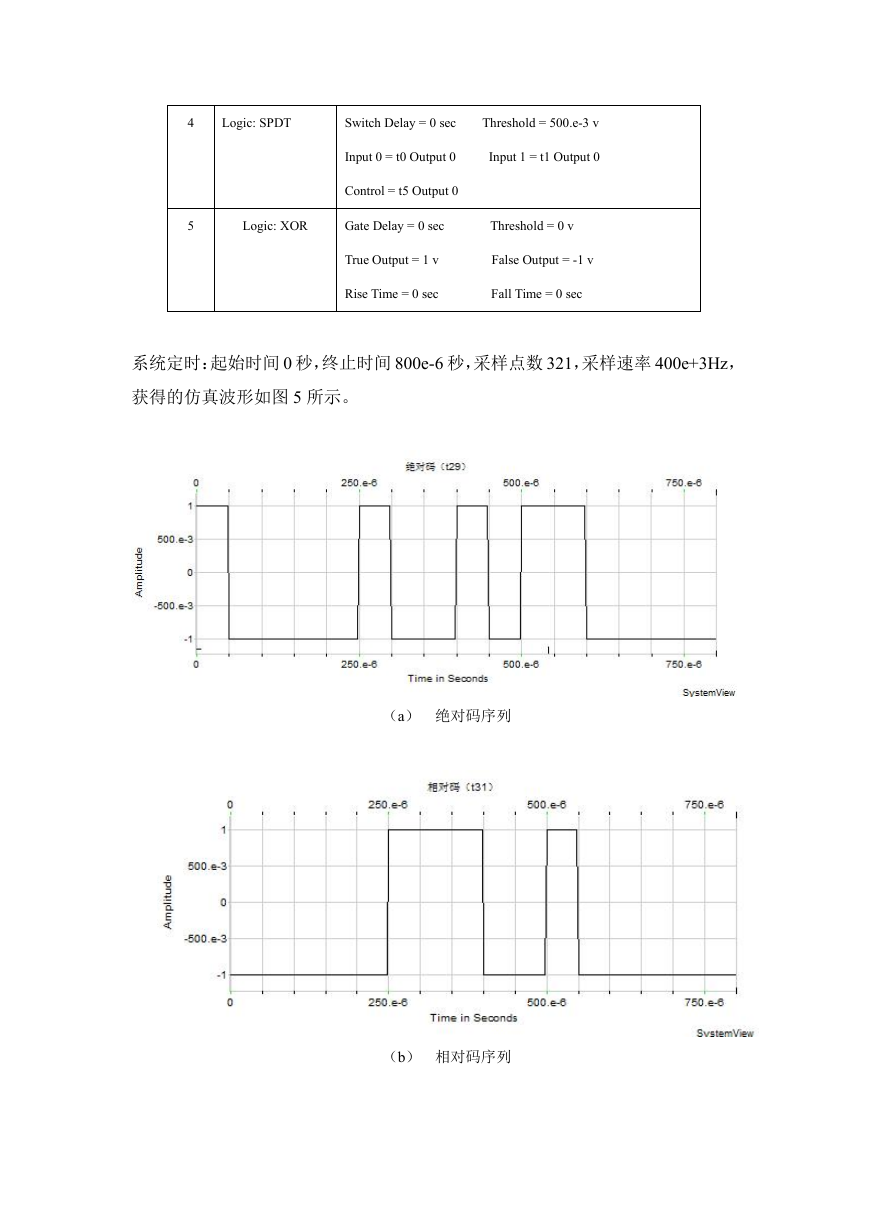

系统定时:起始时间 0 秒,终止时间 800e-6 秒,采样点数 321,采样速率 400e+3Hz,

获得的仿真波形如图 5 所示。

(a) 绝对码序列

(b) 相对码序列

�

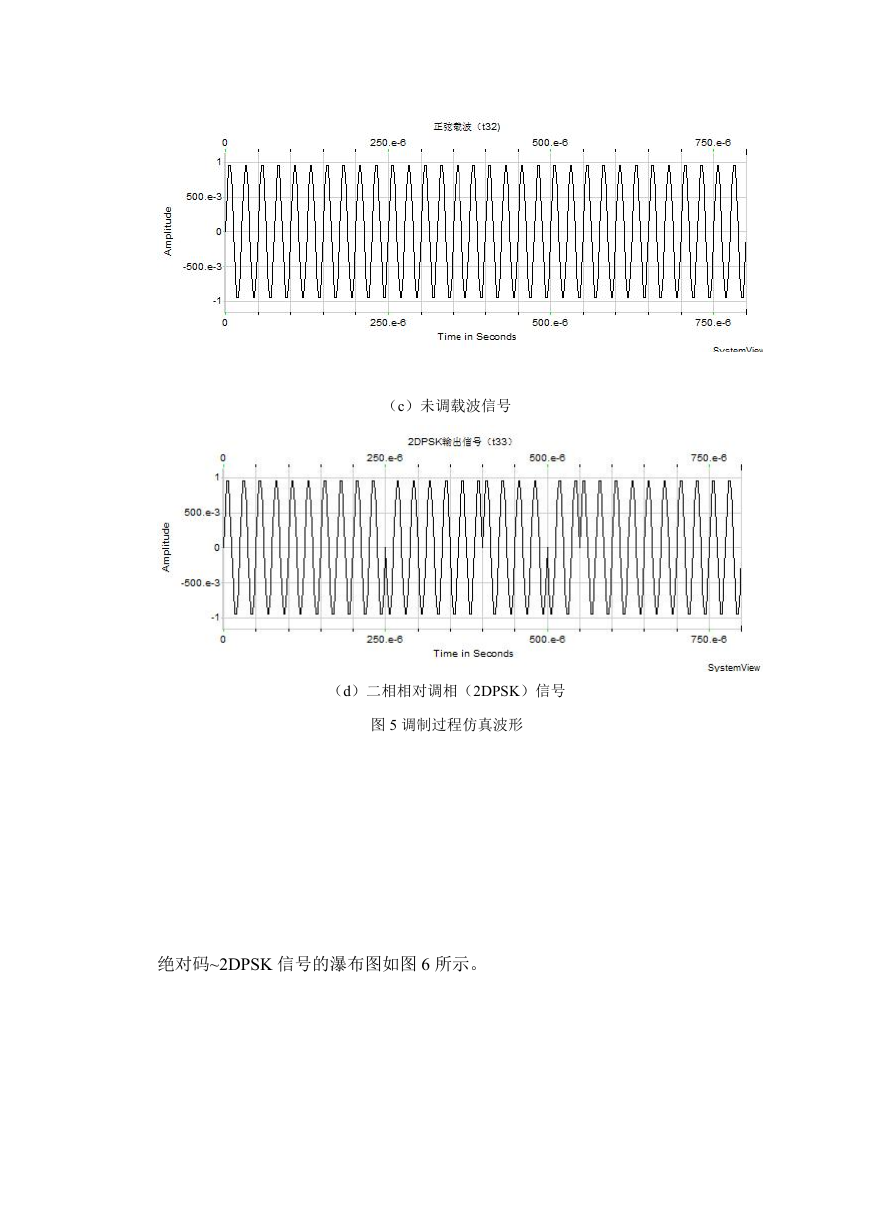

(c)未调载波信号

(d)二相相对调相(2DPSK)信号

图 5 调制过程仿真波形

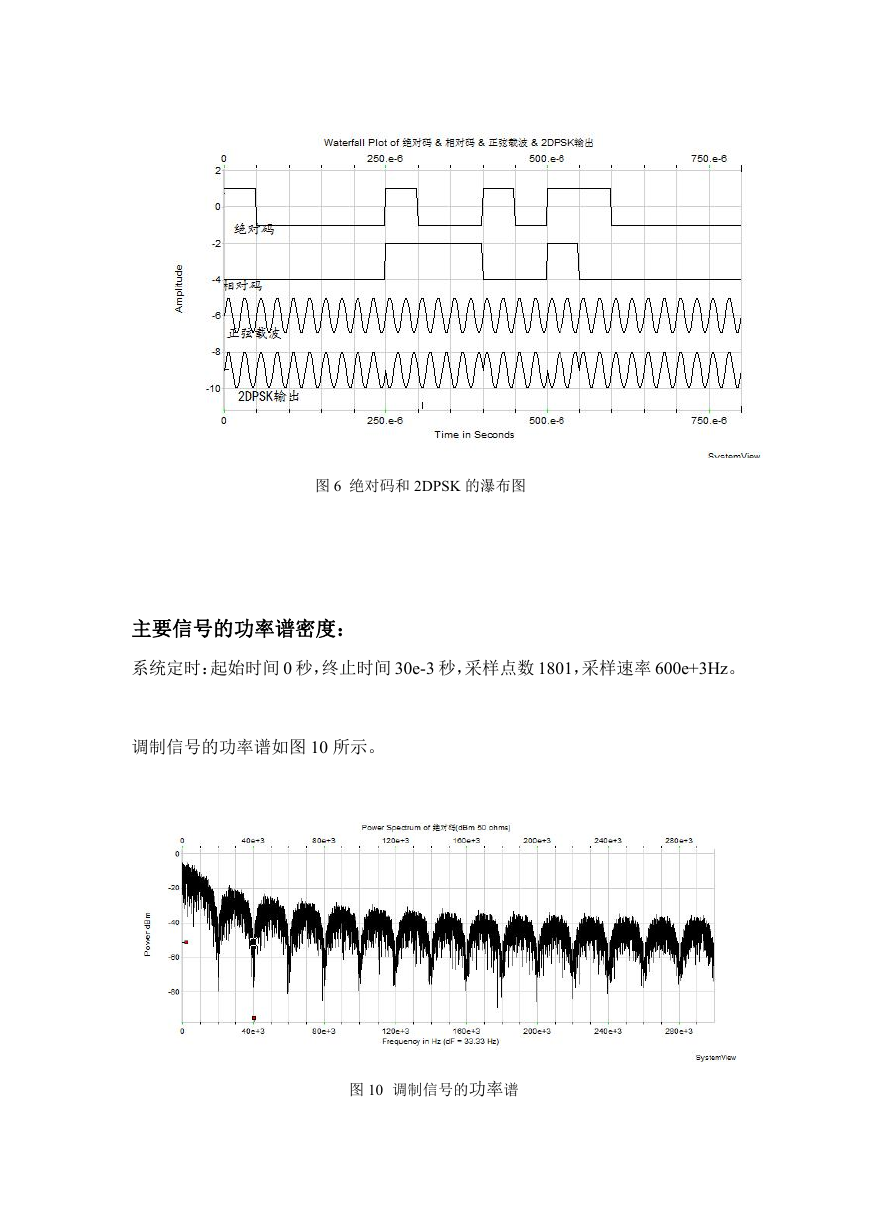

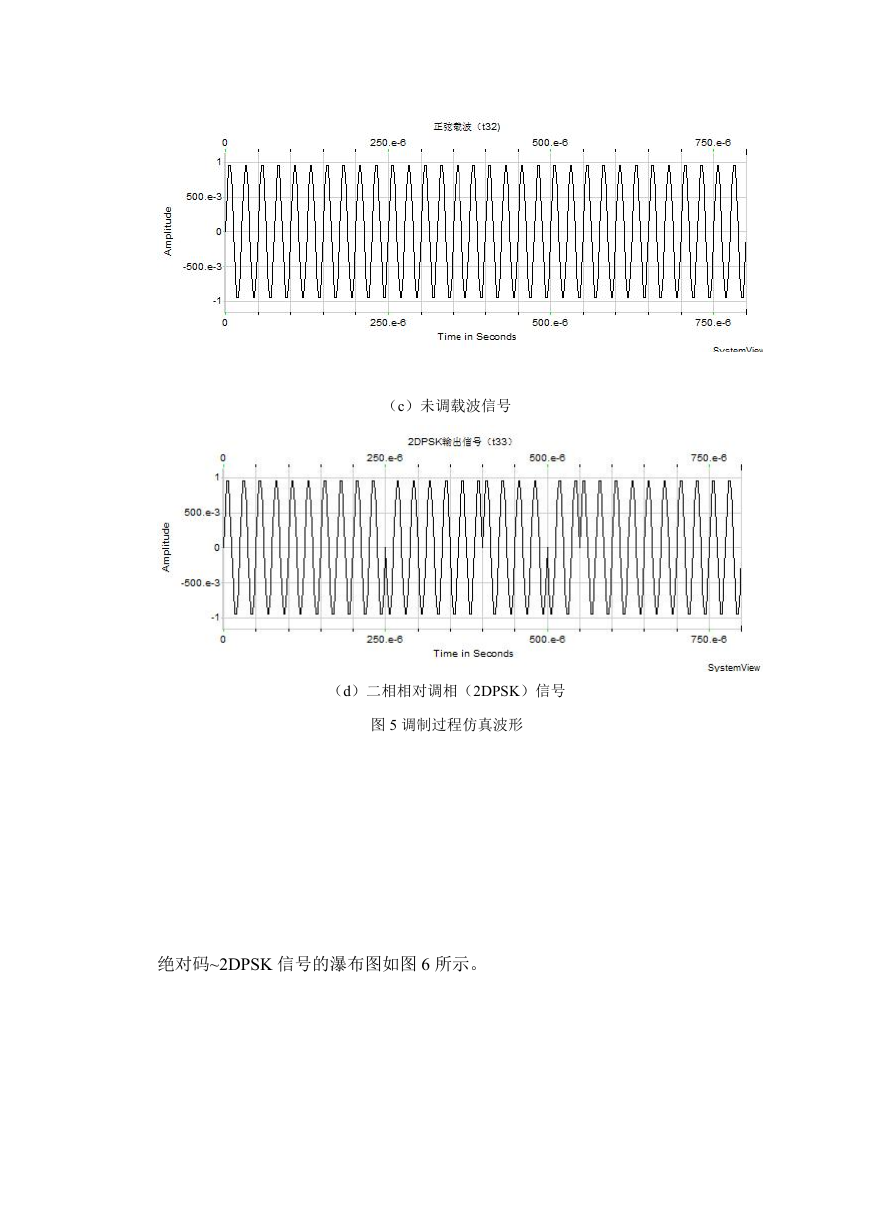

绝对码~2DPSK 信号的瀑布图如图 6 所示。

�

图 6 绝对码和 2DPSK 的瀑布图

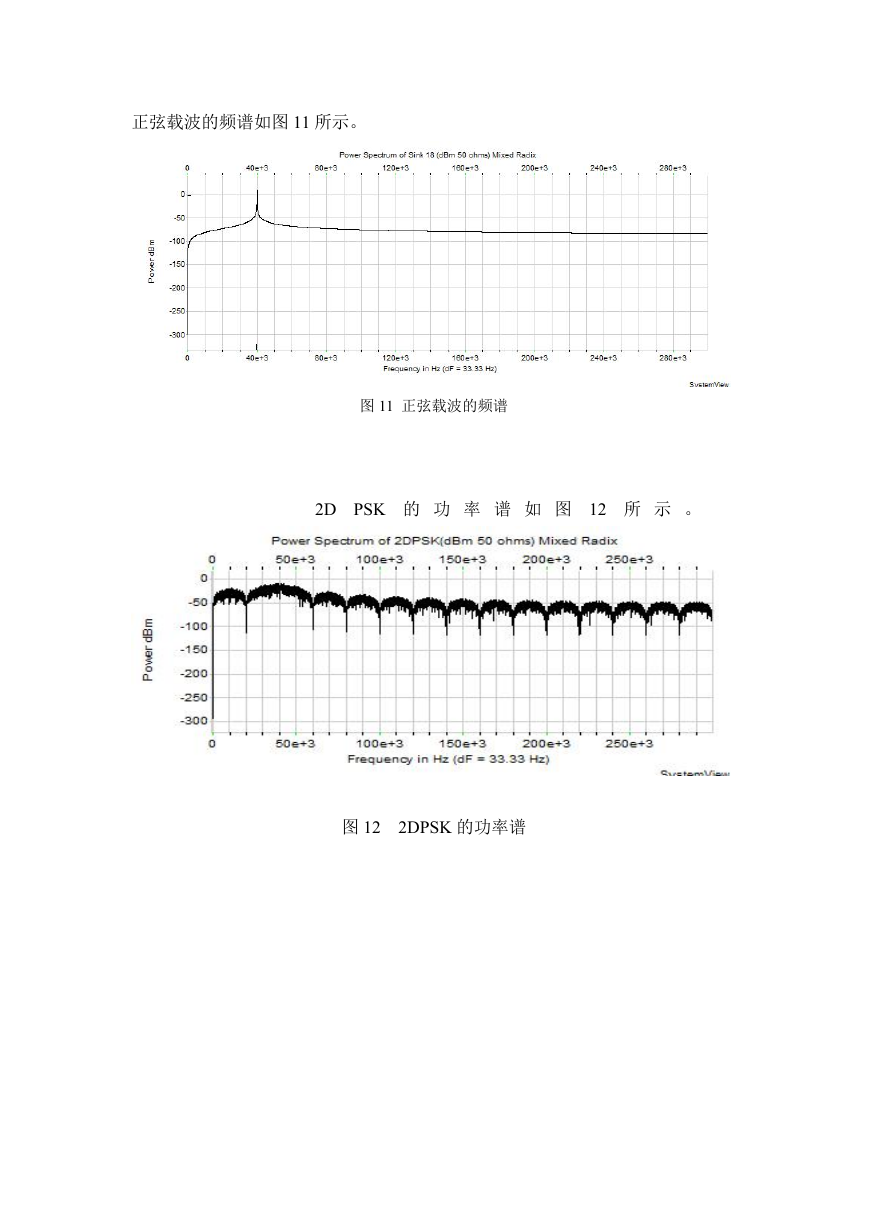

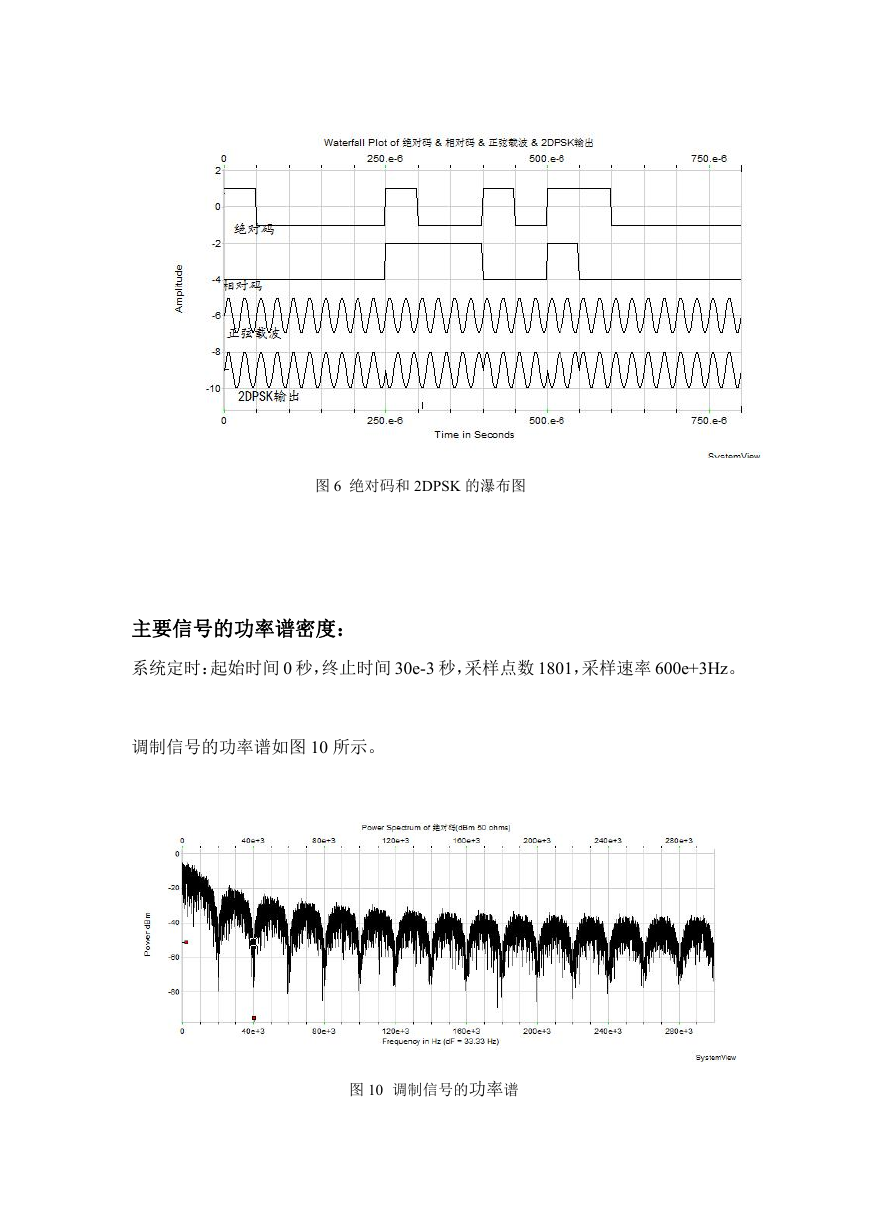

主要信号的功率谱密度:

系统定时:起始时间 0 秒,终止时间 30e-3 秒,采样点数 1801,采样速率 600e+3Hz。

调制信号的功率谱如图 10 所示。

图 10 调制信号的功率谱

�

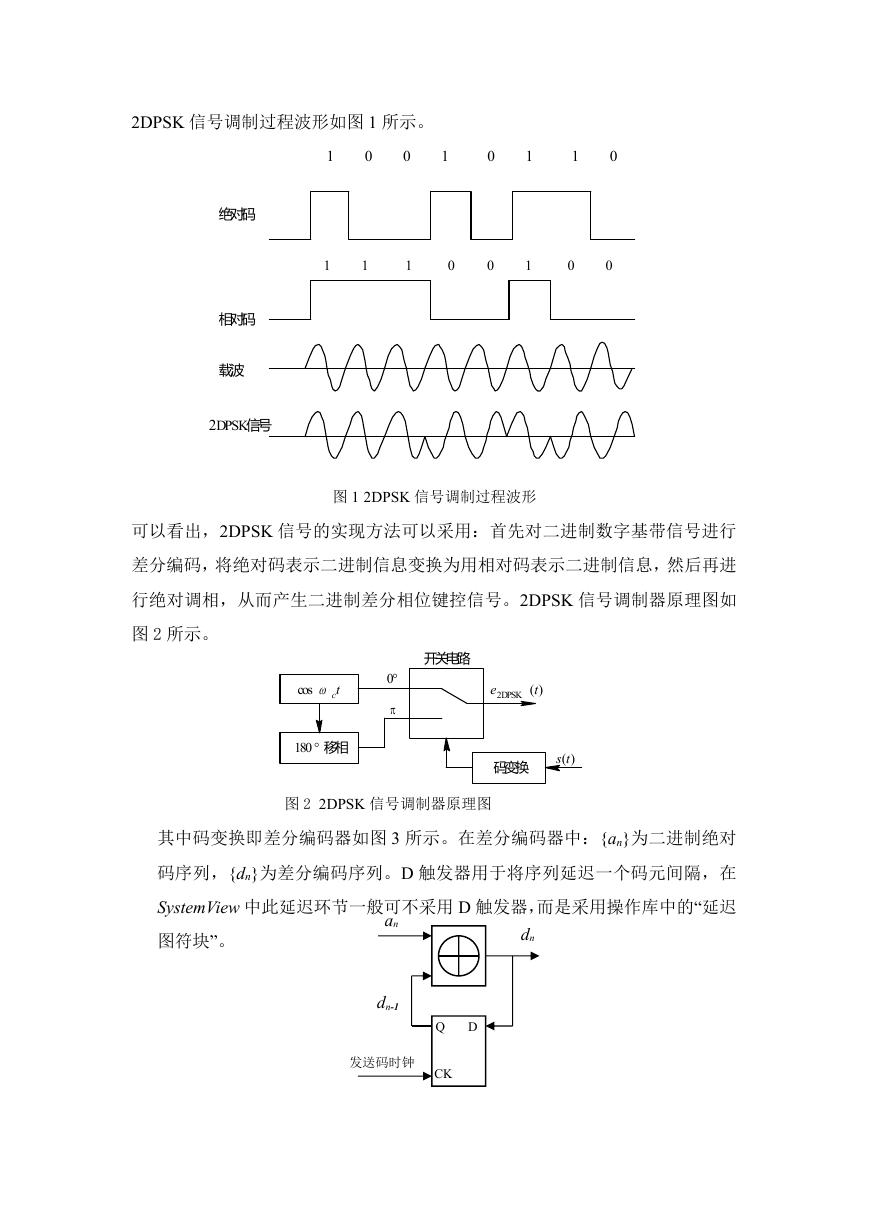

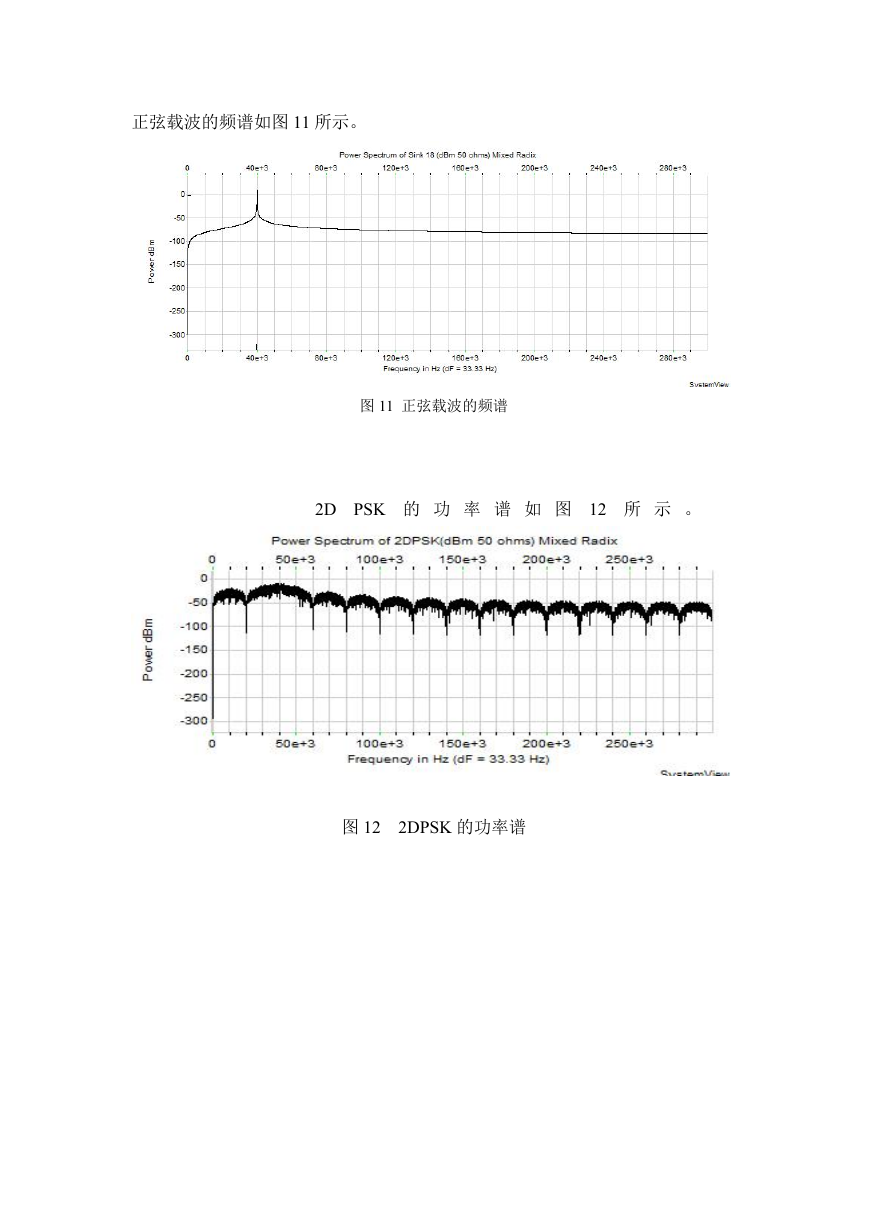

正弦载波的频谱如图 11 所示。

图 11 正弦载波的频谱

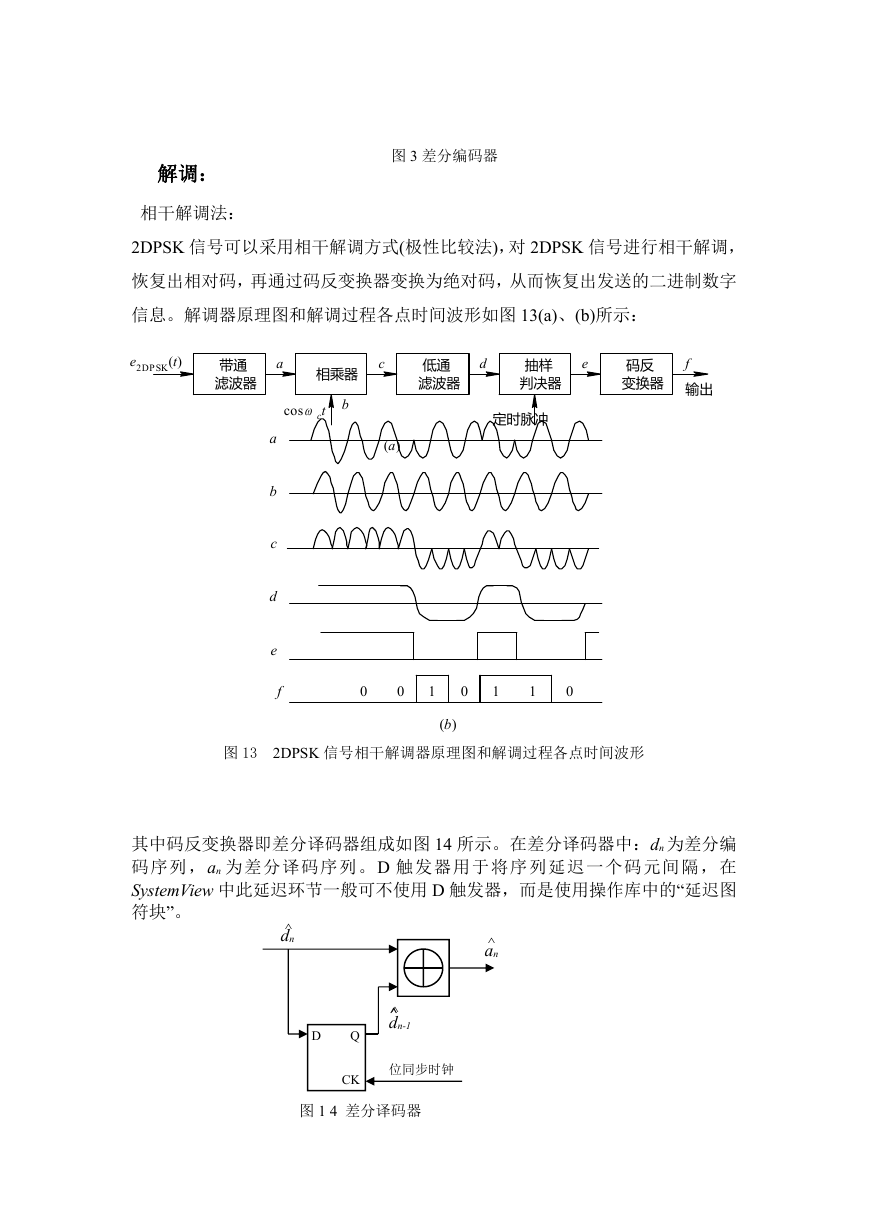

2D PSK 的 功 率 谱 如 图 12 所 示 。

图 12

2DPSK 的功率谱

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc