CORDIC IP 核 使用参考

以 ISE10.1 软件为例,其集成的 CORDIC 算法 IP 为 V3.0 版本,具体步骤如下:

1.新建工程,点 NEW Source…调用 IP Core Generator, 输入模块名如 MyCordic

后按 NEXT

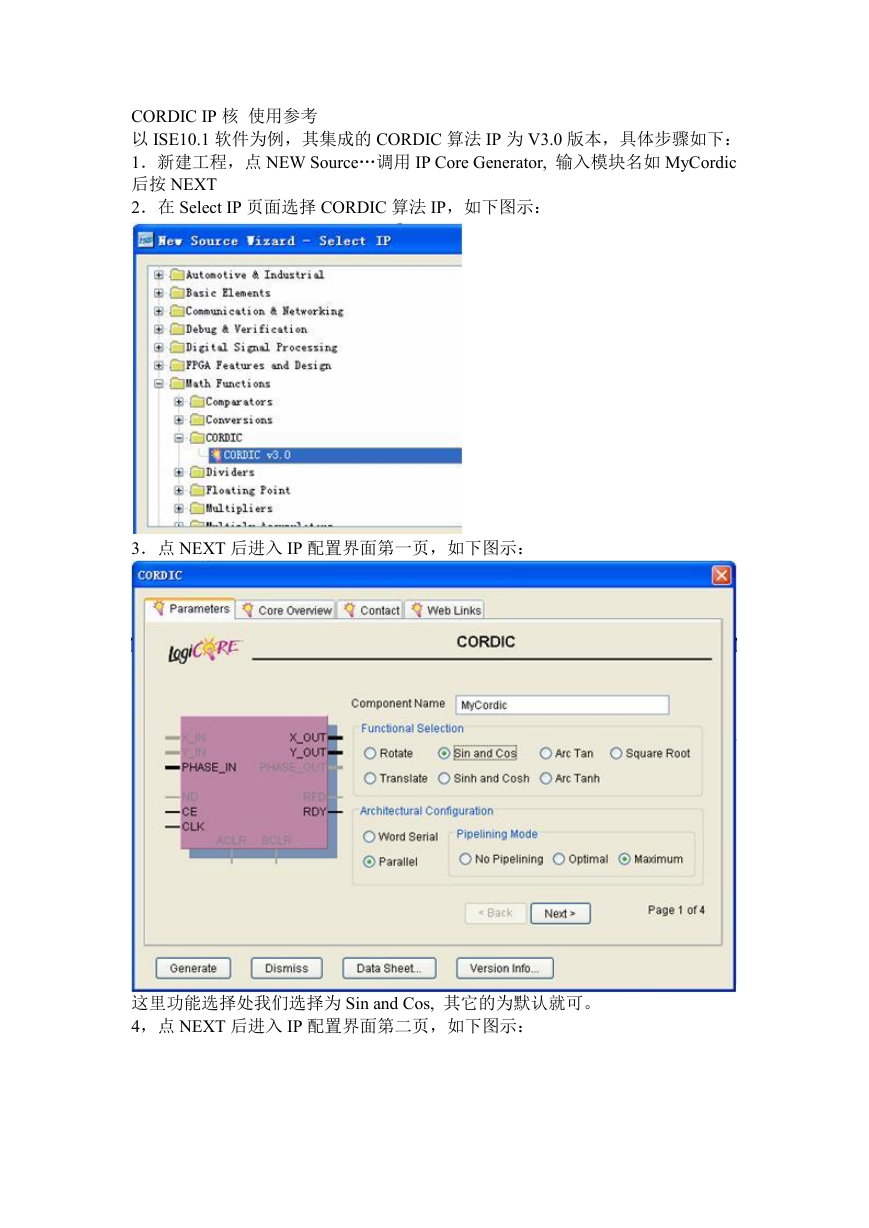

2.在 Select IP 页面选择 CORDIC 算法 IP,如下图示:

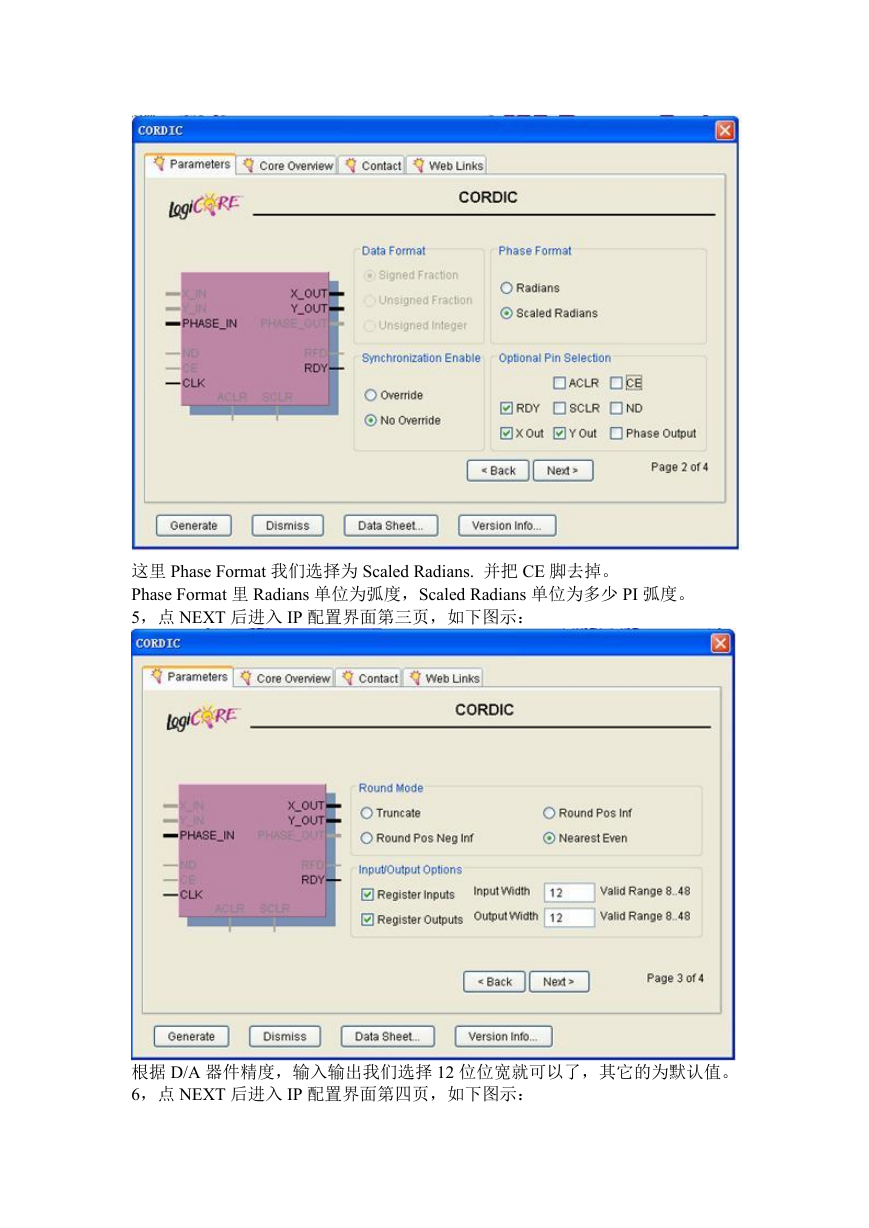

3.点 NEXT 后进入 IP 配置界面第一页,如下图示:

这里功能选择处我们选择为 Sin and Cos, 其它的为默认就可。

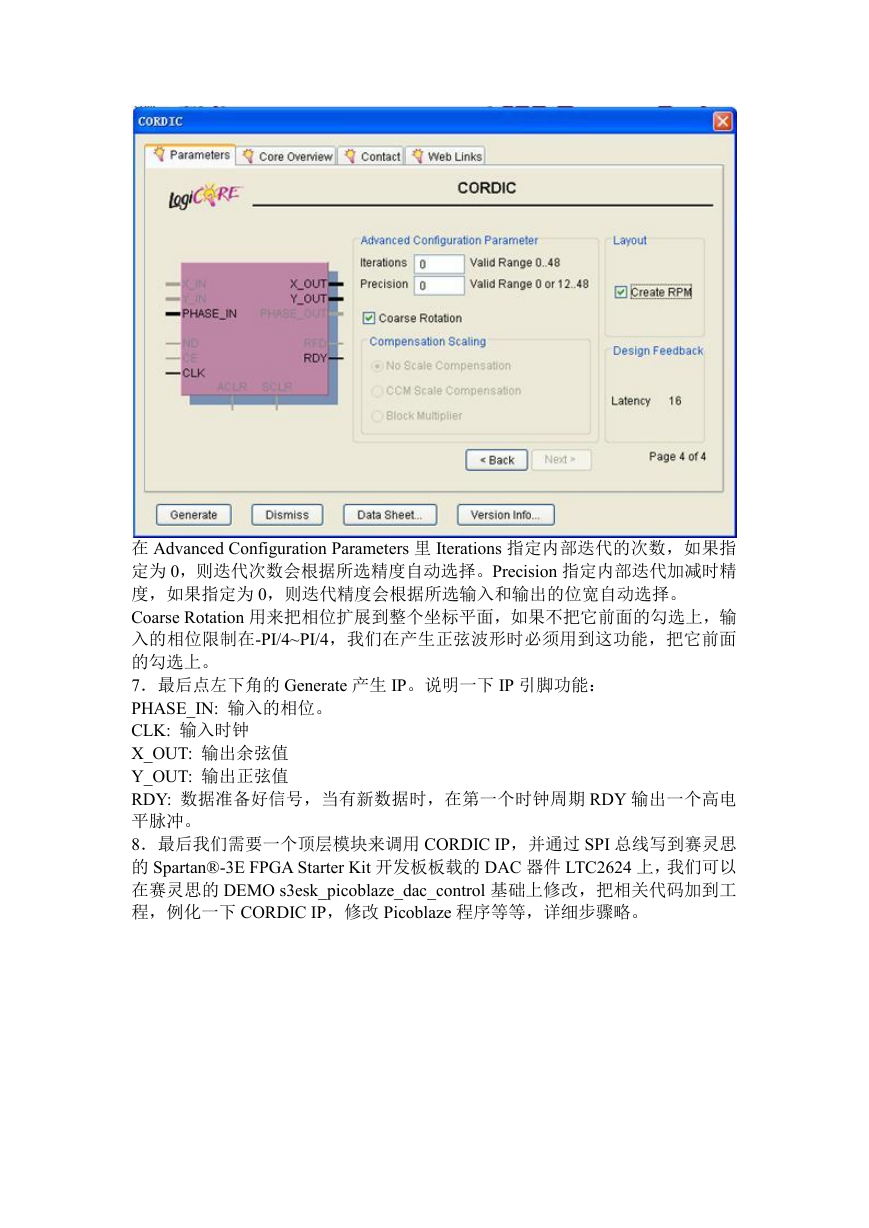

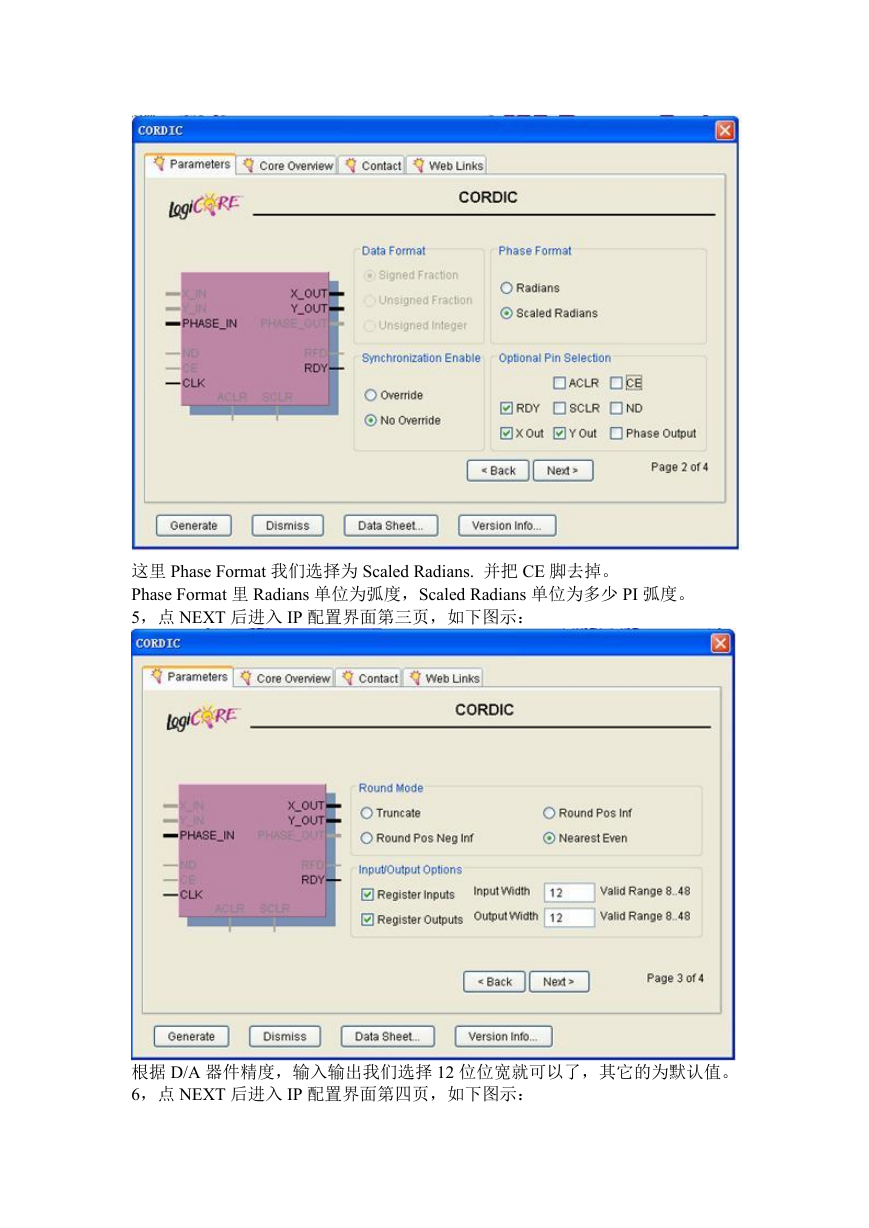

4,点 NEXT 后进入 IP 配置界面第二页,如下图示:

�

这里 Phase Format 我们选择为 Scaled Radians. 并把 CE 脚去掉。

Phase Format 里 Radians 单位为弧度,Scaled Radians 单位为多少 PI 弧度。

5,点 NEXT 后进入 IP 配置界面第三页,如下图示:

根据 D/A 器件精度,输入输出我们选择 12 位位宽就可以了,其它的为默认值。

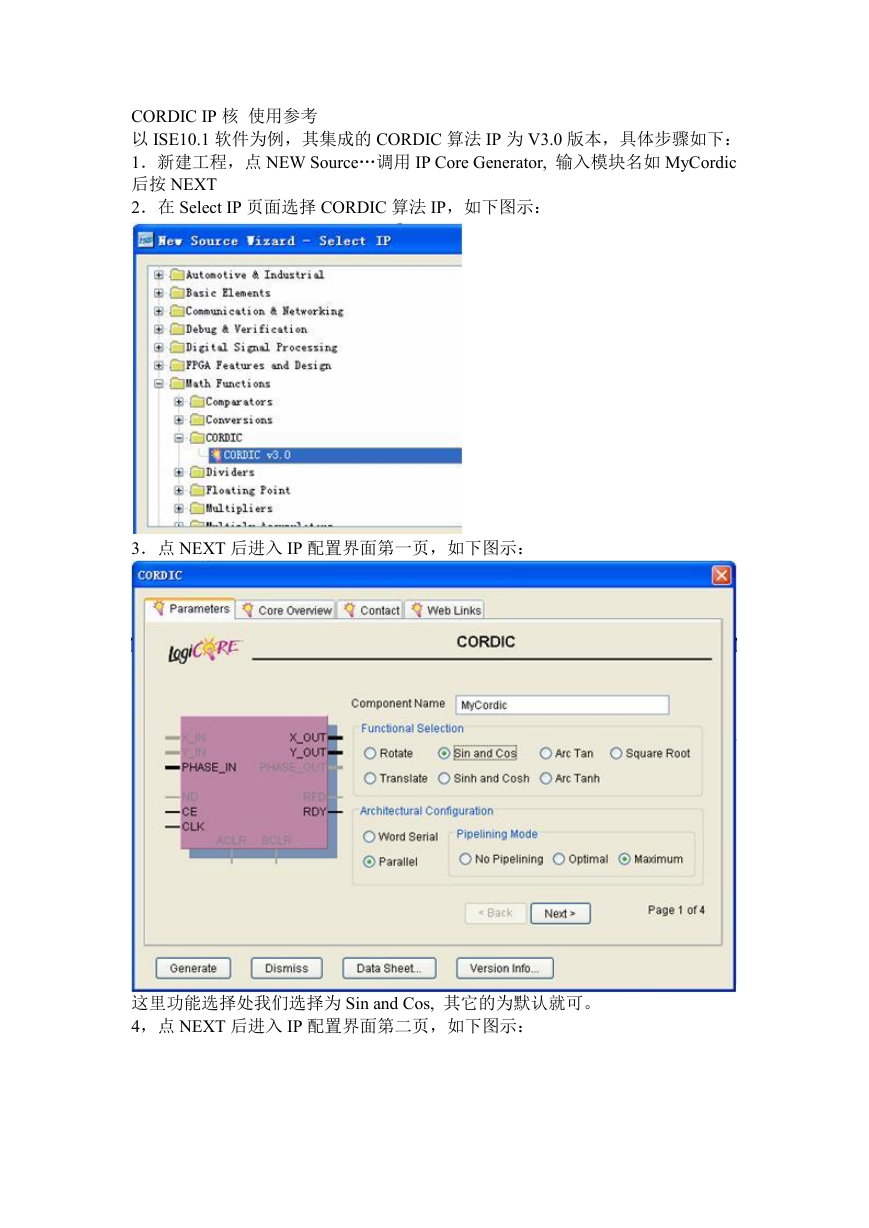

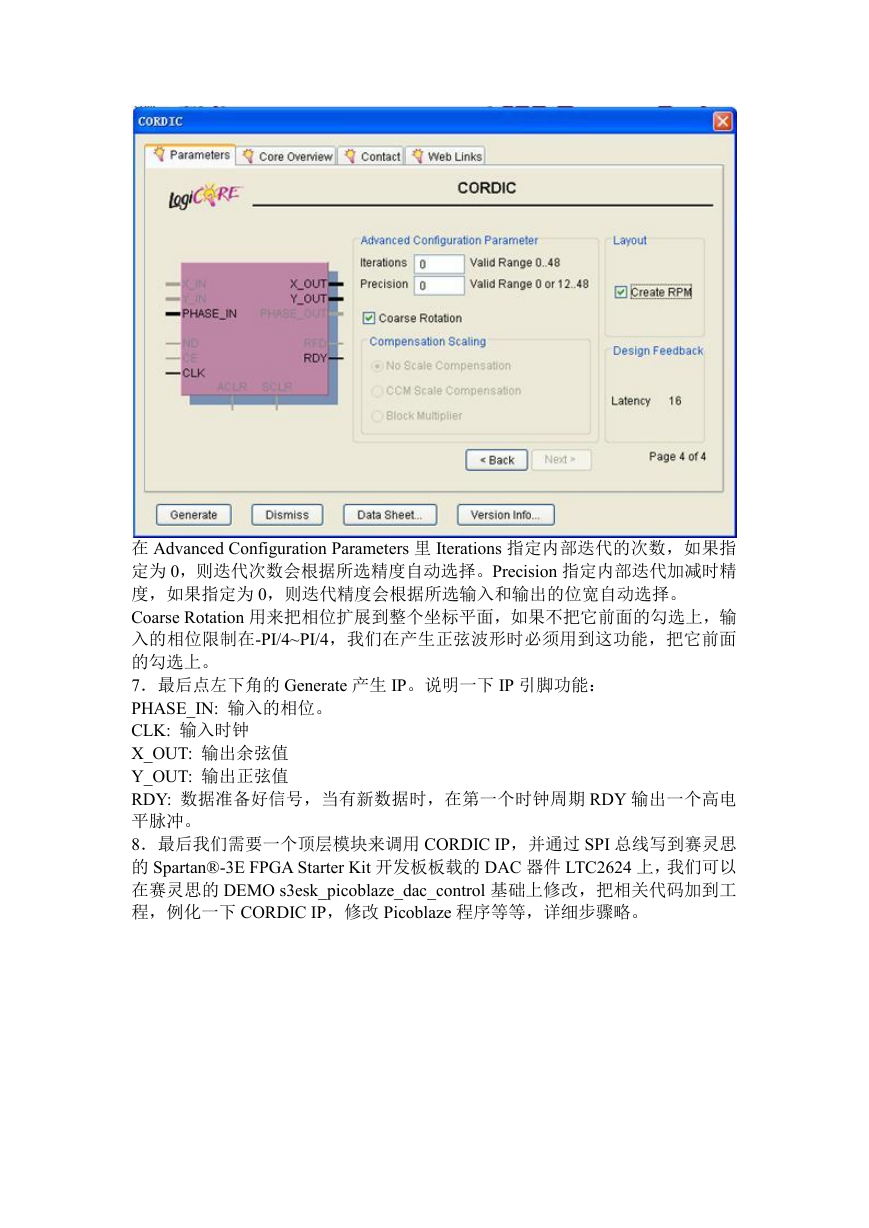

6,点 NEXT 后进入 IP 配置界面第四页,如下图示:

�

在 Advanced Configuration Parameters 里 Iterations 指定内部迭代的次数,如果指

定为 0,则迭代次数会根据所选精度自动选择。Precision 指定内部迭代加减时精

度,如果指定为 0,则迭代精度会根据所选输入和输出的位宽自动选择。

Coarse Rotation 用来把相位扩展到整个坐标平面,如果不把它前面的勾选上,输

入的相位限制在-PI/4~PI/4,我们在产生正弦波形时必须用到这功能,把它前面

的勾选上。

7.最后点左下角的 Generate 产生 IP。说明一下 IP 引脚功能:

PHASE_IN: 输入的相位。

CLK: 输入时钟

X_OUT: 输出余弦值

Y_OUT: 输出正弦值

RDY: 数据准备好信号,当有新数据时,在第一个时钟周期 RDY 输出一个高电

平脉冲。

8.最后我们需要一个顶层模块来调用 CORDIC IP,并通过 SPI 总线写到赛灵思

的 Spartan®-3E FPGA Starter Kit 开发板板载的 DAC 器件 LTC2624 上,我们可以

在赛灵思的 DEMO s3esk_picoblaze_dac_control 基础上修改,把相关代码加到工

程,例化一下 CORDIC IP,修改 Picoblaze 程序等等,详细步骤略。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc