泽屹电子

手把手教你学 FPGA

TimeQuest 静态时序分析

阿东团队 编著

�

手把手教你学 FPGA-TimeQuest 静态时序分析

手把手教你学 FPGA

TimeQuest 静态时序分析

2 / 68

�

手把手教你学 FPGA-TimeQuest 静态时序分析

目 录

1 写在前面 ................................................................ 5

2 简介 .................................................................... 7

3 为什么要做时序分析 ...................................................... 8

3.1 案例一 .............................................................. 8

3.2 案例二 .............................................................. 9

4 时序分析的概念 ......................................................... 10

4.1 同步逻辑时延模型 ................................................... 10

4.1.1 时钟抖动与偏斜 ............................................... 10

4.1.2 建立时间/保持时间 ............................................ 11

4.1.3 恢复时间/移除时间 ............................................ 12

4.1.4 Launch Edge & Latch Edge ..................................... 13

4.1.5 Data & Clock Time ............................................ 14

4.2 时序分析基本公式 ................................................... 17

4.2.1 建立时间(Setup Time)检查 ................................... 18

4.2.2 保持时间(Hold Time)检查 .................................... 19

4.2.3 多周期路径(Multicycle Paths)检查 ........................... 20

4.3 Altera 器件时序模型 ................................................ 22

4.4 基本单元与 paths ................................................... 23

4.5 FPGA 时序约束的几种方法 ............................................ 25

4.5.1 核心频率约束 ................................................. 25

4.5.2 核心频率约束+ 时序例外约束 ................................... 25

4.5.3 核心频率约束+ 时序例外约束+I/O ............................... 25

5 使用 Timequest 时序分析器约束分析设计 ................................... 27

5.1 Timequest 基础 ..................................................... 27

5.1.1 时序约束和分析流程 ........................................... 27

5.1.2 Timequest GUI ................................................ 29

5.1.3 看懂时序波形图 ............................................... 30

5.2 时序约束 ........................................................... 32

5.2.1 Clocks ....................................................... 33

5.2.2 PLL clocks ................................................... 37

5.2.3 I/O .......................................................... 38

5.2.4 False paths .................................................. 44

6 时序分析设计实例 ....................................................... 46

6.1 LED 流水灯 ......................................................... 46

6.1.1 LED 流水灯功能框图 ........................................... 46

6.1.2 LED 流水灯代码 ............................................... 46

6.1.3 LED 流水灯时序分析 ........................................... 47

6.2 摄像头接口 ......................................................... 55

6.2.1 摄像头简介 ................................................... 55

6.2.2 摄像头接口 ................................................... 55

6.2.3 摄像头接口时序 ............................................... 56

3 / 68

�

手把手教你学 FPGA-TimeQuest 静态时序分析

6.3 时序分析设计实例三-Ethernet ........................................ 62

6.3.1 Ethernet 功能框图 ............................................ 62

6.3.2 Ethernet 时序分析 ............................................ 62

6.4 时序分析设计实例三-SDRAM ........................................... 64

6.4.1 SDRAM 控制器功能框图 ......................................... 64

6.4.2 SDRAM 控制器时序分析 ......................................... 64

7 写在最后 ............................................................... 68

4 / 68

�

手把手教你学 FPGA-TimeQuest 静态时序分析

1 写在前面

作者简介:

大家好,我是阿东,我在通信行业做了 10 年的芯片设计,做了几款大型路

由器和交换机芯片,写了 10 年的 Verilog,对 Verilog 是熟悉的不能再熟悉了,

对数据通信、QOS 有深入研究和实现,精通数据通信各种协议,对通信网络有较

深理解。精通 ASIC、FPGA 和 Verilog 架构、方案、实现设计。

希望我的经历能让大家掌握项目开发的编码规范、设计思想、方案设计,给

大家的学习和发展略进绵薄之力。

已经推出的教材包括:

《手把手教你学 FPGA_语法篇》

《手把手教你学 FPGA _编程规范篇》

《手把手教你学 FPGA _仿真篇》

《手把手教你学 FPGA _设计思想篇》。

后续还会推出更多相关资料,包括方案设计、视频教程等,请大家关注我们。

我们的 FPGA 论坛,欢迎大家访问:

http://adfpga.com

我们的 FPGA 开发板网站,欢迎大家访问:

https://shop67541132.taobao.com/

上述教材的很多例子程序都可以在我们开发板配套光盘中找到,配套光盘里

面还有更多更好的例子。

5 / 68

�

手把手教你学 FPGA-TimeQuest 静态时序分析

我们的淘宝店铺:本店专注于 FPGA 开发板,有低端、中端、高端开发板供

大家选择。

1、EP4CE6 FPGA 开发板: (包括开发板+USB Blaster 下载器+电源线+2 个

DVD 光盘):适合没有任何基础,可以用来做学习和一般项目使用。

https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-1006554551.2.30df85ddnc1gGg&id=35

911884243

备注:现在购买还送配套书籍一本(北航出版):

https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-1006554551.8.30df85ddhlb93f&id=540

865636294

2、中端 EP4CE10 FPGA 开发板: (包括开发板+USB Blaster 下载器+电源线

+2 个 DVD 光盘): 适合没有任何基础、有一定基础,可以用来做学习和一般项目、

电子竞赛、NIOS。

https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-1006554551.6.30df85ddnc1gGg&id=52

0588767908

3、高端 EP4CE30 FPGA 开发板: (包括核心板+底板+USB Blaster 下载器+电

源线+2 个 DVD 光盘): 适合没有任何基础、有一定基础、基础较好,可以用来做

学习和高级项目、NIOS。

https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-1006554551.10.30df85ddnc1gGg&id=3

9939126777

还有更多的开发板、配套外设、配套书籍可以直接到我们的淘宝店铺:

https://shop67541132.taobao.com/

联系我们:

QQ :1530384236

旺旺:dongguo100

QQ 群:185735160 (欢迎加入)

阿东 FPGA 论坛:adfpga.com/ (拷贝到浏览器中打开即可)

6 / 68

�

手把手教你学 FPGA-TimeQuest 静态时序分析

2 简介

时序分析在 ASIC 设计中非常重要,芯片频率是否达到预期,各种接口能否

调通等等都需要时序分析。在 FPGA 设计中,很少进行细致全面的时序约束和分

析,Fmax 是最常见也往往是一个设计唯一的约束。这一方面是由 FPGA 的特殊

结构决定的,另一方面也是由于缺乏好用的工具造成的。

好的时序约束可以指导布局布线工具进行权衡,获得最优的器件性能,使设

计代码最大可能的反映设计者的设计意图。

静态时序分析可以保证设计质量,也可以促使设计者再认识自己的代码。后

一点,对于我们这些逻辑设计初学者来说自己的代码,可以更深入地体会语言的

特点,也可以更深入地,尤为重要。从门级(在 Altera 的 FPGA 器件中是 LE 级)

再认识理解综合工具对语言的处理,对于设计能力的提高帮助很大。

本文致力于提高您的时序分析能力,Quartus 使用 TimeQuest 进行时序分

析,本文讲解的工具就是 TimeQuest。

TimeQuest 采用 Synopsys Design Constraints(SDC)文件格式作为时序

约束输入,不同于 Timing Analyzer 采用的 Quartus Settings File(QSF)约

束文件。这正是 TimeQuest 的优点:采用行业通用的约束语言而不是专有语言,

有利于设计约束从 FPGA 向 ASIC 设计流程迁移;有利于创建更细致深入的约束

条件。

7 / 68

�

手把手教你学 FPGA-TimeQuest 静态时序分析

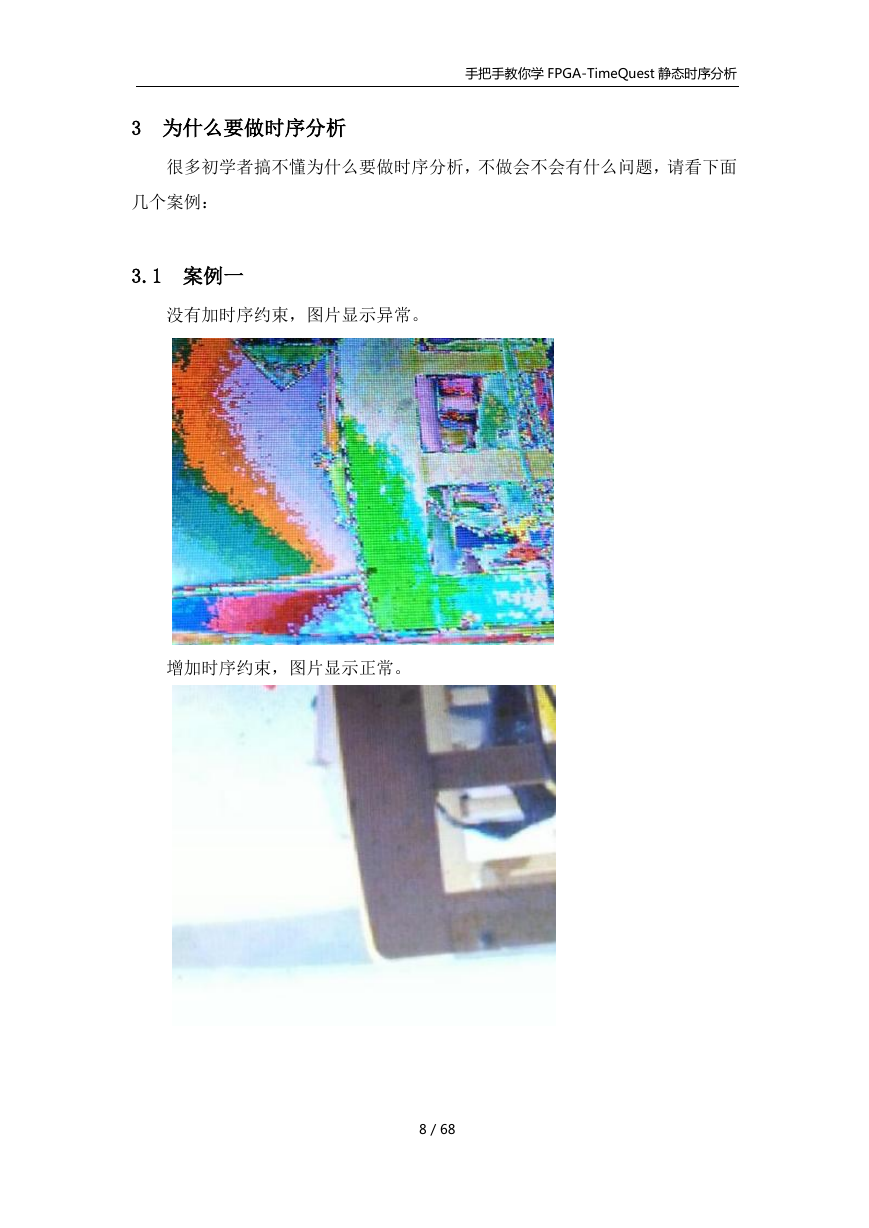

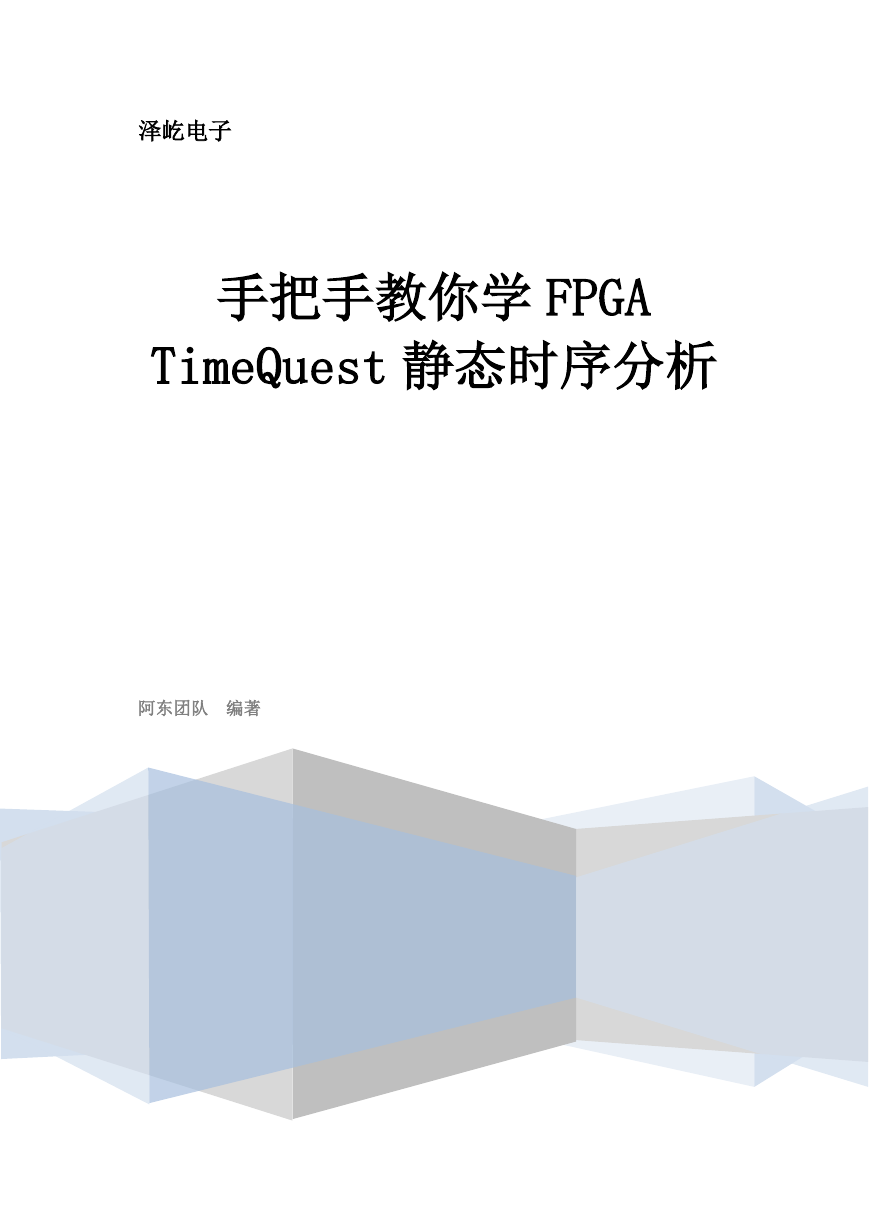

3 为什么要做时序分析

很多初学者搞不懂为什么要做时序分析,不做会不会有什么问题,请看下面

几个案例:

3.1 案例一

没有加时序约束,图片显示异常。

增加时序约束,图片显示正常。

8 / 68

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc