[zz]C64x DSP 音频接口 McASP 应用编程要点

2007-04-19 17:13

McASP 应用编程总结(C64x DSP)

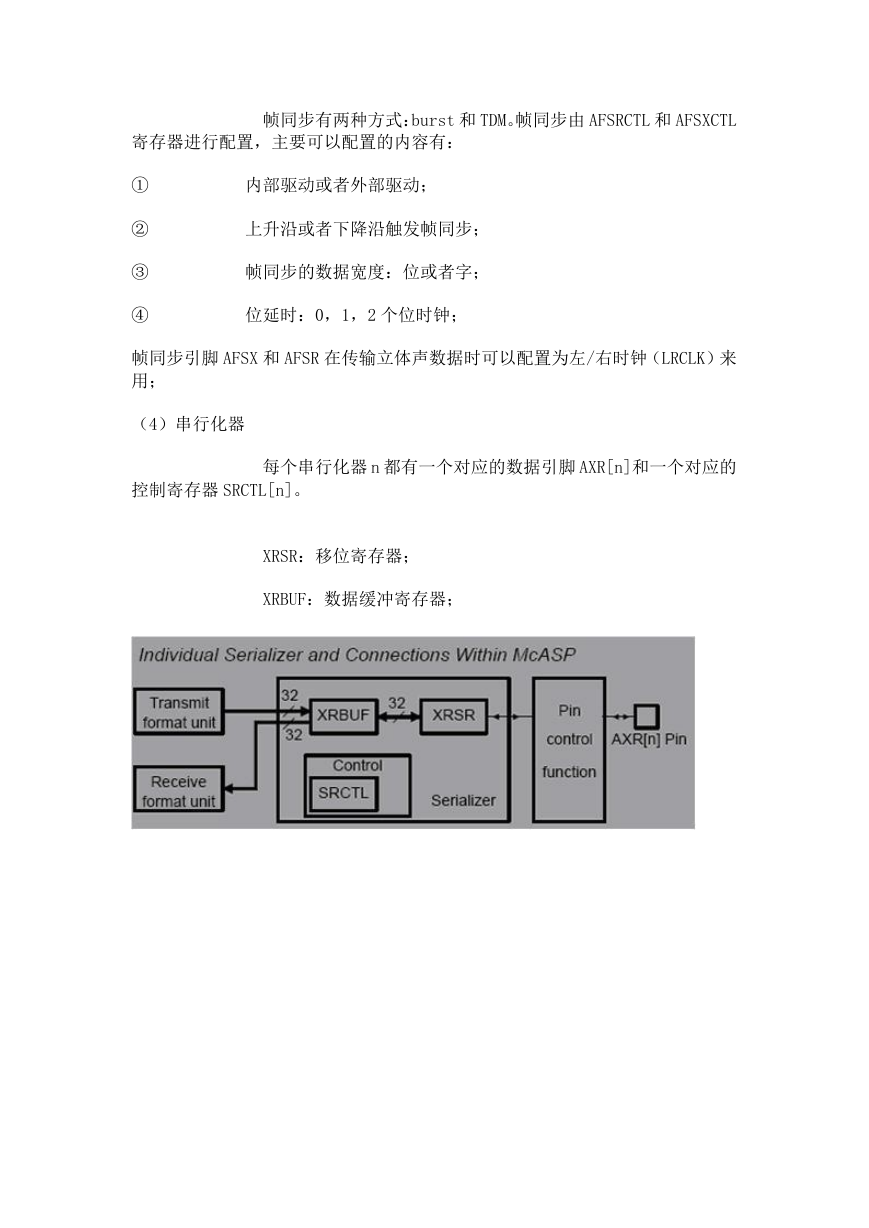

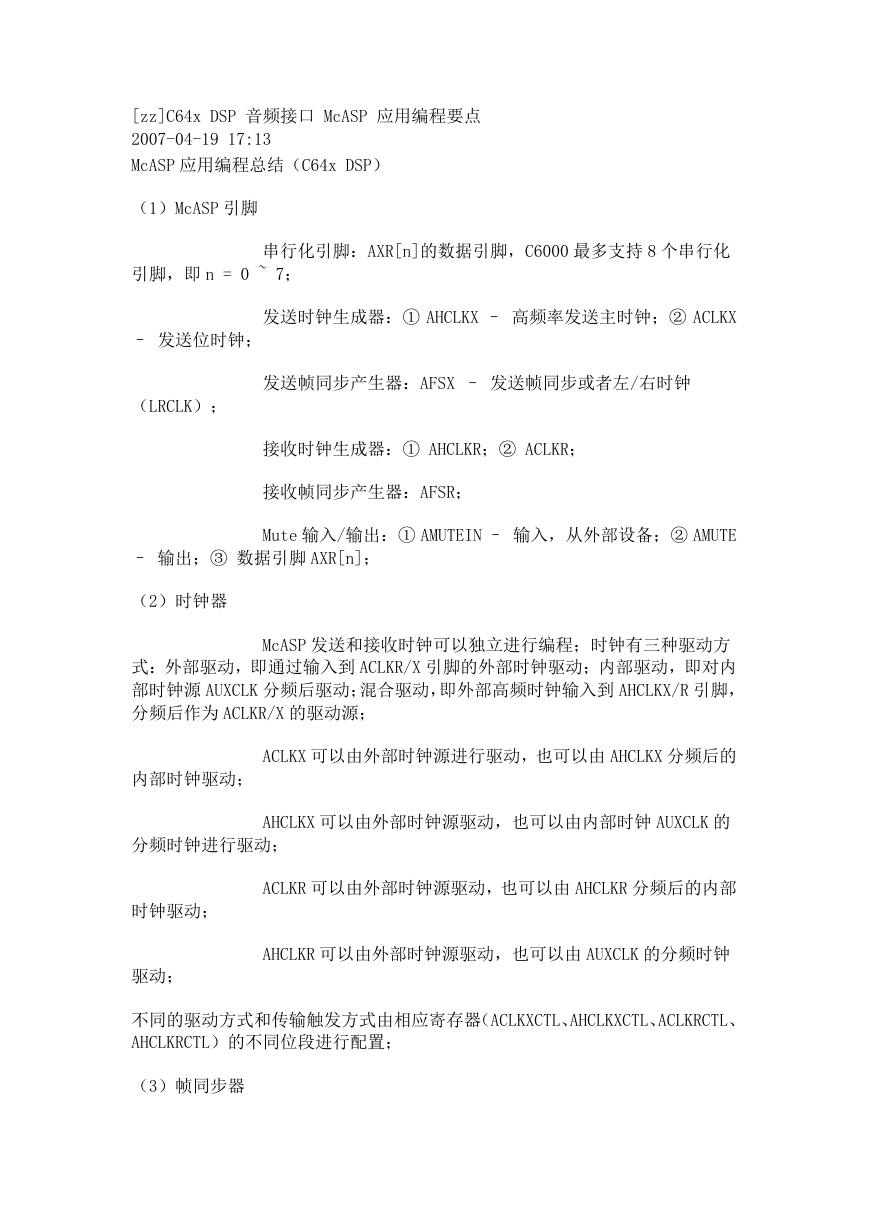

(1)McASP 引脚

串行化引脚:AXR[n]的数据引脚,C6000 最多支持 8 个串行化

引脚,即 n = 0 ~ 7;

发送时钟生成器:① AHCLKX – 高频率发送主时钟;② ACLKX

– 发送位时钟;

(LRCLK);

发送帧同步产生器:AFSX – 发送帧同步或者左/右时钟

接收时钟生成器:① AHCLKR;② ACLKR;

接收帧同步产生器:AFSR;

Mute 输入/输出:① AMUTEIN – 输入,从外部设备;② AMUTE

– 输出;③ 数据引脚 AXR[n];

(2)时钟器

McASP 发送和接收时钟可以独立进行编程;时钟有三种驱动方

式:外部驱动,即通过输入到 ACLKR/X 引脚的外部时钟驱动;内部驱动,即对内

部时钟源 AUXCLK 分频后驱动;混合驱动,即外部高频时钟输入到 AHCLKX/R 引脚,

分频后作为 ACLKR/X 的驱动源;

ACLKX 可以由外部时钟源进行驱动,也可以由 AHCLKX 分频后的

内部时钟驱动;

AHCLKX 可以由外部时钟源驱动,也可以由内部时钟 AUXCLK 的

分频时钟进行驱动;

ACLKR 可以由外部时钟源驱动,也可以由 AHCLKR 分频后的内部

时钟驱动;

驱动;

AHCLKR 可以由外部时钟源驱动,也可以由 AUXCLK 的分频时钟

不同的驱动方式和传输触发方式由相应寄存器(ACLKXCTL、AHCLKXCTL、ACLKRCTL、

AHCLKRCTL)的不同位段进行配置;

(3)帧同步器

�

帧同步有两种方式:burst 和 TDM。帧同步由 AFSRCTL 和 AFSXCTL

寄存器进行配置,主要可以配置的内容有:

①

②

③

④

内部驱动或者外部驱动;

上升沿或者下降沿触发帧同步;

帧同步的数据宽度:位或者字;

位延时:0,1,2 个位时钟;

帧同步引脚 AFSX 和 AFSR 在传输立体声数据时可以配置为左/右时钟(LRCLK)来

用;

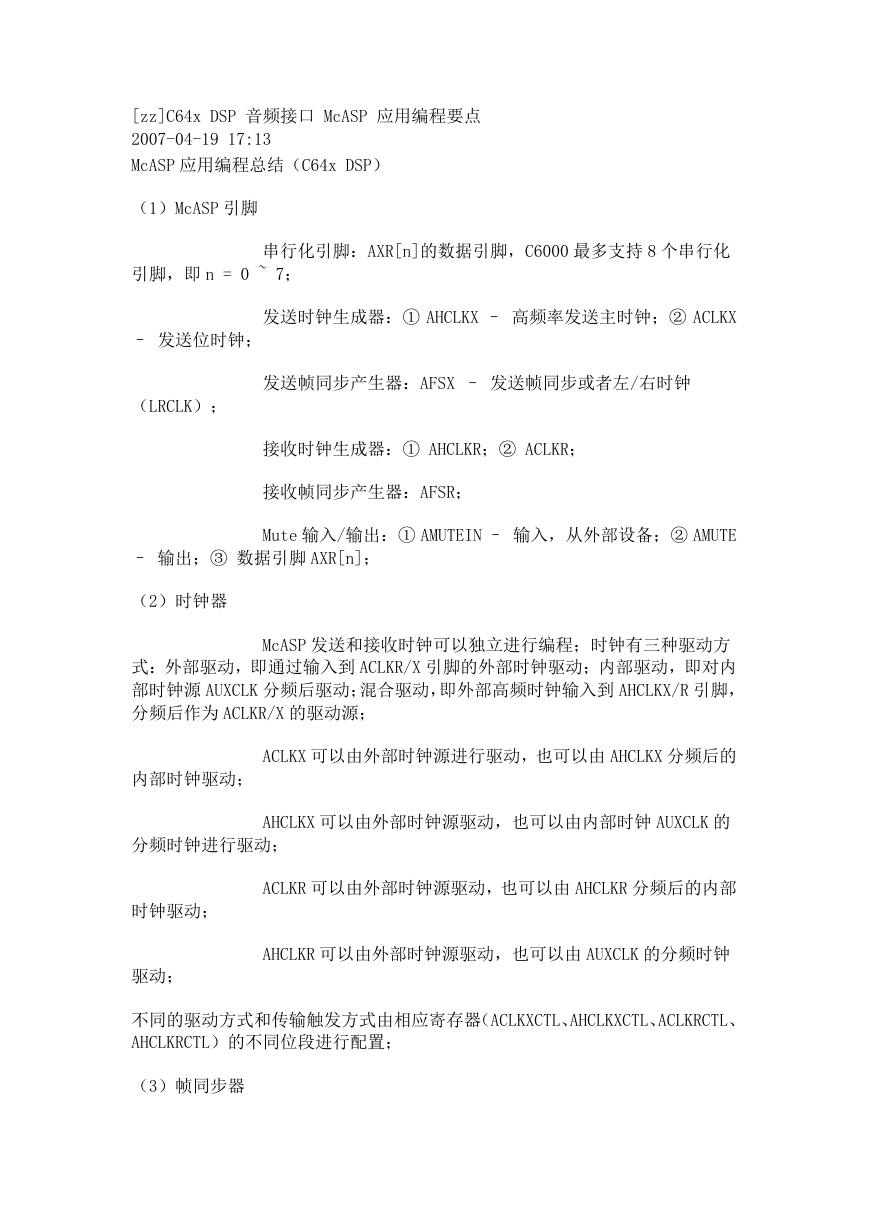

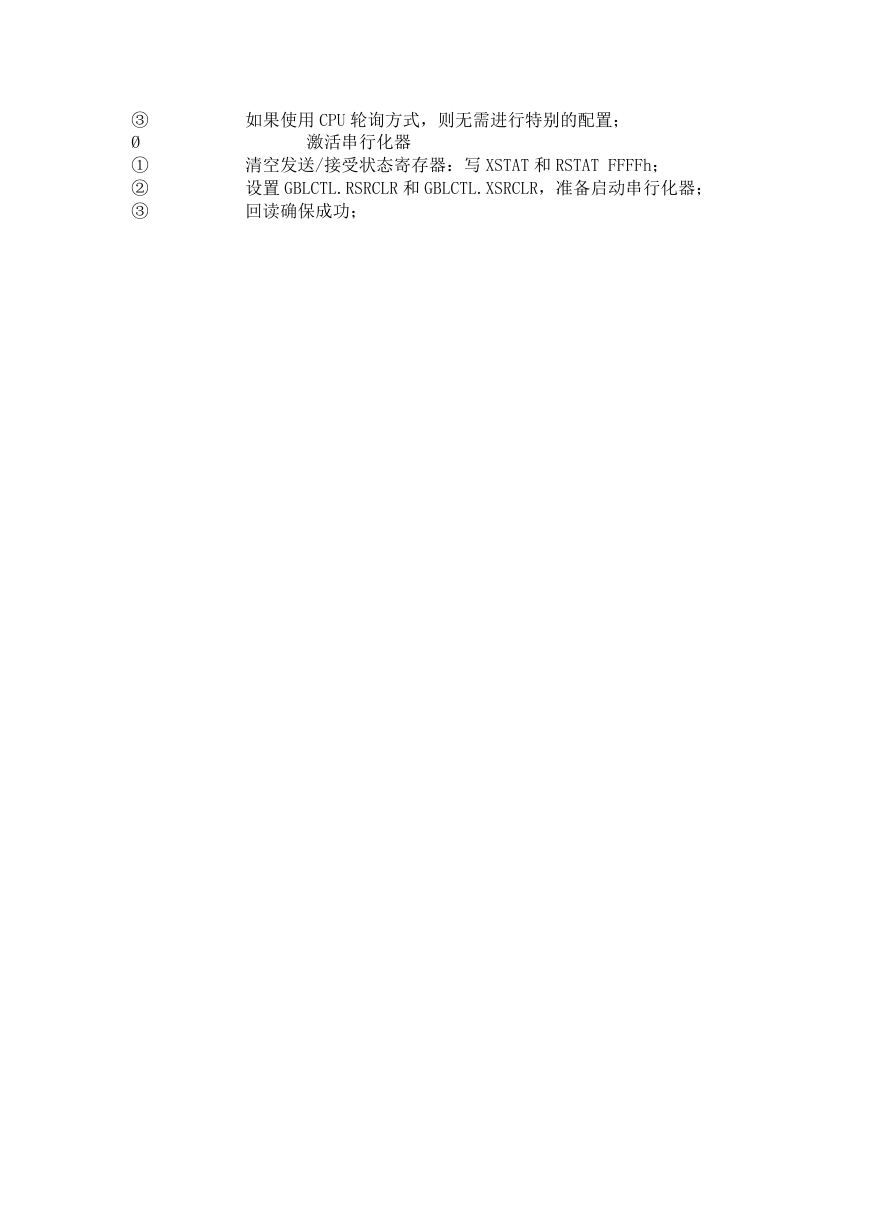

(4)串行化器

每个串行化器 n 都有一个对应的数据引脚 AXR[n]和一个对应的

控制寄存器 SRCTL[n]。

XRSR:移位寄存器;

XRBUF:数据缓冲寄存器;

�

(5)格式化单元

格式化单元(传输字以及 word 在 slot 中的数据对齐、填充等)

位掩码和填充(掩码数据位,进行符号扩展);

循环右移(数据对齐字边界);

由三部分组成,涉及的寄存器是 R/XMASK 和 R/XFMT:

①

接收:RMASK、RPBIT、RPAD;

发送:XMASK、XPBIT、XPAD;

②

接收:RROT;

发送:XRROT;

③

接收:RRVRS;

发送:XRVRS;

(6)状态机

数据反转 (LSB 和 MSB 反转);

① 接收状态机:由 RFMT 寄存器控制,保存 McASP 状态和错误信息于

RSTAT 寄存器中;

�

② 发送状态机:由 XFMT 寄存器控制,保存 McASP 状态和错误信息于

XSTAT 寄存器中;

(7) TDM 序列器

① 接收 TDM 序列器:由 RTDM 寄存器控制,保存当前接收 slot 于 RSLOT

寄存器中;

② 发送 TDM 序列器:由 XTDM 寄存器控制,保存当前接收 slot 于 XSLOT

寄存器中;

(8) 引脚功能控制

除了 AMUTEIN 引脚,所有的引脚均为双向引脚;双向引脚配置

PDSET:PDOUT 别名,PDSET[n] = 1 -> PDOUT[n] = 1(配置 PDSET[n]

PDCLR:PDOUT 别名,PDSET[n] = 0 -> PDOUT[n] = 0 。。。;

如果涉及到外部时钟驱动,则需首先保证外部时钟的正常

设置 GBLCTL = 0,重置 McASP;

按序配置除了 GBLCTL 外的所有 McASP 寄存器:

电源和仿真器管理寄存器:PWRDEMU;

PFUNC 寄存器:配置为 McASP 或 GPIO;

PDIR 寄存器:配置为输入或输出;

PDIN 寄存器:配置为数据输入引脚;

PDOUT:当引脚配置为 GPIO 输出时,配置为数据输出引脚;当配

为 McASP 引脚或者 GPIO 引脚,由以下寄存器控制:

①

②

③

④

置为 McASP 引脚时,无用;

⑤

= 0 时无作用);只在引脚配置为 GPIO 输出时有效;

⑥

(9)发送/接收部件初始化

Ø

设置和工作;

Ø

Ø

①

② 接收寄存器:RMASK,RFMT,AFSRCTL,ACLKRCTL,AHCLKRCTL,RTDM,RINTCTL,

RCLKCHK;如果 ACLKR、AHCLKR 使用了外部时钟源,则必须首先与 GBLCTL 寄存器

同步;

③ 发送寄存器:。。。;

④ 全局寄存器:PFUNC,PDIR,DITCTL,DLBCTL 和 AMUTE;PDIR 必须在时钟寄

存器和帧同步寄存器配置好之后才能配置;

⑤ DIT 模式寄存器:DITCSRA[n],DITCSRB[n],DITUDRA[n]和 DITUDRB[n];

Ø

略此步:

① 设置 GBLCTL. RHCLKRST 和 GBLCTL. XHCLKRST,重置内部高频时钟分频器;

GBLCTL 的所有其它位必须为 0;

② 完成后读回 GBLCTL 相应字段,保证设置成功;

Ø

① 设置 GBLCTL. RCLKRST 和 GBLCTL. XCLKRST,重置内部时钟分频器;GBLCTL

的所有其它位必须保持原来的状态;

② 完成后读回 GBLCTL 相应字段,保证设置成功;

Ø

①

启动;

②

如果使用 EDMA 方式,则启动,即需要在 McASP 重置后还未运行前

如果使用 CPU 中断方式,则启用 McASP 发送/接收中断功能;

如果 AHCLKX 和 AHCLKR 由内部时钟驱动,则启动;否则忽

启动 ACLKX 和 ACLKR(如果它们由外部时钟驱动,则忽略):

配置数据传输方式:

�

③

Ø

①

②

③

如果使用 CPU 轮询方式,则无需进行特别的配置;

激活串行化器

清空发送/接受状态寄存器:写 XSTAT 和 RSTAT FFFFh;

设置 GBLCTL.RSRCLR 和 GBLCTL.XSRCLR,准备启动串行化器;

回读确保成功;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc