揭秘揭秘DSP和和HMM的语音识别系统电路模块设计

的语音识别系统电路模块设计

本文简述了与硬件相关的驱动程序的设计,将硬件驱动程序与语音识别程序综合,编译通过后载入目标板即对

语音信号进行识别。介绍了一个基于DSP的非特定人汉语孤立数字语音识别系统的设计过程,系统通过AD50芯

片将模拟语音信号采集到DSP芯片中,再采用语音识别算法对采集到的信号进行处理,并将识别的结果用LED

输出完成了整个系统设计。

当今社会是数字信息化时代,信用卡号码、电话语音拨号、个人身份证号码、电子密码等都具有数字化特征。同时,随着语音

识别技术的发展,使得对数字的语音识别成为可能。数字语音识别可以识别用户说出的数字,向用户提供最自然、最灵活和最

经济的人机接口界面,从而能有效解决军用和民用领域中遇到的大量数据录入问题。而且,由于电话网络的同益普及,数字自

动语音识别可用于电话人口统计、远程股票交易号码的远程认证等。因此,数字语音识别具有非常高的实用价值。

硬件电路的连接

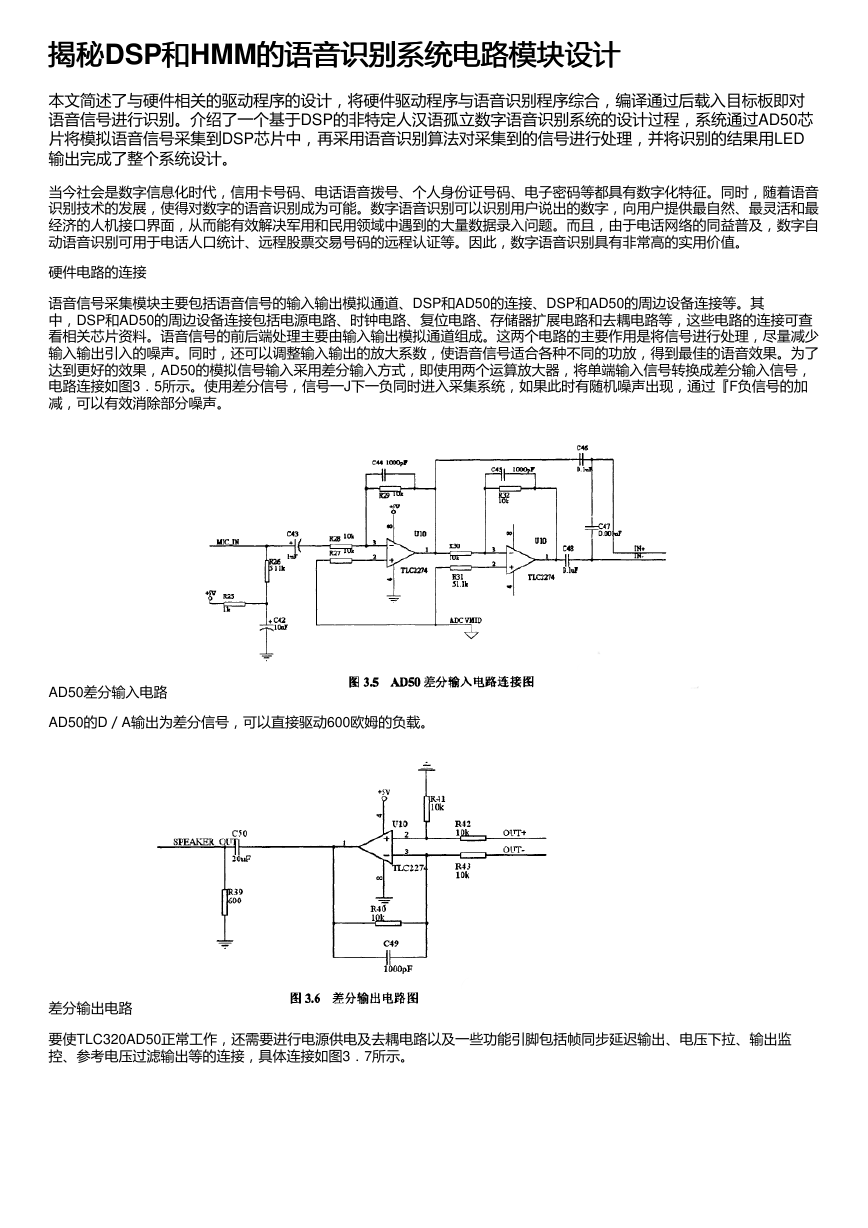

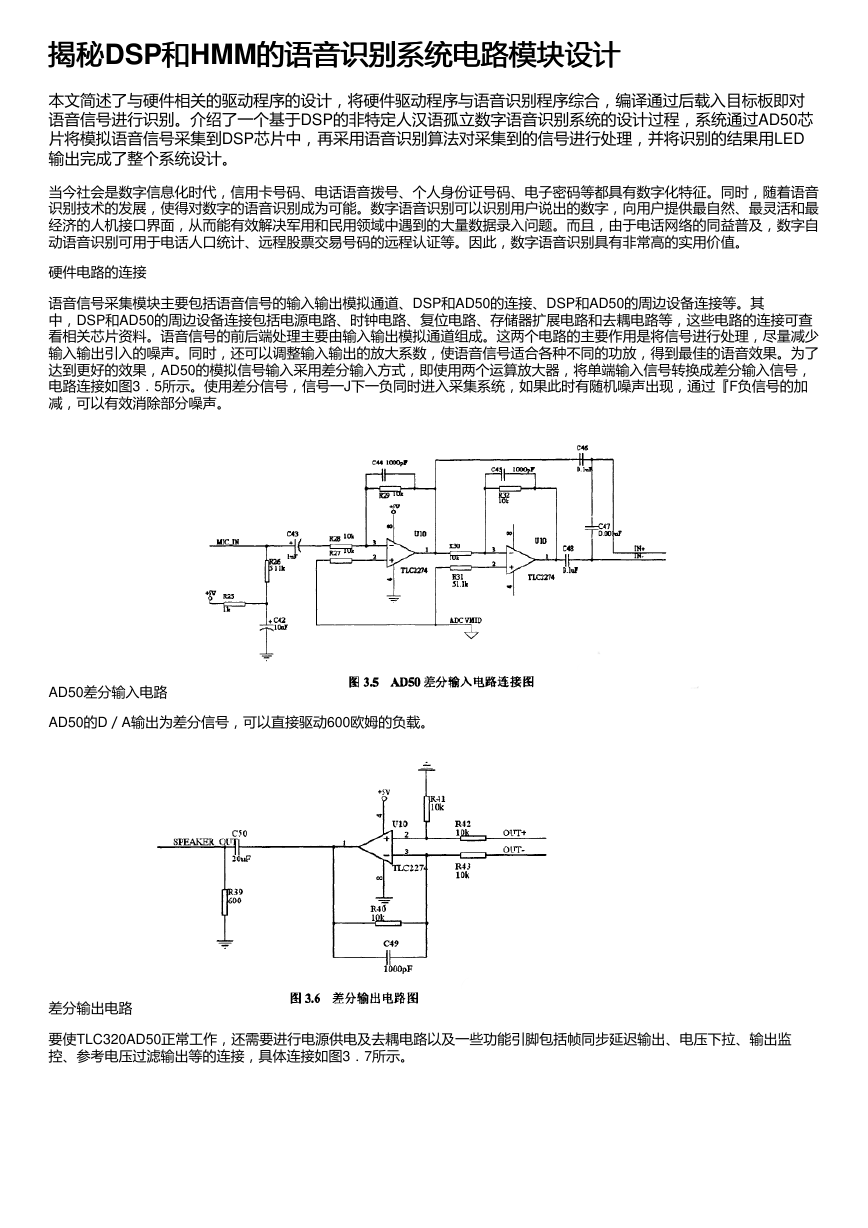

语音信号采集模块主要包括语音信号的输入输出模拟通道、DSP和AD50的连接、DSP和AD50的周边设备连接等。其

中,DSP和AD50的周边设备连接包括电源电路、时钟电路、复位电路、存储器扩展电路和去耦电路等,这些电路的连接可查

看相关芯片资料。语音信号的前后端处理主要由输入输出模拟通道组成。这两个电路的主要作用是将信号进行处理,尽量减少

输入输出引入的噪声。同时,还可以调整输入输出的放大系数,使语音信号适合各种不同的功放,得到最佳的语音效果。为了

达到更好的效果,AD50的模拟信号输入采用差分输入方式,即使用两个运算放大器,将单端输入信号转换成差分输入信号,

电路连接如图3.5所示。使用差分信号,信号一J下一负同时进入采集系统,如果此时有随机噪声出现,通过『F负信号的加

减,可以有效消除部分噪声。

AD50差分输入电路

AD50的D/A输出为差分信号,可以直接驱动600欧姆的负载。

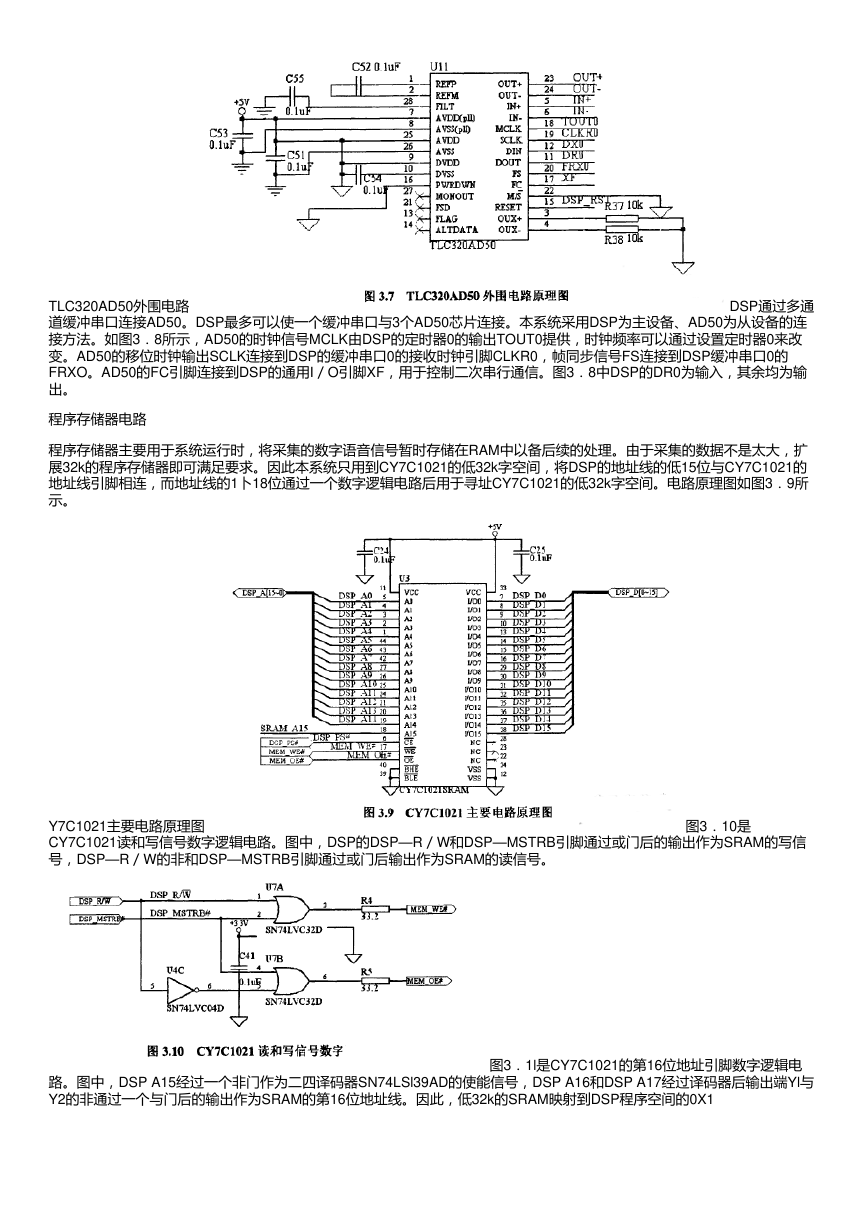

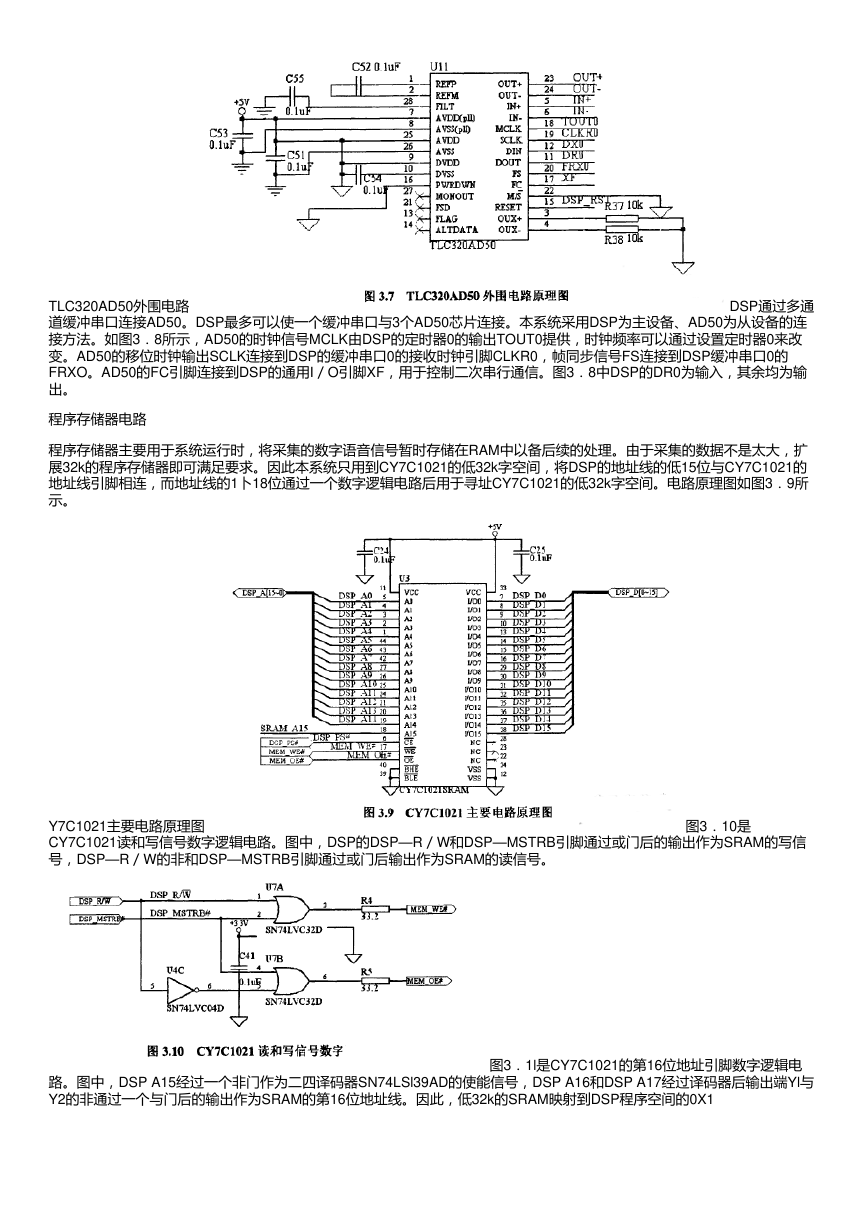

差分输出电路

要使TLC320AD50正常工作,还需要进行电源供电及去耦电路以及一些功能引脚包括帧同步延迟输出、电压下拉、输出监

控、参考电压过滤输出等的连接,具体连接如图3.7所示。

�

TLC320AD50外围电路

DSP通过多通

道缓冲串口连接AD50。DSP最多可以使一个缓冲串口与3个AD50芯片连接。本系统采用DSP为主设备、AD50为从设备的连

接方法。如图3.8所示,AD50的时钟信号MCLK由DSP的定时器0的输出TOUT0提供,时钟频率可以通过设置定时器0来改

变。AD50的移位时钟输出SCLK连接到DSP的缓冲串口0的接收时钟引脚CLKR0,帧同步信号FS连接到DSP缓冲串口0的

FRXO。AD50的FC引脚连接到DSP的通用I/O引脚XF,用于控制二次串行通信。图3.8中DSP的DR0为输入,其余均为输

出。

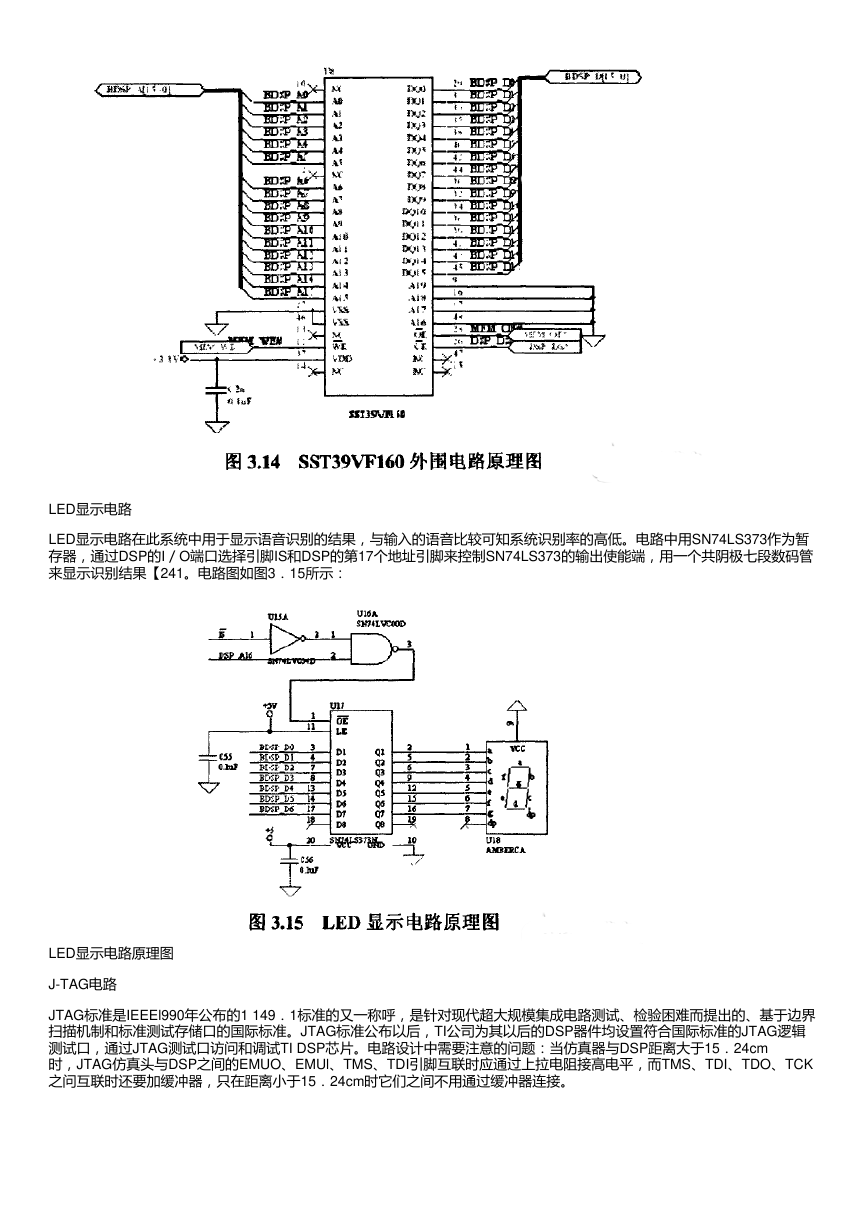

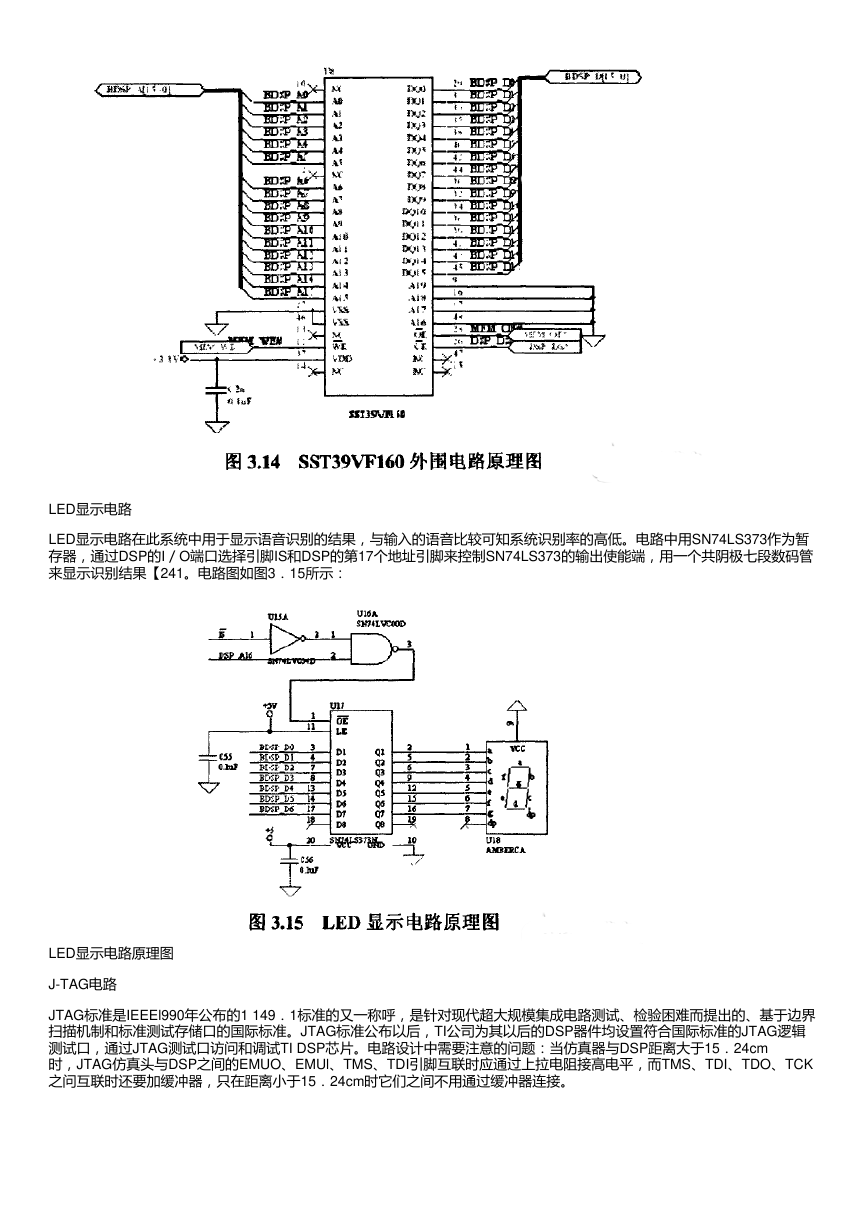

程序存储器电路

程序存储器主要用于系统运行时,将采集的数字语音信号暂时存储在RAM中以备后续的处理。由于采集的数据不是太大,扩

展32k的程序存储器即可满足要求。因此本系统只用到CY7C1021的低32k字空间,将DSP的地址线的低15位与CY7C1021的

地址线引脚相连,而地址线的1卜18位通过一个数字逻辑电路后用于寻址CY7C1021的低32k字空间。电路原理图如图3.9所

示。

Y7C1021主要电路原理图

CY7C1021读和写信号数字逻辑电路。图中,DSP的DSP—R/W和DSP—MSTRB引脚通过或门后的输出作为SRAM的写信

号,DSP—R/W的非和DSP—MSTRB引脚通过或门后输出作为SRAM的读信号。

图3.10是

路。图中,DSP A15经过一个非门作为二四译码器SN74LSl39AD的使能信号,DSP A16和DSP A17经过译码器后输出端Yl与

Y2的非通过一个与门后的输出作为SRAM的第16位地址线。因此,低32k的SRAM映射到DSP程序空间的0X1

图3.1l是CY7C1021的第16位地址引脚数字逻辑电

�

8000__oXlFFFF。

数据存储器电路

数据存储器主要用于存储编译后的系统软件的数据,用于语音识别系统板上电自举。选用flash芯片,是因为flash芯片是电可

擦可写芯片,可以在线对flash进行操作,修改应用程序方便。地址缓冲器和数据缓冲器电路连接分别如图3.12和3.13所

示:

SN74LVTHl6244外围电路

SN74LVTHl6245外围电路原理图

SST39VFl60有1M*16bit的容量,但扩展数据存储器只需64K空间足以,所以电路SST39VFl60的地址线的高4位接地。电路原

理图如图3.14所示:

SST39VFl60外围电路

�

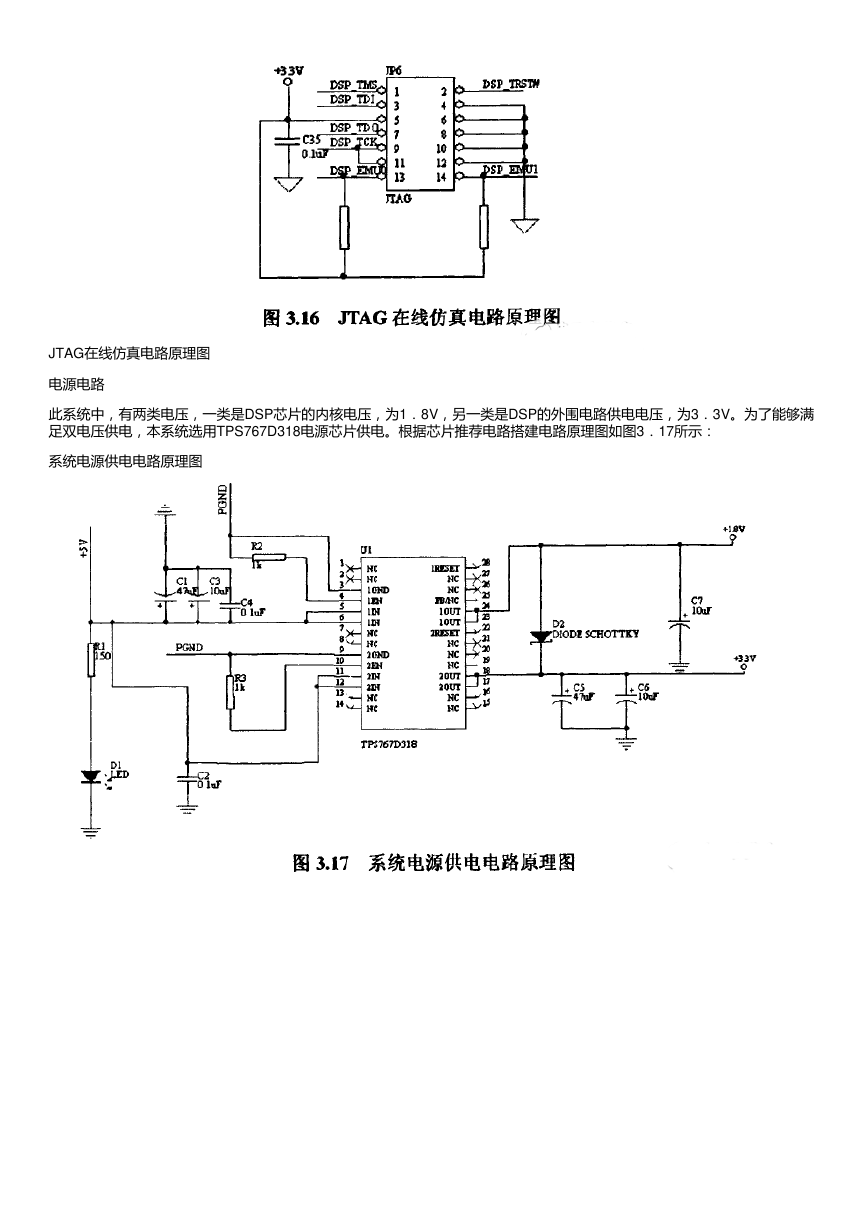

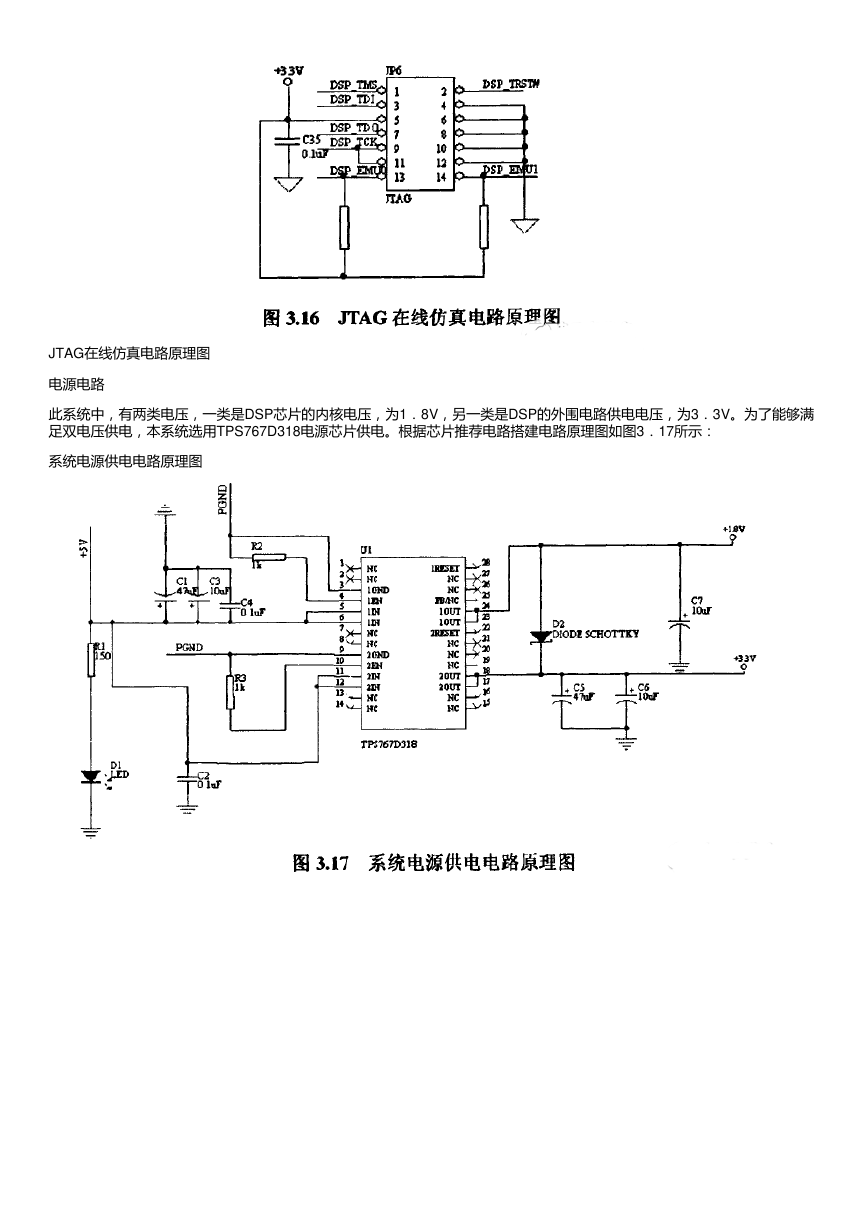

LED显示电路

LED显示电路在此系统中用于显示语音识别的结果,与输入的语音比较可知系统识别率的高低。电路中用SN74LS373作为暂

存器,通过DSP的I/O端口选择引脚IS和DSP的第17个地址引脚来控制SN74LS373的输出使能端,用一个共阴极七段数码管

来显示识别结果【241。电路图如图3.15所示:

LED显示电路原理图

J-TAG电路

JTAG标准是IEEEl990年公布的1 149.1标准的又一称呼,是针对现代超大规模集成电路测试、检验困难而提出的、基于边界

扫描机制和标准测试存储口的国际标准。JTAG标准公布以后,TI公司为其以后的DSP器件均设置符合国际标准的JTAG逻辑

测试口,通过JTAG测试口访问和调试TI DSP芯片。电路设计中需要注意的问题:当仿真器与DSP距离大于15.24cm

时,JTAG仿真头与DSP之间的EMUO、EMUl、TMS、TDI引脚互联时应通过上拉电阻接高电平,而TMS、TDI、TDO、TCK

之问互联时还要加缓冲器,只在距离小于15.24cm时它们之间不用通过缓冲器连接。

�

JTAG在线仿真电路原理图

电源电路

此系统中,有两类电压,一类是DSP芯片的内核电压,为1.8V,另一类是DSP的外围电路供电电压,为3.3V。为了能够满

足双电压供电,本系统选用TPS767D318电源芯片供电。根据芯片推荐电路搭建电路原理图如图3.17所示:

系统电源供电电路原理图

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc