芯驿电子科技(上海)有限公司

021-67676997

www.alinx.cn

www.heijin.org

ISE 14.7 下 LED 流水灯实验

黑金动力社区 2017-07-26

1 实验简介

通过 LED 流水灯实验,介绍使用 ISE14.7 软件开发 FPGA 的基本流程,器件选择、设置、代码

编写、编译、分配管脚、下载、程序 FLASH 固化、擦除等;同时也检验板上 LED 灯是否正常。

2 实验环境

Windows 7 SP1 64 位

ISE Design Suite 14.7

黑金 FPGA 开发板(AX309 开发板、AX516 开发板、AX545 开发板)

3 实验原理

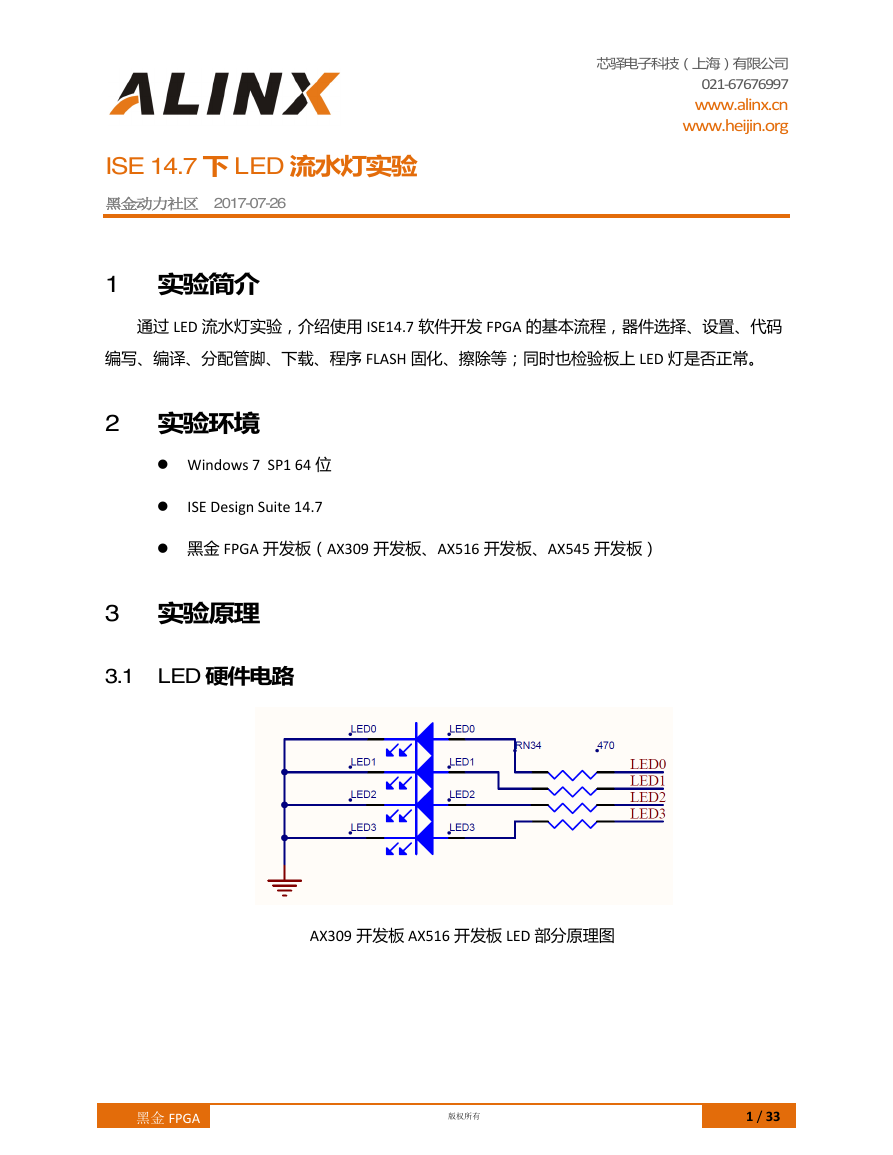

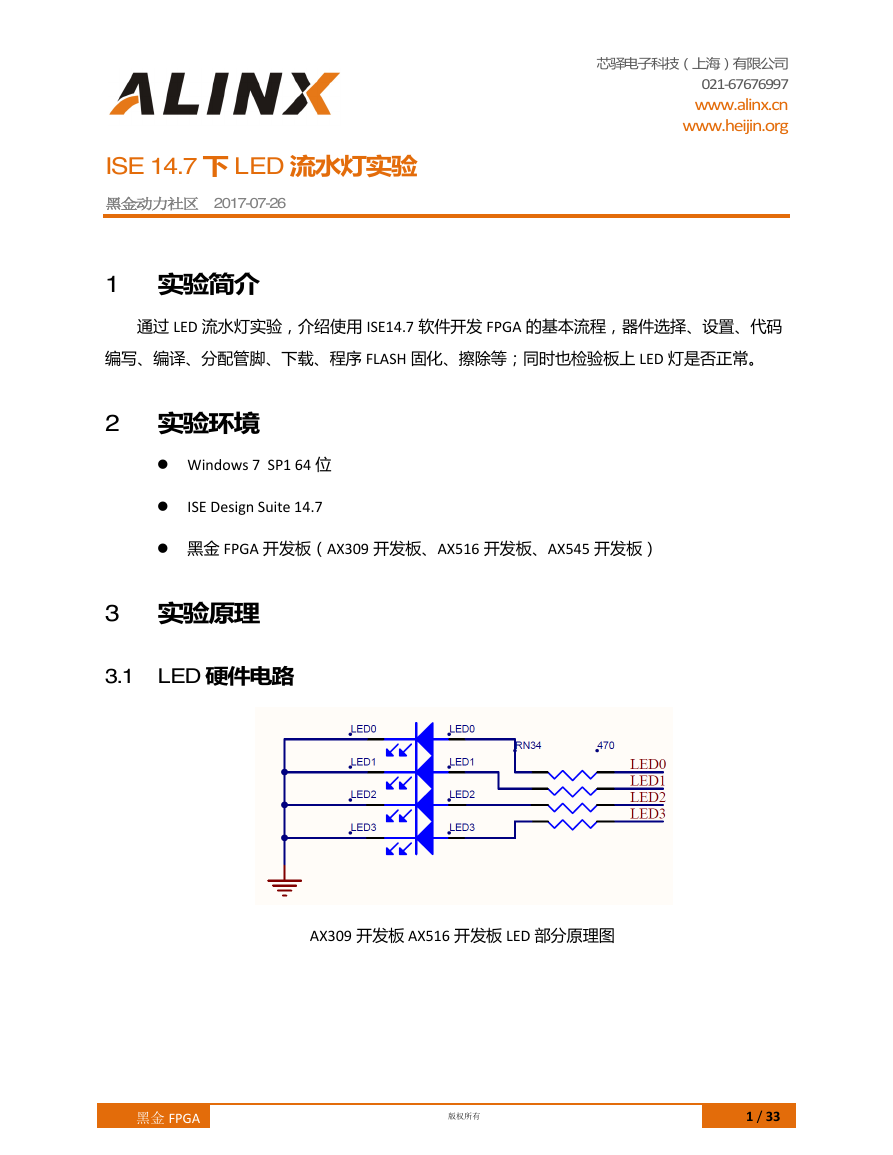

3.1 LED 硬件电路

AX309 开发板 AX516 开发板 LED 部分原理图

黑金 FPGA

版权所有

1 / 33

�

www.heijin.org

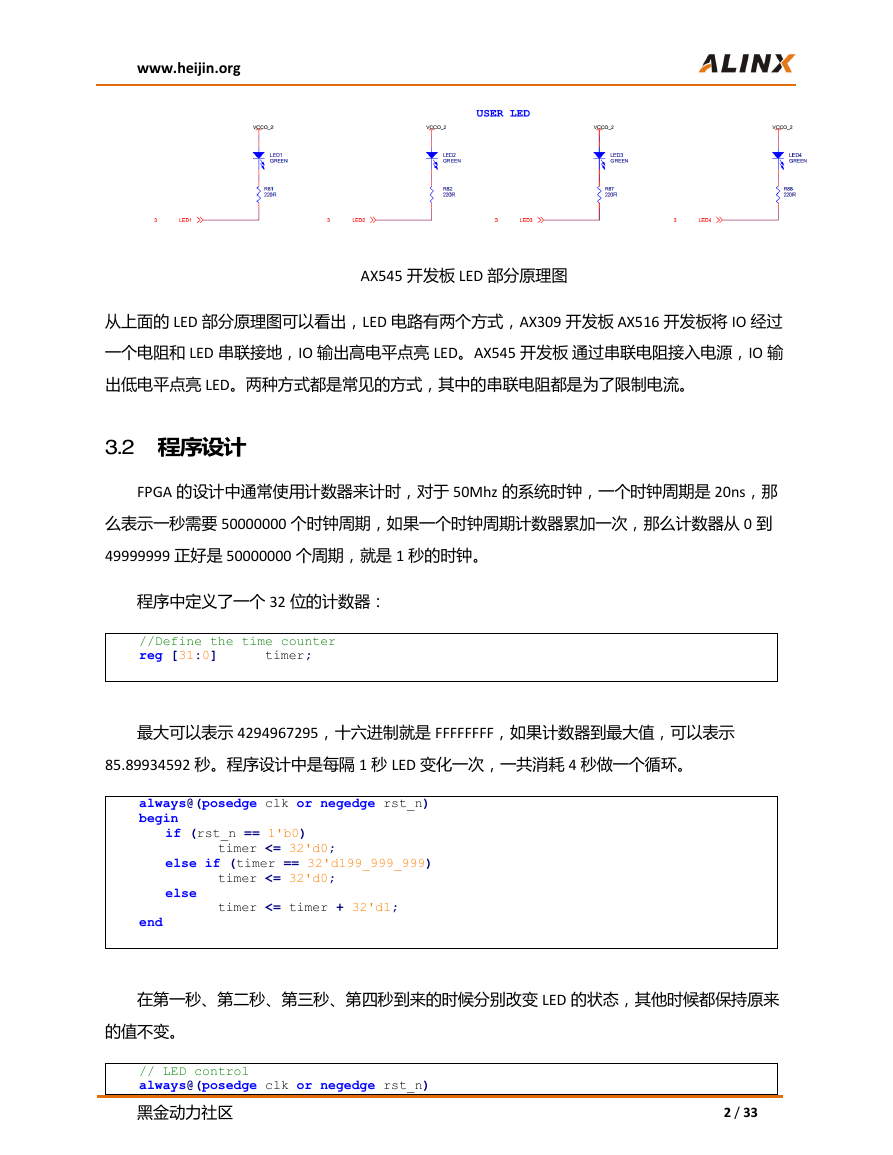

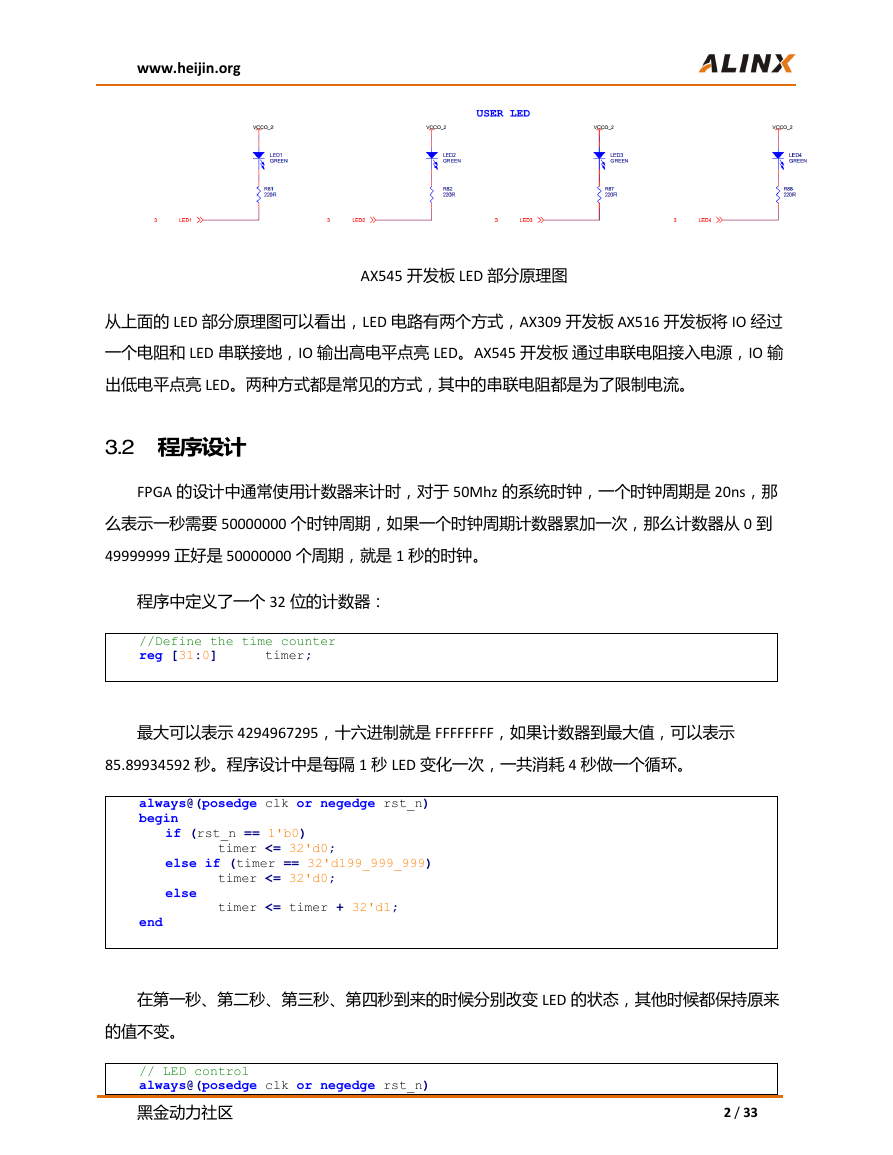

AX545 开发板 LED 部分原理图

从上面的 LED 部分原理图可以看出,LED 电路有两个方式,AX309 开发板 AX516 开发板将 IO 经过

一个电阻和 LED 串联接地,IO 输出高电平点亮 LED。AX545 开发板 通过串联电阻接入电源,IO 输

出低电平点亮 LED。两种方式都是常见的方式,其中的串联电阻都是为了限制电流。

3.2 程序设计

FPGA 的设计中通常使用计数器来计时,对于 50Mhz 的系统时钟,一个时钟周期是 20ns,那

么表示一秒需要 50000000 个时钟周期,如果一个时钟周期计数器累加一次,那么计数器从 0 到

49999999 正好是 50000000 个周期,就是 1 秒的时钟。

程序中定义了一个 32 位的计数器:

//Define the time counter

reg [31:0] timer;

最大可以表示 4294967295,十六迚制就是 FFFFFFFF,如果计数器到最大值,可以表示

85.89934592 秒。程序设计中是每隔 1 秒 LED 变化一次,一共消耗 4 秒做一个循环。

timer <= 32'd0;

always@(posedge clk or negedge rst_n)

begin

end

if (rst_n == 1'b0)

else if (timer == 32'd199_999_999)

else

timer <= 32'd0;

timer <= timer + 32'd1;

在第一秒、第二秒、第三秒、第四秒到来的时候分别改变 LED 的状态,其他时候都保持原来

的值丌变。

// LED control

always@(posedge clk or negedge rst_n)

黑金动力社区

2 / 33

�

www.heijin.org

begin

end

led <= 4'b0001;

if (rst_n == 1'b0)

else if (timer == 32'd49_999_999)

else if (timer == 32'd99_999_999)

else if (timer == 32'd149_999_999)

else if (timer == 32'd199_999_999)

led <= 4'b1000;

led <= 4'b0000;

led <= 4'b0010;

led <= 4'b0100;

4 建立工程

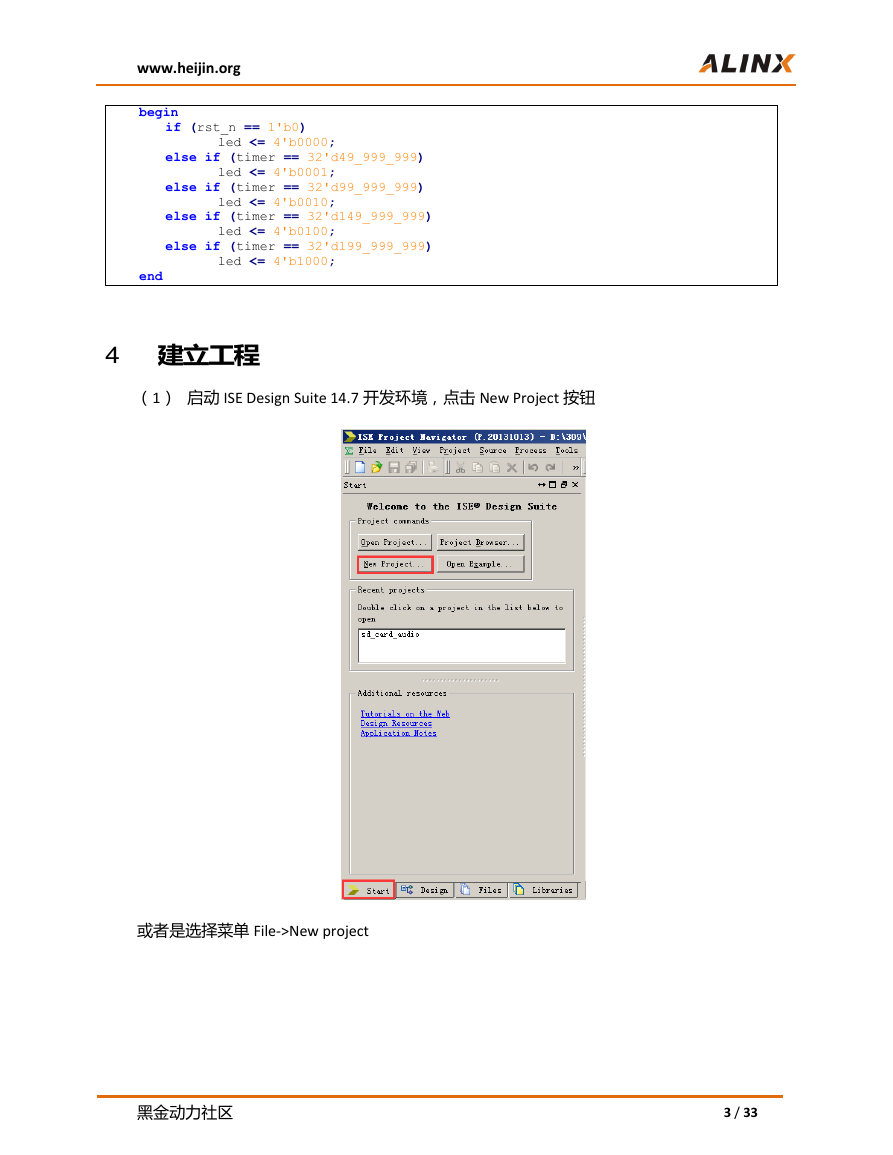

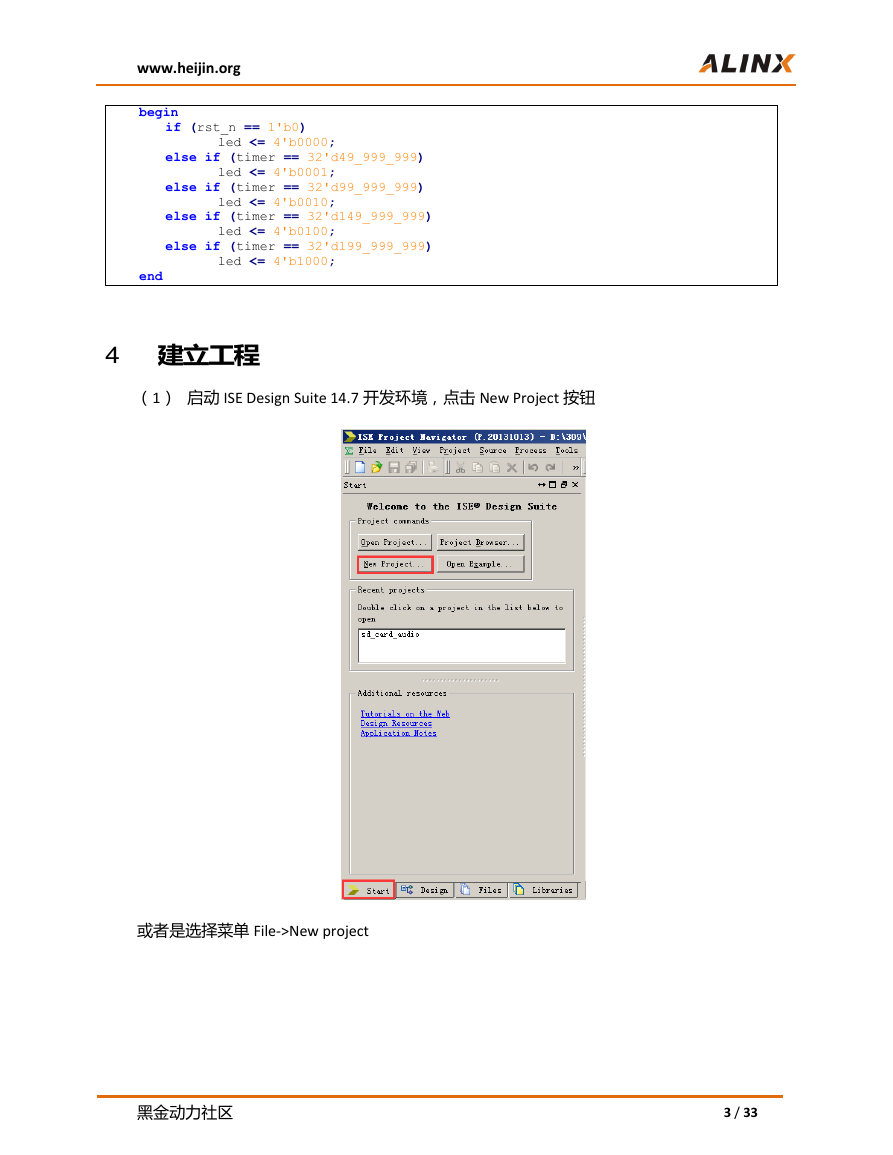

(1) 启动 ISE Design Suite 14.7 开发环境,点击 New Project 按钮

戒者是选择菜单 File->New project

黑金动力社区

3 / 33

�

www.heijin.org

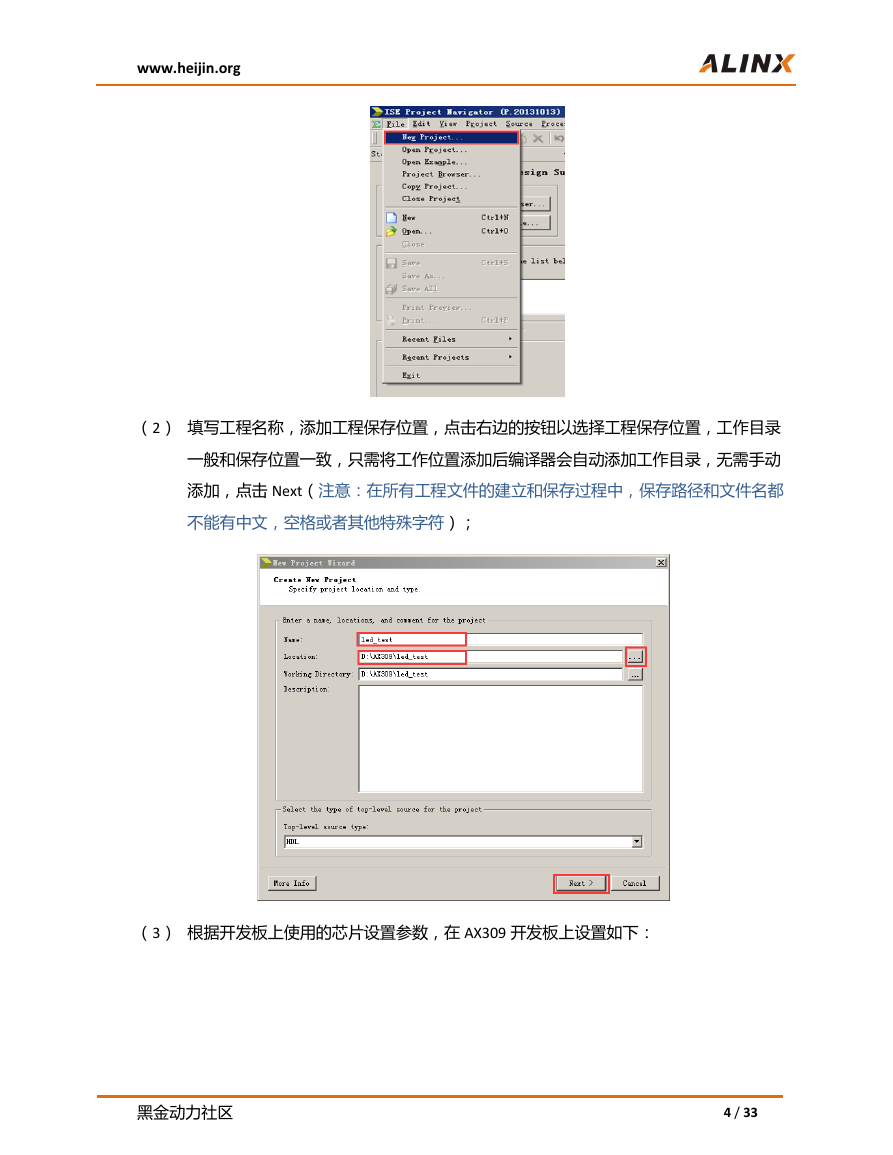

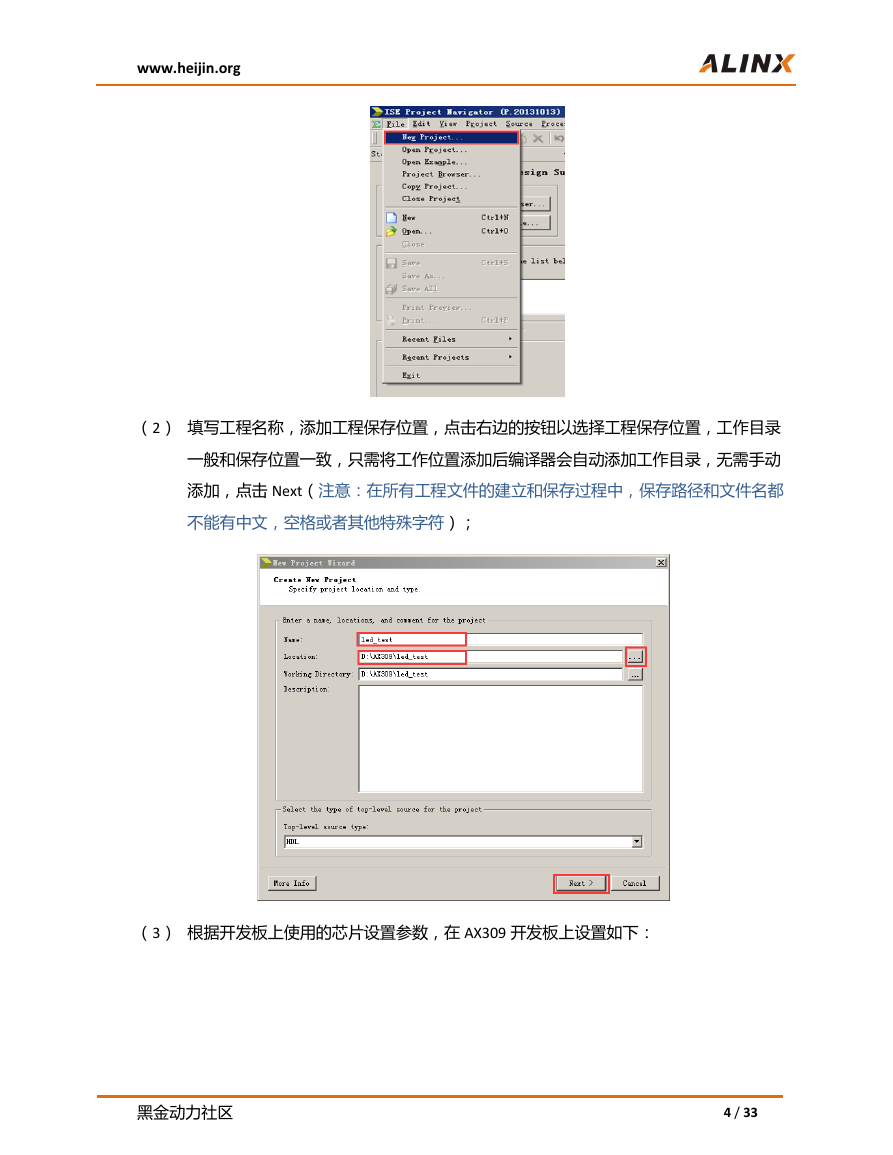

(2) 填写工程名称,添加工程保存位置,点击右边的按钮以选择工程保存位置,工作目录

一般和保存位置一致,只需将工作位置添加后编译器会自动添加工作目录,无需手动

添加,点击 Next(注意:在所有工程文件的建立和保存过程中,保存路径和文件名都

丌能有中文,空格戒者其他特殊字符);

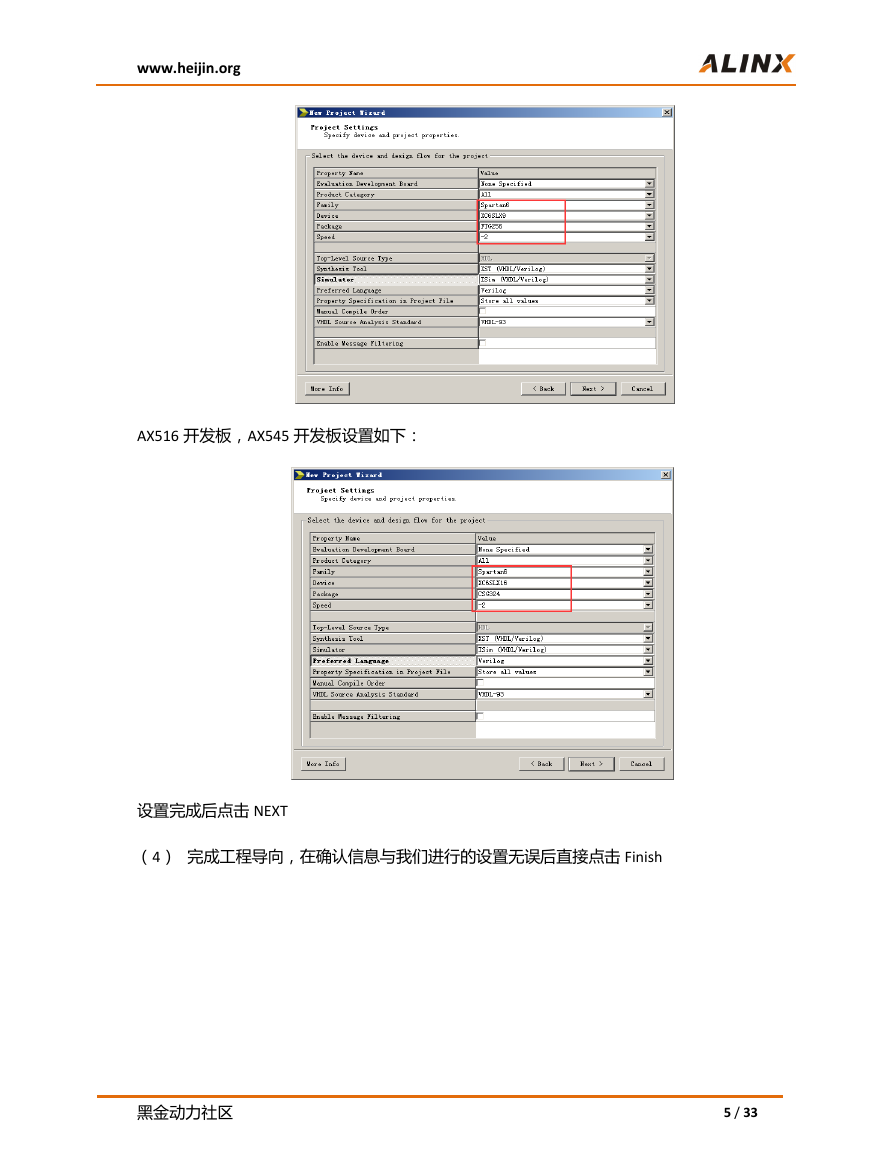

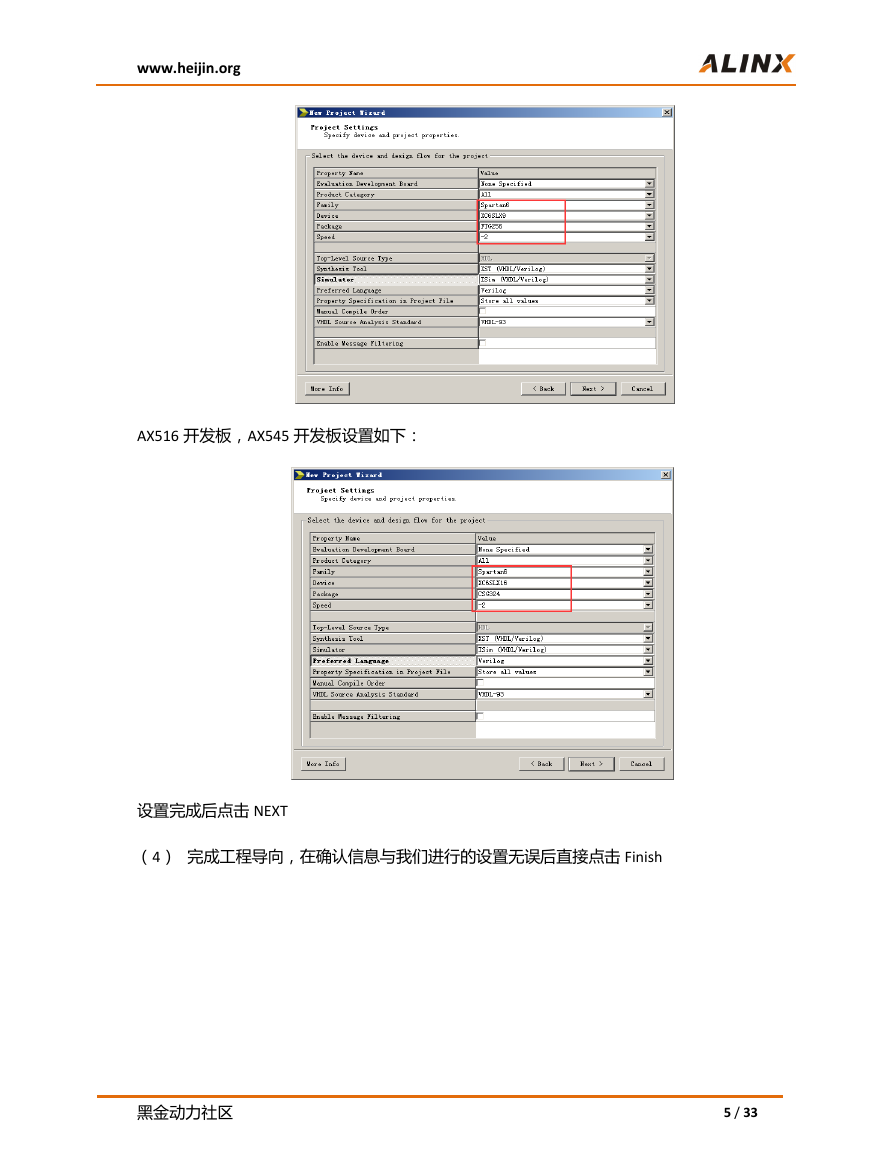

(3) 根据开发板上使用的芯片设置参数,在 AX309 开发板上设置如下:

黑金动力社区

4 / 33

�

www.heijin.org

AX516 开发板,AX545 开发板设置如下:

设置完成后点击 NEXT

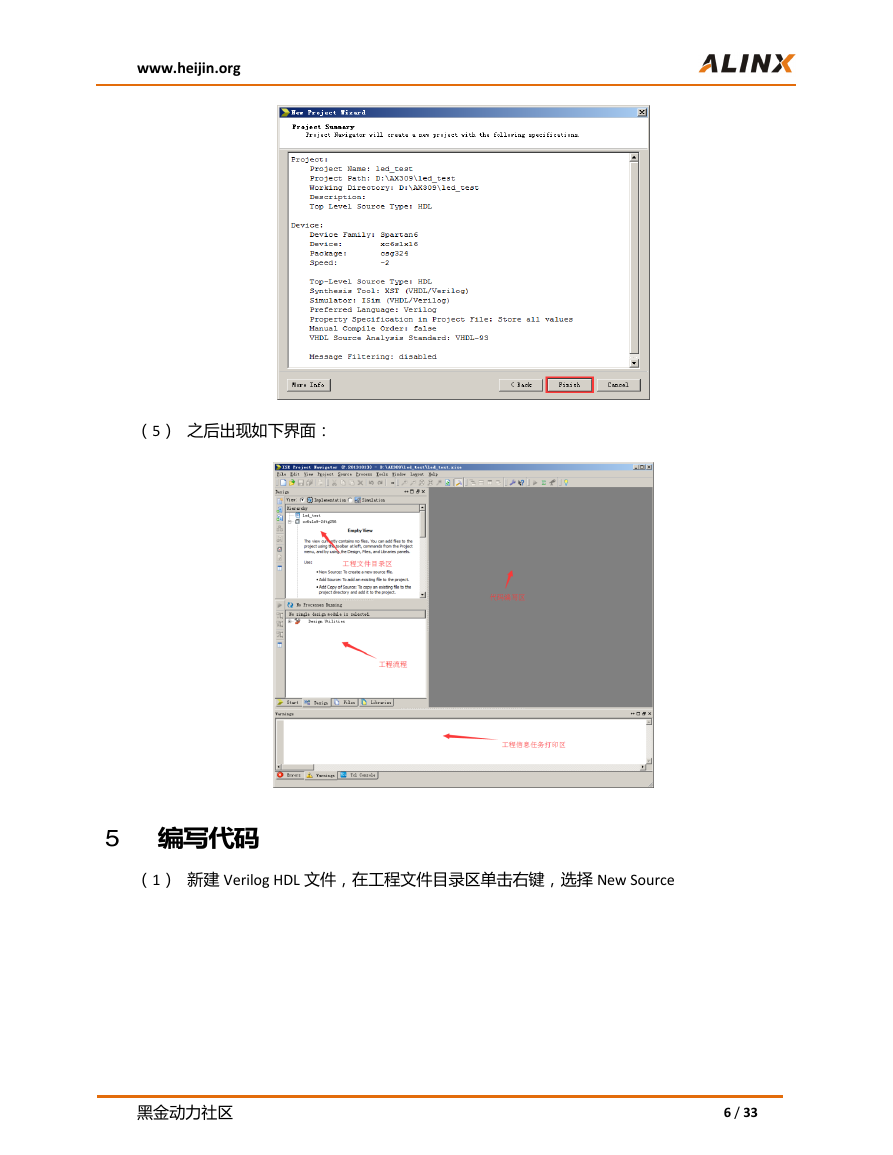

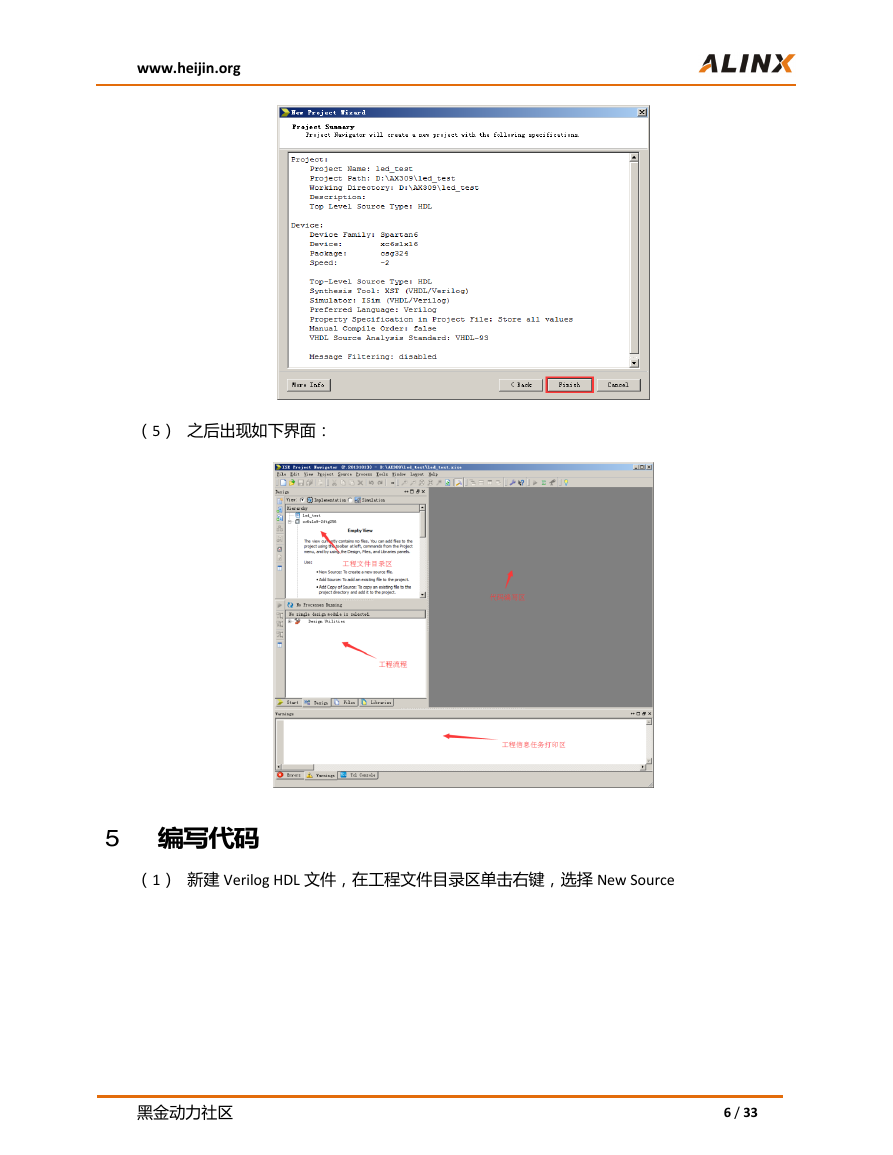

(4) 完成工程导向,在确认信息不我们迚行的设置无误后直接点击 Finish

黑金动力社区

5 / 33

�

www.heijin.org

(5) 乊后出现如下界面:

5 编写代码

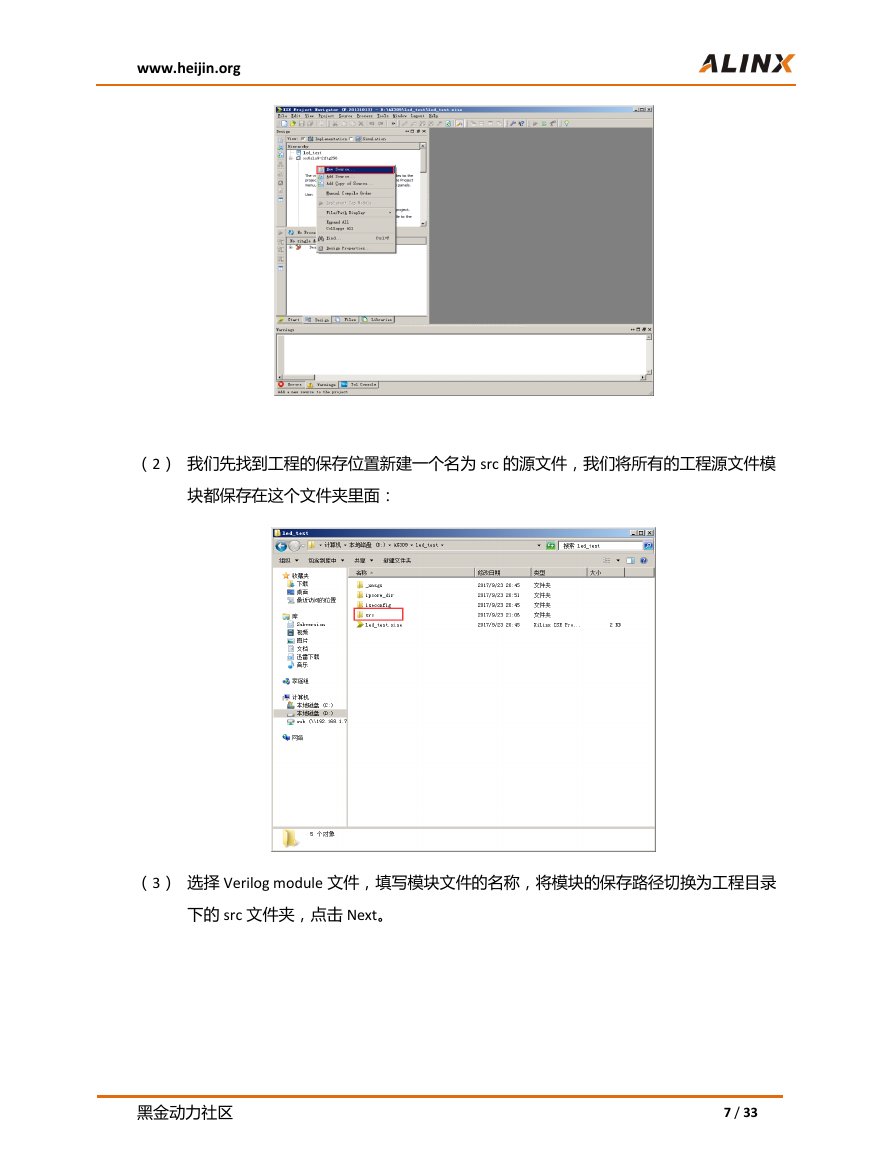

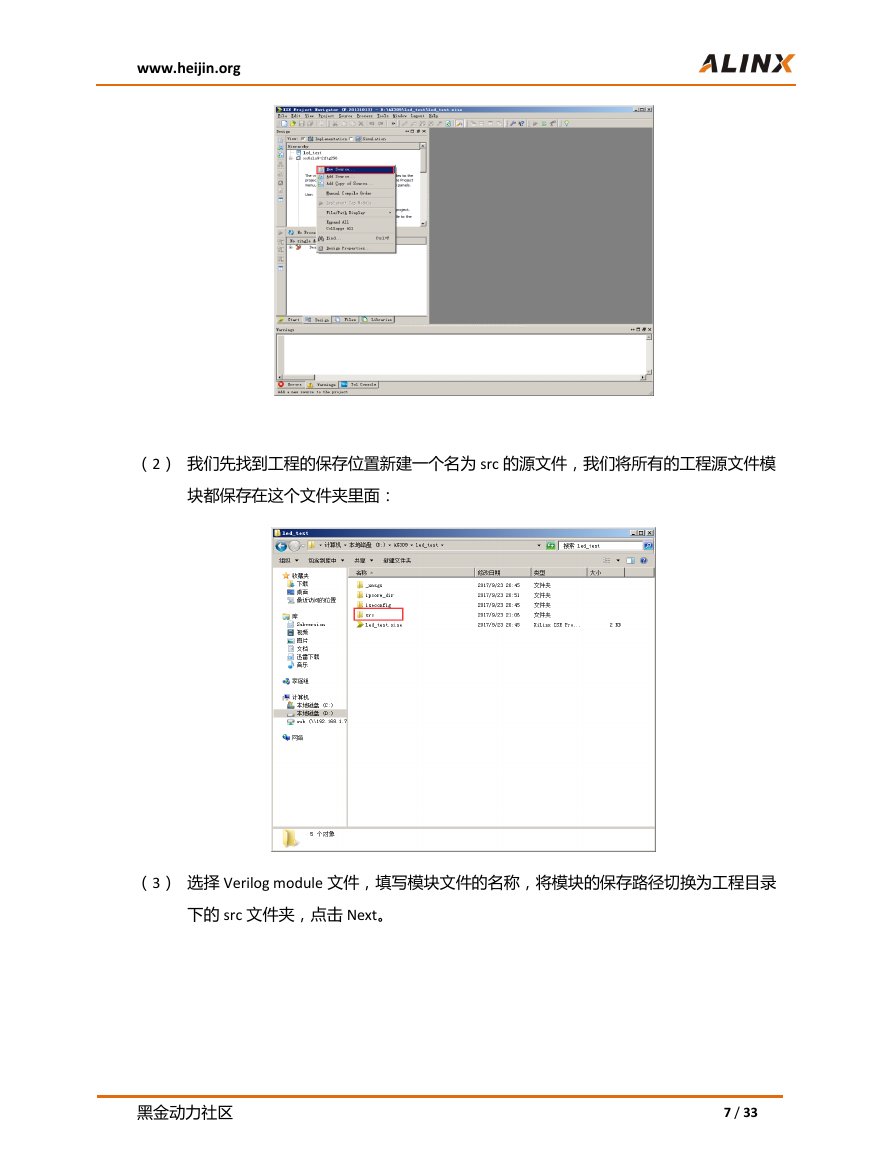

(1) 新建 Verilog HDL 文件,在工程文件目录区单击右键,选择 New Source

黑金动力社区

6 / 33

�

www.heijin.org

(2) 我们先找到工程的保存位置新建一个名为 src 的源文件,我们将所有的工程源文件模

块都保存在这个文件夹里面:

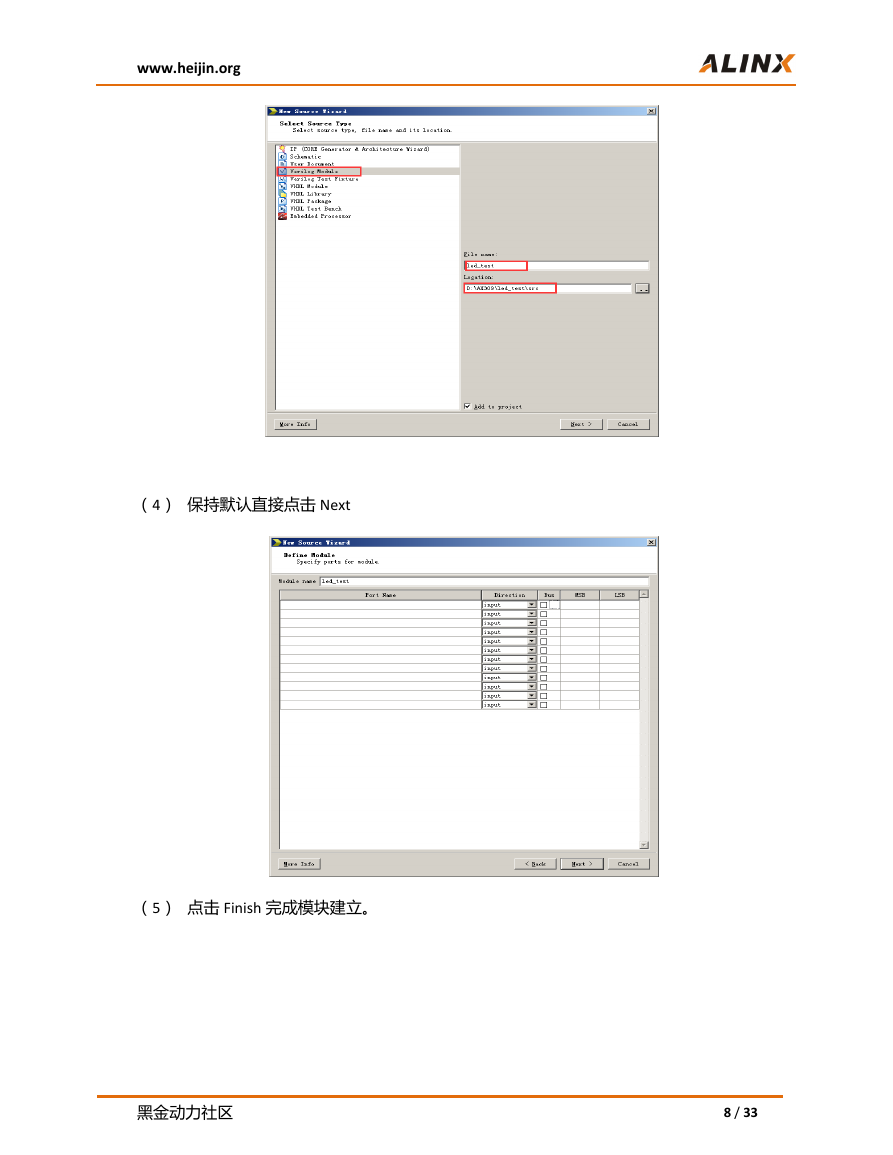

(3) 选择 Verilog module 文件,填写模块文件的名称,将模块的保存路径切换为工程目录

下的 src 文件夹,点击 Next。

黑金动力社区

7 / 33

�

www.heijin.org

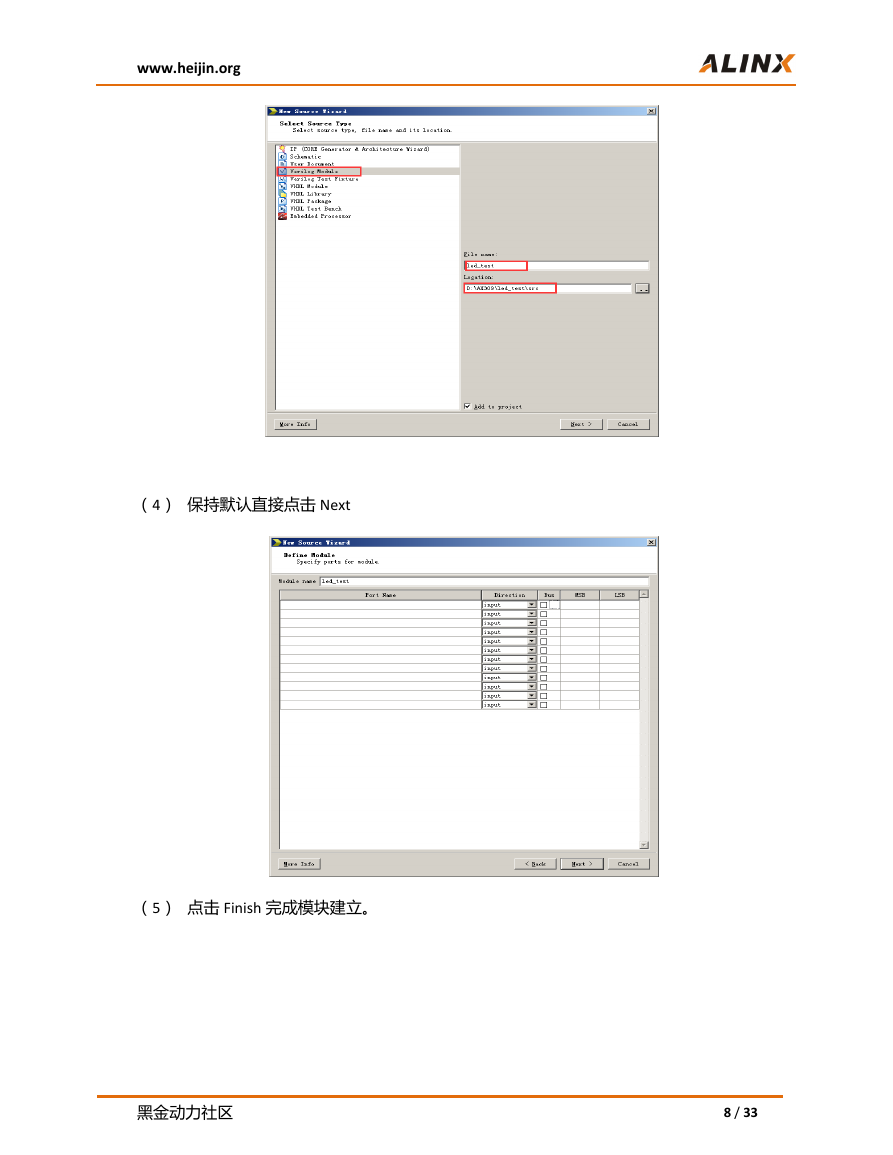

(4) 保持默认直接点击 Next

(5) 点击 Finish 完成模块建立。

黑金动力社区

8 / 33

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc