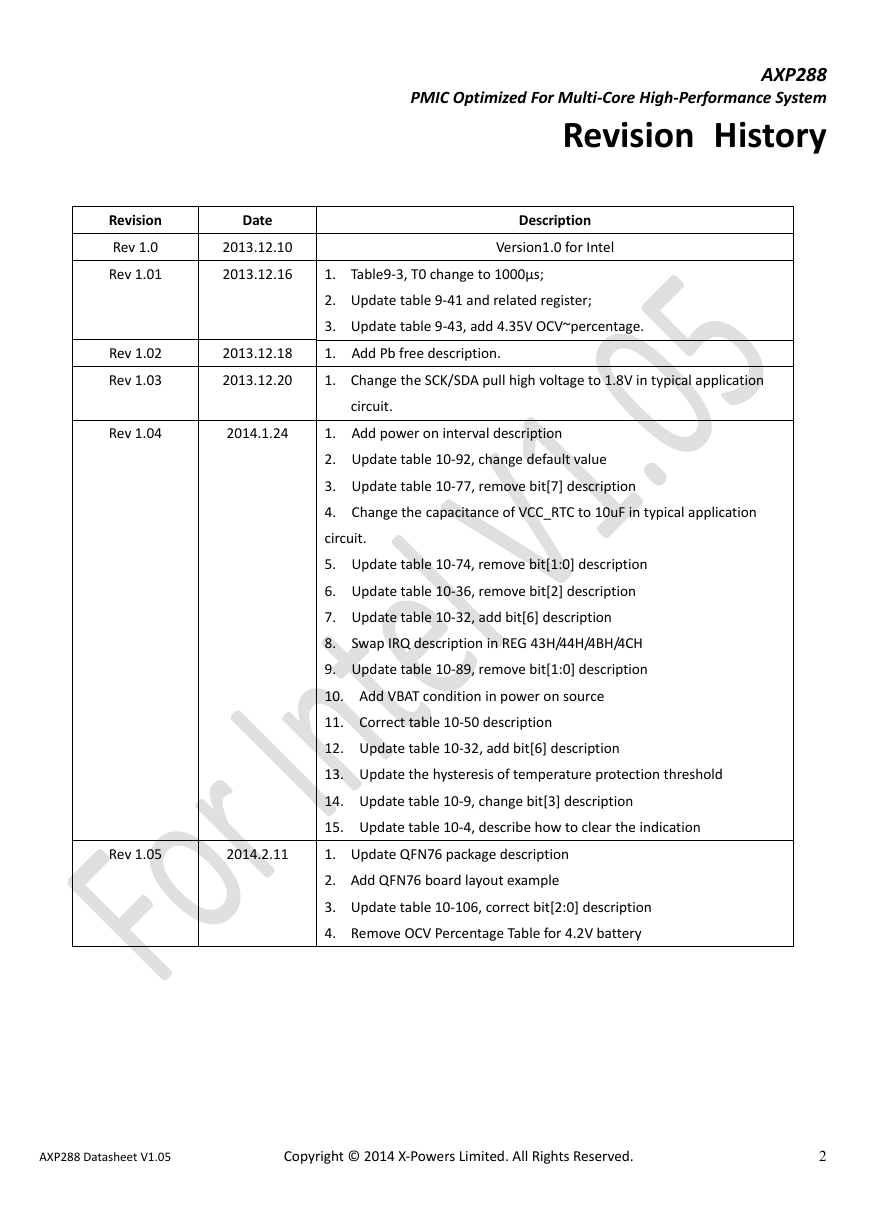

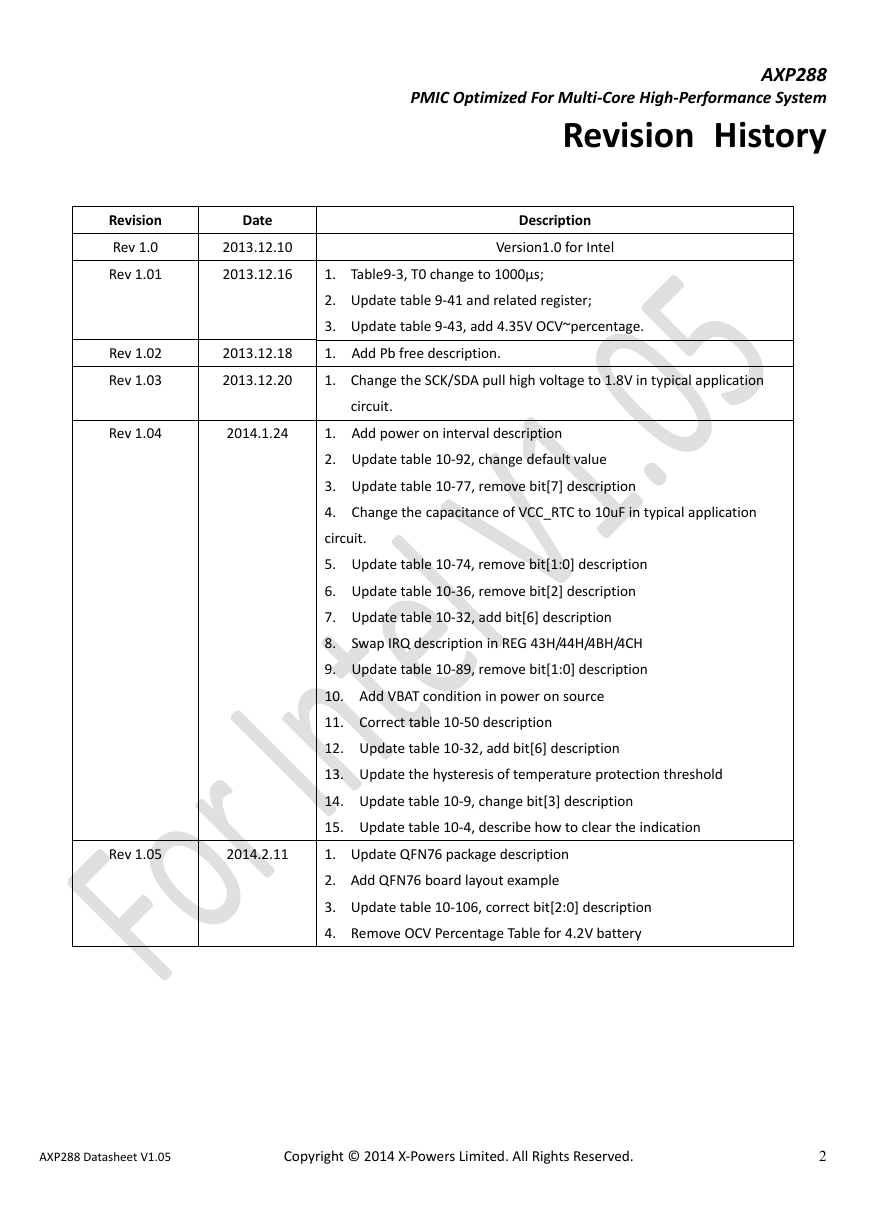

Revision History

Declaration

Catalog

1 Overview

2 Feature

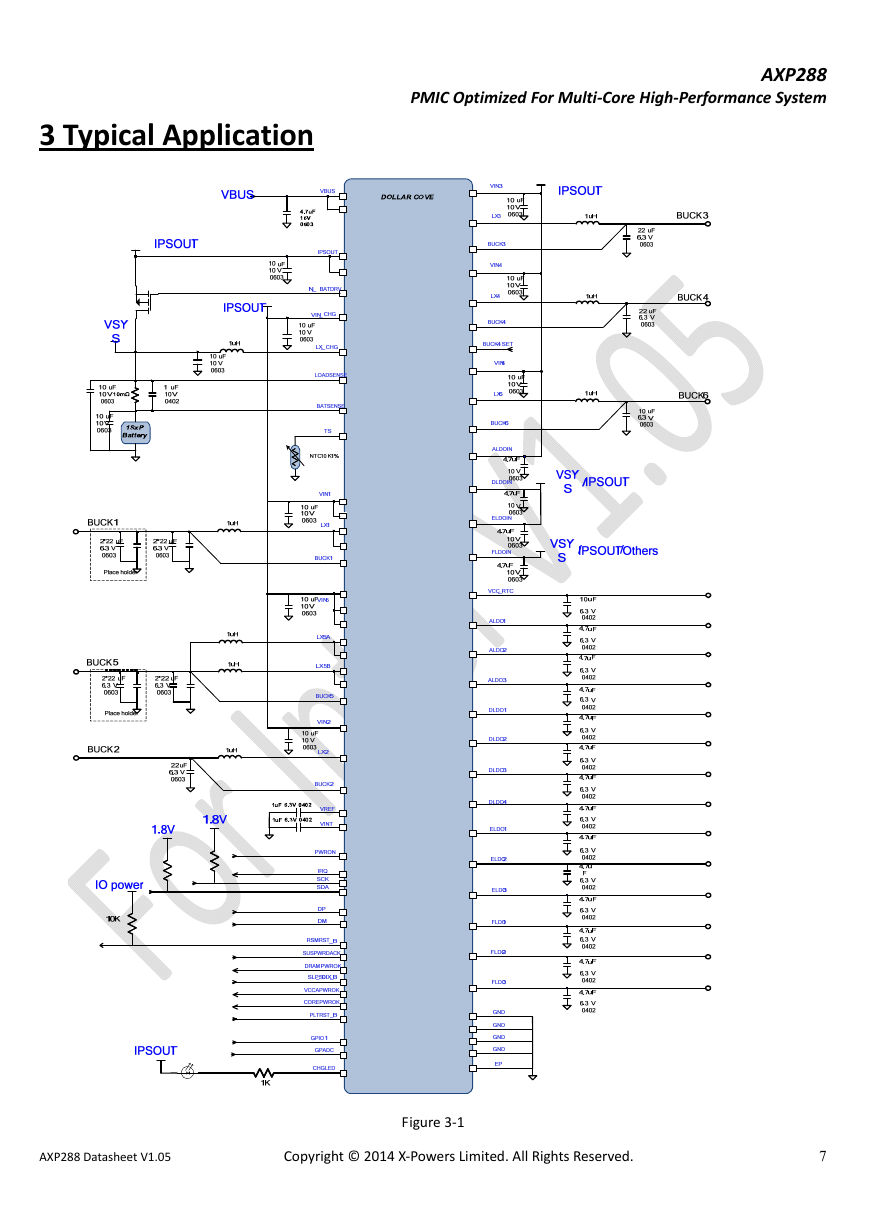

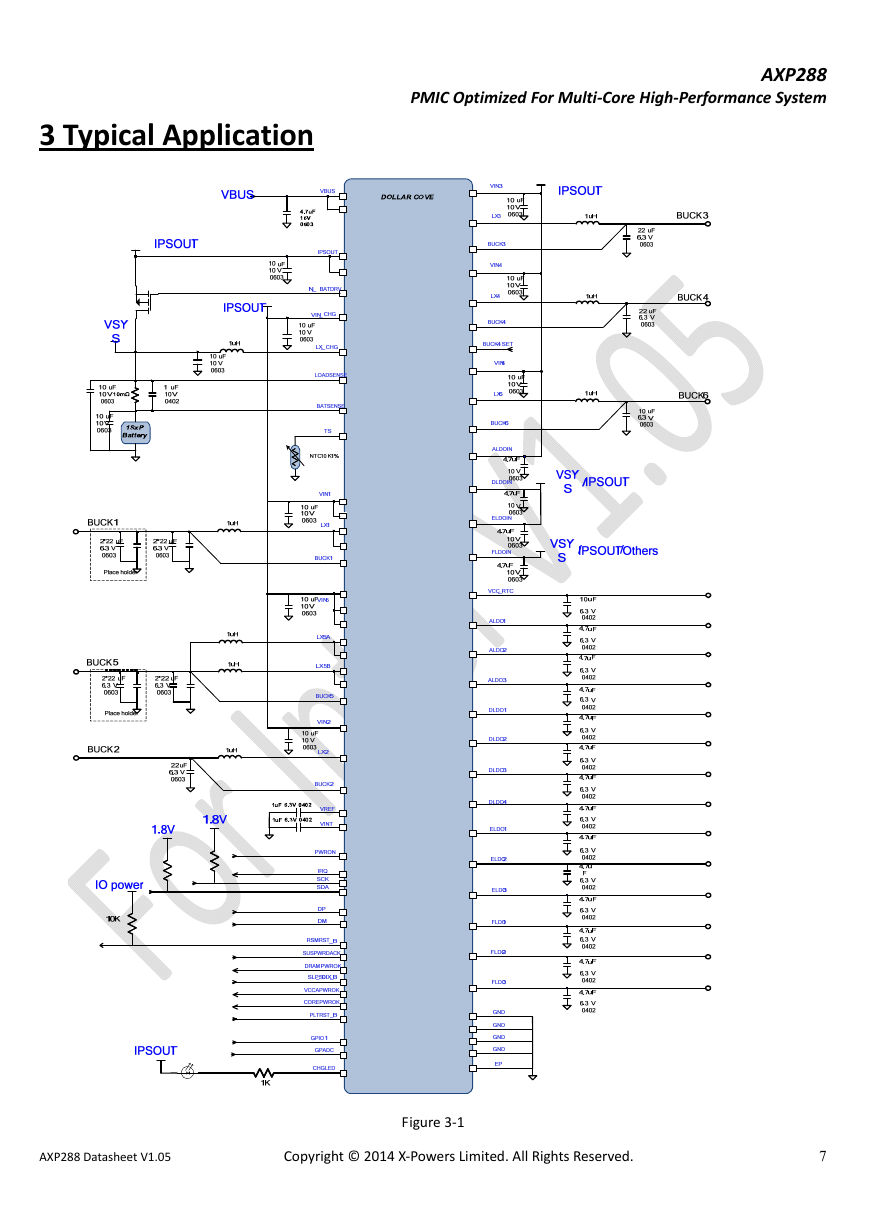

3 Typical Application

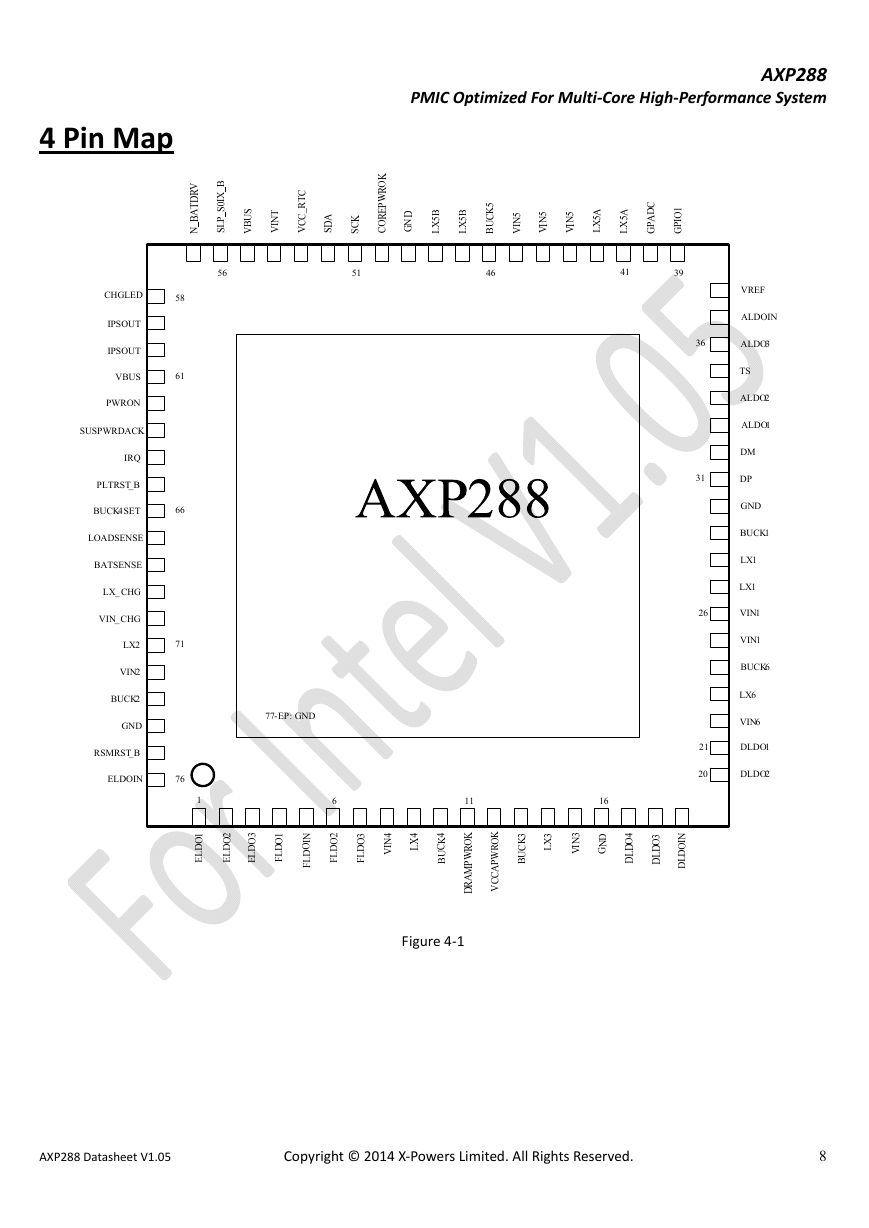

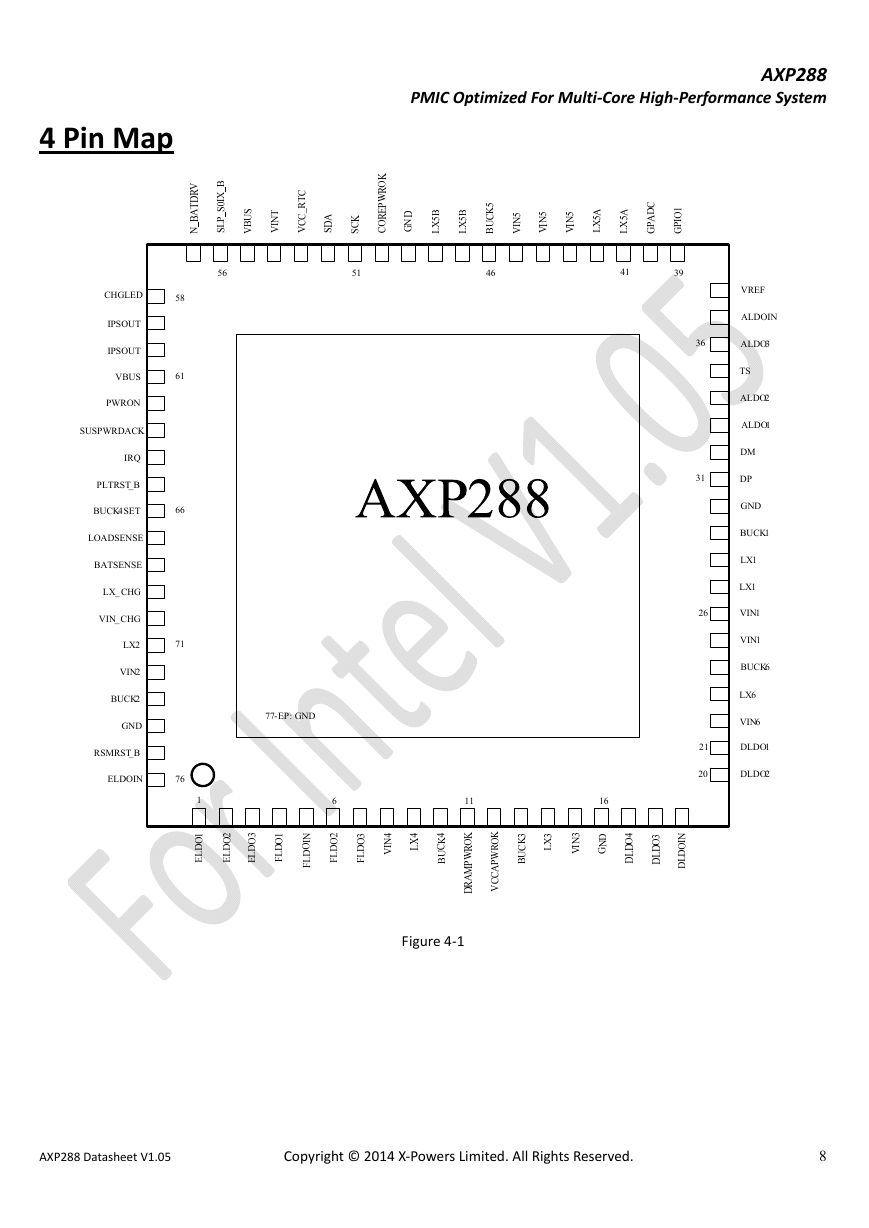

4 Pin Map

5 Pin Description

6 Block Diagram

7 Absolute Maximum Ratings

8 Electrical Characteristics

9 Control and operation

9.1 Power on/off and Power sequences

9.1.1 Power on/off sources

9.1.2 Power up sequence

9.1.3 Power down Sequencing

9.1.4 Cold Reset and Global reset

9.1.5 Sleep state control

9.2 IPS (Intelligent Power Select)

9.2.1 IPS overview

9.2.2 IPSOUT source selection

9.2.3 VBUS current/voltage limitation

9.2.4 VBUS input overvoltage protection

9.2.5 VBUS insertion power up condition

9.3 BC Detection Module

9.4 Adaptive PWM Charger

9.4.1 Charger Overview

9.4.2 Charging start and stop

9.4.3 Timeout activity

9.4.4 CHGLED activity

9.4.5 Battery detection

9.4.6 Temperature protection

9.5 Multi-Power Outputs

9.6 ADC

9.7 Fuel Gauge

9.8 Interrupt Controller

9.9 TWSI

10 Register

Register List

REG 00H: Power source status

REG 01H: Power mode and Charger status

REG 02H: Power up/down reason register

REG 03H: IC type no.

REG 04-0FH: 12 Data buffers

REG 10H: Output power on-off control 1

REG 12H: Output power on-off control 2

REG 13H: Output power on-off control 3

REG 14H: On/Off synchronous control

REG 15H: DLDO1 voltage control

REG 16H: DLDO2 voltage control

REG 17H: DLDO3 voltage control

REG 18H: DLDO4 voltage control

REG 19H: ELDO1 voltage control

REG 1AH: ELDO2 voltage control

REG 1BH: ELDO3 voltage control

REG 1CH: FLDO1 voltage control

REG 1DH: FLDO2/3 voltage control

REG 20H: BUCK6 voltage control

REG 21H: BUCK5 voltage control

REG 22H: Reserved

REG 23H: BUCK1 voltage control

REG 24H: BUCK4 voltage control

REG 25H: BUCK3 voltage control

REG 26H: BUCK2 voltage control

REG 27H: BUCK1 /2 /3 /4 /5 DVM control

REG 28H: ALDO1 voltage control

REG 29H: ALDO2 voltage control

REG 2AH: ALDO3 voltage control

REG 2CH: BC Module Global Register

REG 2DH: BC Module VBUS Control and Status Register

REG 2EH: BC USB Status Register

REG 2FH: BC Detect Status Register

REG 30H: VBUS path control & Hold voltage setting

REG 31H: Power wakeup control & VOFF setting

REG 32H: Power Disable, BAT detect and CHGLED pin control

REG 33H: Charger Control 1

REG 34H: Charger Control 2

REG 35H: Charger Control 3

REG 36H: POK setting

REG 37H: POK Power off activity time setting

REG 38H: VLTF-charge setting

REG 39H: VHTF-charge setting

REG 3AH: Reserved

REG 3BH: Buck frequency setting

REG 3CH: VLTF-work setting

REG 3DH: VHTF-work setting

REG 40H: IRQ enable 1

REG 41H: IRQ enable 2

REG 42H: IRQ enable 3

REG 43H: IRQ enable 4

REG 44H: IRQ enable 5

REG 45H: IRQ enable 6

REG 48H: IRQ Status 1

REG 49H: IRQ Status 2

REG 4AH: IRQ Status 3

REG 4BH: IRQ Status 4

REG 4CH: IRQ Status 5

REG 4DH: IRQ Status 6

REG 58H: TS pin input ADC data, highest 8bit

REG 59H: TS pin input ADC data, lowest 4bit

REG 5AH: GPADC pin input ADC data, highest 8bit

REG 5BH: GPADC pin input ADC data, lowest 4bit

REG 78H: Average data bit[11:4] for Battery voltage (BATSENSE)

REG 79H: Average data bit[3:0] for Battery voltage (BATSENSE)

REG 7AH: Average data bit[11:4] for Battery charge current

REG 7BH: Average data bit[3:0] for Battery charge current

REG 7CH: Average data bit[11:4] for Battery discharge current

REG 7DH: Average data bit[3:0] for Battery discharge current

REG 80H: Buck PWM/PFM mode select

REG 81H: Off-Discharge and Output monitor control

REG 82H: ADC Enable

REG 84H: ADC speed setting, TS pin Control

REG 85H: ADC speed setting

REG 8AH: Timer control

REG 8EH: Buck output voltage monitor de-bounce time setting

REG 8FH: IRQ pin, hot-over shut down

REG 90H: GPIO0 (GPADC) control

REG 91H: GPIO0LDO and GPIO0 high level voltage setting

REG 92H: GPIO1 control

REG 93H: GPIO1LDO and GPIO1 high level voltage setting

REG 94H: GPIO signal bit

REG 97H: GPIO pull down control

REG 9AH: Run time Sleep power up sequence 1

REG 9BH: Run time Sleep power up sequence 2

REG 9CH: Run time Sleep power down sequence 1

REG 9DH: Run time Sleep power down sequence 2

REG 9EH: Power rail mode in Sleep state

REG B8H: Fuel Gauge Control

REG B9H: Battery capacity percentage for indication

REG BAH: RDC 1

REG BBH: RDC 0

REG BCH: OCV 1

REG BDH: OCV0

REG E0H: Battery maximum capacity

REG E1H: Battery maximum capacity

REG E2H: Coulomb meter counter1

REG E3H: Coulomb meter counter2

REG E4H: OCV Percentage of battery capacity

REG E5H: Coulomb meter percentage of battery capacity

REG E6H: Battery capacity percentage warning level

REG E8H: Fuel gauge tuning control 0

REG E9H: Fuel gauge tuning control 1

REG EAH: Fuel gauge tuning control 2

REG EBH: Fuel gauge tuning control 3

REG ECH: Fuel gauge tuning control 4

REG EDH: Fuel gauge tuning control 5

11 Package

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc