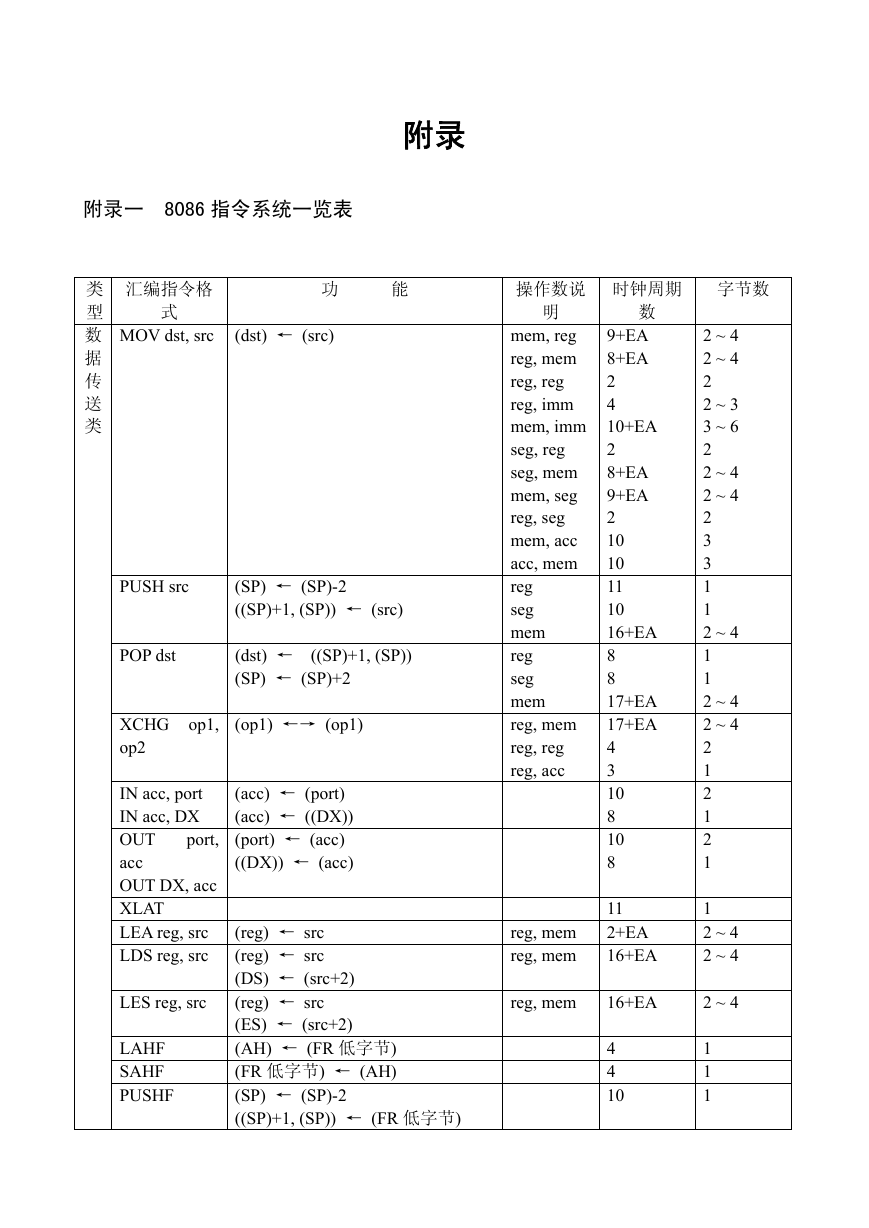

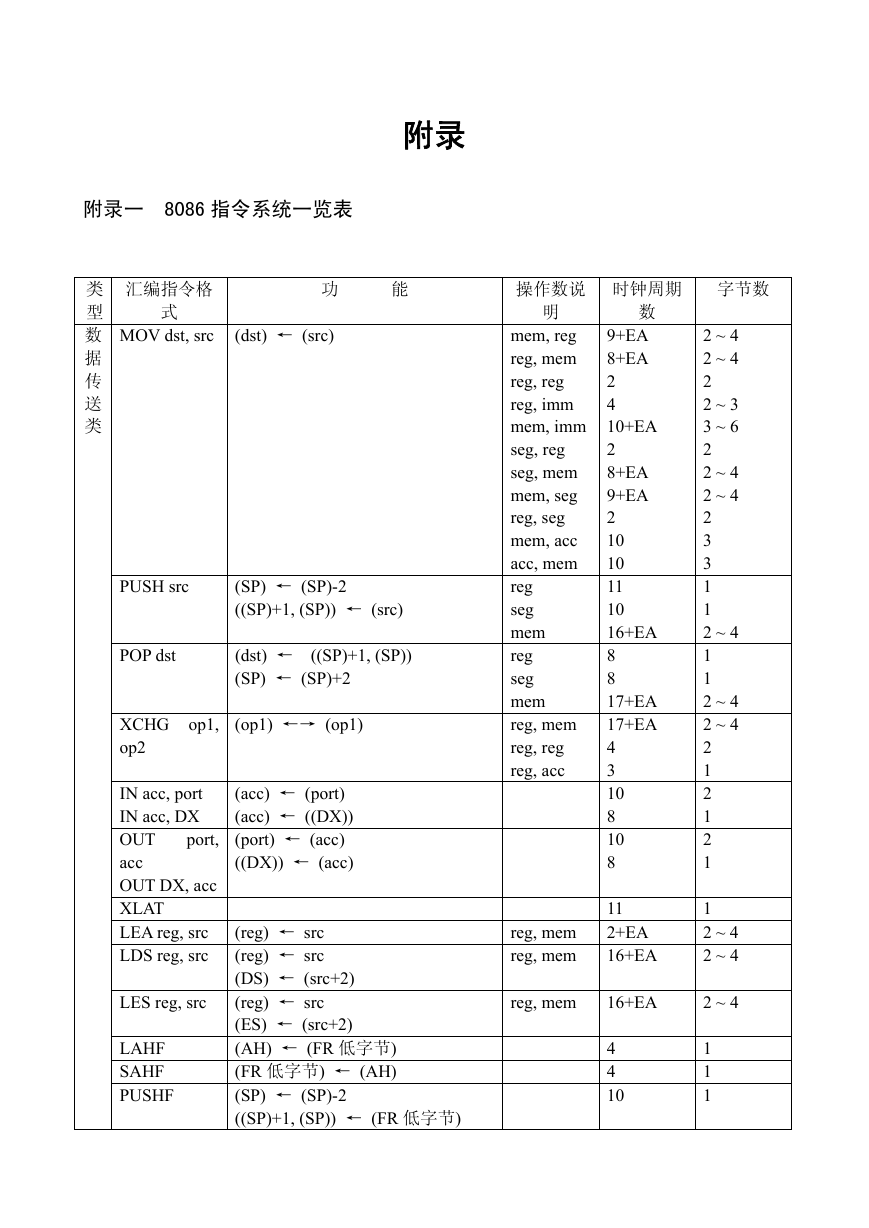

附录

附录一 8086 指令系统一览表

汇编指令格

式

功 能

MOV dst, src

(dst) ← (src)

类

型

数

据

传

送

类

PUSH src

(SP) ← (SP)-2

((SP)+1, (SP)) ← (src)

POP dst

(dst) ← ((SP)+1, (SP))

(SP) ← (SP)+2

XCHG op1,

op2

port,

IN acc, port

IN acc, DX

OUT

acc

OUT DX, acc

XLAT

LEA reg, src

LDS reg, src

LES reg, src

LAHF

SAHF

PUSHF

(op1) ←→ (op1)

(acc) ← (port)

(acc) ← ((DX))

(port) ← (acc)

((DX)) ← (acc)

(reg) ← src

(reg) ← src

(DS) ← (src+2)

(reg) ← src

(ES) ← (src+2)

(AH) ← (FR 低字节)

(FR 低字节) ← (AH)

(SP) ← (SP)-2

((SP)+1, (SP)) ← (FR 低字节)

操作数说

时钟周期

明

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

seg, reg

seg, mem

mem, seg

reg, seg

mem, acc

acc, mem

reg

seg

mem

reg

seg

mem

reg, mem

reg, reg

reg, acc

reg, mem

reg, mem

数

9+EA

8+EA

2

4

10+EA

2

8+EA

9+EA

2

10

10

11

10

16+EA

8

8

17+EA

17+EA

4

3

10

8

10

8

11

2+EA

16+EA

reg, mem

16+EA

4

4

10

字节数

2 ~ 4

2 ~ 4

2

2 ~ 3

3 ~ 6

2

2 ~ 4

2 ~ 4

2

3

3

1

1

2 ~ 4

1

1

2 ~ 4

2 ~ 4

2

1

2

1

2

1

1

2 ~ 4

2 ~ 4

2 ~ 4

1

1

1

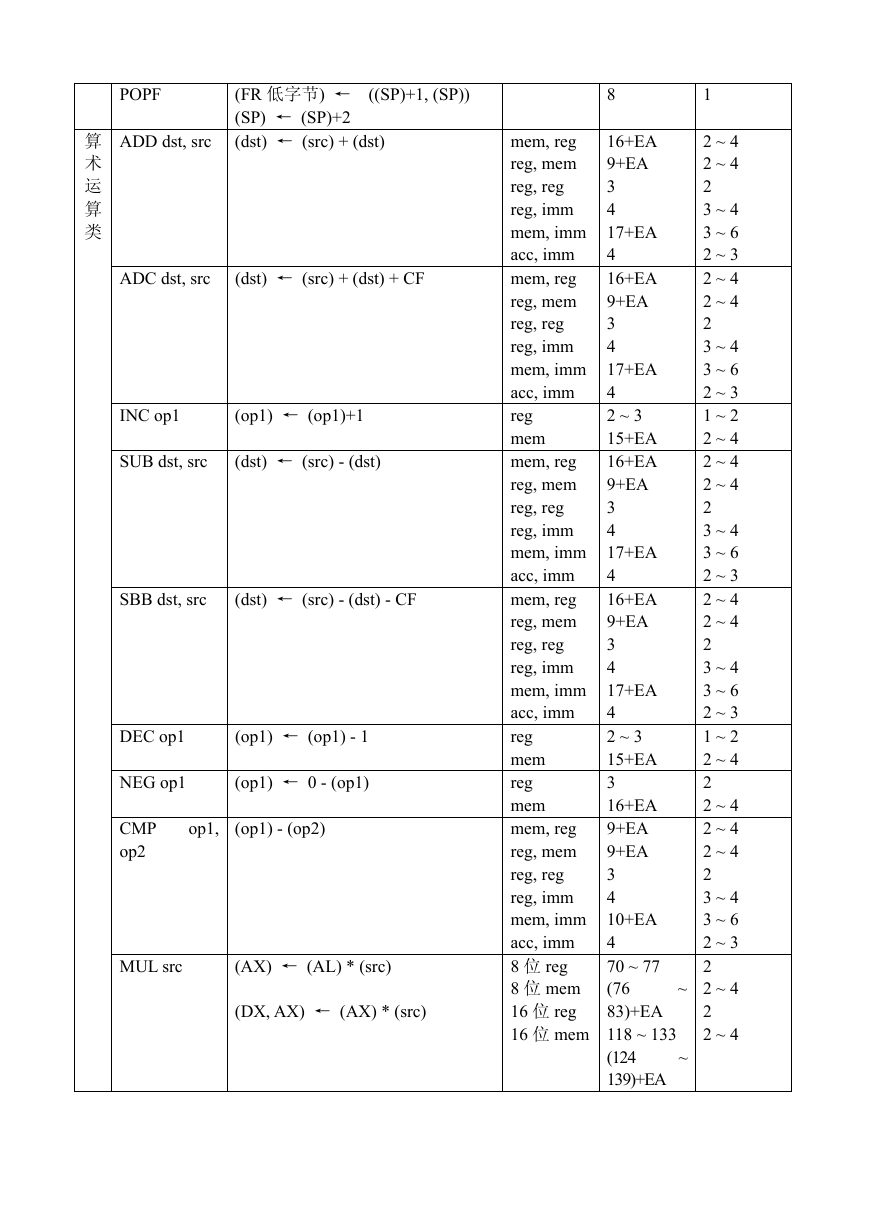

�

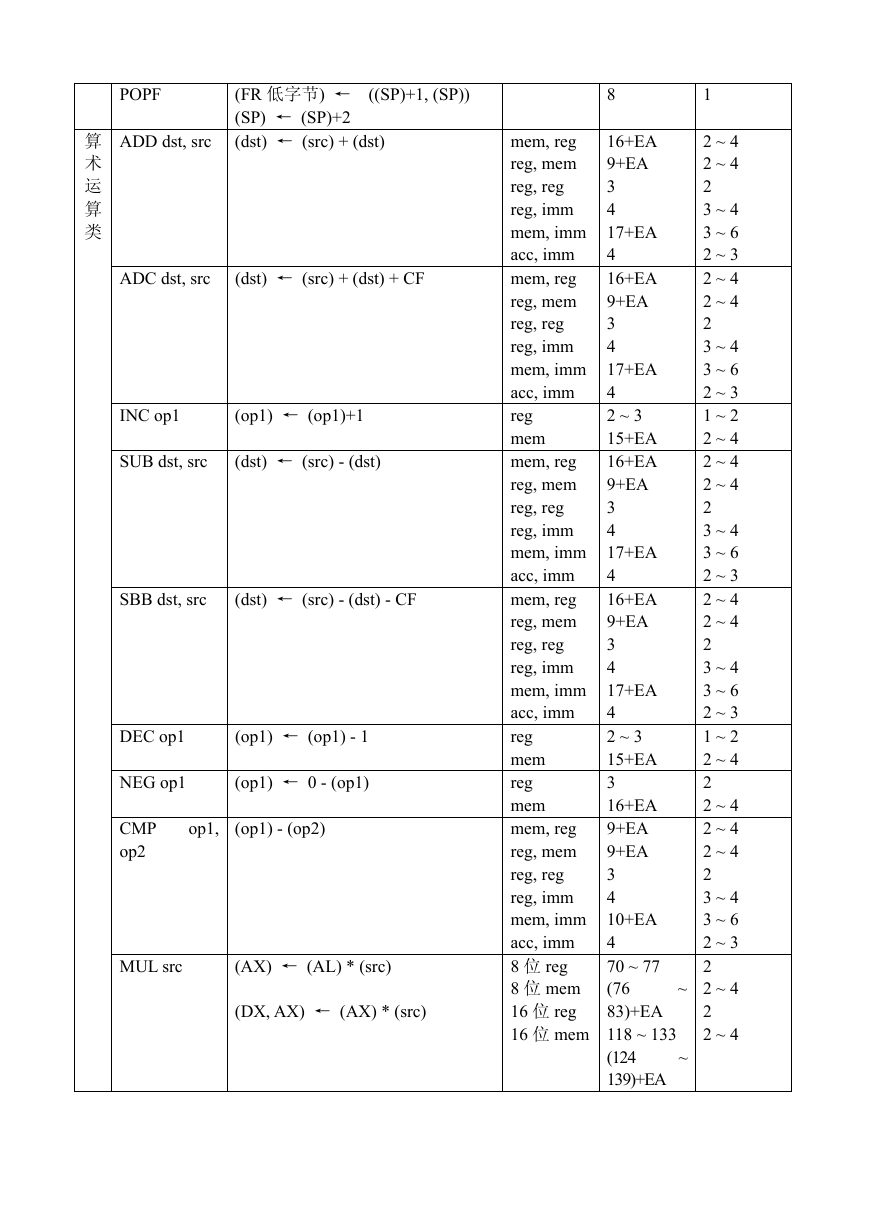

POPF

ADD dst, src

(FR 低字节) ← ((SP)+1, (SP))

(SP) ← (SP)+2

(dst) ← (src) + (dst)

算

术

运

算

类

ADC dst, src

(dst) ← (src) + (dst) + CF

INC op1

(op1) ← (op1)+1

SUB dst, src

(dst) ← (src) - (dst)

SBB dst, src

(dst) ← (src) - (dst) - CF

DEC op1

(op1) ← (op1) - 1

NEG op1

(op1) ← 0 - (op1)

CMP

op2

op1,

(op1) - (op2)

MUL src

(AX) ← (AL) * (src)

(DX, AX) ← (AX) * (src)

8

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

reg

mem

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

reg

mem

reg

mem

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

8 位 reg

8 位 mem

16 位 reg

16 位 mem

16+EA

9+EA

3

4

17+EA

4

16+EA

9+EA

3

4

17+EA

4

2 ~ 3

15+EA

16+EA

9+EA

3

4

17+EA

4

16+EA

9+EA

3

4

17+EA

4

2 ~ 3

15+EA

3

16+EA

9+EA

9+EA

3

4

10+EA

4

70 ~ 77

(76

83)+EA

118 ~ 133

(124

~

139)+EA

~

1

2 ~ 4

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

2 ~ 4

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

1 ~ 2

2 ~ 4

2 ~ 4

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

2 ~ 4

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

1 ~ 2

2 ~ 4

2

2 ~ 4

2 ~ 4

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

2

2 ~ 4

2

2 ~ 4

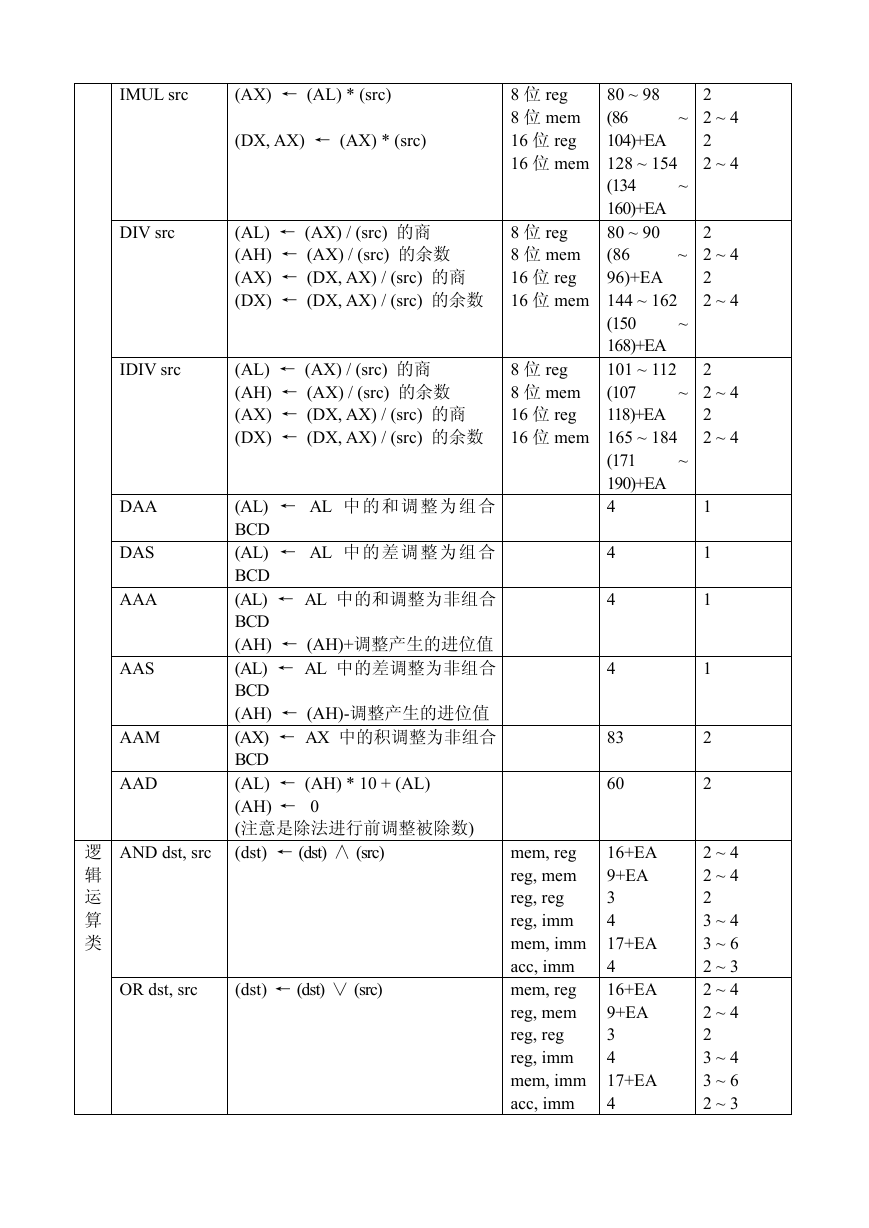

�

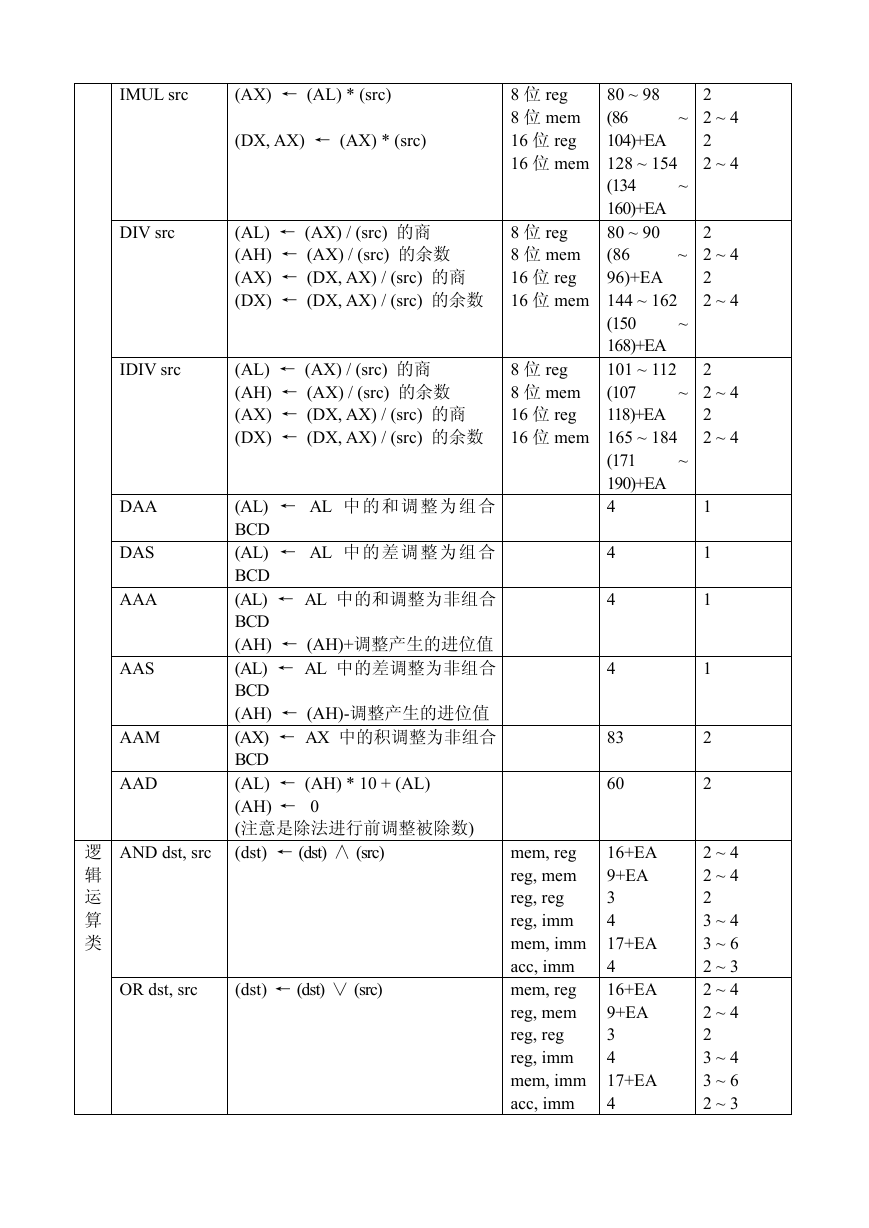

IMUL src

(AX) ← (AL) * (src)

(DX, AX) ← (AX) * (src)

8 位 reg

8 位 mem

16 位 reg

16 位 mem

~

~

80 ~ 98

(86

104)+EA

128 ~ 154

(134

~

160)+EA

80 ~ 90

(86

96)+EA

144 ~ 162

(150

~

168)+EA

101 ~ 112

(107

~

118)+EA

165 ~ 184

(171

~

190)+EA

4

4

4

4

83

60

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

1

1

1

1

2

2

2 ~ 4

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

2 ~ 4

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

16+EA

9+EA

3

4

17+EA

4

16+EA

9+EA

3

4

17+EA

4

(AL) ← (AX) / (src) 的商

(AH) ← (AX) / (src) 的余数

(AX) ← (DX, AX) / (src) 的商

(DX) ← (DX, AX) / (src) 的余数

8 位 reg

8 位 mem

16 位 reg

16 位 mem

(AL) ← (AX) / (src) 的商

(AH) ← (AX) / (src) 的余数

(AX) ← (DX, AX) / (src) 的商

(DX) ← (DX, AX) / (src) 的余数

8 位 reg

8 位 mem

16 位 reg

16 位 mem

(AL) ← AL 中 的 和 调 整 为 组 合

BCD

(AL) ← AL 中 的 差 调 整 为 组 合

BCD

(AL) ← AL 中的和调整为非组合

BCD

(AH) ← (AH)+调整产生的进位值

(AL) ← AL 中的差调整为非组合

BCD

(AH) ← (AH)-调整产生的进位值

(AX) ← AX 中的积调整为非组合

BCD

(AL) ← (AH) * 10 + (AL)

(AH) ← 0

(注意是除法进行前调整被除数)

(dst) ← (dst) ∧ (src)

DIV src

IDIV src

DAA

DAS

AAA

AAS

AAM

AAD

AND dst, src

逻

辑

运

算

类

OR dst, src

(dst) ← (dst) ∨ (src)

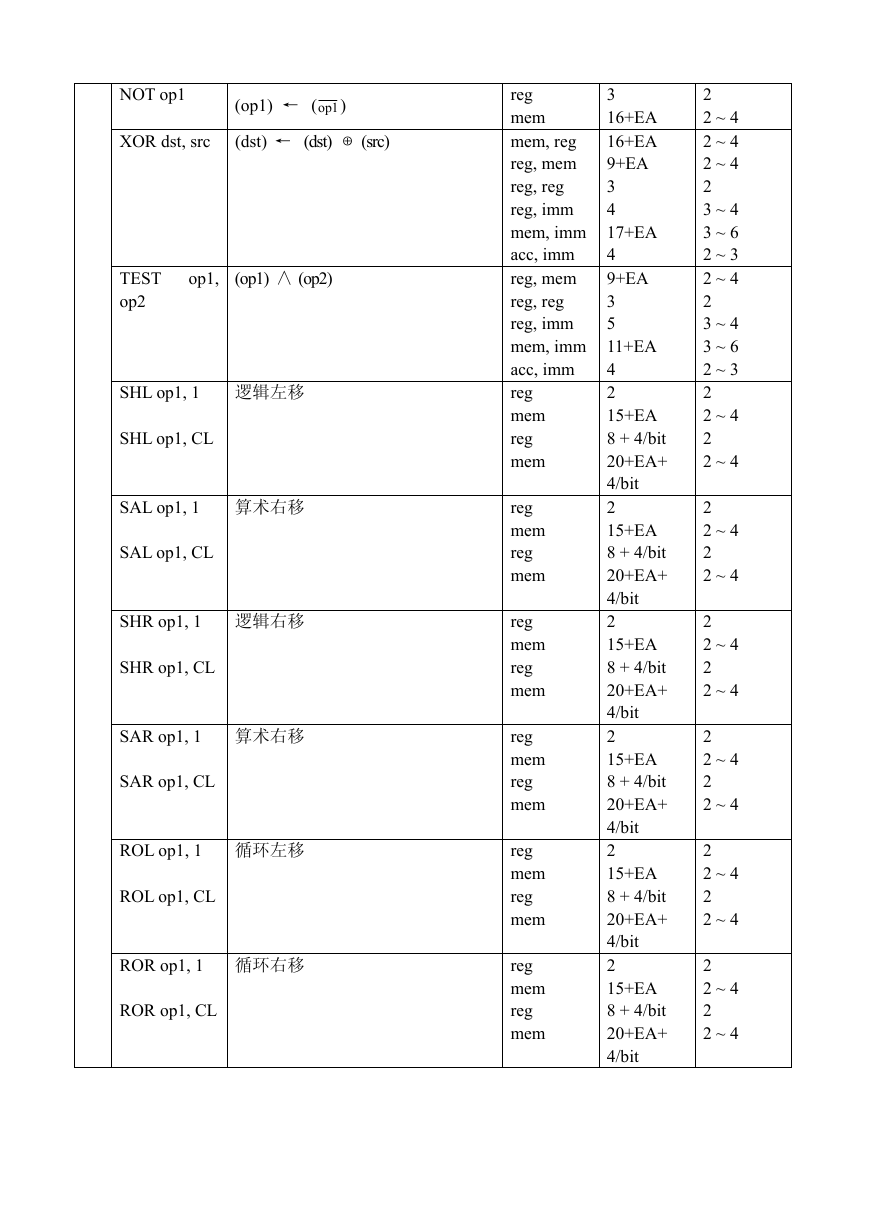

�

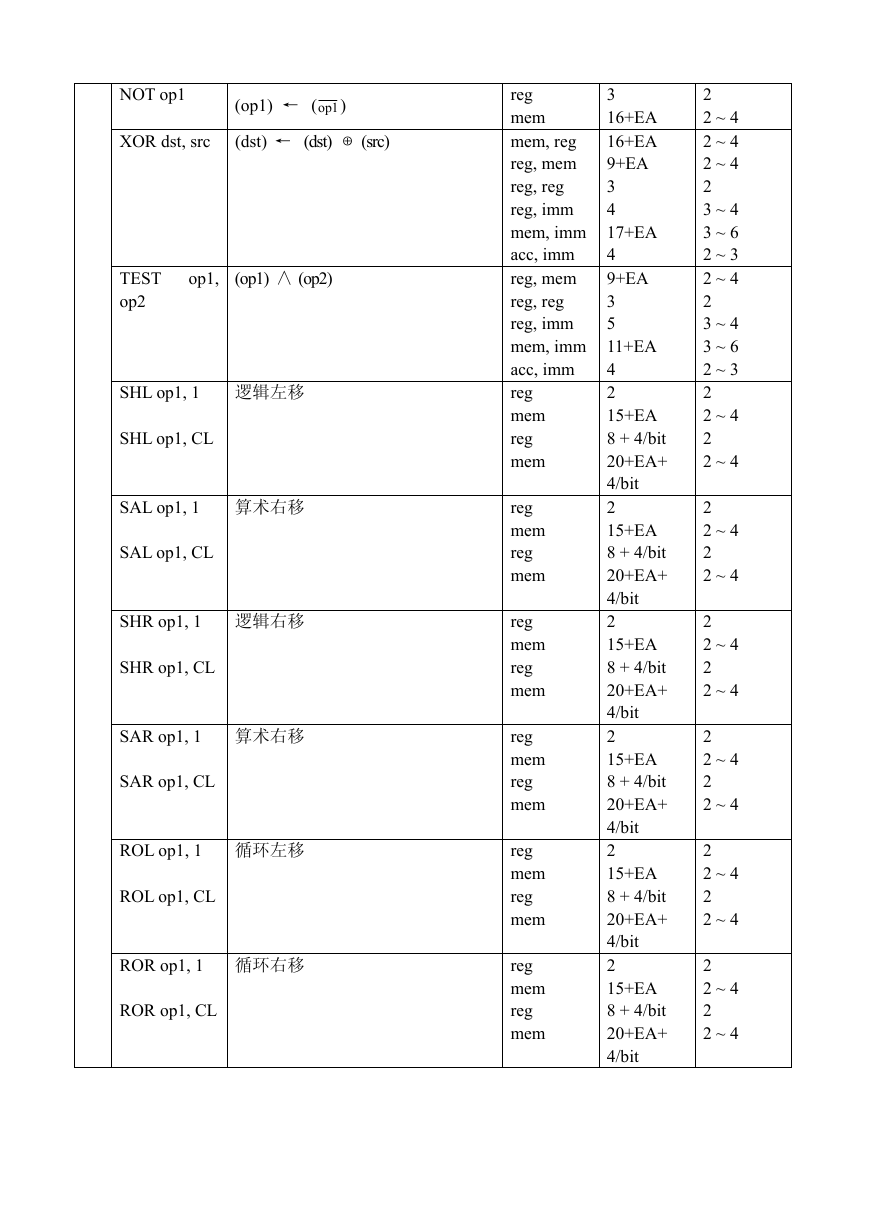

NOT op1

(op1) ← (

1op )

XOR dst, src

(dst) ← (dst) ⊕ (src)

TEST

op2

op1,

(op1) ∧ (op2)

逻辑左移

算术右移

SHL op1, 1

SHL op1, CL

SAL op1, 1

SAL op1, CL

逻辑右移

SHR op1, 1

SHR op1, CL

算术右移

SAR op1, 1

SAR op1, CL

循环左移

ROL op1, 1

ROL op1, CL

循环右移

ROR op1, 1

ROR op1, CL

reg

mem

mem, reg

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

reg, mem

reg, reg

reg, imm

mem, imm

acc, imm

reg

mem

reg

mem

reg

mem

reg

mem

reg

mem

reg

mem

reg

mem

reg

mem

reg

mem

reg

mem

reg

mem

reg

mem

3

16+EA

16+EA

9+EA

3

4

17+EA

4

9+EA

3

5

11+EA

4

2

15+EA

8 + 4/bit

20+EA+

4/bit

2

15+EA

8 + 4/bit

20+EA+

4/bit

2

15+EA

8 + 4/bit

20+EA+

4/bit

2

15+EA

8 + 4/bit

20+EA+

4/bit

2

15+EA

8 + 4/bit

20+EA+

4/bit

2

15+EA

8 + 4/bit

20+EA+

4/bit

2

2 ~ 4

2 ~ 4

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

2 ~ 4

2

3 ~ 4

3 ~ 6

2 ~ 3

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

�

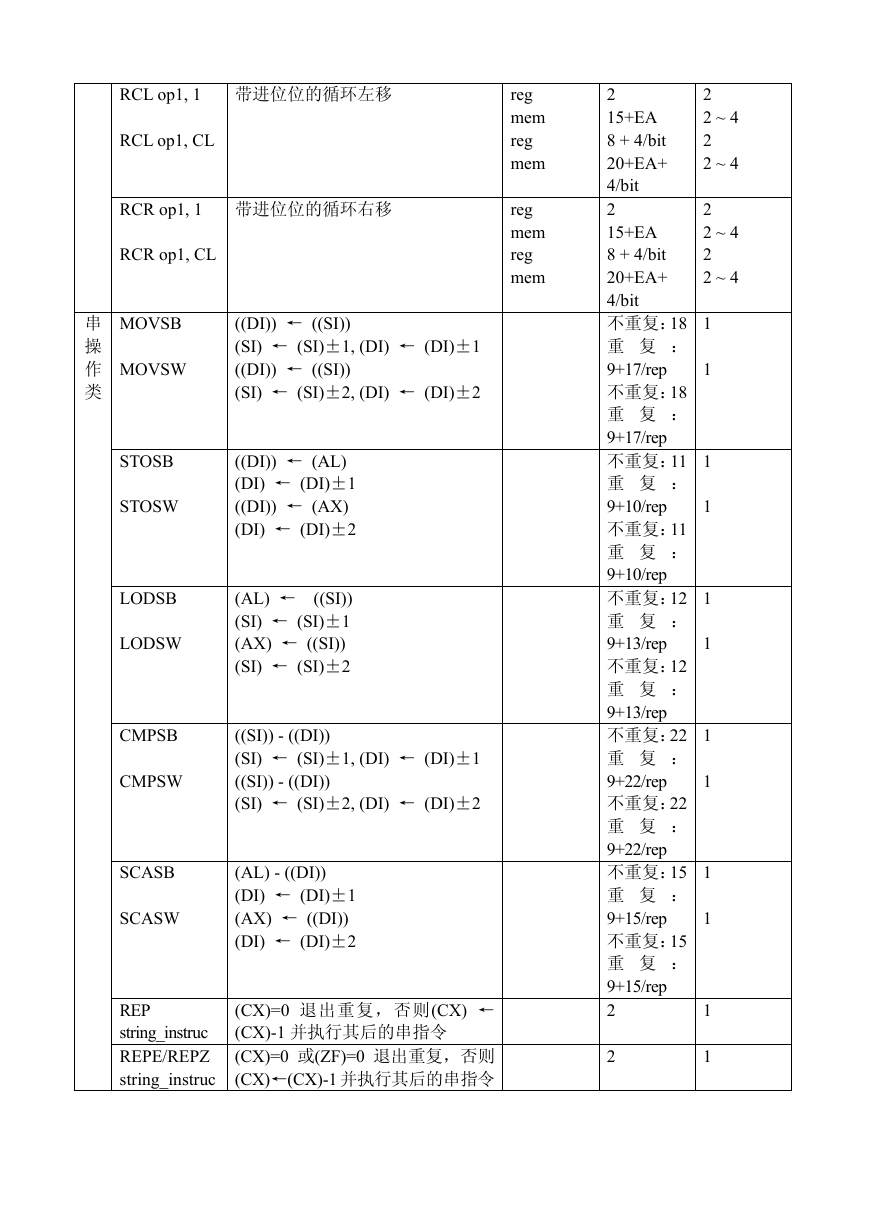

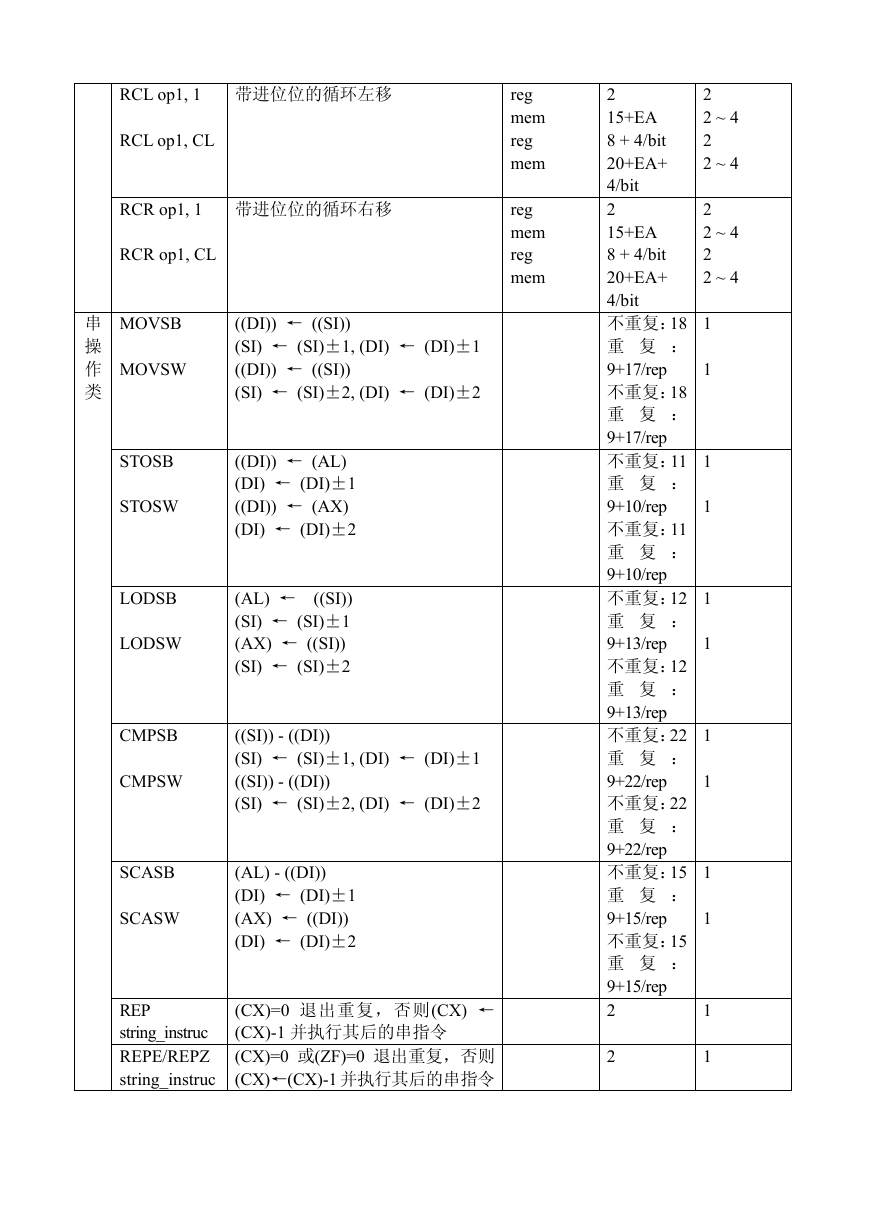

带进位位的循环左移

带进位位的循环右移

RCL op1, 1

RCL op1, CL

RCR op1, 1

RCR op1, CL

MOVSB

MOVSW

串

操

作

类

((DI)) ← ((SI))

(SI) ← (SI)±1, (DI) ← (DI)±1

((DI)) ← ((SI))

(SI) ← (SI)±2, (DI) ← (DI)±2

STOSB

STOSW

LODSB

LODSW

CMPSB

CMPSW

SCASB

SCASW

((DI)) ← (AL)

(DI) ← (DI)±1

((DI)) ← (AX)

(DI) ← (DI)±2

(AL) ← ((SI))

(SI) ← (SI)±1

(AX) ← ((SI))

(SI) ← (SI)±2

((SI)) - ((DI))

(SI) ← (SI)±1, (DI) ← (DI)±1

((SI)) - ((DI))

(SI) ← (SI)±2, (DI) ← (DI)±2

(AL) - ((DI))

(DI) ← (DI)±1

(AX) ← ((DI))

(DI) ← (DI)±2

REP

string_instruc

REPE/REPZ

string_instruc

(CX)=0 退出重复,否则(CX) ←

(CX)-1 并执行其后的串指令

(CX)=0 或(ZF)=0 退出重复,否则

(CX)←(CX)-1 并执行其后的串指令

reg

mem

reg

mem

reg

mem

reg

mem

2

15+EA

8 + 4/bit

20+EA+

4/bit

2

15+EA

8 + 4/bit

20+EA+

4/bit

不重复:18

重 复 :

9+17/rep

不重复:18

重 复 :

9+17/rep

不重复:11

重 复 :

9+10/rep

不重复:11

重 复 :

9+10/rep

不重复:12

重 复 :

9+13/rep

不重复:12

重 复 :

9+13/rep

不重复:22

重 复 :

9+22/rep

不重复:22

重 复 :

9+22/rep

不重复:15

重 复 :

9+15/rep

不重复:15

重 复 :

9+15/rep

2

2

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

2

2 ~ 4

1

1

1

1

1

1

1

1

1

1

1

1

�

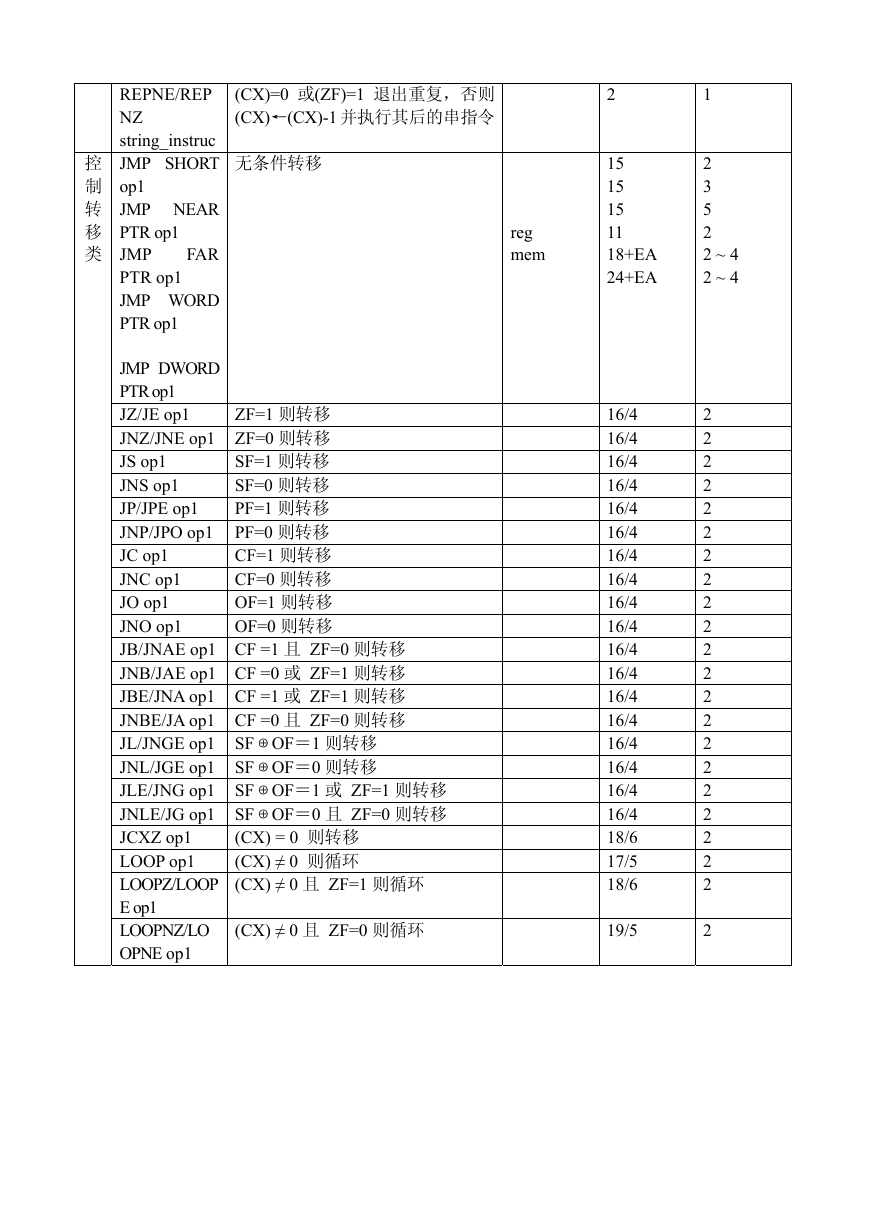

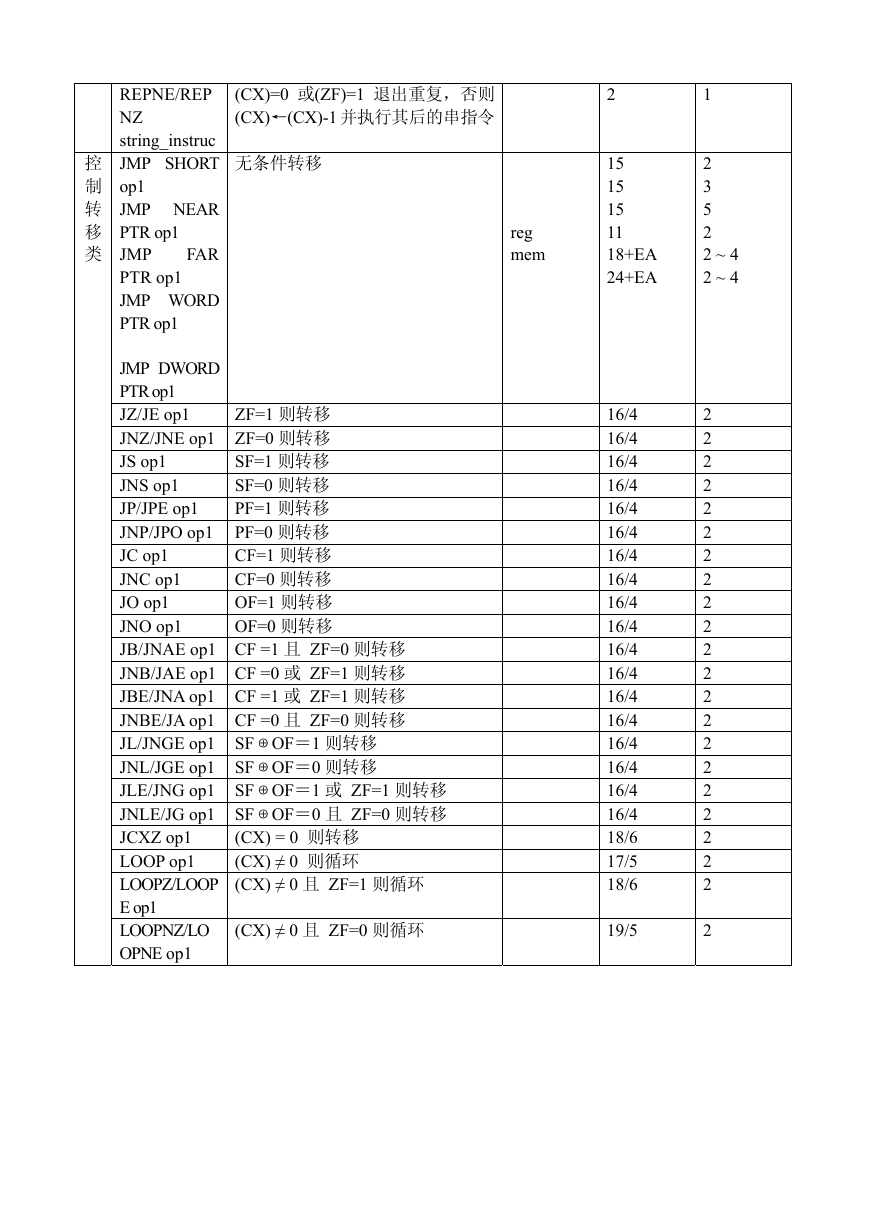

控

制

转

移

类

FAR

(CX)=0 或(ZF)=1 退出重复,否则

(CX)←(CX)-1 并执行其后的串指令

无条件转移

REPNE/REP

NZ

string_instruc

JMP SHORT

op1

JMP NEAR

PTR op1

JMP

PTR op1

JMP WORD

PTR op1

JMP DWORD

PTR op1

JZ/JE op1

ZF=1 则转移

JNZ/JNE op1 ZF=0 则转移

SF=1 则转移

JS op1

JNS op1

SF=0 则转移

JP/JPE op1

PF=1 则转移

JNP/JPO op1 PF=0 则转移

JC op1

CF=1 则转移

CF=0 则转移

JNC op1

OF=1 则转移

JO op1

JNO op1

OF=0 则转移

JB/JNAE op1 CF =1 且 ZF=0 则转移

JNB/JAE op1 CF =0 或 ZF=1 则转移

JBE/JNA op1 CF =1 或 ZF=1 则转移

JNBE/JA op1 CF =0 且 ZF=0 则转移

JL/JNGE op1 SF⊕OF=1 则转移

JNL/JGE op1 SF⊕OF=0 则转移

JLE/JNG op1 SF⊕OF=1 或 ZF=1 则转移

JNLE/JG op1 SF⊕OF=0 且 ZF=0 则转移

JCXZ op1

LOOP op1

LOOPZ/LOOP

E op1

LOOPNZ/LO

OPNE op1

(CX) = 0 则转移

(CX) ≠ 0 则循环

(CX) ≠ 0 且 ZF=1 则循环

(CX) ≠ 0 且 ZF=0 则循环

2

1

reg

mem

15

15

15

11

18+EA

24+EA

2

3

5

2

2 ~ 4

2 ~ 4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

16/4

18/6

17/5

18/6

19/5

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

�

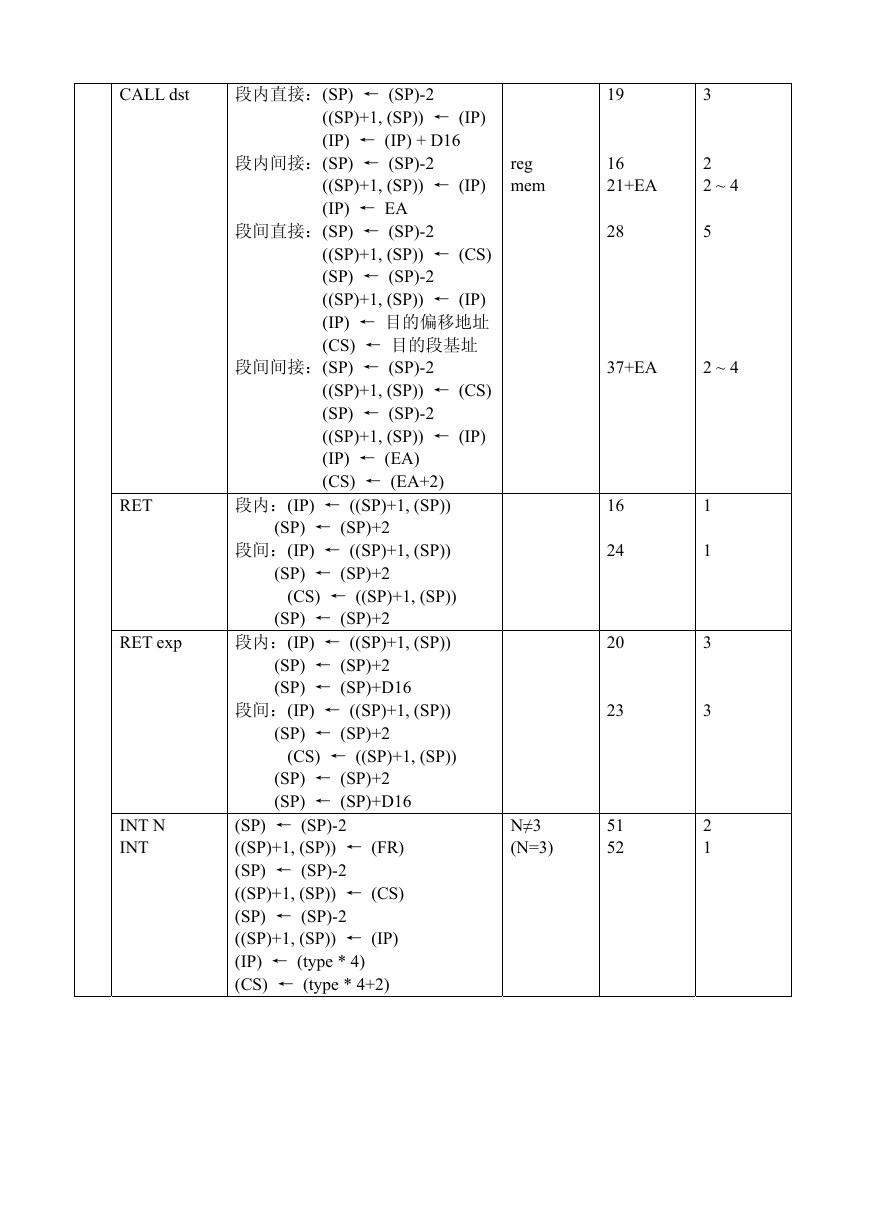

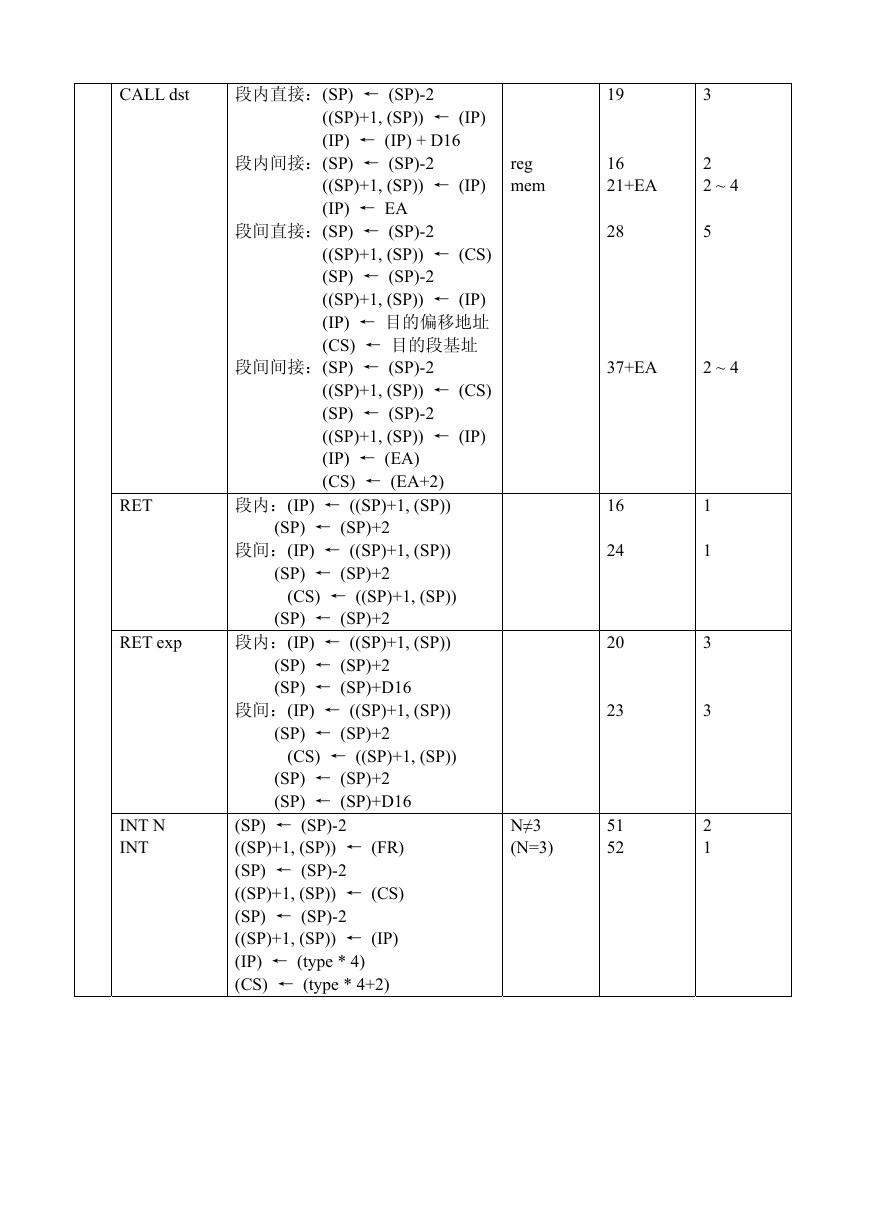

reg

mem

N≠3

(N=3)

19

16

21+EA

28

37+EA

3

2

2 ~ 4

5

2 ~ 4

16

24

20

23

51

52

1

1

3

3

2

1

CALL dst

RET

RET exp

INT N

INT

段内间接:(SP) ← (SP)-2

段间直接:(SP) ← (SP)-2

((SP)+1, (SP)) ← (IP)

(IP) ← (IP) + D16

((SP)+1, (SP)) ← (IP)

(IP) ← EA

((SP)+1, (SP)) ← (CS)

(SP) ← (SP)-2

((SP)+1, (SP)) ← (IP)

(IP) ← 目的偏移地址

(CS) ← 目的段基址

段内直接:(SP) ← (SP)-2

段间间接:(SP) ← (SP)-2

((SP)+1, (SP)) ← (CS)

(SP) ← (SP)-2

((SP)+1, (SP)) ← (IP)

(IP) ← (EA)

(CS) ← (EA+2)

段内:(IP) ← ((SP)+1, (SP))

(SP) ← (SP)+2

段间:(IP) ← ((SP)+1, (SP))

(SP) ← (SP)+2

(CS) ← ((SP)+1, (SP))

(SP) ← (SP)+2

段内:(IP) ← ((SP)+1, (SP))

(SP) ← (SP)+2

(SP) ← (SP)+D16

段间:(IP) ← ((SP)+1, (SP))

(SP) ← (SP)+2

(CS) ← ((SP)+1, (SP))

(SP) ← (SP)+2

(SP) ← (SP)+D16

(SP) ← (SP)-2

((SP)+1, (SP)) ← (FR)

(SP) ← (SP)-2

((SP)+1, (SP)) ← (CS)

(SP) ← (SP)-2

((SP)+1, (SP)) ← (IP)

(IP) ← (type * 4)

(CS) ← (type * 4+2)

�

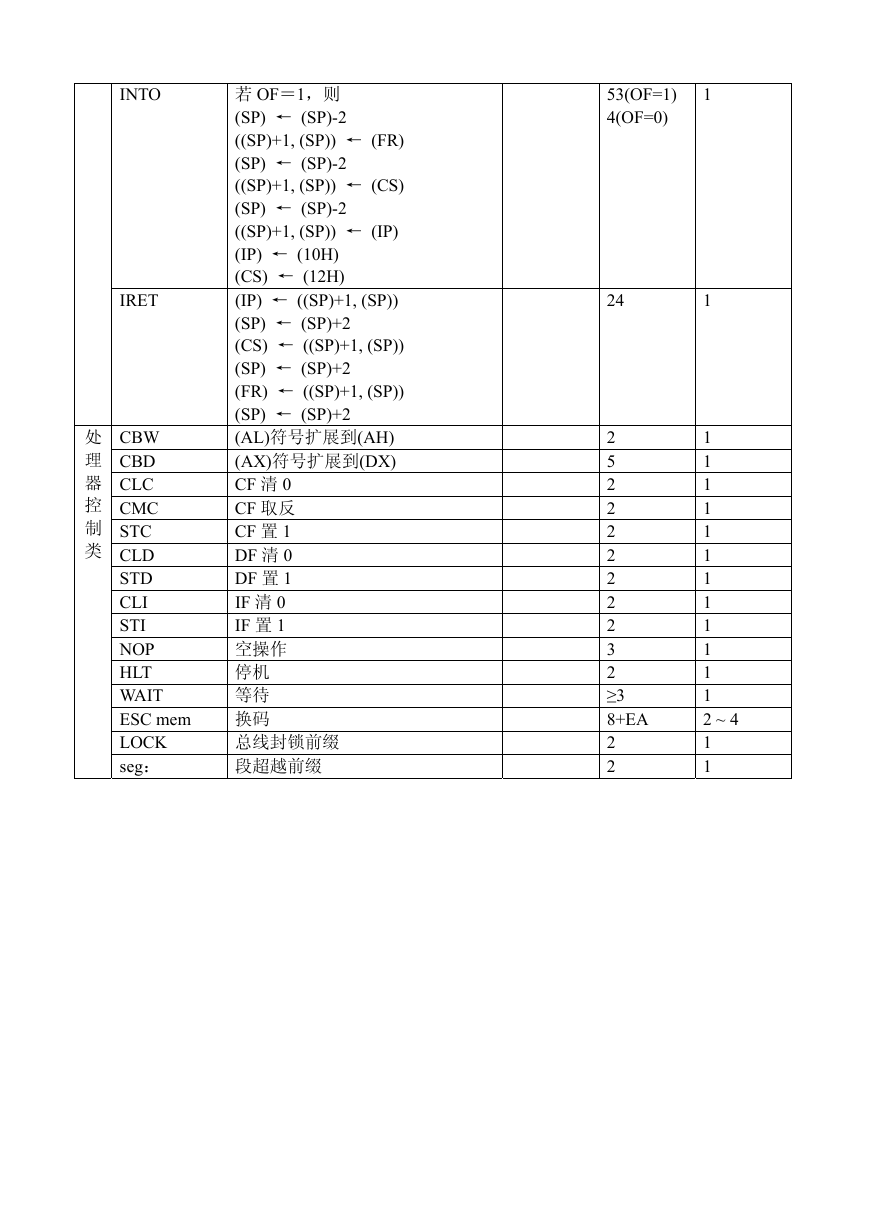

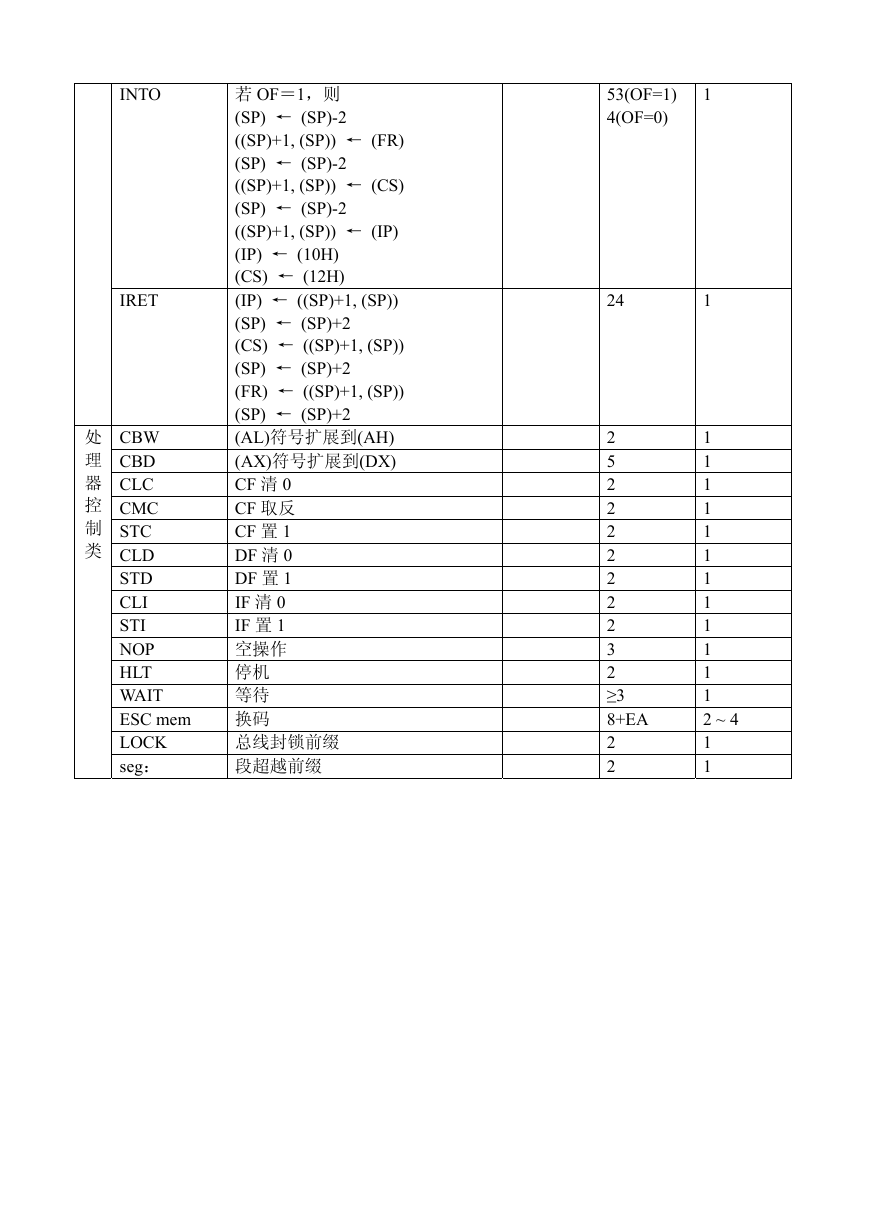

INTO

IRET

处

理

器

控

制

类

CBW

CBD

CLC

CMC

STC

CLD

STD

CLI

STI

NOP

HLT

WAIT

ESC mem

LOCK

seg:

若 OF=1,则

(SP) ← (SP)-2

((SP)+1, (SP)) ← (FR)

(SP) ← (SP)-2

((SP)+1, (SP)) ← (CS)

(SP) ← (SP)-2

((SP)+1, (SP)) ← (IP)

(IP) ← (10H)

(CS) ← (12H)

(IP) ← ((SP)+1, (SP))

(SP) ← (SP)+2

(CS) ← ((SP)+1, (SP))

(SP) ← (SP)+2

(FR) ← ((SP)+1, (SP))

(SP) ← (SP)+2

(AL)符号扩展到(AH)

(AX)符号扩展到(DX)

CF 清 0

CF 取反

CF 置 1

DF 清 0

DF 置 1

IF 清 0

IF 置 1

空操作

停机

等待

换码

总线封锁前缀

段超越前缀

53(OF=1)

4(OF=0)

1

24

2

5

2

2

2

2

2

2

2

3

2

≥3

8+EA

2

2

1

1

1

1

1

1

1

1

1

1

1

1

1

2 ~ 4

1

1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc