广州周立功单片机发展有限公司 Tel:(020)38730916 38730917 38730976 38730977 Fax:38730925

PCF8574T I2C 并行口扩展电路

I2C 并行口扩展电路

1. 特性

操作电压 2.5~6.0V

低备用电流(≤10μA)

开漏中断输出

与大多数 MCU 兼容

口输出锁存,具有大电流驱动能力,可直接驱动 LED

通过 3 个硬件地址引脚可寻址 8 个器件(PCF8574A 可多达 16 个)

DIP16,SO16 或 SSOP20 形式封装

I2C 总线 实现 8 位远程 I/O 口

2. 概述

PCF8574 是 CMOS 电路。它通过两条双向总线(I2C)可使大多数 MCU 实现远程 I/O 口扩展。该

器件包含一个 8 位准双向口和一个 I2C 总线接口。PCF8574 电流消耗很低,且口输出锁存具有大电流驱

动能力,可直接驱动 LED。它还带有一条中断接线(INT)可与 MCU 的中断逻辑相连。通过 INT 发送

中断信号,远端 I/O 口不必经过 I2C 总线通信就可通知 MCU 是否有数据从端口输入。这意味着 PCF8574

可以作为一个单被控器。

PCF8574 和 PCF8574A 的唯一区别仅在于器件地址不相同。

3. 订单信息

型号

PCF8574T

PCF8574AT

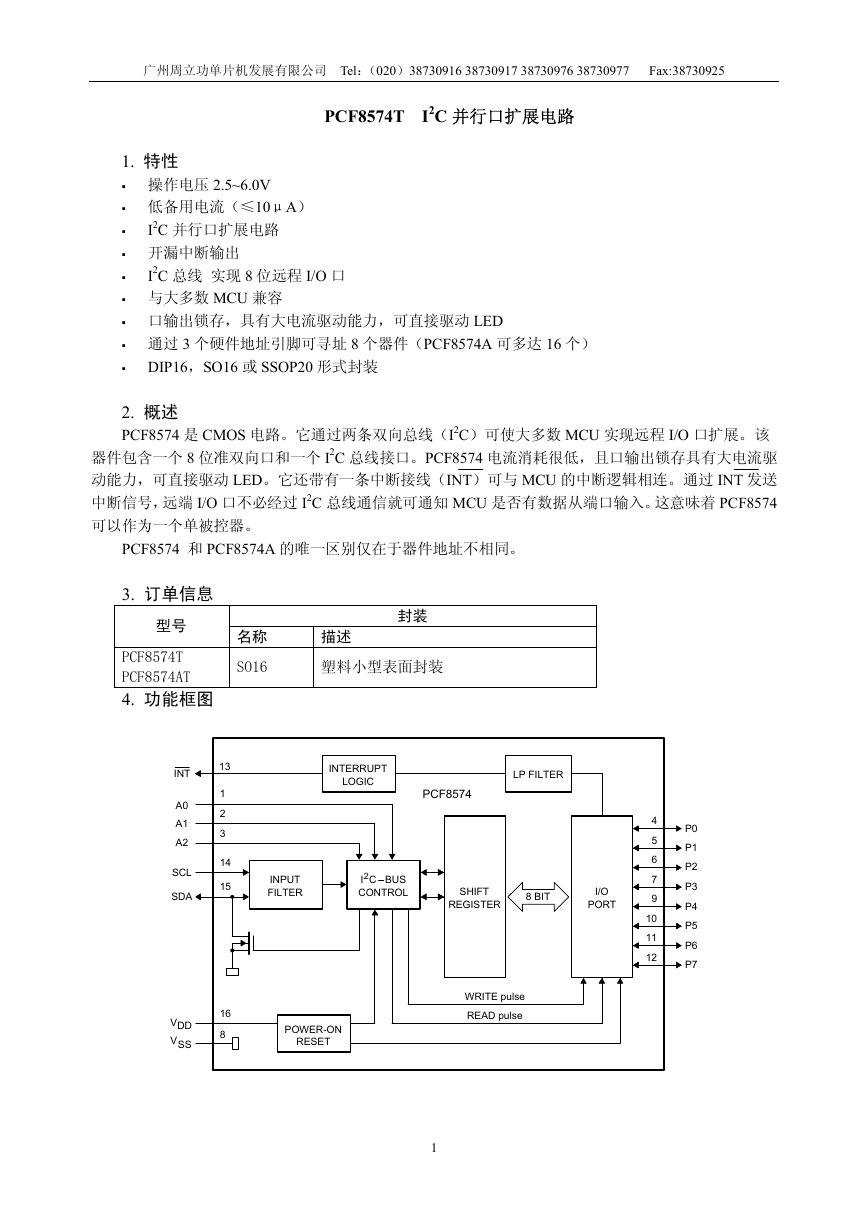

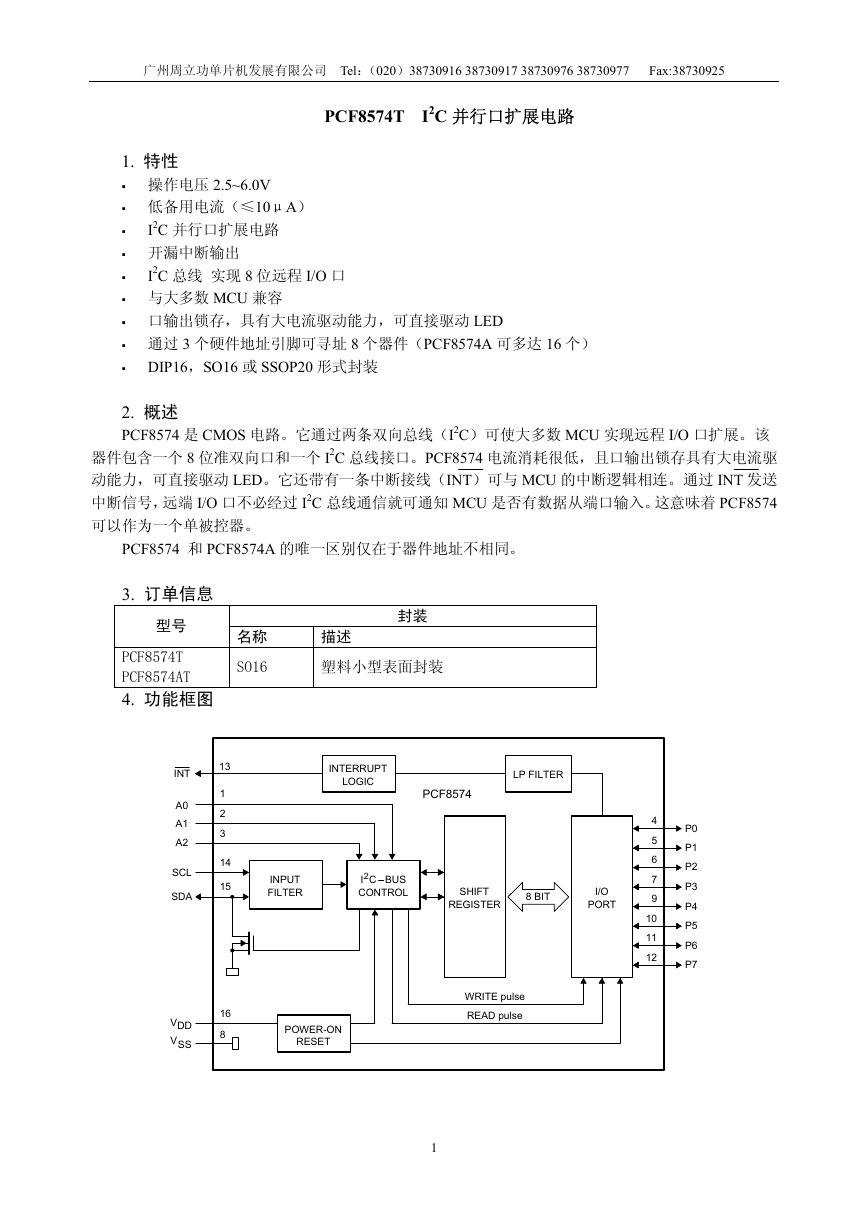

4. 功能框图

名称

SO16

封装

描述

塑料小型表面封装

13

1

2

3

14

15

16

8

INT

A0

A1

A2

SCL

SDA

VDD

VSS

INTERRUPT

LOGIC

PCF8574

LP FILTER

INPUT

FILTER

2

I C BUS

CONTROL

SHIFT

REGISTER

8 BIT

I/O

PORT

POWER-ON

RESET

WRITE pulse

READ pulse

1

4

5

6

7

9

10

11

12

P0

P1

P2

P3

P4

P5

P6

P7

�

广州周立功单片机发展有限公司 Tel:(020)38730916 38730917 38730976 38730977 Fax:38730925

5. 管脚描述

标号

管脚

SO16

描述

A0

A1

A2

P0

P1

P2

P3

VSS

P4

P5

P6

P7

INT

SCL

SDA

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

地址输入 0

地址输入 1

地址输入 2

准双向 I/O 口 0

准双向 I/O 口 1

准双向 I/O 口 2

准双向 I/O 口 3

地

准双向 I/O 口 4

准双向 I/O 口 5

准双向 I/O 口 6

准双向 I/O 口 7

中断输入(低电平有效)

串行时钟线

串行数据线

电源

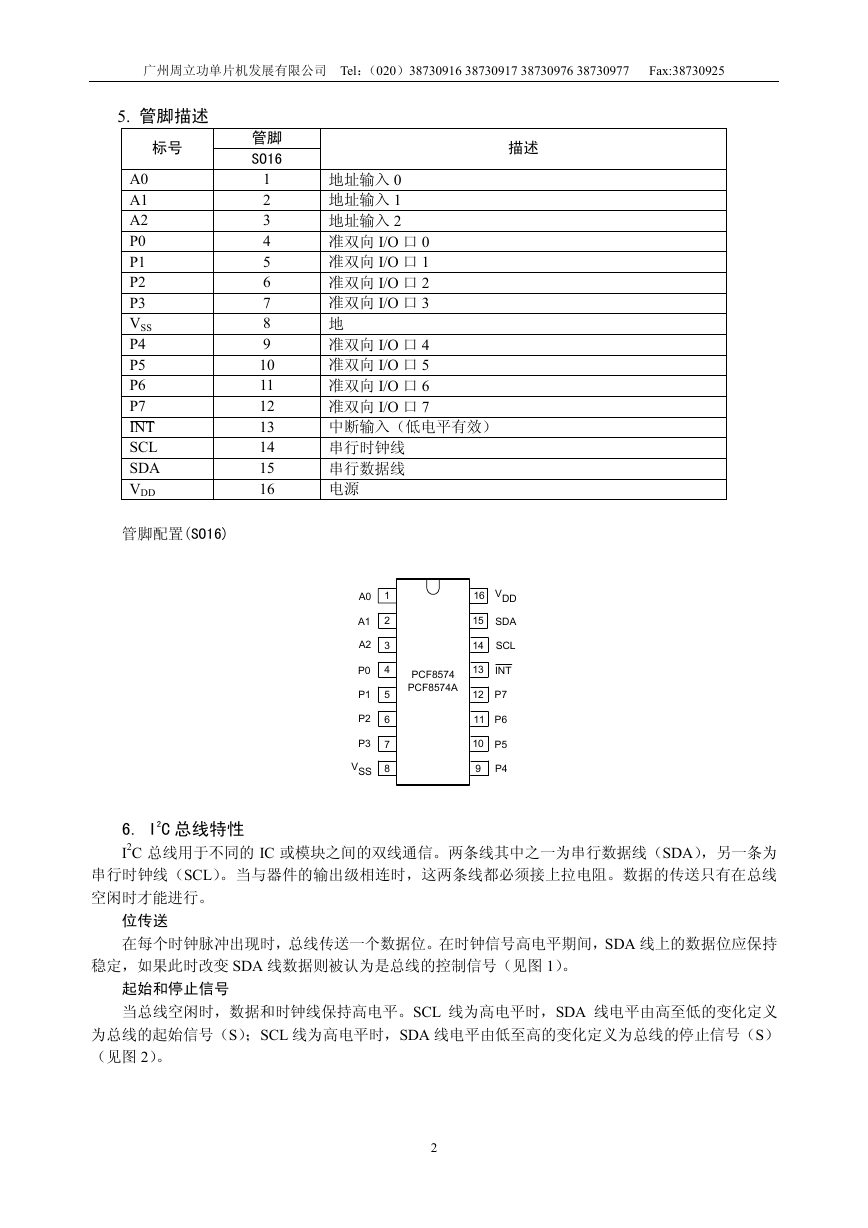

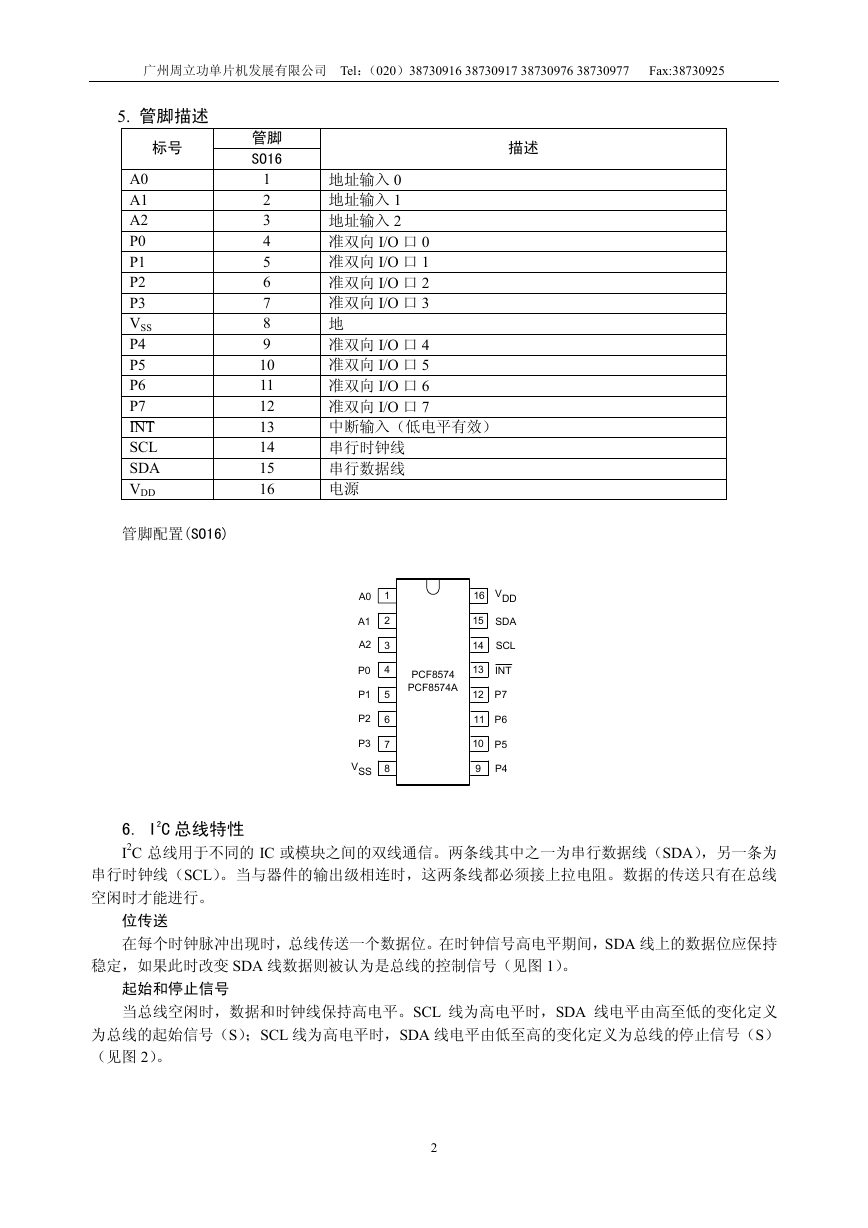

管脚配置(SO16)

A0

A1

A2

P0

P1

P2

P3

VSS

1

2

3

4

5

6

7

8

PCF8574

PCF8574A

16

15

14

13

12

VDD

SDA

SCL

INT

P7

11

P6

10

9

P5

P4

6. I2C 总线特性

I2C 总线用于不同的 IC 或模块之间的双线通信。两条线其中之一为串行数据线(SDA),另一条为

串行时钟线(SCL)。当与器件的输出级相连时,这两条线都必须接上拉电阻。数据的传送只有在总线

空闲时才能进行。

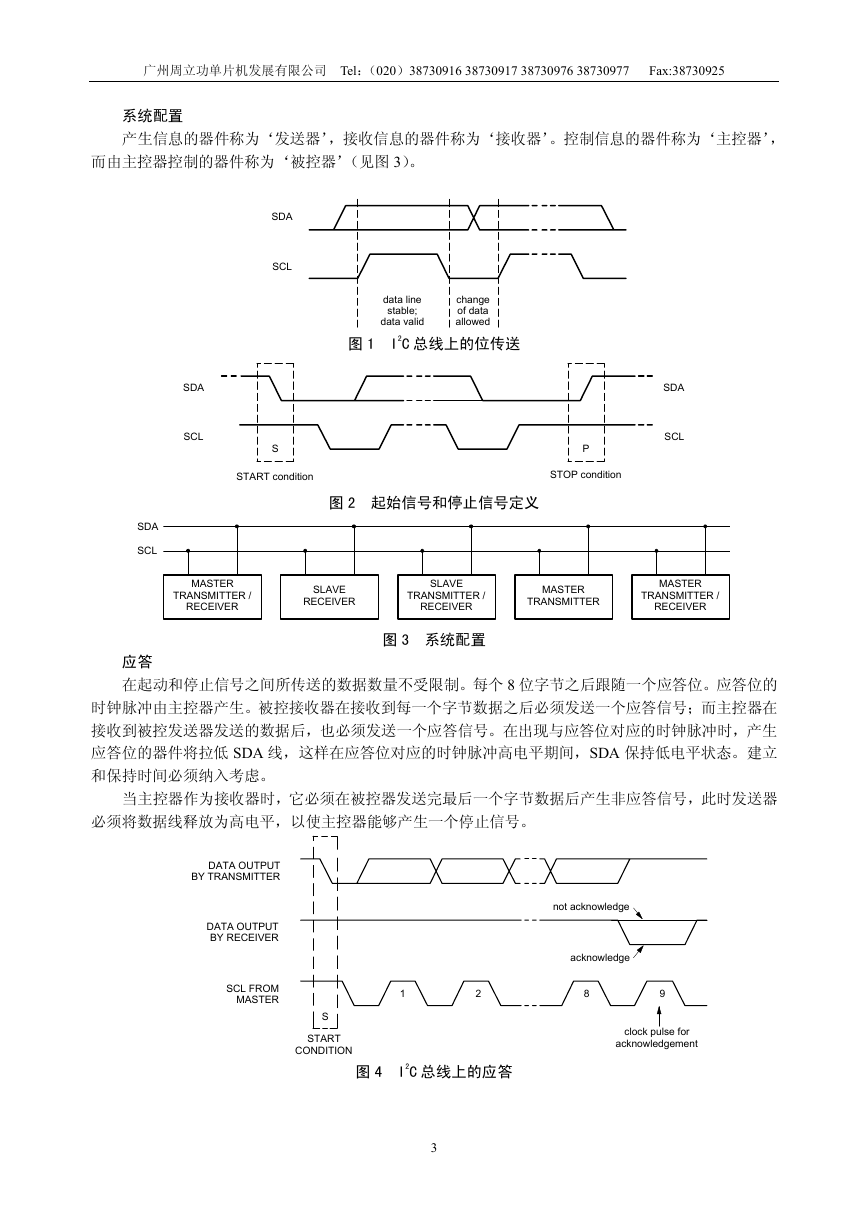

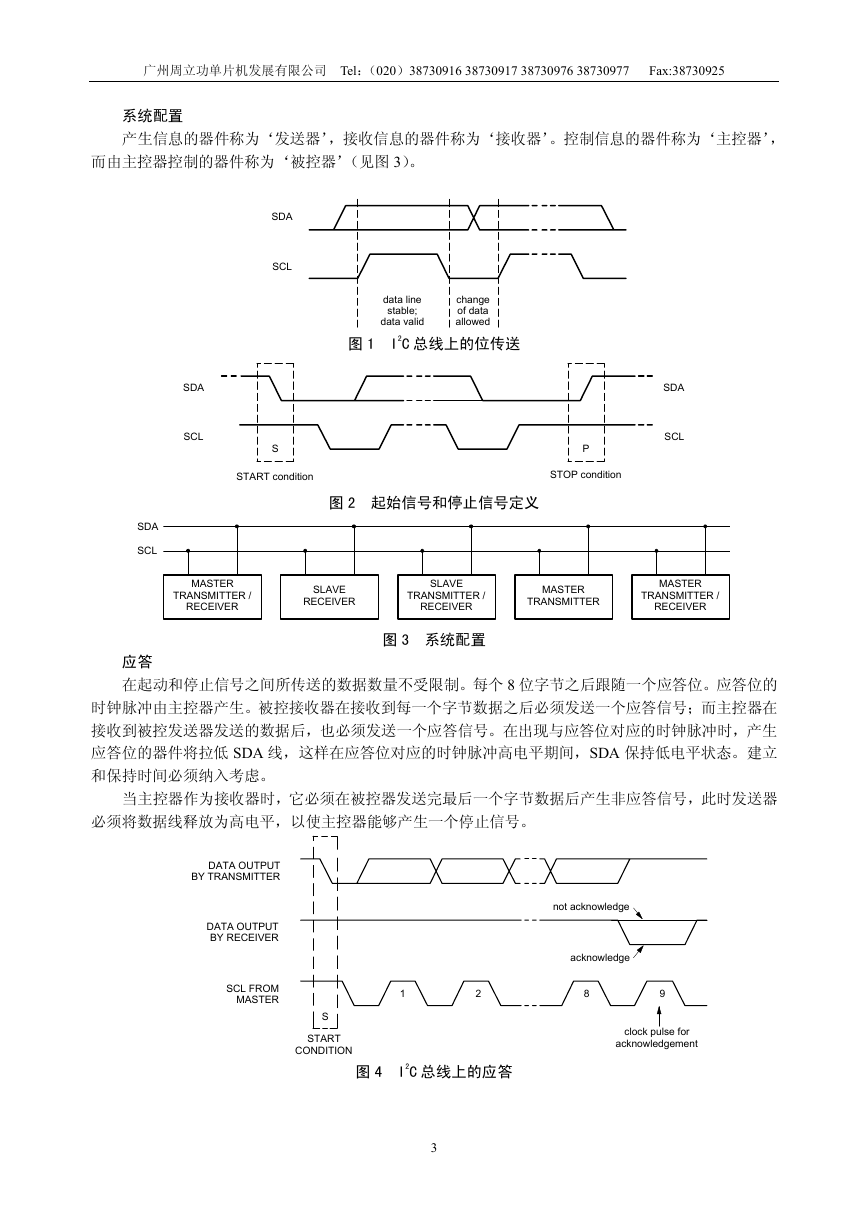

位传送

在每个时钟脉冲出现时,总线传送一个数据位。在时钟信号高电平期间,SDA 线上的数据位应保持

稳定,如果此时改变 SDA 线数据则被认为是总线的控制信号(见图 1)。

起始和停止信号

当总线空闲时,数据和时钟线保持高电平。SCL 线为高电平时,SDA 线电平由高至低的变化定义

为总线的起始信号(S);SCL 线为高电平时,SDA 线电平由低至高的变化定义为总线的停止信号(S)

(见图 2)。

2

�

广州周立功单片机发展有限公司 Tel:(020)38730916 38730917 38730976 38730977 Fax:38730925

系统配置

产生信息的器件称为‘发送器’,接收信息的器件称为‘接收器’。控制信息的器件称为‘主控器’,

而由主控器控制的器件称为‘被控器’(见图 3)。

SDA

SCL

data line

stable;

data valid

change

of data

allowed

图 1 I2C 总线上的位传送

SDA

SCL

S

START condition

SDA

SCL

图 2 起始信号和停止信号定义

SDA

SCL

P

STOP condition

MASTER

TRANSMITTER /

RECEIVER

SLAVE

RECEIVER

SLAVE

TRANSMITTER /

RECEIVER

MASTER

TRANSMITTER

MASTER

TRANSMITTER /

RECEIVER

图 3 系统配置

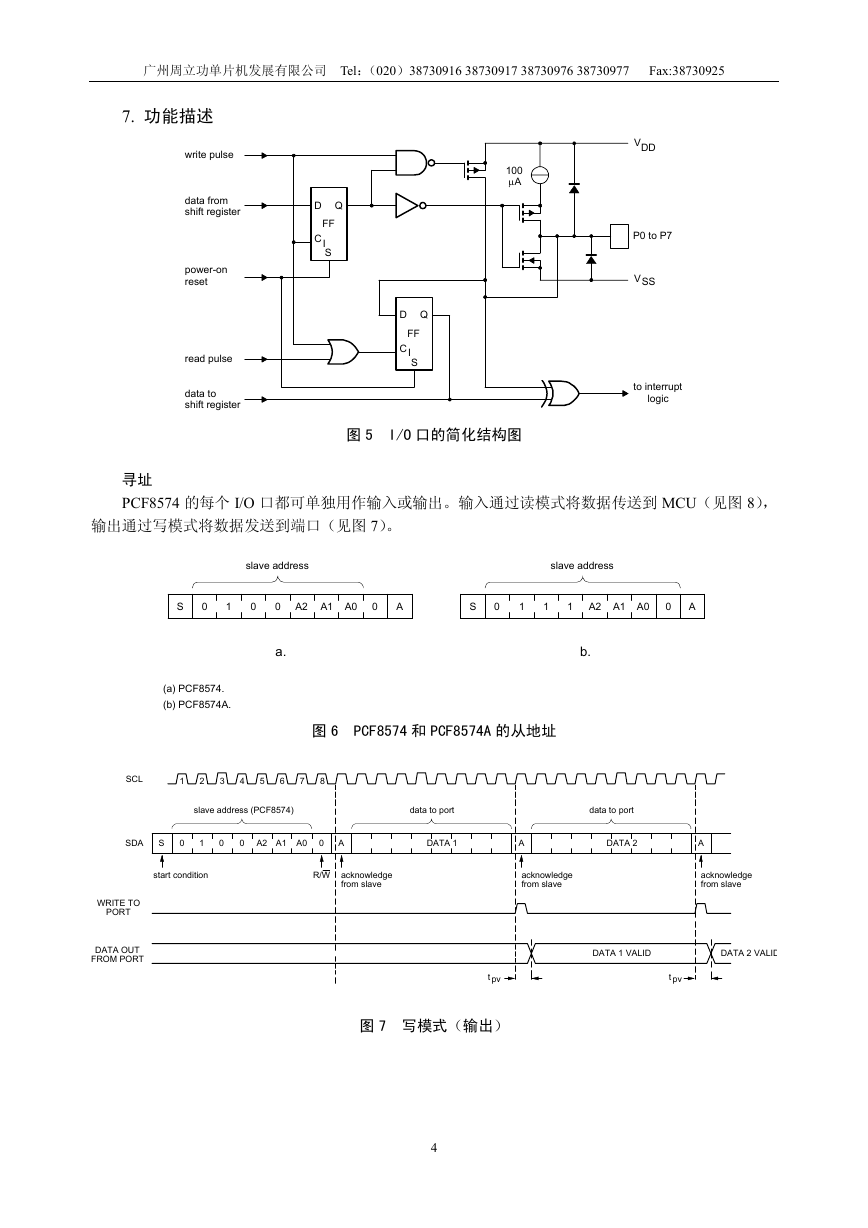

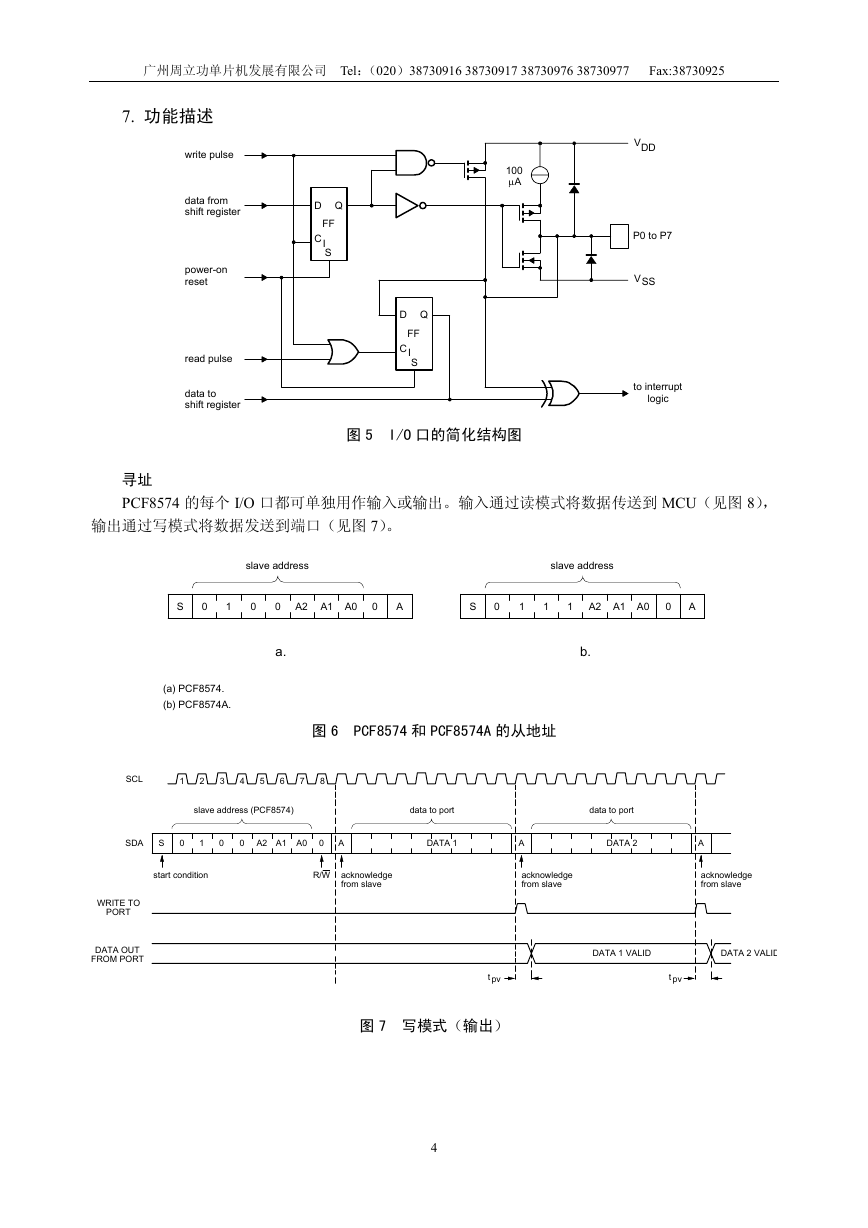

应答

在起动和停止信号之间所传送的数据数量不受限制。每个 8 位字节之后跟随一个应答位。应答位的

时钟脉冲由主控器产生。被控接收器在接收到每一个字节数据之后必须发送一个应答信号;而主控器在

接收到被控发送器发送的数据后,也必须发送一个应答信号。在出现与应答位对应的时钟脉冲时,产生

应答位的器件将拉低 SDA 线,这样在应答位对应的时钟脉冲高电平期间,SDA 保持低电平状态。建立

和保持时间必须纳入考虑。

当主控器作为接收器时,它必须在被控器发送完最后一个字节数据后产生非应答信号,此时发送器

必须将数据线释放为高电平,以使主控器能够产生一个停止信号。

DATA OUTPUT

BY TRANSMITTER

DATA OUTPUT

BY RECEIVER

SCL FROM

MASTER

not acknowledge

acknowledge

1

2

8

9

S

START

CONDITION

图 4 I2C 总线上的应答

clock pulse for

acknowledgement

3

�

广州周立功单片机发展有限公司 Tel:(020)38730916 38730917 38730976 38730977 Fax:38730925

7. 功能描述

write pulse

data from

shift register

power-on

reset

read pulse

data to

shift register

100

µA

D Q

FF

CI

S

D Q

FF

CI

S

图 5 I/O 口的简化结构图

VDD

P0 to P7

VSS

to interrupt

logic

寻址

输出通过写模式将数据发送到端口(见图 7)。

PCF8574 的每个 I/O 口都可单独用作输入或输出。输入通过读模式将数据传送到 MCU(见图 8),

slave address

slave address

S

0

1

0

0

A2 A1 A0

0

A

S

0

1

1

1

A2 A1 A0

0

A

a.

b.

(a) PCF8574.

(b) PCF8574A.

图 6 PCF8574 和 PCF8574A 的从地址

SCL

1

2

3

4

5

6

7

8

slave address (PCF8574)

data to port

data to port

SDA

S

0

1

0

0

A2 A1 A0

0

A

DATA 1

A

DATA 2

A

start condition

R/W acknowledge

from slave

acknowledge

from slave

acknowledge

from slave

WRITE TO

PORT

DATA OUT

FROM PORT

DATA 1 VALID

DATA 2 VALID

t pv

t pv

图 7 写模式(输出)

4

�

广州周立功单片机发展有限公司 Tel:(020)38730916 38730917 38730976 38730977 Fax:38730925

slave address (PCF8574)

data from port

data from port

SDA

S

0

1

0

0

A2 A1 A0

1

A

DATA 1

A

DATA 4

1

P

start condition

R/W acknowledge

from slave

acknowledge

from slave

stop

condition

READ FROM

PORT

DATA INTO

PORT

INT

t iv

DATA 2

DATA 3

DATA 4

tph

t ps

t ir

图 8 读模式(输入)

t ir

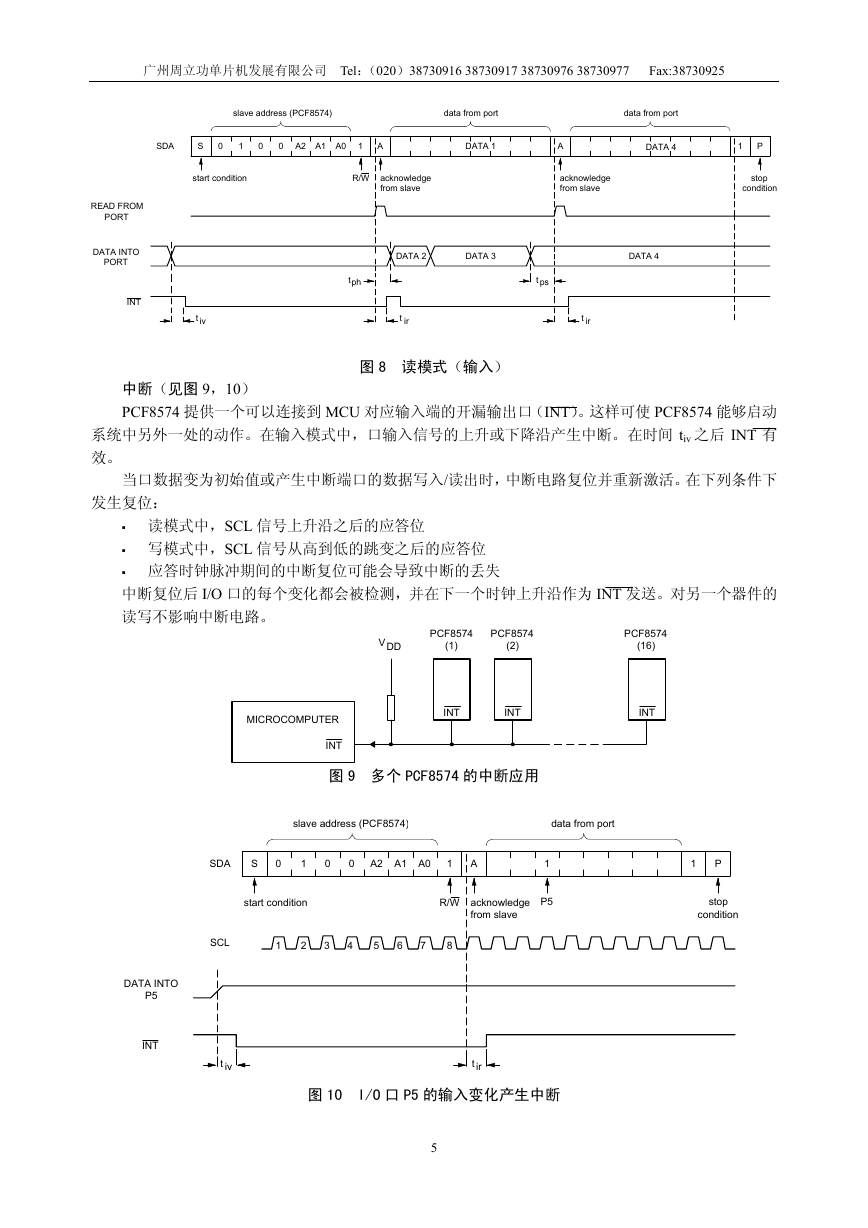

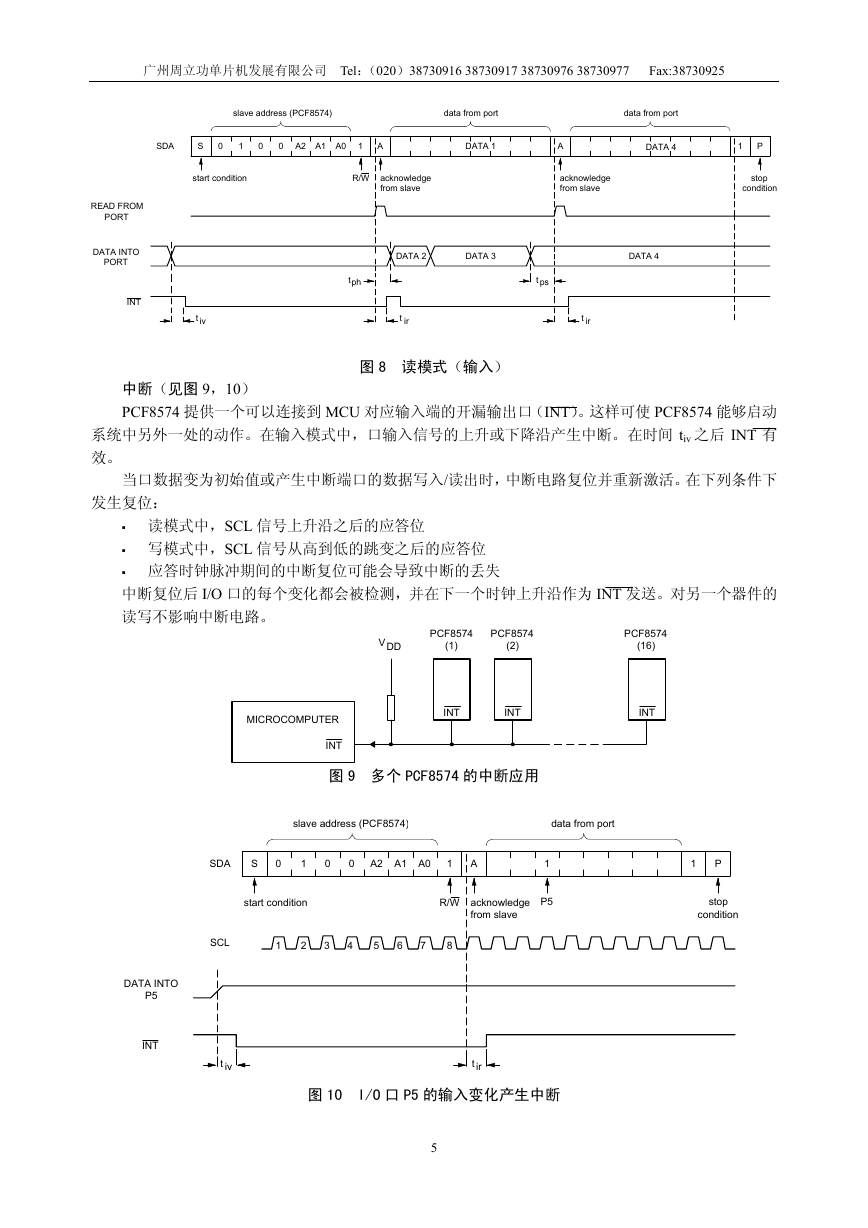

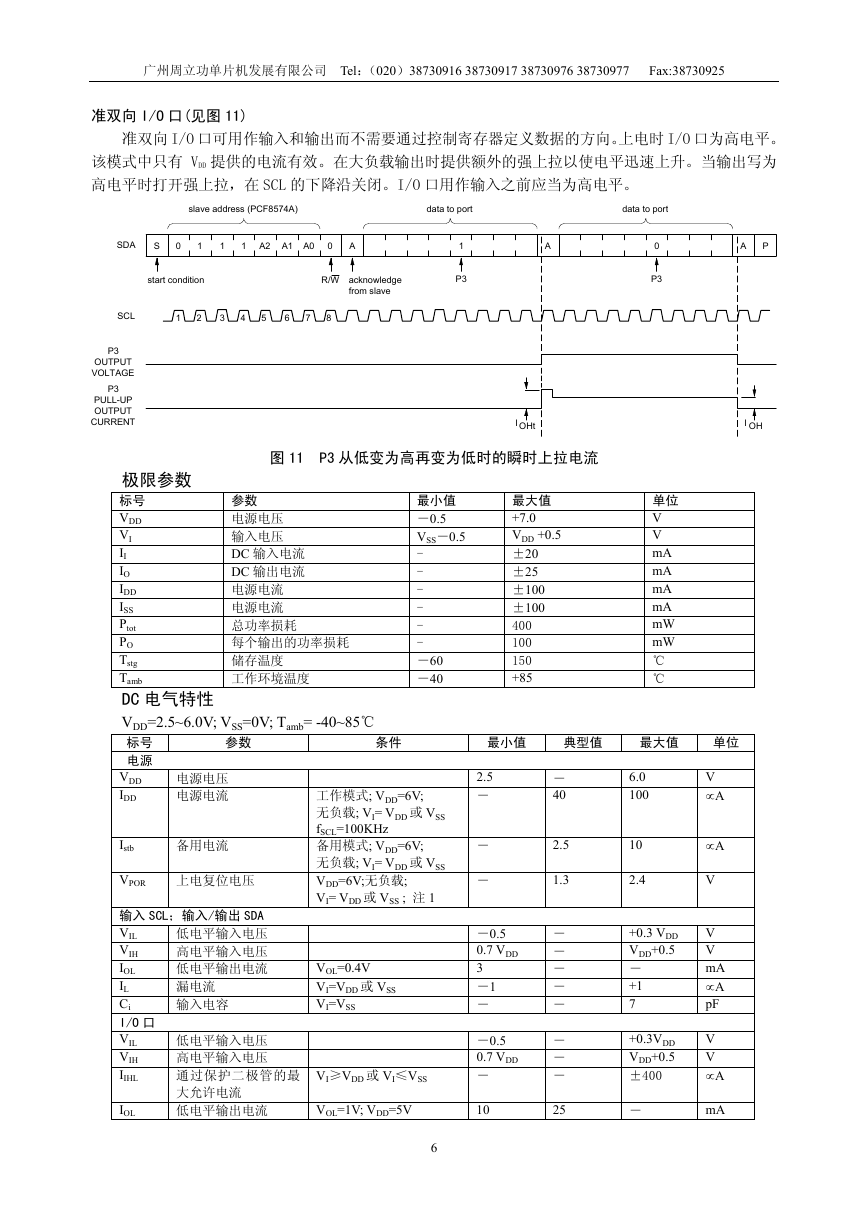

中断(见图 9,10)

PCF8574 提供一个可以连接到 MCU 对应输入端的开漏输出口(INT)。这样可使 PCF8574 能够启动

系统中另外一处的动作。在输入模式中,口输入信号的上升或下降沿产生中断。在时间 tiv 之后 INT 有

效。

当口数据变为初始值或产生中断端口的数据写入/读出时,中断电路复位并重新激活。在下列条件下

发生复位:

读模式中,SCL 信号上升沿之后的应答位

写模式中,SCL 信号从高到低的跳变之后的应答位

应答时钟脉冲期间的中断复位可能会导致中断的丢失

中断复位后 I/O 口的每个变化都会被检测,并在下一个时钟上升沿作为 INT 发送。对另一个器件的

读写不影响中断电路。

PCF8574

PCF8574

VDD

(1)

(2)

PCF8574

(16)

MICROCOMPUTER

INT

INT

INT

INT

图 9 多个 PCF8574 的中断应用

slave address (PCF8574)

data from port

SDA

S

0

1

0

0

A2 A1 A0

1

A

start condition

R/W acknowledge

from slave

SCL

1

2

3

4

5

6

7

8

1

P5

1

P

stop

condition

DATA INTO

P5

INT

t iv

t ir

图 10 I/O 口 P5 的输入变化产生中断

5

�

广州周立功单片机发展有限公司 Tel:(020)38730916 38730917 38730976 38730977 Fax:38730925

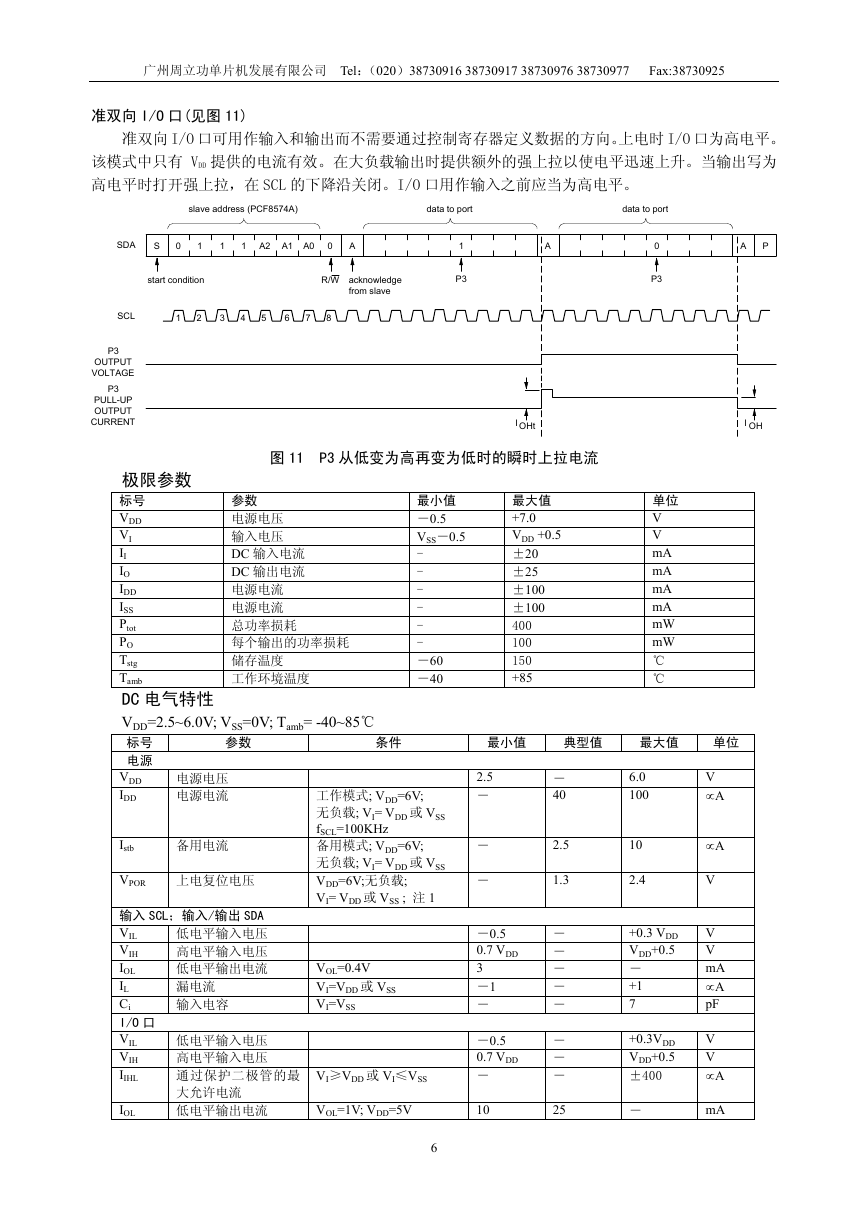

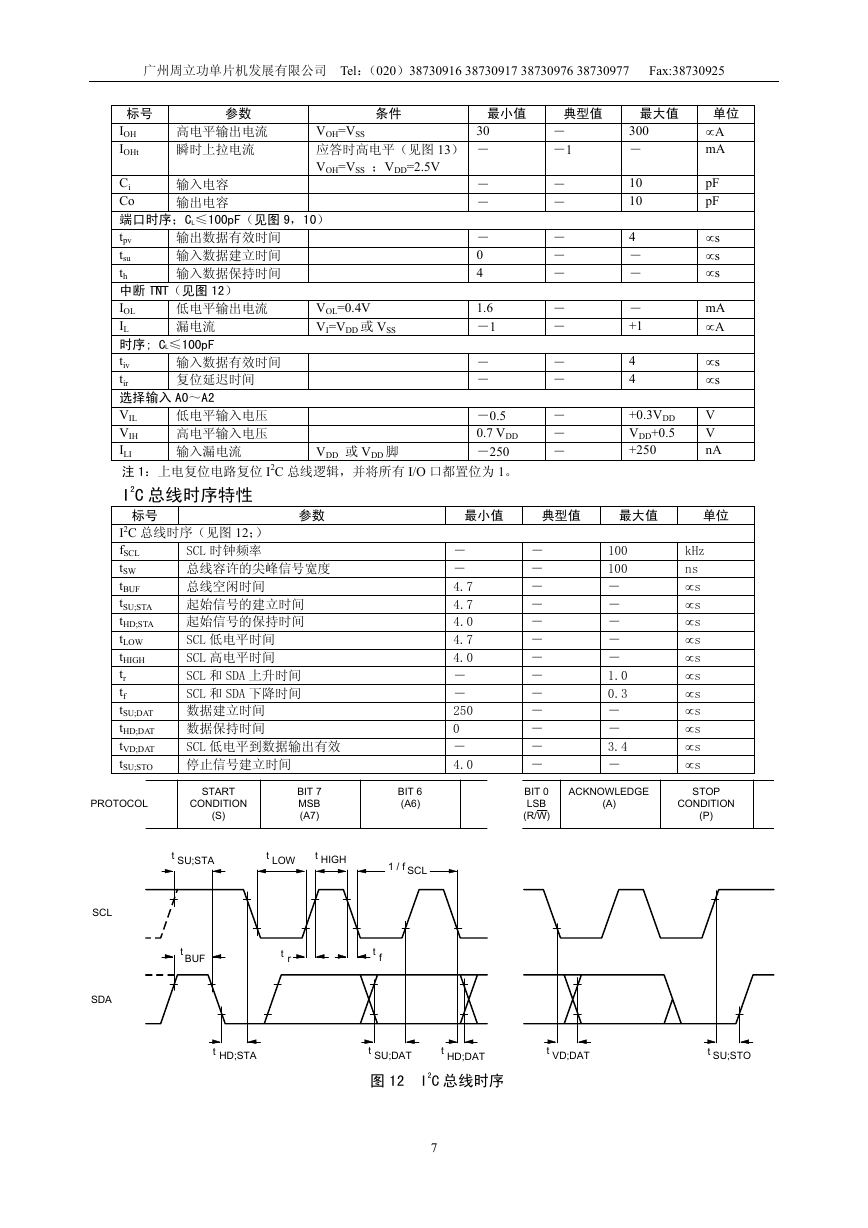

准双向 I/O 口(见图 11)

准双向 I/O 口可用作输入和输出而不需要通过控制寄存器定义数据的方向。上电时 I/O 口为高电平。

该模式中只有 VDD 提供的电流有效。在大负载输出时提供额外的强上拉以使电平迅速上升。当输出写为

高电平时打开强上拉,在 SCL 的下降沿关闭。I/O 口用作输入之前应当为高电平。

slave address (PCF8574A)

data to port

data to port

SDA

S

0

1

1

1

A2 A1 A0

0

A

start condition

R/W acknowledge

from slave

SCL

1

2

3

4

5

6

7

8

A

1

P3

A

P

0

P3

P3

OUTPUT

VOLTAGE

P3

PULL-UP

OUTPUT

CURRENT

极限参数

图 11 P3 从低变为高再变为低时的瞬时上拉电流

I OHt

I OH

参数

电源电压

输入电压

DC 输入电流

DC 输出电流

电源电流

电源电流

总功率损耗

每个输出的功率损耗

储存温度

工作环境温度

标号

VDD

VI

II

IO

IDD

ISS

Ptot

PO

Tstg

Tamb

DC 电气特性

VDD=2.5~6.0V; VSS=0V; Tamb= -40~85℃

标号

电源

VDD

IDD

电源电压

电源电流

参数

条件

最小值

-0.5

VSS-0.5

-

-

-

-

-

-

-60

-40

最大值

+7.0

VDD +0.5

±20

±25

±100

±100

400

100

150

+85

单位

V

V

mA

mA

mA

mA

mW

mW

℃

℃

最小值

典型值

最大值

单位

Istb

备用电流

VPOR

上电复位电压

输入 SCL;输入/输出 SDA

VIL

低电平输入电压

VIH

高电平输入电压

IOL

低电平输出电流

IL

漏电流

Ci

输入电容

I/O 口

VIL

VIH

IIHL

低电平输入电压

高电平输入电压

通过保护二极管的最

大允许电流

低电平输出电流

IOL

工作模式; VDD=6V;

无负载; VI= VDD 或 VSS

fSCL=100KHz

备用模式; VDD=6V;

无负载; VI= VDD 或 VSS

VDD=6V;无负载;

VI= VDD 或 VSS ; 注 1

VOL=0.4V

VI=VDD 或 VSS

VI=VSS

VI≥VDD 或 VI≤VSS

2.5

-

-

-

-0.5

0.7 VDD

3

-1

-

-0.5

0.7 VDD

-

VOL=1V; VDD=5V

10

6

-

40

2.5

1.3

-

-

-

-

-

-

-

-

25

6.0

100

10

2.4

+0.3 VDD

VDD+0.5

-

+1

7

+0.3VDD

VDD+0.5

±400

-

V

∝A

∝A

V

V

V

mA

∝A

pF

V

V

∝A

mA

�

广州周立功单片机发展有限公司 Tel:(020)38730916 38730917 38730976 38730977 Fax:38730925

标号

IOH

IOHt

参数

高电平输出电流

瞬时上拉电流

最小值

30

-

典型值

-

-1

最大值

300

-

单位

∝A

mA

条件

VOH=VSS

应答时高电平(见图 13)

VOH=VSS ;VDD=2.5V

输入电容

输出电容

输出数据有效时间

输入数据建立时间

输入数据保持时间

Ci

Co

端口时序;CL≤100pF(见图 9,10)

tpv

tsu

th

中断 INT(见图 12)

IOL

低电平输出电流

IL

漏电流

时序; CL≤100pF

tiv

tir

选择输入 A0~A2

VIL

-0.5

0.7 VDD

VIH

ILI

-250

注 1:上电复位电路复位 I2C 总线逻辑,并将所有 I/O 口都置位为 1。

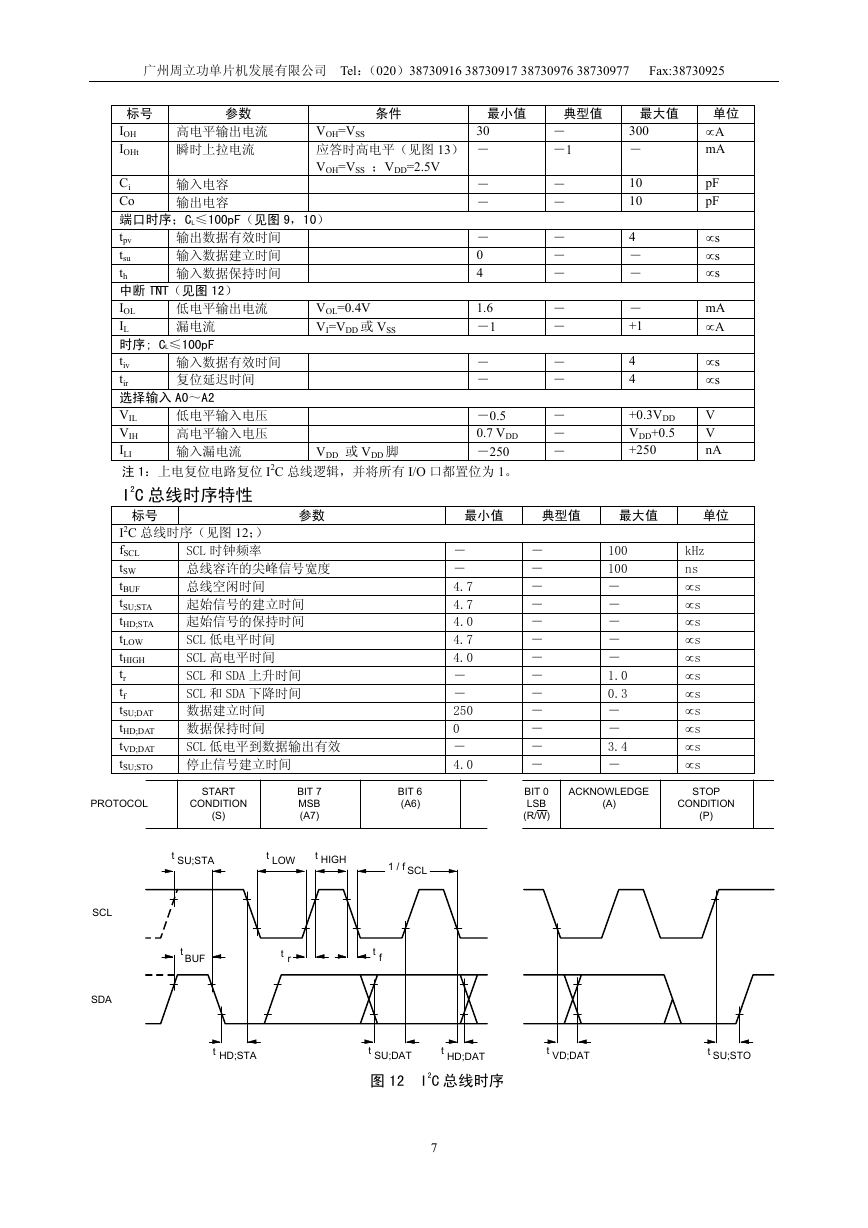

I2C 总线时序特性

低电平输入电压

高电平输入电压

输入漏电流

VDD 或 VDD 脚

输入数据有效时间

复位延迟时间

VOL=0.4V

VI=VDD 或 VSS

-

-

-

0

4

1.6

-1

-

-

-

-

-

-

-

-

-

-

-

-

-

-

10

10

4

-

-

-

+1

4

4

+0.3VDD

VDD+0.5

+250

pF

pF

∝s

∝s

∝s

mA

∝A

∝s

∝s

V

V

nA

标号

参数

I2C 总线时序(见图 12;)

fSCL

SCL 时钟频率

tSW

总线容许的尖峰信号宽度

tBUF

总线空闲时间

tSU;STA

起始信号的建立时间

tHD;STA

起始信号的保持时间

tLOW

SCL 低电平时间

tHIGH

SCL 高电平时间

tr

SCL 和 SDA 上升时间

tf

SCL 和 SDA 下降时间

tSU;DAT

数据建立时间

tHD;DAT

数据保持时间

tVD;DAT

SCL 低电平到数据输出有效

tSU;STO

停止信号建立时间

PROTOCOL

START

CONDITION

(S)

BIT 7

MSB

(A7)

t SU;STA

t LOW

t HIGH

t BUF

rt

t f

最小值

典型值

最大值

单位

-

-

4.7

4.7

4.0

4.7

4.0

-

-

250

0

-

4.0

-

-

-

-

-

-

-

-

-

-

-

-

-

100

100

-

-

-

-

-

1.0

0.3

-

-

3.4

-

kHz

ns

∝s

∝s

∝s

∝s

∝s

∝s

∝s

∝s

∝s

∝s

∝s

BIT 0

LSB

(R/W)

ACKNOWLEDGE

(A)

BIT 6

(A6)

1 / f SCL

STOP

CONDITION

(P)

SCL

SDA

t HD;STA

t SU;DAT

t HD;DAT

t VD;DAT

t SU;STO

图 12 I2C 总线时序

7

�

广州周立功单片机发展有限公司 Tel:(020)38730916 38730917 38730976 38730977 Fax:38730925

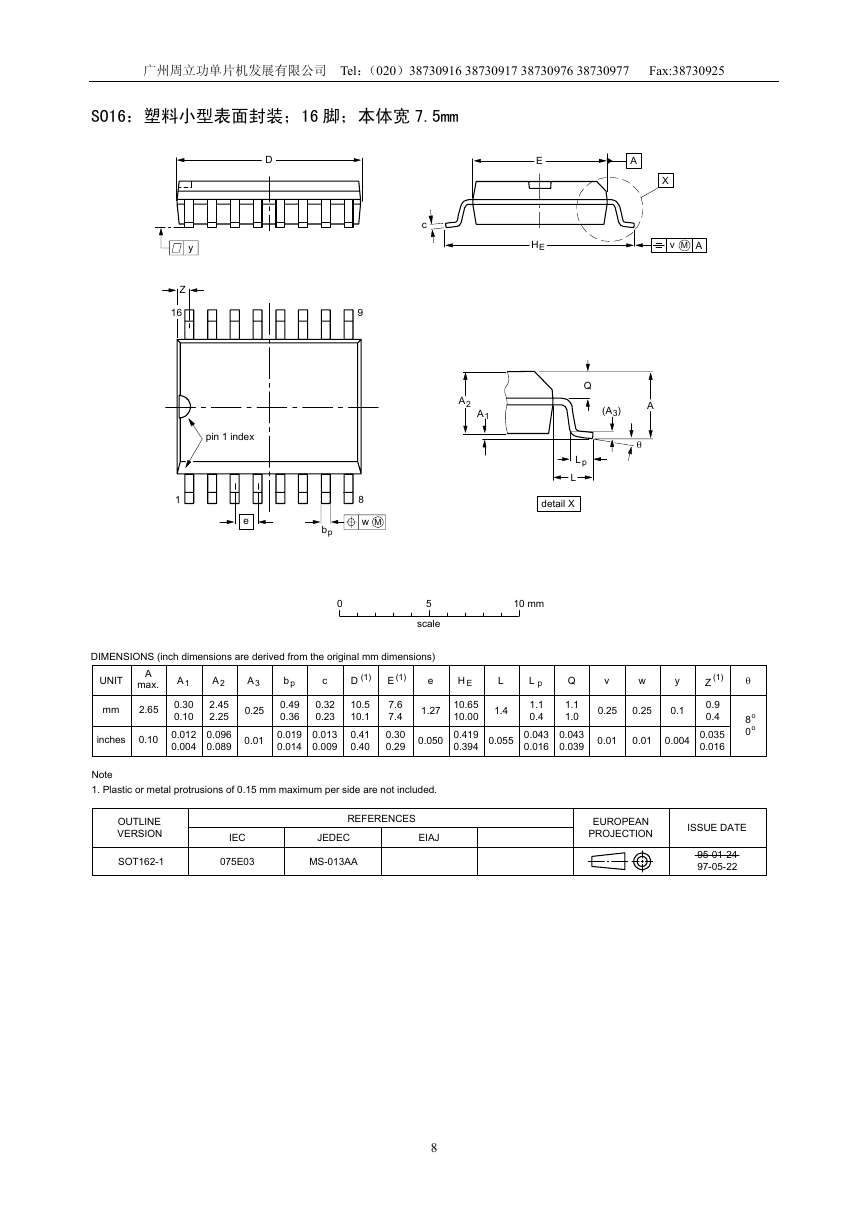

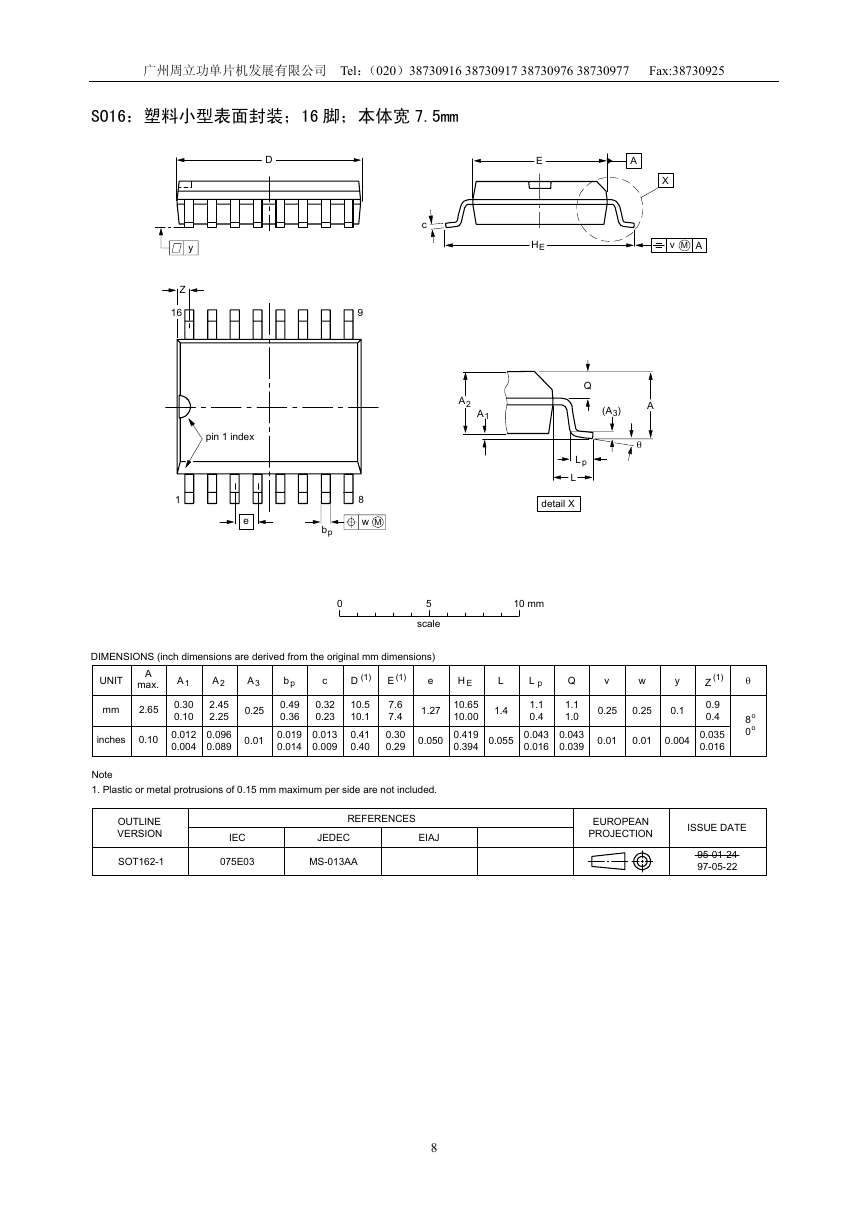

SO16:塑料小型表面封装;16 脚;本体宽 7.5mm

D

y

Z

16

pin 1 index

1

e

E

HE

A

X

v M A

c

9

A2

A1

(A )3

A

θ

Q

Lp

L

detail X

5

scale

10 mm

8

w M

bp

0

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

UNIT

mm

A

max.

2.65

inches

0.10

A1

A 2

A 3

b p

c

D (1)

E (1)

e

0.30

0.10

0.012

0.004

2.45

2.25

0.096

0.089

0.25

0.01

0.49

0.36

0.019

0.014

0.32

0.23

0.013

0.009

10.5

10.1

0.41

0.40

7.6

7.4

0.30

0.29

1.27

0.050

H E

10.65

10.00

0.419

0.394

L

1.4

0.055

L p

1.1

0.4

0.043

0.016

Q

v

w

y

1.1

1.0

0.043

0.039

0.25

0.25

0.1

0.01

0.01

0.004

(1)

Z

0.9

0.4

0.035

0.016

θ

o

o

8

0

Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

OUTLINE

VERSION

SOT162-1

REFERENCES

IEC

075E03

JEDEC

MS-013AA

EIAJ

EUROPEAN

PROJECTION

ISSUE DATE

95-01-24

97-05-22

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc