Cir c u its & th e ir a p p lic a tio n s

文章编号: 1002- 8692( 2007) 04- 0031- 02

1024QAM 调制解调系统的 FPGA 实现 *

·实用技术·

梁海丽, 段吉海, 游路路

( 桂林电子科技大学 通信与信息工程系, 广西 桂林 541004)

【摘 要 】 在 MQAM 调制 解 调 原理 的 基 础上 重 点 介绍 了 如 何利 用 DSP Builder 实 现 1024QAM 调 制 解 调系 统 模 型以 及 对 模型 进 行

算法级仿真和生成 VHDL 代码, 以及与第三方软件结合生成的 VHDL 代码如何下载到 FPGA 器件中进行验证。

【关键词】MQAM 调制解调; 1024QAM 建模; DSP Builder 工具

【文献标识码】B

【中图分类号】TN919.8

Implementation of the 1024QAM Demodulation System Based on FPGA

( Dept.of Telecommunication & Information Engineering, GUET, Guangxi Guilin 541004, China)

LIANG Hai- li, DUAN Ji- hai, YOU Lu- lu

【Abstr act】This paper introduces how to use DSPBuilder to implement the model of 1024QAM modulation and demodulation sys-

tem and how to simulate the grade of algorithms to the module and how to generate VHDL codes on the basic principle of

MQAM demodulation,

and briefly introduces how to download the VHDL code generated in combination with the 3rd party soft-

ware into the FPGA devices.

【Key wor ds】MQAM; 1024QAM; DSP builder

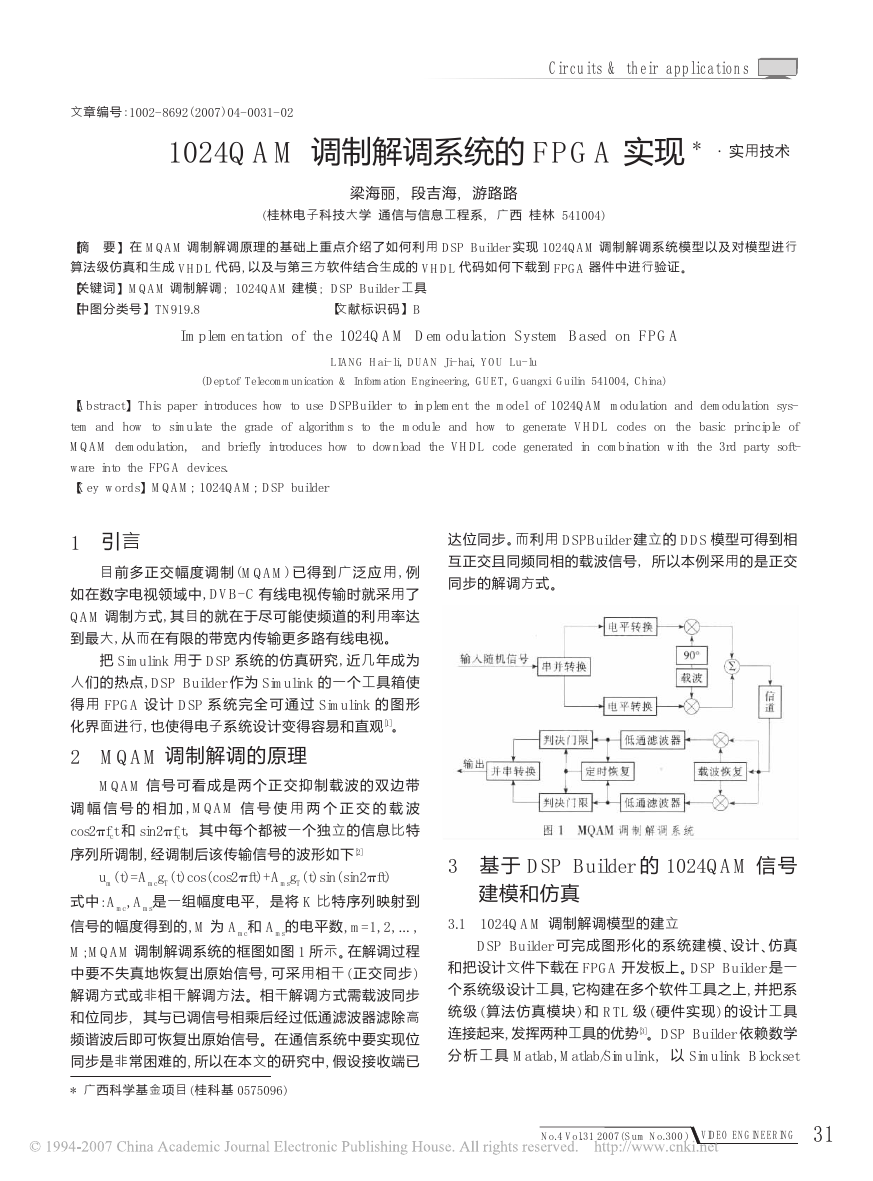

达位同步。而利用 DSPBuilder 建立的 DDS 模型可得到相

互正交且同频同相的载波信号, 所以本例采用的是正交

同步的解调方式。

1 引言

目前多正交幅度 调 制( MQAM) 已 得 到 广 泛 应 用, 例

如在数字电视领域中, DVB- C 有线电视传输时就采用了

QAM 调制方式, 其目的就在于尽可能使频道的利用率达

到最大, 从而在有限的带宽内传输更多路有线电视。

把 Simulink 用于 DSP 系统的仿真研究, 近几年成为

人们的热点, DSP Builder 作为 Simulink 的一个工具箱使

得 用 FPGA 设 计 DSP 系 统 完 全 可 通 过 Simulink 的 图 形

化界面进行, 也使得电子系统设计变得容易和直观[1]。

2 MQAM 调制解调的原理

MQAM 信 号 可 看 成 是 两 个 正 交 抑 制 载 波 的 双 边 带

调 幅 信 号 的 相 加 , MQAM 信 号 使 用 两 个 正 交 的 载 波

cos2!f

t, 其中每个都被一个独立的信息比特

序列所调制, 经调制后该传输信号的波形如下[2]

t 和 sin2!f

c

c

, A

mc

ms

g

T

ms

( t) sin( sin2!ft)

( t) cos( cos2!ft) +A

u

( t) =A

m

式中: A

g

mc

T

是一组幅度电平, 是将 K 比特序列映射到

信号的幅度得到的, M 为 A

的电平数, m=1, 2, …,

M; MQAM 调制解调系统的框图如图 1 所示。在解调过程

中要不失真地恢复出原始信号, 可采用相干( 正 交同步)

和 A

mc

ms

解调方式或非相干解调方法。相干解调方式需载波同步

和位同步, 其与已调信号相乘后经过低通滤波器滤除高

频谐波后即可恢复出原始信号。在通信系统中要实现位

同步是非常困难的, 所以在本文的研究中, 假设接收端已

* 广西科学基金项目( 桂科基 0575096)

3 基 于 DSP Builder 的 1024QAM 信 号

建模和仿真

3.1 1024QAM 调制解调模型的建立

DSP Builder 可完成 图 形 化 的 系 统 建 模 、设 计 、仿 真

和把设计文件下载在 FPGA 开发板上。DSP Builder 是一

个系统级设计工具, 它构建在多个软件工具之上, 并把系

统 级( 算 法 仿 真 模 块) 和 RTL 级( 硬 件 实 现) 的设计工具

连接起来, 发挥两种工具的优势[3]。DSP Builder 依赖数学

分 析 工 具 Matlab, Matlab/Simulink, 以 Simulink Blockset

No.4 Vol.31 2007( Sum No.300 )

VIDEO ENGINEERING

31

�

电 路 与 应 用

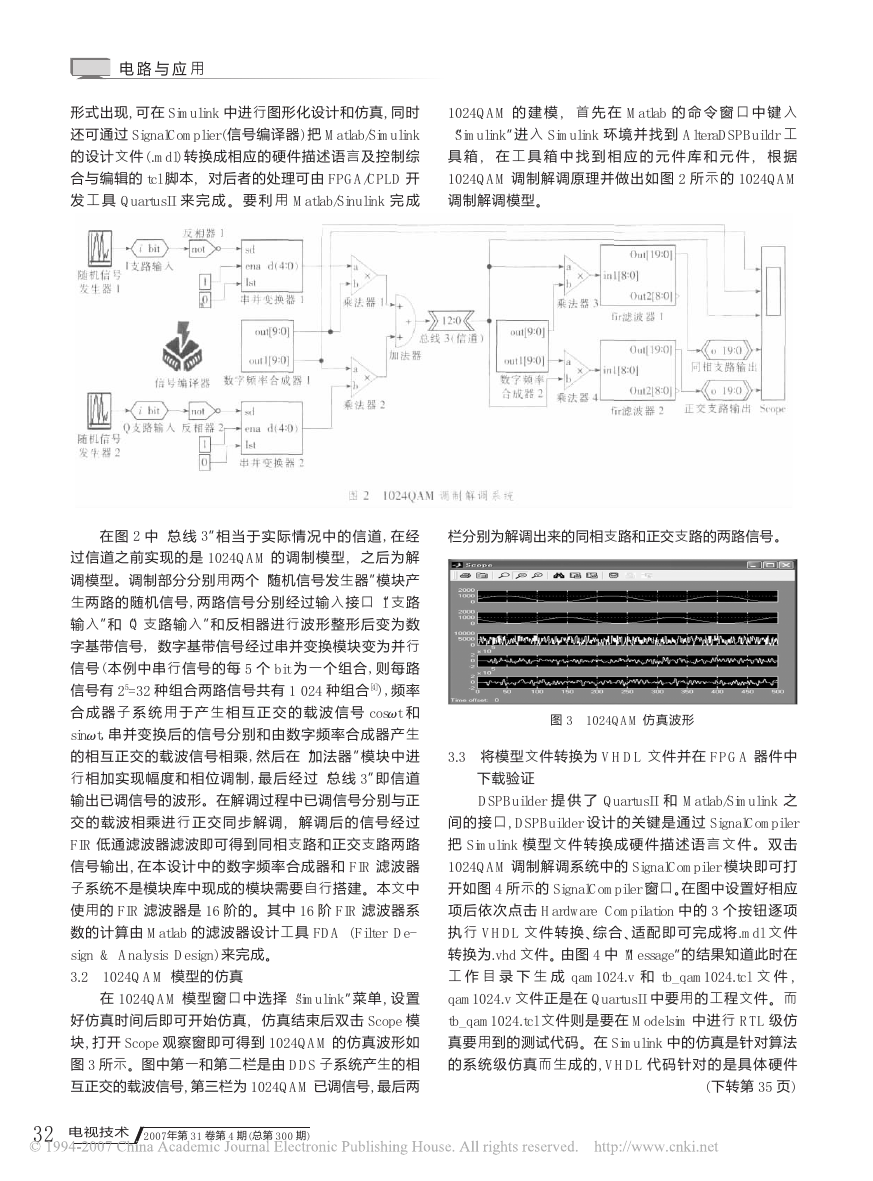

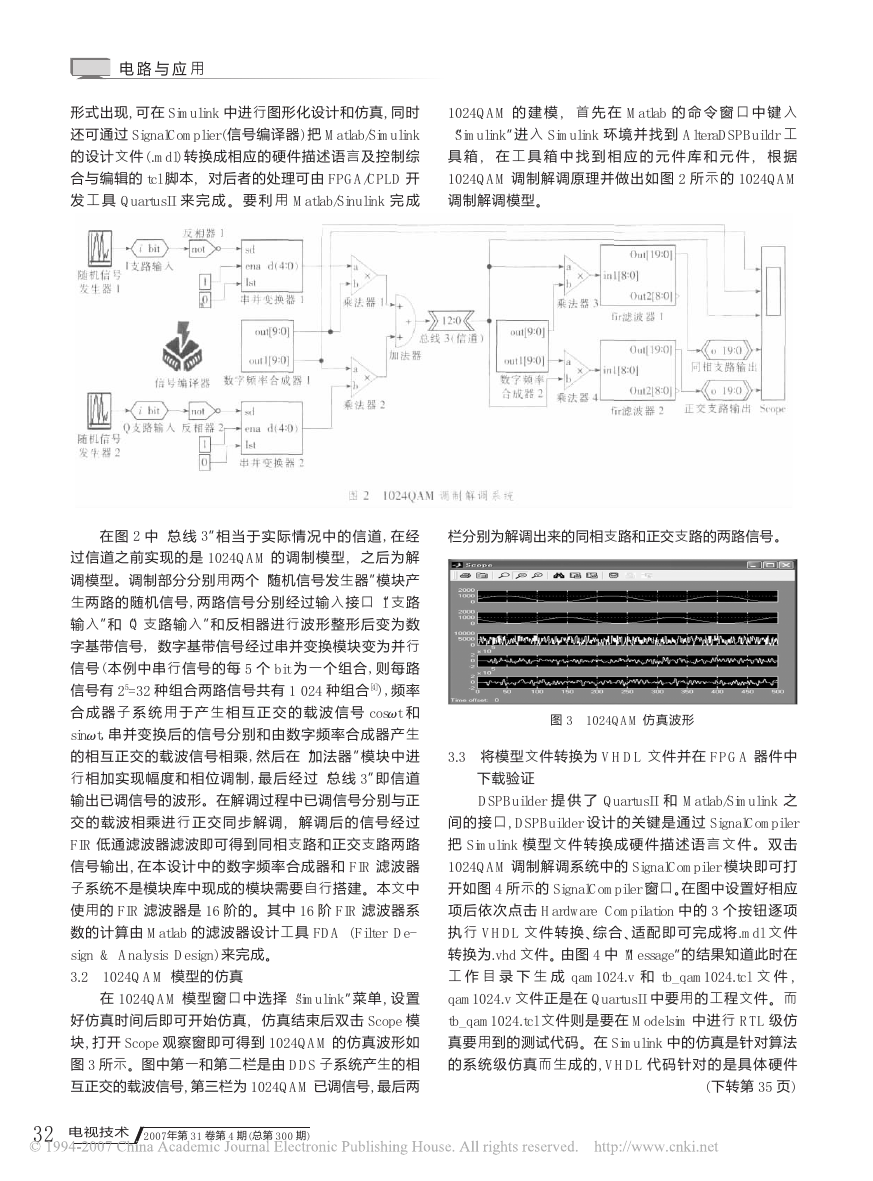

形式出现, 可在 Simulink 中进行图形化设计和仿真, 同时

还可通过 SignalComplier( 信号编译器) 把 Matlab/Simulink

的设计文件( .mdl) 转换成相应的硬件描述语言及控制综

合与编辑的 tcl 脚本, 对后者的处理可由 FPGA/CPLD 开

发 工 具 QuartusII 来 完 成 。 要 利 用 Matlab/Sinulink 完 成

1024QAM 的 建 模 , 首 先 在 Matlab 的 命 令 窗 口 中 键 入

“Simulink”进 入 Simulink 环 境 并 找 到 AlteraDSPBuildr 工

具 箱 , 在 工 具 箱 中 找 到 相 应 的 元 件 库 和 元 件 , 根 据

1024QAM 调制解调原理并做出如图 2 所示 的 1024QAM

调制解调模型。

在图 2 中 “总 线 3”相 当 于 实 际 情 况 中 的 信 道, 在 经

过信道之前实现的是 1024QAM 的调制模型, 之后为解

调模型。调制部分分别用两个“随机信号发生器”模块产

生两路的随机信号, 两路信号分别经过输入接口“I 支路

输入”和“Q 支路输入”和反相器进行波 形整形后变为数

字基带信号, 数字基带信号经过串并变换模块变为并行

信号( 本例中串行信号的每 5 个 bit 为一个组合, 则每路

信号有 25=32 种组合两路信号共有 1 024 种组合[4]) , 频率

合 成 器 子 系 统 用 于 产 生 相 互 正 交 的 载 波 信 号 cos!t 和

sin!t, 串并变换后的信号分别和由数字频率合成器产生

的相互正交的载波信号相乘, 然后在“加法器 ”模块中进

行相加实现幅度和相位调制, 最 后 经 过 “总 线 3”即 信 道

输出已调信号的波形。在解调过程中已调信号分别与正

交 的 载 波 相 乘 进 行 正 交 同 步 解 调 , 解 调 后 的 信 号 经 过

FIR 低通滤波器滤波即可得到同相支路和正交支路两路

信号输出, 在本设计中的数字频率合成器和 FIR 滤波器

子系统不是模块库中现成的模块需要自行搭建。本文中

使用的 FIR 滤波器是 16 阶的。其中 16 阶 FIR 滤波器系

数的计算由 Matlab 的滤波器设计工具 FDA ( Filter De-

sign & Analysis Design) 来完成。

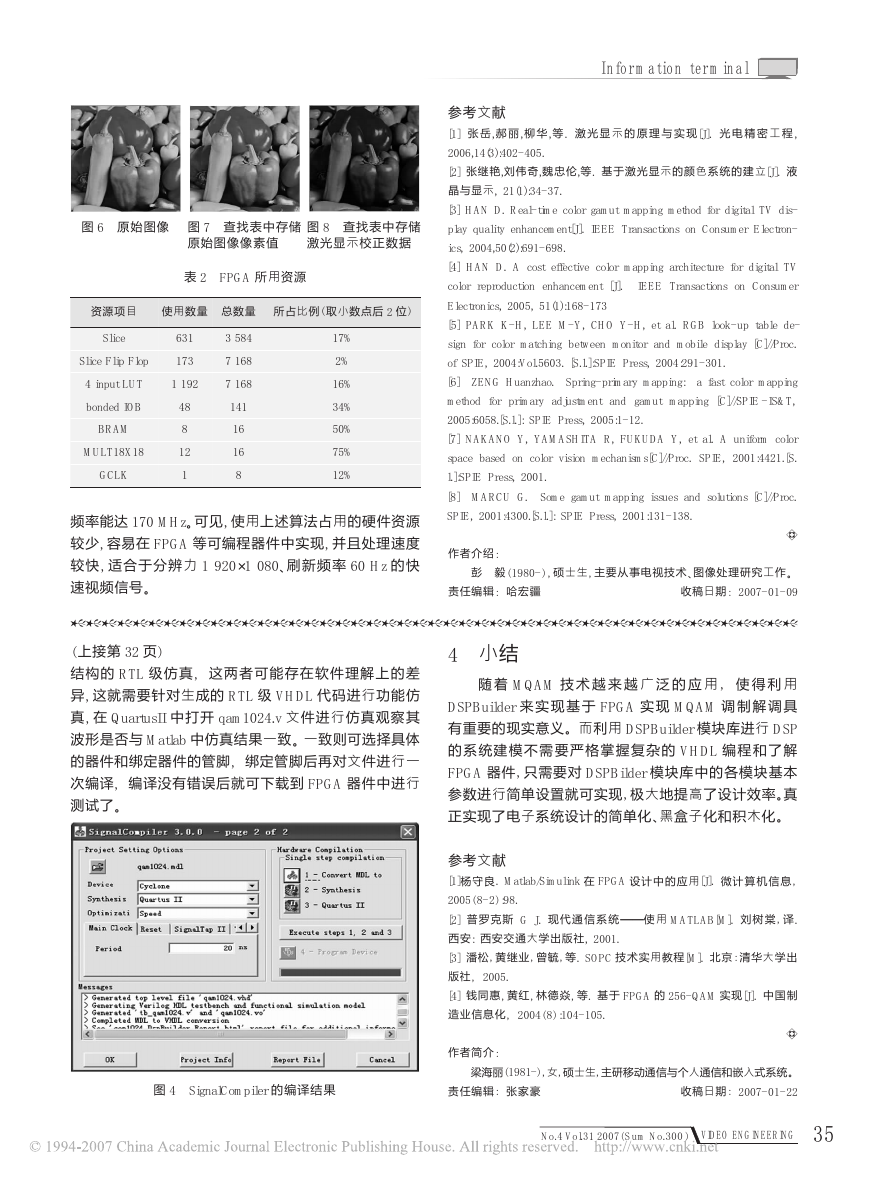

3.2 1024QAM 模型的仿真

在 1024QAM 模 型 窗 口 中 选 择 “simulink”菜 单, 设 置

好仿真时间后即可开始仿真, 仿真结束后双击 Scope 模

块, 打开 Scope 观察窗即可得到 1024QAM 的仿真波形如

图 3 所示。图中第一和第二栏是由 DDS 子系统产生的相

互正交的载波信号, 第三栏为 1024QAM 已调信号, 最后两

32

电视技术

2007年第 31 卷第 4 期( 总第 300 期)

栏分别为解调出来的同相支路和正交支路的两路信号。

图 3 1024QAM 仿真波形

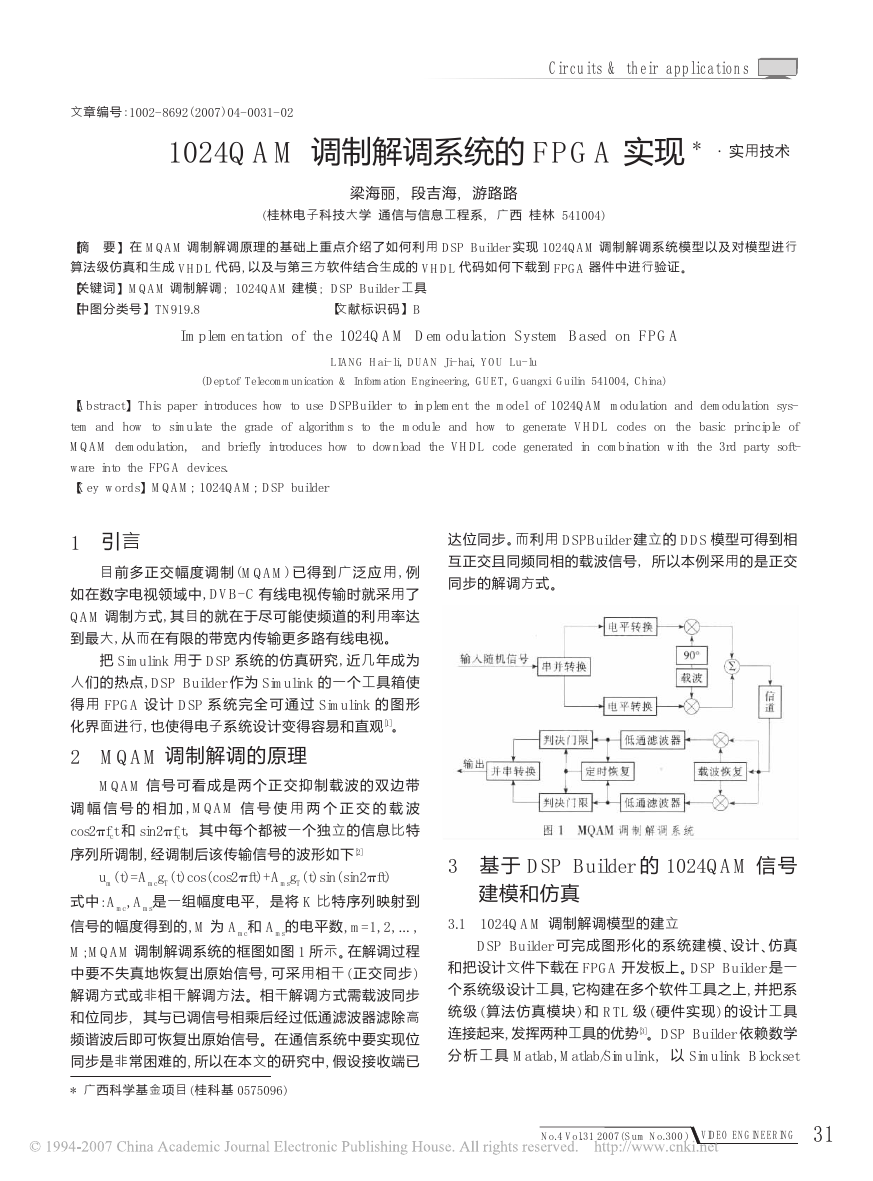

3.3 将模型文件转换为 VHDL 文件并在 FPGA 器件中

下载验证

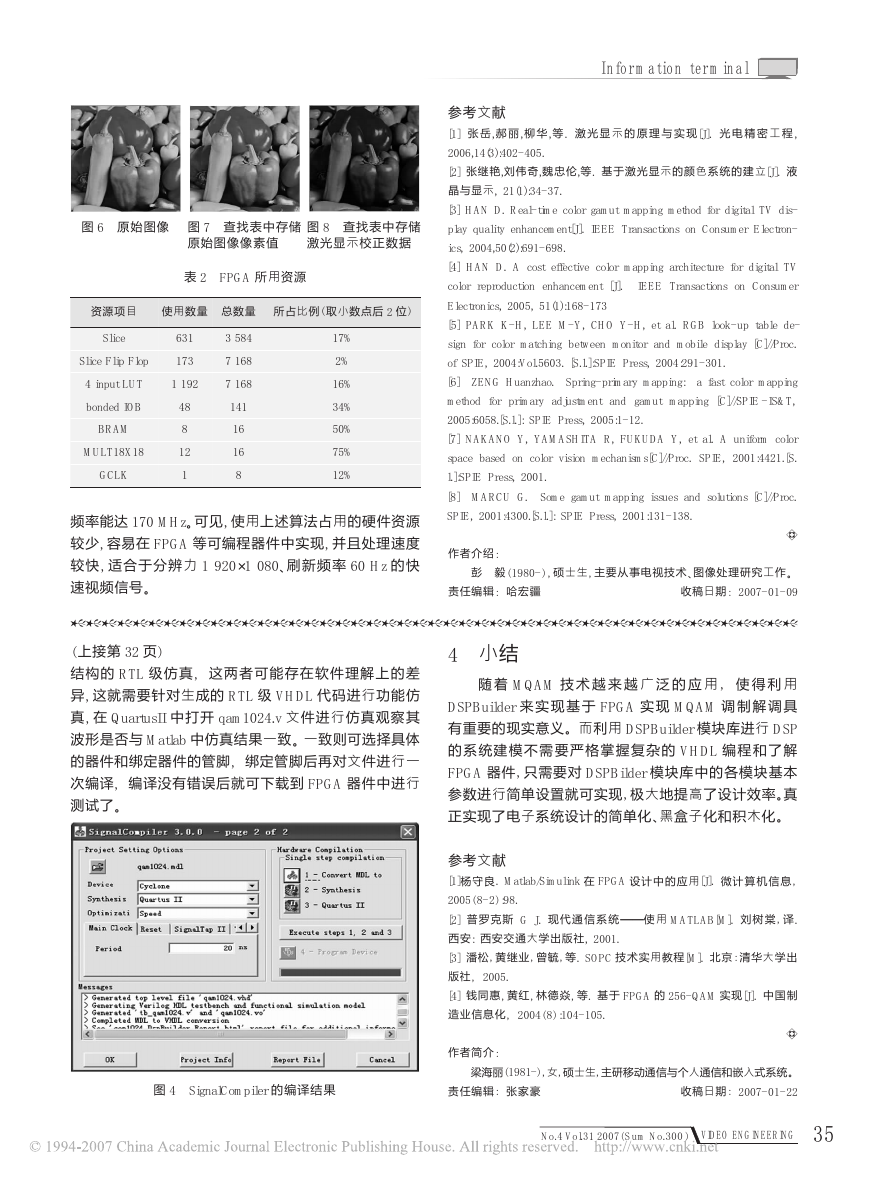

DSPBuilder 提 供 了 QuartusII 和 Matlab/Simulink 之

间的接口, DSPBuilder 设计的关键是通 过 SignalCompiler

把 Simulink 模 型 文 件 转 换 成 硬 件 描 述 语 言 文 件 。 双 击

1024QAM 调制解调系统中的 SignalCompiler 模块即可打

开如图 4 所示的 SignalCompiler 窗口。在图中设置好相应

项后依次点击 Hardware Compilation 中的 3 个 按 钮 逐 项

执 行 VHDL 文 件 转 换 、综 合 、适 配 即 可 完 成 将.mdl 文 件

转换为.vhd 文件。由图 4 中“Message”的结果知道此时在

工 作 目 录 下 生 成 qam1024.v 和 tb_qam1024.tcl 文 件 ,

qam1024.v 文件正是在 QuartusII 中要用的工程文件。而

tb_qam1024.tcl 文件则是要在 Modelsim 中进行 RTL 级仿

真要用到的测试代码。在 Simulink 中的仿真是针对算法

的系统级仿真而生成的, VHDL 代 码 针 对 的 是 具 体 硬 件

( 下转第 35 页)

�

In fo r m a tio n te r m in a l

参考文献

[1] 张 岳,郝 丽,柳 华,等. 激 光 显 示 的 原 理 与 实 现[J]. 光 电 精 密 工 程 ,

2006,14(3):402- 405.

[2] 张继艳,刘伟 奇,魏 忠伦,等. 基于 激光 显示 的颜色 系统 的建 立[J]. 液

晶与显示, 21(1):34- 37.

[3] HAN D. Real- time color gamut mapping method for digital TV dis-

play quality enhancement[J]. IEEE Transactions on Consumer Electron-

ics, 2004,50(2):691- 698.

[4] HAN D. A cost effective color mapping architecture for digital TV

color reproduction enhancement [J].

IEEE Transactions on Consumer

Electronics, 2005, 51(1):168- 173

[5] PARK K- H, LEE M- Y, CHO Y- H, et al. RGB look- up table de-

sign for color matching between monitor and mobile display [C]//Proc.

of SPIE, 2004:Vol.5603. [S.l.]:SPIE Press, 2004:291- 301.

[6] ZENG Huanzhao. Spring- primary mapping:

a fast color mapping

method for primary adjustment and gamut mapping [C]//SPIE - IS&T,

2005:6058.[S.l.]: SPIE Press, 2005:1- 12.

[7] NAKANO Y, YAMASHITA R, FUKUDA Y, et al. A uniform color

space based on color vision mechanisms[C]//Proc. SPIE, 2001:4421.[S.

l.]:SPIE Press, 2001.

[8] MARCU G. Some gamut mapping issues and solutions [C]//Proc.

SPIE, 2001:4300.[S.l.]: SPIE Press, 2001:131- 138.

作者介绍:

彭 毅( 1980- ) , 硕士生, 主要从事电视技术、图像处理研究工作。

收稿日期: 2007- 01- 09

责任编辑: 哈宏疆

!

图 6 原始图像

图 7 查找表中存储

原始图像像素值

图 8 查找表中存储

激光显示校正数据

表 2 FPGA 所用资源

资源项目

使用数量 总数量 所占比例( 取小数点后 2 位)

Slice

Slice Flip Flop

631

173

4 input LUT

1 192

bonded IOB

BRAM

MULT18X18

GCLK

48

8

12

1

3 584

7 168

7 168

141

16

16

8

17%

2%

16%

34%

50%

75%

12%

频率能达 170 MHz。可见, 使用上述算法占用的硬件资源

较少, 容易在 FPGA 等可编程器件中实现, 并且处理速度

较快, 适合于分辨 力 1 920×1 080、刷 新 频 率 60 Hz 的 快

速视频信号。

4 小结

"""""""""""""""""""""""""""""""""""""""""""""""

( 上接第 32 页)

结构的 RTL 级 仿 真, 这 两 者 可 能 存 在 软 件 理 解 上 的 差

异, 这就需要针对生成的 RTL 级 VHDL 代码进行功能仿

真, 在 QuartusII 中打开 qam1024.v 文件进行仿真观察 其

波形是否与 Matlab 中仿真结果一致。一致则可选择具体

的器件和绑定器件的管脚, 绑定管脚后再对文件进行一

次编译, 编译没有错误后就可下载到 FPGA 器件中进行

随 着 MQAM 技 术 越 来 越 广 泛 的 应 用 , 使 得 利 用

DSPBuilder 来 实 现 基 于 FPGA 实 现 MQAM 调 制 解 调 具

有重要的现实意义。而利用 DSPBuilder 模块库进行 DSP

的 系 统 建 模 不 需 要 严 格 掌 握 复 杂 的 VHDL 编 程 和 了 解

FPGA 器件, 只需要对 DSPBilder 模块库中的各模块基本

参数进行简单设置就可实现, 极大地提高了设计效率。真

正实现了电子系统设计的简单化、黑盒子化和积木化。

测试了。

图 4 SignalCompiler 的编译结果

参考文献

[1]杨守良. Matlab/Simulink 在 FPGA 设 计中 的应 用[J]. 微 计 算 机 信 息 ,

2005( 8- 2) :98.

[2] 普 罗 克 斯 G J. 现 代 通 信 系 统 ———使 用 MATLAB[M]. 刘 树 棠 , 译.

西安: 西安交通大学出版社, 2001.

[3] 潘松, 黄继业, 曾毓, 等. SOPC 技术实用教程[M]. 北京: 清华大 学出

版社, 2005.

[4] 钱同惠, 黄红, 林德焱, 等. 基于 FPGA 的 256- QAM 实现[J]. 中国 制

造业信息化, 2004( 8) :104- 105.

作者简介:

梁海丽(1981- ) , 女, 硕士生, 主研移动通信与个人通信和嵌入式系统。

收稿日期: 2007- 01- 22

责任编辑: 张家豪

!

No.4 Vol.31 2007( Sum No.300 )

VIDEO ENGINEERING

35

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc