Title Page

Acknowledgement

TOC

1. Introduction

1.1. Scope and Motivation

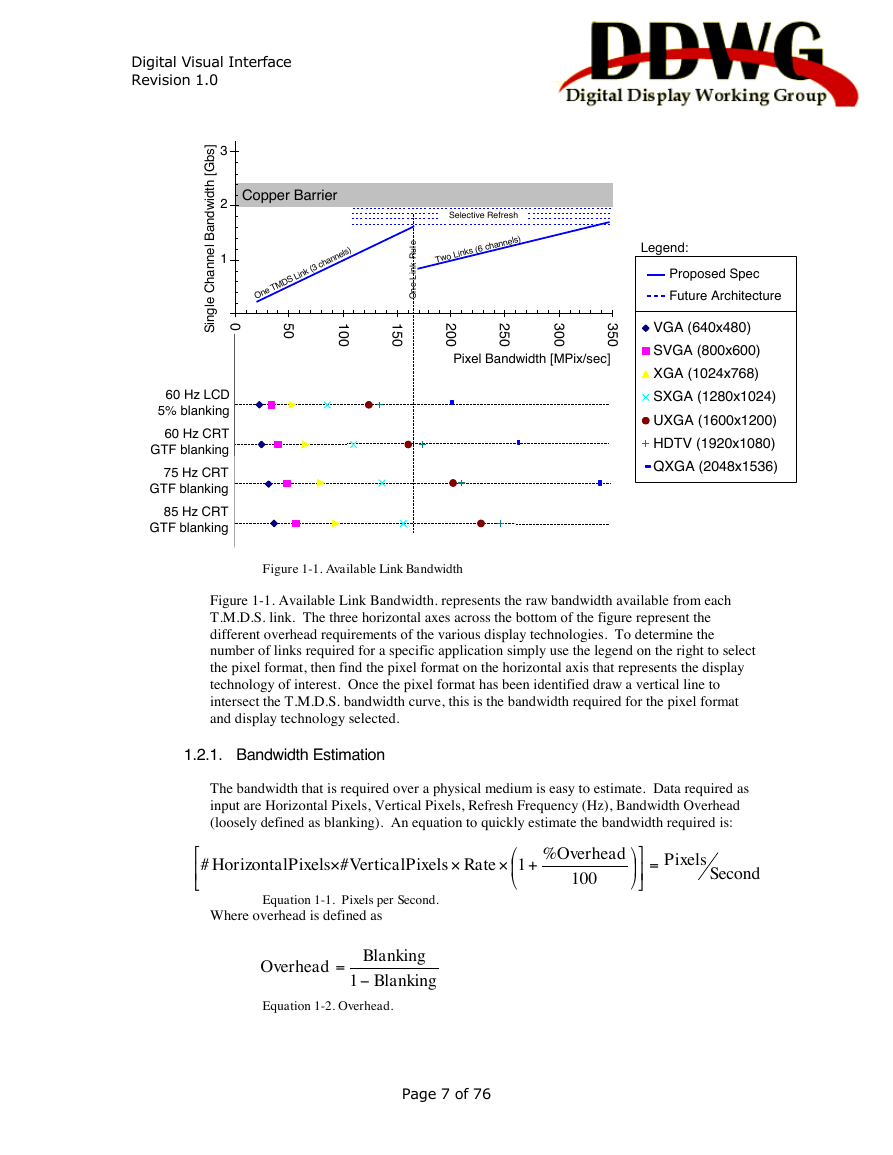

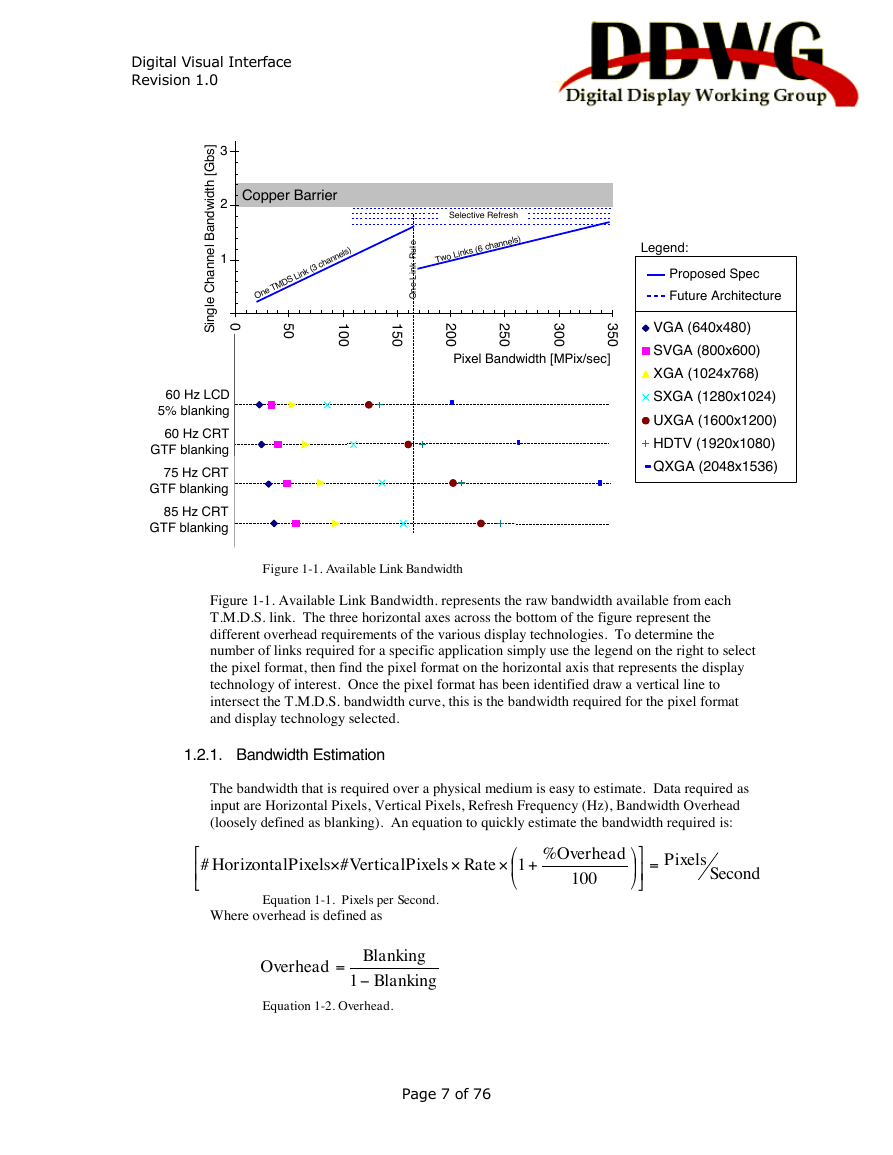

1.2. Performance Scalability

1.2.1. Bandwidth Estimation

1.2.2. Conversion to Selective Refresh

1.3. Related Documents

1.3.1. VESA Display Data Channel (DDC) Specification

1.3.2. VESA Extended Display Identification Data (EDID) Specification

1.3.3. VESA Video Signal Standard (VSIS) Specification

1.3.4. VESA Monitor Timing Specifications (DMT)

1.3.5. VESA Generalized Timing Formula Specification (GTF)

1.3.6. VESA Timing Definition for LCD Monitors Specification

1.3.7. Compatibility with Other T.M.D.S. Based Implementations.

2. Architectural Requirements

2.1. T.M.D.S. Overview

2.2. Plug and Play Specification

2.2.1. Overview

2.2.2. T.M.D.S. Link Usage Model

2.2.3. High Color Depth Support

2.2.4. Low Pixel Format Support

2.2.5. EDID

2.2.6. DDC

2.2.7. Gamma

2.2.8. Scaling

2.2.9. Hot Plugging

2.2.10. HSync, VSync and Data Enable Required

2.2.11. Data Formats

2.2.12. Interoperability with Other T.M.D.S. Based Specifications

2.3. Bandwidth

2.3.1. Minimum Frequency Supported

2.3.2. Alternate Media

2.4. Digital Monitor Power Management

2.4.1. Link Inactivity Definition

2.4.2. System Power Management Requirements

2.4.3. Monitor Power Management Requirements

2.5. Analog

2.5.1. Analog Signal Quality

2.5.2. HSync and VSync Required

2.5.3. Analog Timings

2.5.4. Analog Power Management

2.6. Signal List

3. T.M.D.S. Protocol Specification

3.1 Overview

3.1.1 Link Architecture

3.1.2 Clocking

3.1.3 Synchronization

3.1.4 Encoding

3.1.5 Dual-Link Architecture

3.2 Encoder Specification

3.2.1 Channel Mapping

3.2.2 Encode Algorithm

3.2.3 Serialization

3.3 Decoder Specification

3.3.1 Clock Recovery

3.3.2 Data Synchronization

3.3.3 Decode Algorithm

3.3.4 Channel Mapping

3.3.5 Error Handling

3.4 Link Timing Requirements

4. T.M.D.S. Electrical Specification

4.1. Overview

4.2. System Ratings and Operating Conditions

4.3. Transmitter Electrical Specifications

4.4. Receiver Electrical Specifications

4.5. Cable Assembly Specifications

4.6. Jitter Specifications

4.7. Electrical Measurement Procedures

4.7.1. Test Patterns

4.7.2. Normalized Amplitudes

4.7.3. Clock Recovery

4.7.4. Transmitter Rise/Fall Time

4.7.5. Transmitter Skew Measurement

4.7.6. Transmitter Eye

4.7.7. Jitter Measurement

4.7.8. Receiver Eye

4.7.9. Receiver Skew Measurement

4.7.10. Differential TDR Measurement Procedure

5. Physical Interconnect Specification

5.1. Overview

5.2. Mechanical Characteristics

5.2.1. Signal Pin Assignments

5.2.2. Contact Sequence

5.2.3. Digital-Only Receptacle Connectors

5.2.4. Combined Analog and Digital Receptacle Connectors

5.2.5. Digital Plug Connectors

5.2.6. Analog Plug Connectors

5.2.7. Recommended Panel Cutout

5.2.8. Mechanical Performance

5.3. Electrical Characteristics

5.3.1. Connector Electrical Performance

5.3.2. Cable Electrical Performance

5.4. Environmental Characteristics

5.5. Test Sequences

5.5.1. Group 1: Mated Environmental

5.5.2. Group II: Mated Mechanical

5.5.3. Group III: Mechanical Mate/Unmate Forces

5.5.4. Group IV: Insulator Integrity

5.5.5. Group V: Cable Flexing

5.5.6. Group VI: Electrostatic Discharge

Appendix A. Glossary of Terms

Appendix B. Contact Geometry

Appendix C. Digital Monitor Power States

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc