(A 卷)

班级

学号

姓名

密 封

线 内

不 得

答

题

赣 南 师 范 学 院

2010—2011 学年第一学期期末考试试卷(A 卷)(闭卷)

年级 2008 专业 电子科学与技术 (本)课程名称 EDA 技术基础

一

二

三

四

五

总分

题号

得分

阅卷人

注意事项:1、教师出题时请勿超出边界虚线;

2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线;

3、答题请用蓝、黑钢笔或圆珠笔。

一、单项选择题(30 分,每题 2 分)

1.以下关于适配描述错误的是 B

A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使

之产生最终的下载文件

B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列

C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真

D.通常,EDAL 软件中的综合器可由专业的第三方 EDA 公司提供,而适

配器则需由 FPGA/CPLD 供应商提供

2.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体

与结构体两部分,结构体描述 D

。

B.器件的综合约束

D.器件的内部功能

D.signall

D

A.器件外部特性

C.器件外部特性与内部功能

3.下列标识符中, B

A.State0

B.9moon

是不合法的标识符。

C.Not_Ack_0

4.以下工具中属于 FPGA/CPLD 集成化开发工具的是

A.ModelSim

C.MATLAB

B.Synplify Pro

D.QuartusII

5.进程中的变量赋值语句,其变量更新是 A

A.立即完成

C.在进程的最后完成

B.按顺序完成

D.都不对

6.以下关于 CASE 语句描述中错误的是 A

。

A.CASE 语句执行中可以不必选中所列条件名的一条

B.除非所有条件句的选择值能完整覆盖 CASE 语句中表达式的取值,否则

最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语

句>”

C.CASE 语句中的选择值只能出现一次

第 1页(共 3页)

D. WHEN 条件句中的选择值或标识符所代表的值必须在表达式的取值范

围

7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B

A.STD_LOGIC_ARITH

B.STD_LOGIC_1164

C.STD_LOGIC_UNSIGNED

D.STD_LOGIC_SIGNED

8.基于 EDA 软件的 FPGA / CPLD 设计流程为:原理图/HDL 文本输入→ A →

综合→适配→时序仿真→编程下载→硬件测试。

A.功能仿真 B.逻辑综合

C.配置

9.不完整的 IF 语句,其综合结果可实现 D

D.引脚锁定

A.三态控制电路

C.双向控制电路

B.条件相或的逻辑电路

D.时序逻辑电路

10.下列语句中,属于并行语句的是 A

A.进程语句

B.IF 语句

C.CASE 语句

D.FOR 语句

11.综合是 EDA 设计流程的关键步骤,综合就是把抽象设计层次中的一种表

示转化成另一种表示的过程;在下面对综合的描述中, C 是错误的。

A.综合就是将电路的高级语言转化成低级的,可与 FPGA / CPLD 的基本

结构相映射的网表文件

B.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映

射过程,并且这种映射关系不是唯一的

C.综合是纯软件的转换过程,与器件硬件结构无关

D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综

合约束

12.CPLD 的可编程是主要基于什么结构 D 。

13.以下器件中属于 Altera 公司生产的是 B

A.查找表(LUT)

C.PAL 可编程

A.ispLSI 系列器件

C.XC9500 系列器件

B.ROM 可编程

D.与或阵列可编程

B.MAX 系列器件

D.Virtex 系列器件

14. 在 VHDL 语言中,下列对时钟边沿检测描述中,错误的是 D

A.if clk'event and clk = '1' then

C.if rising_edge(clk) then

B.if clk'stable and not clk = '1' then

D.if not clk'stable and clk = '1' then

15.以下关于状态机的描述中正确的是 B

A.Moore 型状态机其输出是当前状态和所有输入的函数

B.与 Moore 型状态机相比,Mealy 型的输出变化要领先一个时钟周期

C.Mealy 型状态机其输出是当前状态的函数

D.以上都不对

�

(A 卷)

二、EDA 名词解释,写出下列缩写的中文含义(10 分,每题 2 分)

END bhv;

班级

学号

姓名

密 封

线 内

不 得

答

题

1.FPGA:现场可编程门阵列

2.HDL: 硬件描述语言

3.LE: 逻辑单元

4.FSM: 有限状态机

5.SOPC: 可编程片上系统

三、程序填空题(20 分,每空 2 分)

以下是一个模为 60(0~59)的 8421BCD 码加法计数器 VHDL 描述,请补充完

整

LIBRARY IEEE;

Use IEEE.std_logic_1164.all

;

ENTITY ta IS

PORT ( CLK : IN STD_LOGIC ;

SHI

: OUT INTEGER RANGE 0 TO 9;

GE: OUT INTEGER RANGE 0 TO 9) ;

END ;

ARCHITECTURE bhv OF ta

SIGNAL SHI1,GE1 : INTEGER RANGE 0 TO 9

IS

;

BEGIN

PROCESS ( CLK

BEGIN

)

IF

CLK’EVENT AND CLK=’1’

then

IF GE1 = 9 THEN

GE1 <= 0 ;

SHI1=5

IF

SHI1<=0;

THEN

ELSE SHI1<=SHI+1

END IF;

ELSE

GE1<=GE1+1

END IF;

END IF

END PROCESS ;

GE <= GE1;

SHI<=SHI1

;

;

;

;

四、程序改错题(仔细阅读下列程序后回答问题,12 分)

PORT ( CLK : IN STD_LOGIC ;

Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)) ;

SIGNAL Q1 : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS (CLK)

LIBRARY IEEE;

ENTITY ga IS

END gb;

ARCHITECTURE bhv OF ga IS

1

2 USE IEEE.STD_LOGIC_1164.ALL;

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 END bhv;

END PROCESS ;

Q <= Q1;

IF Q1 < “1001” THEN

Q1 <= Q1 + 1 ;

END IF;

END IF;

BEGIN

IF RISING_EDGE(CLK) begin

ELSE

Q1 <= (OTHERS => '0');

程序编译时,提示的错误为:

Error: Line 12: File e:\mywork\test\ga.vhd: VHDL syntax error: If statement must have

THEN, but found BEGIN instead

Error: Line 14: File e:\mywork\test\ga.vhd:Subprogram error:can’t interpret subprogram

call

请回答问题:在程序中存在两处错误,试指出并修改正确(如果是缺少语句请

指出应该插入的行号)

答:

(1)12 行 begin 改为 then

(2)第 2 行和第 3 行见加 USE IEEE.STD_LOGIC_UNSIGNED.ALL;

五、程序设计题(28 分)

第 2页(共 3页)

�

班级

学号

姓名

密 封

线 内

不 得

答

题

(A 卷)

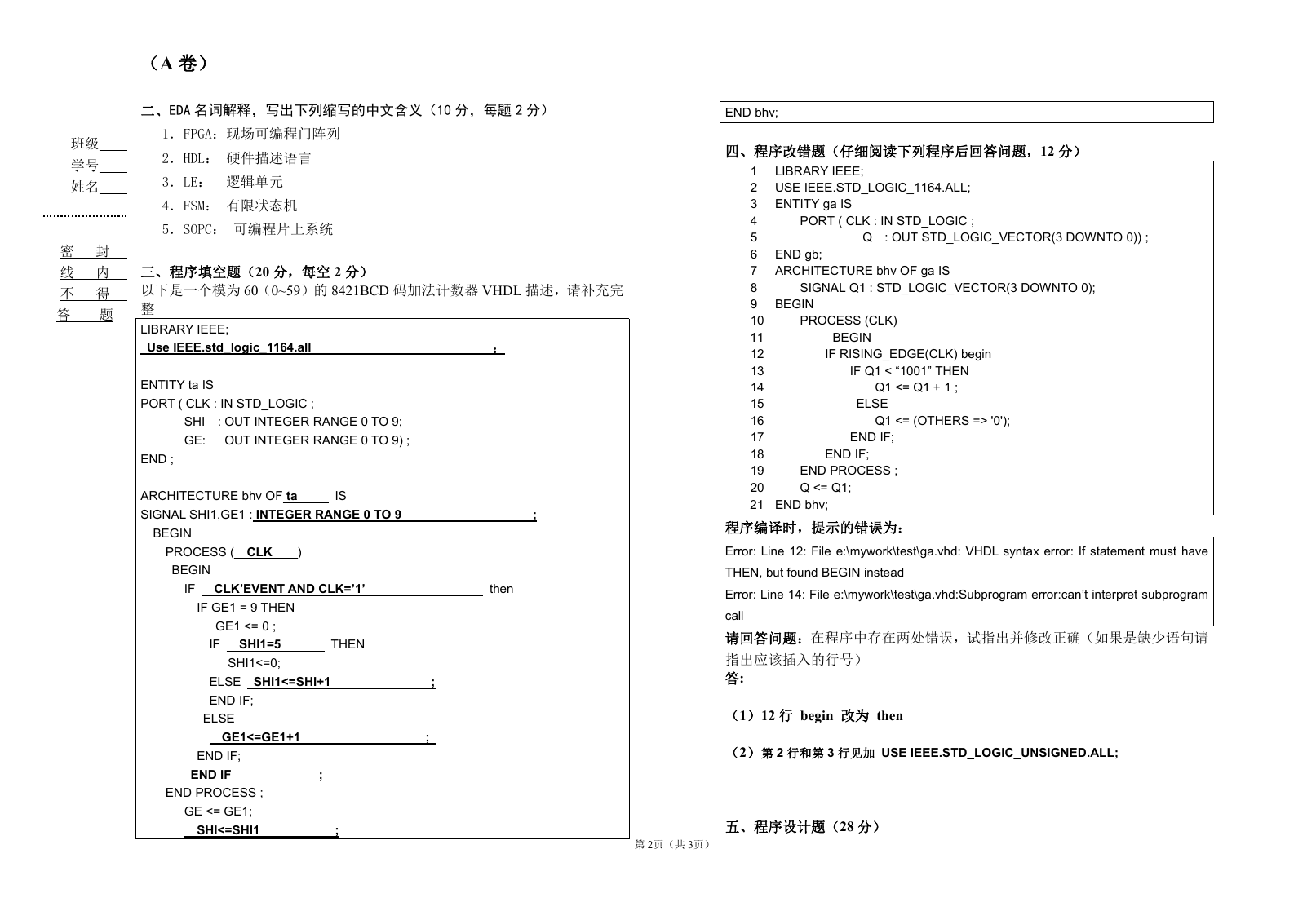

1.试用 VHDL 描述一个外部特性如图所示的数据选择器,S 为控制端口。(10

分)

Library IEEE;

Use IEEE.std_logic_1164.all;

Entity sjxz IS

Port(A,B,S:in std_logic;

Q:out std_logic);

END entity sjxz;

Architecture bhv of sjxz IS

Process(S)

Begin

IF S=’0’ Then Q<=A;

ELSE Q<=B;

END IF;

END PROCESS’

END bhv;

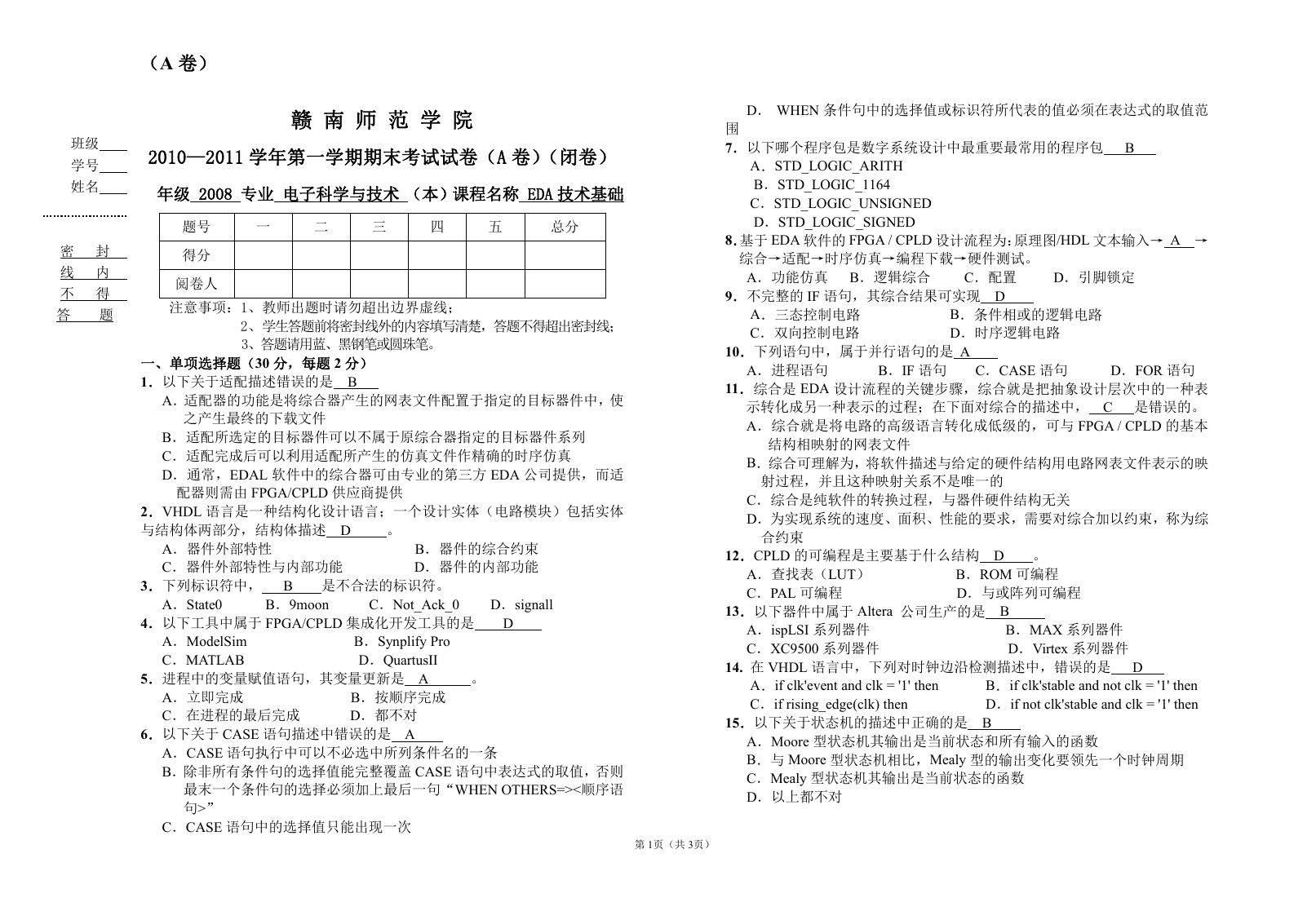

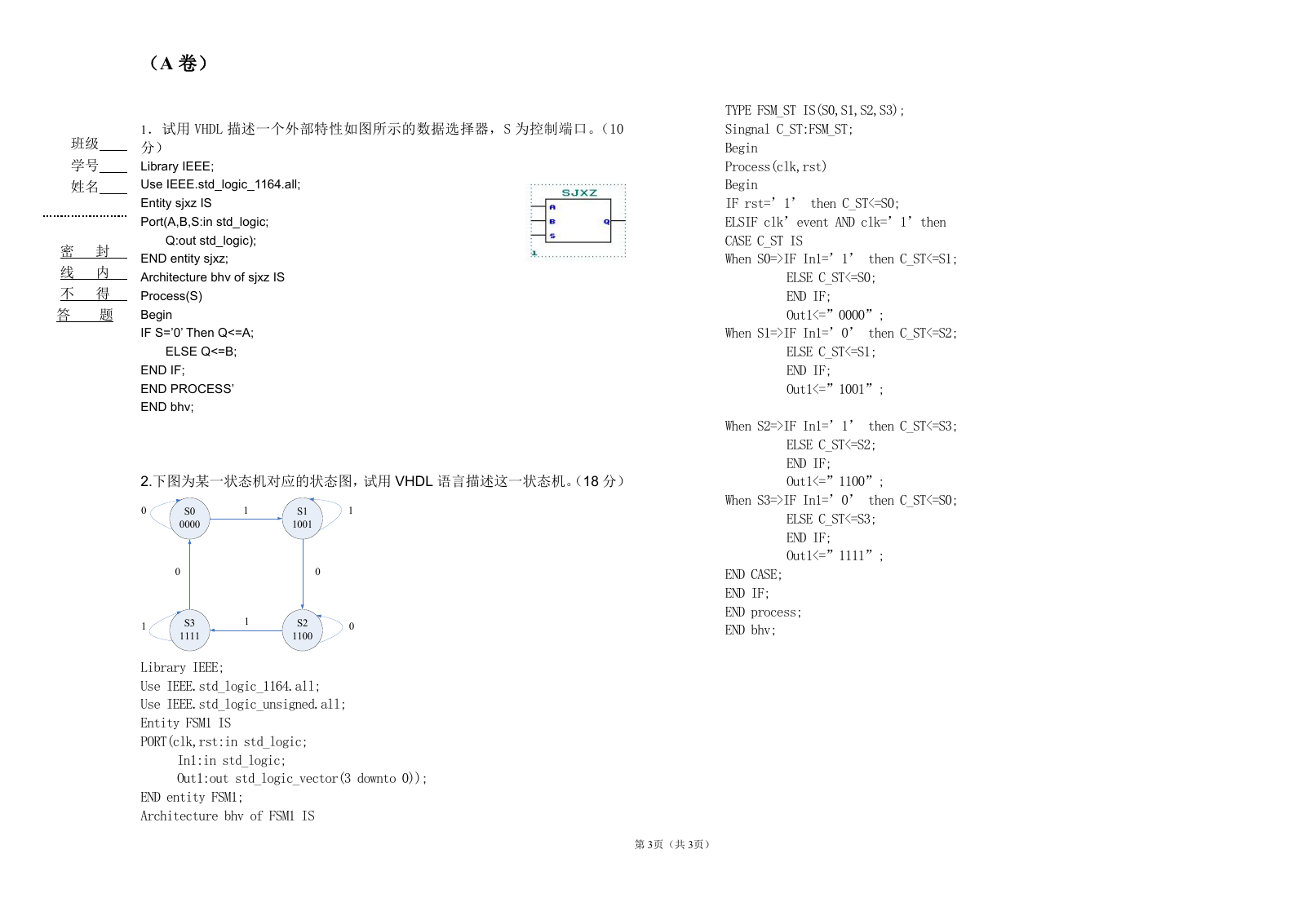

2.下图为某一状态机对应的状态图,试用 VHDL 语言描述这一状态机。(18 分)

0

1

S0

0000

0

S3

1111

1

1

S1

1001

0

S2

1100

1

0

Library IEEE;

Use IEEE.std_logic_1164.all;

Use IEEE.std_logic_unsigned.all;

Entity FSM1 IS

PORT(clk,rst:in std_logic;

In1:in std_logic;

Out1:out std_logic_vector(3 downto 0));

END entity FSM1;

Architecture bhv of FSM1 IS

第 3页(共 3页)

TYPE FSM_ST IS(S0,S1,S2,S3);

Singnal C_ST:FSM_ST;

Begin

Process(clk,rst)

Begin

IF rst=’1’ then C_ST<=S0;

ELSIF clk’event AND clk=’1’then

CASE C_ST IS

When S0=>IF In1=’1’ then C_ST<=S1;

ELSE C_ST<=S0;

END IF;

Out1<=”0000”;

When S1=>IF In1=’0’ then C_ST<=S2;

ELSE C_ST<=S1;

END IF;

Out1<=”1001”;

When S2=>IF In1=’1’ then C_ST<=S3;

ELSE C_ST<=S2;

END IF;

Out1<=”1100”;

When S3=>IF In1=’0’ then C_ST<=S0;

ELSE C_ST<=S3;

END IF;

Out1<=”1111”;

END CASE;

END IF;

END process;

END bhv;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc