郑州轻工业学院

实 验 报 告

课程名称

计算机组成原理

实验名称

通用寄存器和存储器部件

班

姓

学

级

名

号

指导教师

成

绩

计科 06-1

王玉红

200607010141

胡东华

�

一.实验目的

⒈熟悉通用寄存器的概念。

⒉熟悉通用寄存器的组成和硬件电路

3.熟悉存储器和总线组成的硬件电路

二.实验原理

这个试验所用的通用寄存器数据电路由三片 8 位字长的 74LS374 组成 R0、R1、

R2 寄存器组成,通用寄存器输入经过三态门和数据总线相连,3 个寄存器由 一

8 芯扁平线与数据总线相连。R0-B、R1-B、R2-B 经 CBA 的二进制开关译码器产生

数据输出选通信号,LDR0、LDR1、LDR2 为数据写入允许信号。由二进制开关模

拟,T4 位寄存器数据写入脉冲,按动一次【单步】键将产生一次 T4 信号。

第二个实验中所用的是半导体静态存储器电路。该静态存储器有一片 6116(2K*8)

构成,其数据线(D7-D0)以 8 芯扁平线方式和数据总线相连,地址由四肢锁存

器(74LS273)给出。数据开关经一三态门(74LS245)以 8 芯扁平线方式与数据总线

相连分别给出地址和数据。6116 有 3 根控制线:CS(片选线),OE(读线),W(写线)。

本实验中将 OE 引脚接地,在此情况下,当 CS=0,WR=1 时进行读操作,CS=0,WR=0 时

进行写操作,其写时间与 T3 脉冲宽度一致。实验时 T3 脉冲由【单步】命令键产生,其它

电平控制信号由二进制开关模拟,其中 CE,SW-B,LDAR 为高电平有效,而 WE 为/读写(W/R)

控制 H 信号,当 WE=0 时进行读操作,当 WE=1 时进行写操作。

三.实验模块

1.B1 单元:缓冲输入单元,8 位数据开关经过三态门与数据总线相连用来给出

参与运算的数据,SW-B 为三态门的控制端,当 SW-B=1 时三态门

导通,数据开关的数据进数据总线。

2.B2 单元:地址总线单元,当 CBA=000,CE=0,SW-B=1 时,若 LDAR=1 可将 B1 单

元的地址信息锁存到地址寄存器 AR 器件中。

3.B3 单元:内存单元 L,当 CBA=000,LDAR=0,SW-B=1 时 CE=1WE=1,若可将 B1 单

元的数据信息锁存到存储器 6116。

4.B5 单元:寄存器组单元,由三片 8 位字长的 74LS374 组成 R0、R1、R2 通用寄

存器,由 LDR0、LDR1、LDR2 控制数据的写入。

5.B10 单元:时序启停单元,主要是为试验提供由时序电路产生的节拍脉冲信

号,由短线把时钟信号和控制线相连。

四.实验内容及结果

1.实验三通用寄存器实验

a.通用寄存器的写入

关闭 ALU 输出三态门(CBA=000),CE=0,开启输入三态门(SW-B=1),设置

数据开关,向 R0 存入 00001101(0DH),向 R1 存入 00011010(1AH)。向 R2 存

入 00011011(1BH)

b.通用寄存器的读出

关闭输入三态门(SW-B=1),CE=0,设置 LDR0=0、LDR1=0、LDR2=0,分别打

开 R0、R1、R2 输出控制位,分别置 CBA=100、101、110,按“单步”读出数

�

据。

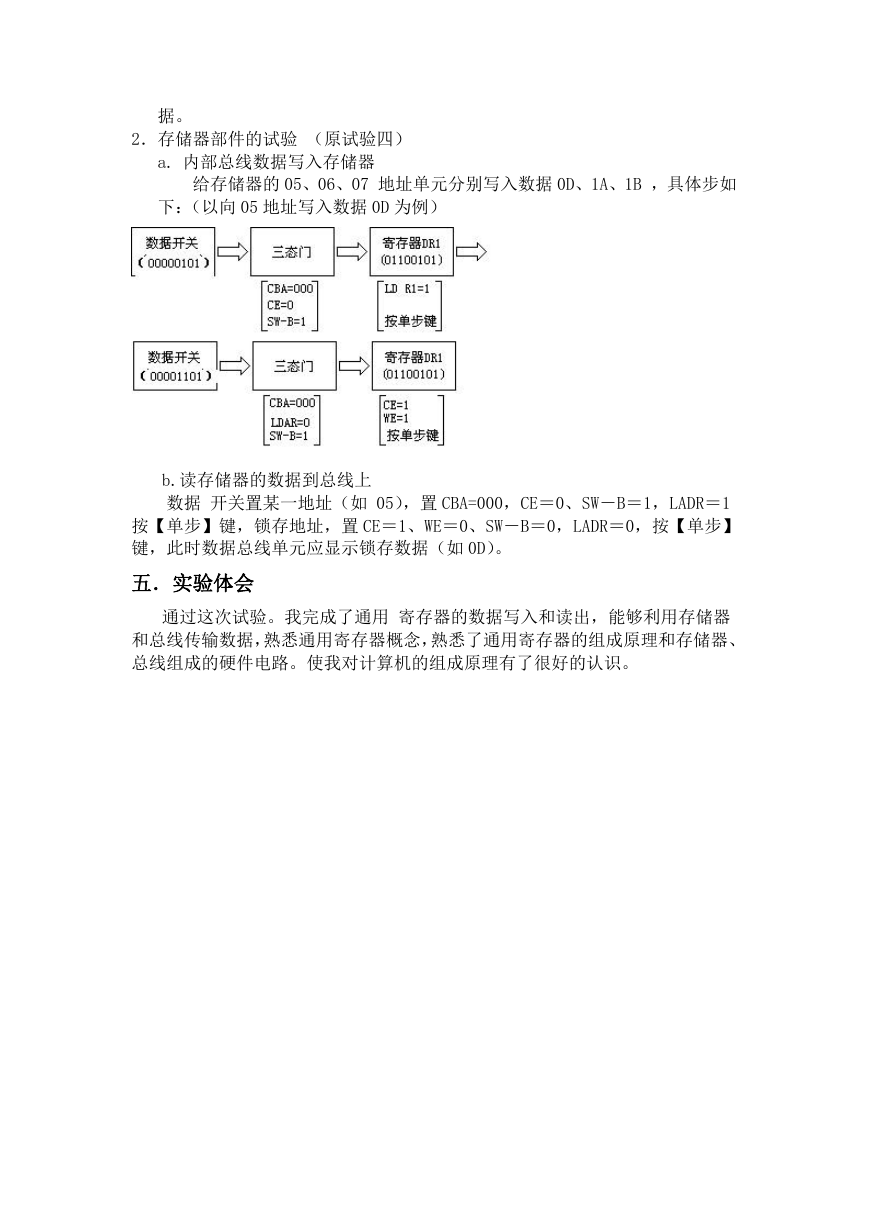

2.存储器部件的试验 (原试验四)

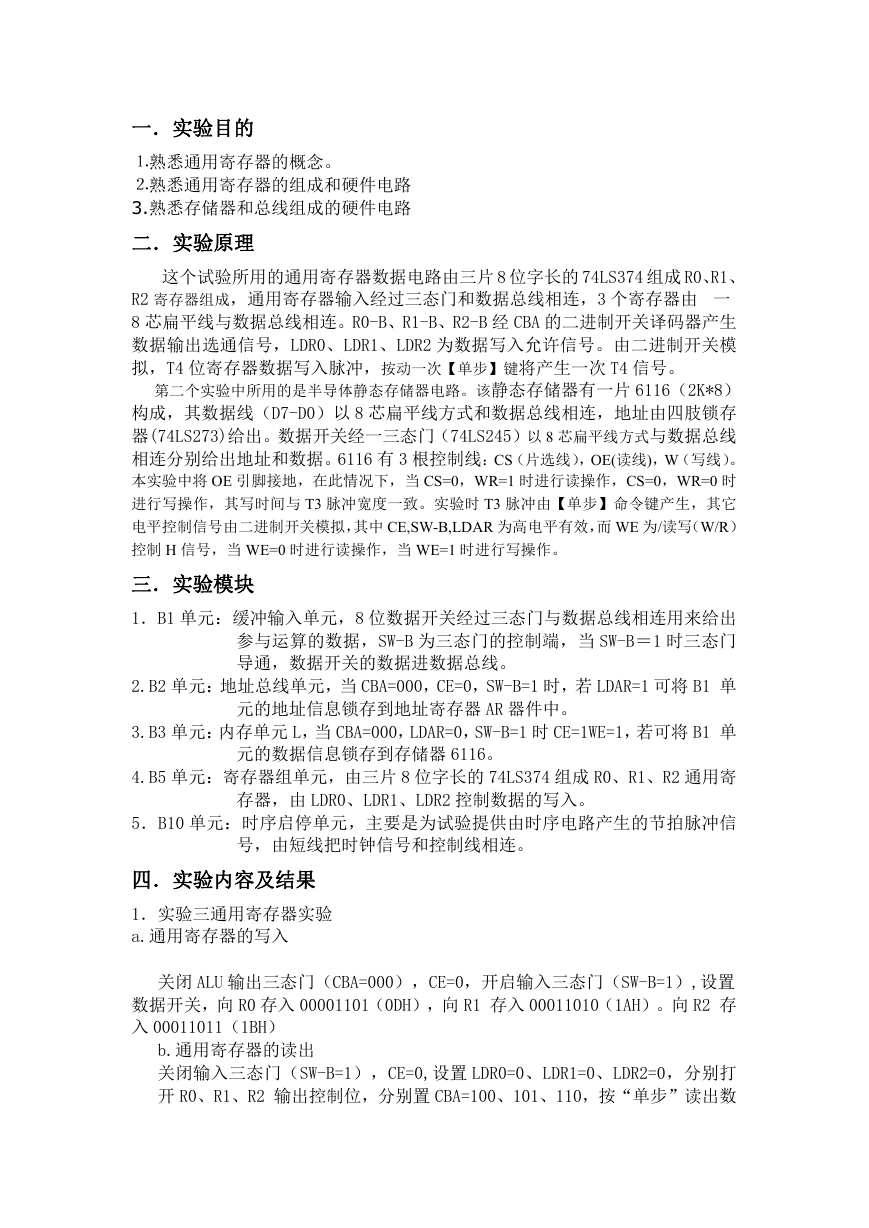

a. 内部总线数据写入存储器

给存储器的 05、06、07 地址单元分别写入数据 0D、1A、1B ,具体步如

下:(以向 05 地址写入数据 0D 为例)

b.读存储器的数据到总线上

数据 开关置某一地址(如 05),置 CBA=000,CE=0、SW-B=1,LADR=1

按【单步】键,锁存地址,置 CE=1、WE=0、SW-B=0,LADR=0,按【单步】

键,此时数据总线单元应显示锁存数据(如 0D)。

五.实验体会

通过这次试验。我完成了通用 寄存器的数据写入和读出,能够利用存储器

和总线传输数据,熟悉通用寄存器概念,熟悉了通用寄存器的组成原理和存储器、

总线组成的硬件电路。使我对计算机的组成原理有了很好的认识。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc