Verilog HDL 那些事兒 - 建模篇

一

�

Verilog HDL 那些事兒 - 建模篇

书语书语书语书语

学习 Verilog HDL 和 FPGA 之间,始终会出现一组群体,他们都是徘徊在学习的边缘。

在他们的心中一直回响着这样的一个问题:“我在学什么,为什么不管我怎么学,我都

没有实感 ... ” 没错这就是初学 Verilog HDL + FPGA 的心声。

在众多的 Verilog HDL 参考书,隐隐约约会会出现这样的一个“建模”。建模在 Verilog

HDL 的世界里是一个重要的基础,笔者始终无法明白,为什么参考书们怎么都不甘情愿

的好好描述它们。“建模”顾名思义就是“模块建立”的省略。FPGA 的逻辑资源,好比

乐高的积木,要组合乐高就是需要工具,那 Verilog HDL 就是 FPGA 建模的工具。

Verilog HDL 作为“建模”的一个工具,但是没有技巧的使用它们是无法很好的发挥到

它。读者们,曾经何时有没有为建模的规划而头疼过?读者们,曾经何时有没有为天书

般的源码,想把头去撞墙?到最后的最后,读者们,曾经何时有没有冲动想用一把火把

全部东西都烧掉。这些心情笔者也拥有过,而且笔者也干过,这一切的一切都只是一个

原因 :

“没有建模的技巧 ... ”

网络上常说学习 Verilog HDL 就是要明白什么是 RTL 级代码,多参考别人写的代码,

但是前提是“你能不能看懂别人在写什么,别人在设计什么,别人在做什么”。有一句

学习 Verilog HDL 的名言 “参考别人的代码有如半死不活的受折磨”,当你看懂别人在

写什么的时候,估计在那之际你已经形成一具行尸走肉,这一切的一切都是:

“没有建模技巧 ... ”

在这里笔者没有攻击他人的意思,笔者始终觉得一个好的设计不仅是自己看得懂,而且

还要别人看得懂,设计的表达能力要直接,代码要整齐,建模有结构。

笔者一直觉得可恨,为什么建模技巧作为 Verilog HDL 的基本功,它甚至比时序分析,

功能仿真来得更重要,但是却没有被重视。建模技巧的潜能是难以估计,笔者一直深信

拥有建模技巧的建模,Verilog HDL 语言绝对不会亚于其他高级语言,甚至还可以超越

它们。关于这一点,这一本笔记已经可以证明。

很多初学 Verilog HDL + FPGA 的朋友会成为徘徊在边缘的一群,主要原因就是他们没

有掌握好建模技巧,而形成他们继续前进的一大阻碍。

在这里笔者将自己养成的建模技巧,故笔者称为“低级建模”这一建模技巧。笔者经过

一段时间使用后,编辑成为一本笔记。好让许更多初学的朋友越过这一段学习的大障碍。

二

�

Verilog HDL 那些事兒 - 建模篇

前言前言前言前言

说实话,在这本笔记还没有开始之前,笔者正是初到社会之际。那时候的笔者正好

是徘徊在学习 Verilog HDL + FPGA 的边缘,每天早上七时工作到晚上七时,失去大量

的学习热情的同时,再加上无法突破学习的障碍。笔者真的很想很想什么东西都不干,

甚至放下笔者所喜爱的学习。

在学习 Verilog HDL + FPGA 的时候,笔者有尝试过把头撞墙,表演“狮子”。最后笔者

一股劲将所有之前所学的资料,都一把火(Shift + Delete)通通烧掉。好似将所有有

关 Verilog HDL + FPGA 的学习回归到零,那种心情笔者到现在还记忆犹新。

在工厂工作一段时间后,不知为何学习的冲动一只从心里深处涌出! 笔者向自己说“好

想再一次接触 Verilog HDL + FPGA 呀,就这样放弃我真的很不甘心 ”。到底是偶然还

是冥冥之中,笔者在 ourdev 上看见了 FPGA 黑金开发板 ...... ( 笔者真的很感谢黑金

动力社区的 AVIC 大大,很感谢他提供了一个给笔者编写这一本笔记的平台)

笔者告诉自己,不会再犯同样的错误,要找出“障碍的原因”。于是笔者开始测试许多

不同的实验,最后笔者发现到一个关键的东西,那就是“建模”。笔者为了证实自己的

想法是对的,就开始针对“建模”写了一本关于 Verilog HDL 建模技巧的思路篇笔记。

之后,想法越来越多,“建模技巧”也越来越成熟。

大约是 2010 年七月末 FPGA 黑金开发板开始发售了,笔者很意外的接到 AVIC 大大为 FPGA

黑金开发板写教程的要求。那时候的心情笔者真的很惊奇,因为笔者重来没有干过这样

的事情。笔者写学习笔记的目的是为了更好的反馈自己,想不到会成为另一种形式的开

端 ...

初头笔者一直犹豫着和担心着什么,但是笔者明白到如果某件事情发生在自己的身上就

一定有它的原因,此外笔者一直还有为建模技巧写一本实例篇的打算。就这样长达 12

个月学习笔记开始编写了 ...

“低级建模”作为笔者的“建模技巧”(建模习惯),笔者真的很用心去记录每一个内容。

虽然文中可能会出现许多“奇怪的字眼和用词”,关于这一点笔者希望读者们不要太认

真,笔者的语言能力有限,用字不好。如果文中有得罪的地方,真的很抱歉,笔者一向

都是直言直语 ,单刀直入那种人。

akuei2 24-10-2010 上

三

�

Verilog HDL 那些事兒 - 建模篇

笔者的博客:

http://blog.ednchina.com/akuei2

黑金动力社区:

http://www.heijing.com

这本笔记的适合群:

一、初学者。

二、希望从另一个角度去了解 Verilog HDL 的人们。

这一本笔记确实有点不适合入门者,怎么说呢?因为这本笔记笔者按着自己的习惯编

辑,则笔者不是按着典型的方向去编辑。入门者应该先从一些权威的参考书去了解“什

么是 Verlilog HDL 语言”,对 Verilog HDL 语言有一定的了解后,再来看这本笔记。

此外,稍微要知道 Quartus II 是什么(版本随便)。

四

�

Verilog HDL 那些事兒 - 建模篇

目录:目录:目录:目录:

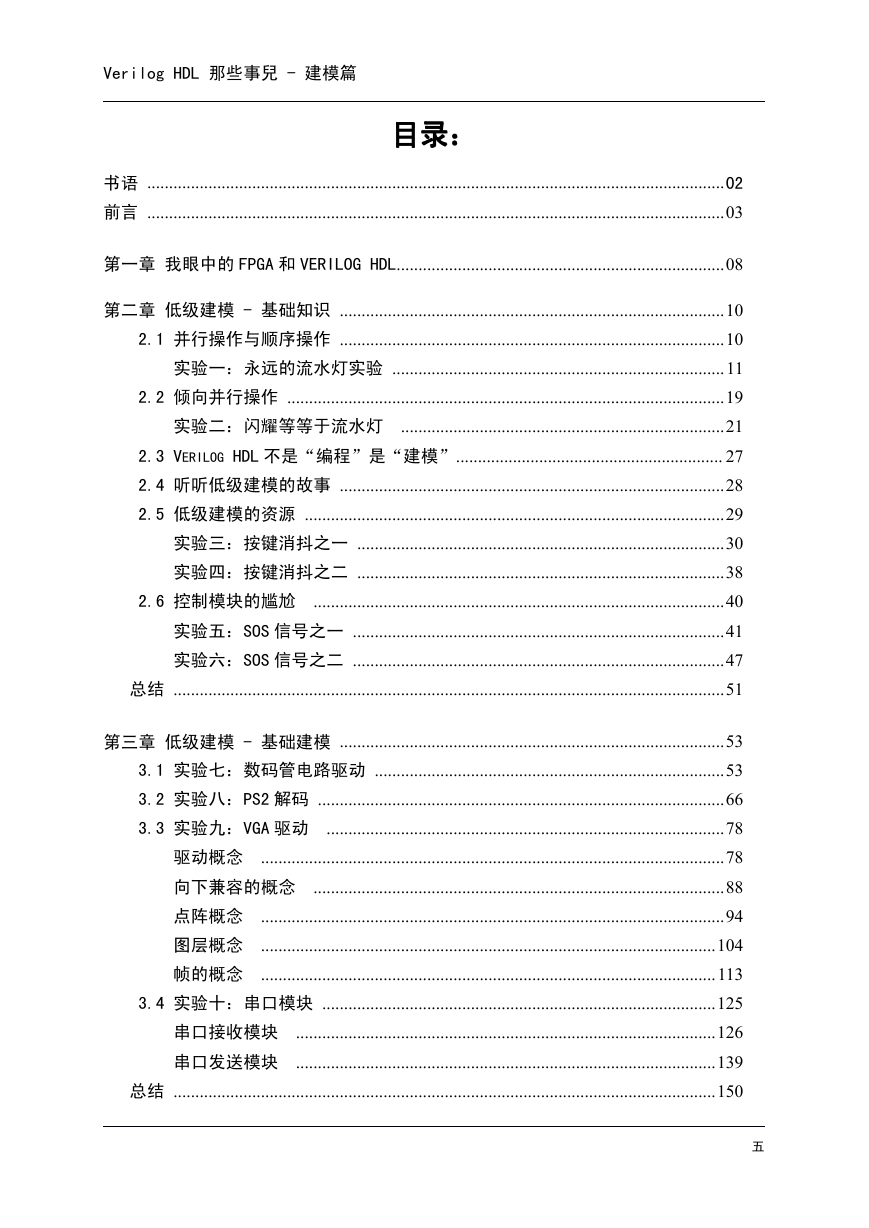

书语 ....................................................................................................................................02

前言 ....................................................................................................................................03

第一章 我眼中的 FPGA 和 VERILOG HDL...........................................................................08

第二章 低级建模 - 基础知识 ........................................................................................10

2.1 并行操作与顺序操作 ........................................................................................10

实验一:永远的流水灯实验 ............................................................................11

2.2 倾向并行操作 ....................................................................................................19

实验二:闪耀等等于流水灯 ..........................................................................21

2.3 VERILOG HDL 不是“编程”是“建模”............................................................. 27

2.4 听听低级建模的故事 ........................................................................................28

2.5 低级建模的资源 ................................................................................................29

实验三:按键消抖之一 ....................................................................................30

实验四:按键消抖之二 ....................................................................................38

2.6 控制模块的尴尬 ..............................................................................................40

实验五:SOS 信号之一 .....................................................................................41

实验六:SOS 信号之二 .....................................................................................47

总结 ..............................................................................................................................51

第三章 低级建模 - 基础建模 ........................................................................................53

3.1 实验七:数码管电路驱动 ................................................................................53

3.2 实验八:PS2 解码 .............................................................................................66

3.3 实验九:VGA 驱动 ...........................................................................................78

驱动概念 ..........................................................................................................78

向下兼容的概念 ..............................................................................................88

点阵概念 ..........................................................................................................94

图层概念 ........................................................................................................104

帧的概念 ........................................................................................................113

3.4 实验十:串口模块 ..........................................................................................125

串口接收模块 ................................................................................................126

串口发送模块 ................................................................................................139

总结 ............................................................................................................................150

五

�

Verilog HDL 那些事兒 - 建模篇

第四章 低级建模 - 仿顺序操作 ..................................................................................152

4.1 基本思路 ..........................................................................................................152

实验十一:SOS 信号之三 ...............................................................................153

4.2 实验十二:12864(ST7565P)液晶驱动 ......................................................167

4.3 命令式仿顺序操作 ..........................................................................................196

实验十三:DS1302 实时时钟驱动 .................................................................203

总结 ..................................................................................................................................224

第五章 低级建模 - 封装(接口建模)........................................................................226

5.1 实验十四:独立按键封装 ..............................................................................230

5.2 实验十五:数码管封装 ..................................................................................228

5.3 实验十六:蜂鸣器封装 ..................................................................................252

5.4 实验十七:PS2 封装 .......................................................................................267

5.5 实验十八:串口发送|接收封装 ....................................................................277

5.6 实验十九:VGA 封装 .......................................................................................290

5.7 实验二十:LCD(12864)封装 ......................................................................305

5.8 实验二十一:RTC 接口 ...................................................................................321

总结 ..................................................................................................................................339

第六章 低级建模 - 系统建模 ......................................................................................343

6.1 实验二十二:SOS 系统 ...................................................................................343

6.2 实验二十三:RTC 系统 ...................................................................................346

6.3 实验二十四:GUI 系统 ...................................................................................349

总结 ..................................................................................................................................373

结束语 ..............................................................................................................................374

六

�

Verilog HDL 那些事兒 - 建模篇

第一章

我眼中的 FPGA 和 Verilog HDL

他人都喜欢跑,跑累了容易迷茫,

我却喜欢步行,走累的我只要休息就能重新出发。

七

�

Verilog HDL 那些事兒 - 建模篇

第一第一第一第一章:章:章:章:我眼中的

Verilog

我眼中的我眼中的我眼中的 FPGAFPGAFPGAFPGA 和和和和 Verilog

Verilog HDLHDLHDLHDL

Verilog

当接触一门新知识的时候,如果在心中没有任何形状(概念),掌握的感觉都是遥不可及

的。当然,FPGA 也好 Verilog HDL 也好,也是一回事儿。今天笔者就将这个秘密 告

诉读者!在新手之间有一个很普遍的问题 “FPGA 和 Verilog HDL 是什么?”。在笔者

的心里,FPGA 宛如 “一堆乐高积木”和 Verilog HDL 是自己的手(工具) ,自己可

以随心所愿的要怎么拆就怎么拆。

这句话所包含的意义又是什么呢?

第一“形状”。很多的新手都发问 FPGA 到底是什么?对于笔者的看法,FPGA 就是一

堆乐高积木而已。但是这堆乐高积木又能做什么。笔者相信很多朋友在接触 FPGA 之前,

都有接触过单片机。当学习 FPGA 的时候,我们会不知不觉把 FPGA 当成“控制器”的

形状。这样的想法并非完全正确也非完全错误。无论是 “接口”,“控制器”,“IC”,从

最简单的到最复杂的,都是 FPGA 都可以涉及的范围,都是 FPGA 可以实现的“形状”。

FPGA 就是一堆乐高积木,只要方法得到,手段有效,就没有拆不出来的“形状”

第二“学习的形状”。我们应该用什么的形状来学习 FPGA 呢?笔者的答案都很肯定,

就是什么都涉及,但是不求最困难的,只求最相似和最简单的。如:一个接口的设计,可

以是一个数码管驱动程式。在笔者的众多学习之中,都是从“控制器”的这个形状入门

开始,当掌握资源的驱动方法后,尝试建模,然后学习接口封装,最后甚至可以建立起

属于自己的系统。

第三“组合 FPGA 的一双手”。Verilog HDL 语言就如"组合乐高积木的一双手"(工具),

没有了“这双手”我们就无法使 FPGA 组装起来。有一句话笔者一直都在强调,硬件描

述语言是基本功,必须很好的掌握。

第四“建模技巧”。建模技巧可以看成是“组合乐高积木的手段”,这也是这本笔记要讨

论的东西。事实上是诸多新手面对最大的瓶颈。建模这东西原本就没有具体的规则,笔

者也是按照自己建模习惯,作为一个基础,希望可以帮助到更多的新手越过这段瓶颈。

第五“要掌握到何种的地步才算足够?”作为曾经是新手的笔者,对于这问题笔者表示

压力很大。但是经过一轮的思考,发现自己真的是笨级了,这些“杞人忧天”的问题,

还是顺其自然的好。最重要就是学习的心态,学习是一件快乐的事情,为什么要搞得如

此忧郁呢?在笔者看来,最起码的,也是最重要的就是“掌握基本功”。

事实上这本笔记仅是讨论“Verilog HDL 基本功的一部分”,因为 FPGA 涉及的知识实在

是太广泛了,如时序分析等相关的知识。所以呀,我希望大家保持正向的“学习心态”,

好好的阅读这本笔记。这本笔记不会涉及太多专业的知识,而是非常焦距在建模的基础

之上。“学习如同玩具,要一点一滴的去享受,才能体会到乐趣,如果只是单纯的为了

目的或者是匆忙来去,无论是多么有趣的玩具在你的手中,你永远也不会体验到当中的

乐趣”。学习应该时时刻刻保持正向的心态。

八

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc