皖 西 学 院

课程设计报告

系

专

别:

业:

机电系

学 生 姓 名:

学 号:

课程设计题目:

篮球 24 秒计时器设计与仿真

起 迄 日 期:

课程设计地点:

指 导 教 师:

完成任务日期:

09 年 11 月 19 日

�

目录

摘要

第一章 计时器概述

1.1 篮球竞赛 24 秒计时器功能

1.2 设计任务及要求

1.2.1 基本要求

1.2.2 设计任务及目标

1.2.3 主要参考器件:

第二章 电路设计原理与单元模块

2.1 设计原理

2.2 设计方案

2.3 单元模块

2.3.1 8421BCD 码递减计数器模块

2.3.2 时钟模块

2.3.3 辅助时序控制模块

第三章 实验仿真

第四章 实验体会

结 论

致谢

参考文献

附录

�

摘要:本课程设计,设计了篮球竞赛 24 秒计时器。此计时器功能齐全,可以直

接清零、启动、暂停和连续以及具有光电报警功能,同时应用了七段数码管来显

示时间。此计时器有了启动、暂停和连续功能,可以方便地实现断点计时功能,

当计时器递减到零时,会发出光电报警信号。

第一章 计时器概述

1.1 篮球竞赛 24 秒计时器功能

随着信息时代的到来,电子技术在社会生活中发挥着越来越重要的作用,运

用模电和数电知识设计的电子产品成为社会生活不可缺少的一部分,特别是在各

种竞技运动中,定时器成为检验运动员成绩的一个重要工具。在篮球比赛中,规

定了球员的持球时间不能超过 24 秒,否则就犯规了。本课程设计的“篮球竞赛

24 秒计时器”,可用于篮球比赛中,用于对球员持球时间 24 秒限制。一旦球员

的持球时间超过了 24 秒,它自动的报警从而判定此球员的犯规。

本设计主要能完成:显示 24 秒倒计时功能;系统设置外部操作开关,控制

计时器的直接清零、启动和暂停/连续功能;在直接清零时,数码管显示器灭灯;

计时器为 24 秒递减计时其计时间隔为 1 秒;计时器递减计时到零时,数码显示

器不灭灯,同时发出光电报警信号等。

1.2 设计任务及要求

1.2.1 本次课程设计应达到的目的

(1) 综合运用相关课程中所学到的理论知识去独立完成某一设计课题;

(2) 通过查阅手册和相关文献资料,培养学生独立分析和解决问题的能力;

�

(3) 进一步熟悉常用芯片和电子器件的类型及特性,并掌握合理选用器件的

原则;

(4) 学会电路的设计与仿真;

(5) 培养严肃认真的工作作风和严谨的科学态度。

1.2.2 设计任务及目标

(1) 具有 24 秒计时功能;

(2) 设置外部操作开关,控制计数器的直接清零、启动、和暂停/连续功能;

(3) 计时器为 24 秒递减计时,计时间隔为 1 秒;

(4) 计时到零时数码管不能灭灯,同时发出光电报警。

(5) 并用相关仿真软件对电路进行仿真。

1.2.3 主要参考器件:

555

74LS74(1)

74LS192(2)

第二章 电路设计原理与单元模块

2.1 设计原理

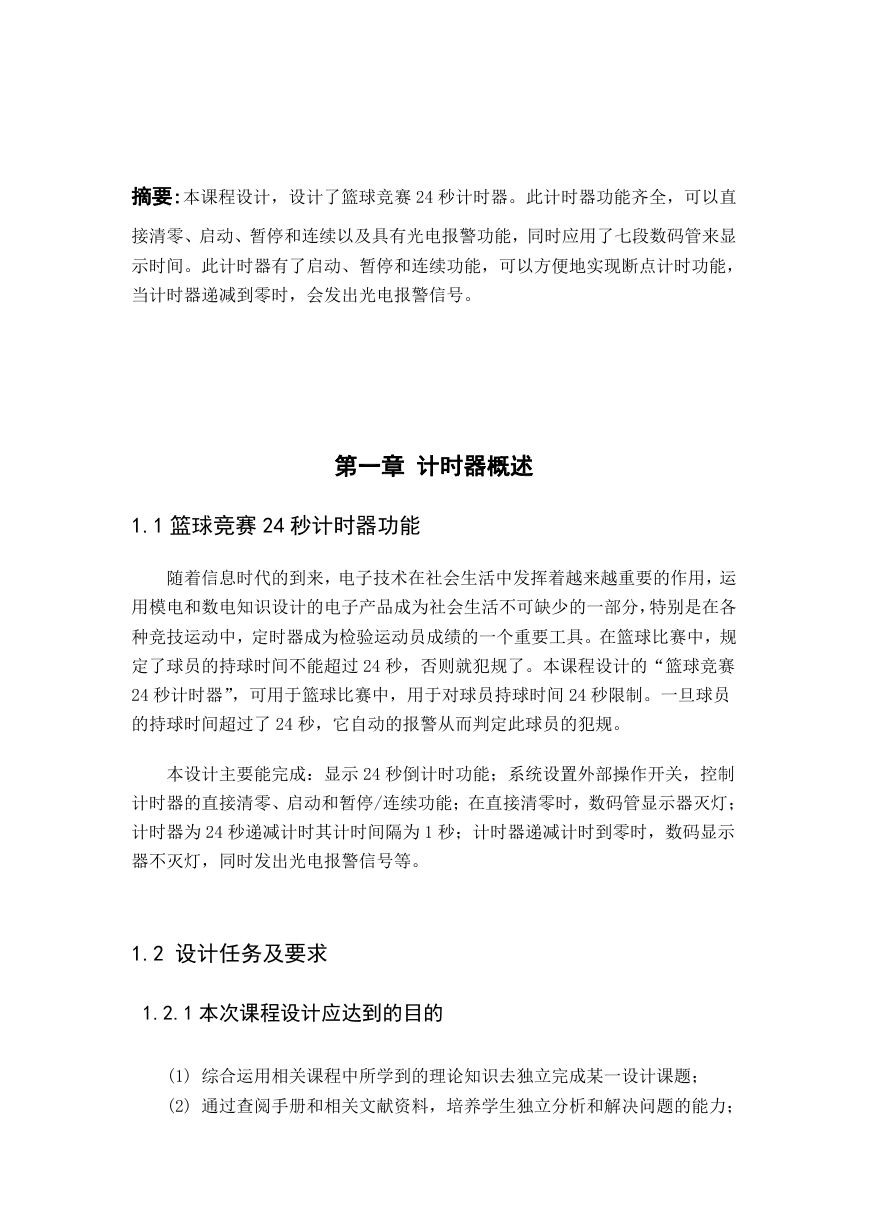

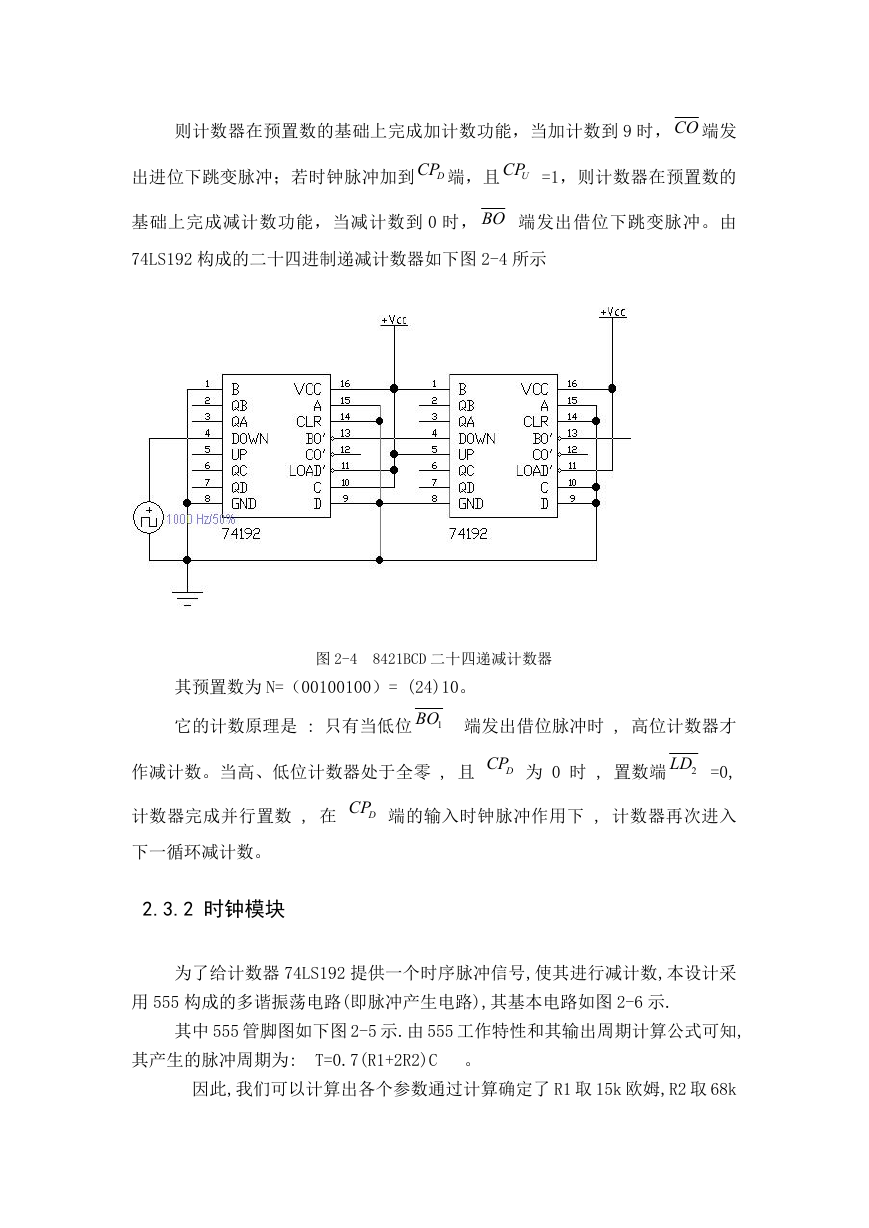

24 秒计时器的总体参考方案框图如图 2-1 所示。它包括秒脉冲发生器、计

数器、译码显示电路、报警电路和辅助时序控制电路(简称控制电路)等五个模

块组成。其中计数器和控制电路是系统的主要模块。计数器完成 24 秒计时功能,

而控制电路完成计数器的直接清零、启动计数、暂停/连续计数、译码显示电路

的显示与灭灯、定时时间到报警等功能。

�

秒脉冲发生器

计数器

控制电路

外 部 操

作开关

译码

显示

报警电路

图 2-1

24 秒计时器系统设计框图

秒脉冲发生器产生的信号是电路的时钟脉冲和定时标准,但本设计对此信号

要求并不太高,故电路可采用 555 集成电路或由 TTL 与非门组成的多谐振荡器构

成。

译码显示电路由 74LS48 和共阴极七段 LED 显示器组成。报警电路在实验中

可用发光二极管代替。

2.2 设计方案

分析设计任务,计数器和控制电路是系统的主要部分。计数器完成 24s 计

时功能,而控制电路具有直接控制计数器的启动计数、暂停/连续计数、译码显

示电路的显示和灭灯功能。为了满足系统的设计要求,在设计控制电路时,应正

确处理各个信号之间的时序关系。在操作直接清零开关时,要求计数器清零,数

码显示器灭灯。

当启动开关闭合时,控制电路应封锁时钟信号 CP,同时计数器完成置数功

能,译码显示电路显示“24”字样;当启动开关断开时,计数器开始计数;当暂

停/连

续开关拨在暂停位置上时,计数器停止计数,处于保持状态;当

暂停/连续开关拨在连续时,计数器继续递减计数。

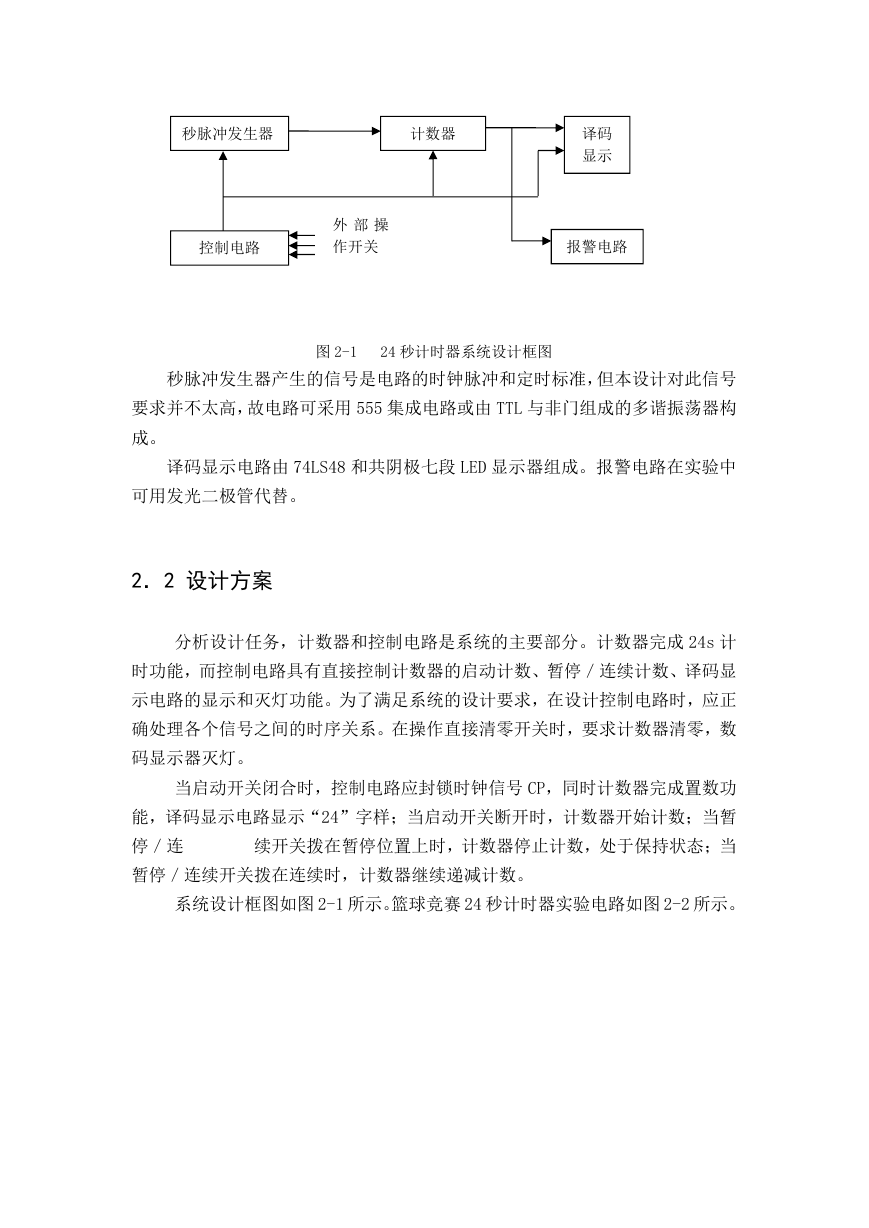

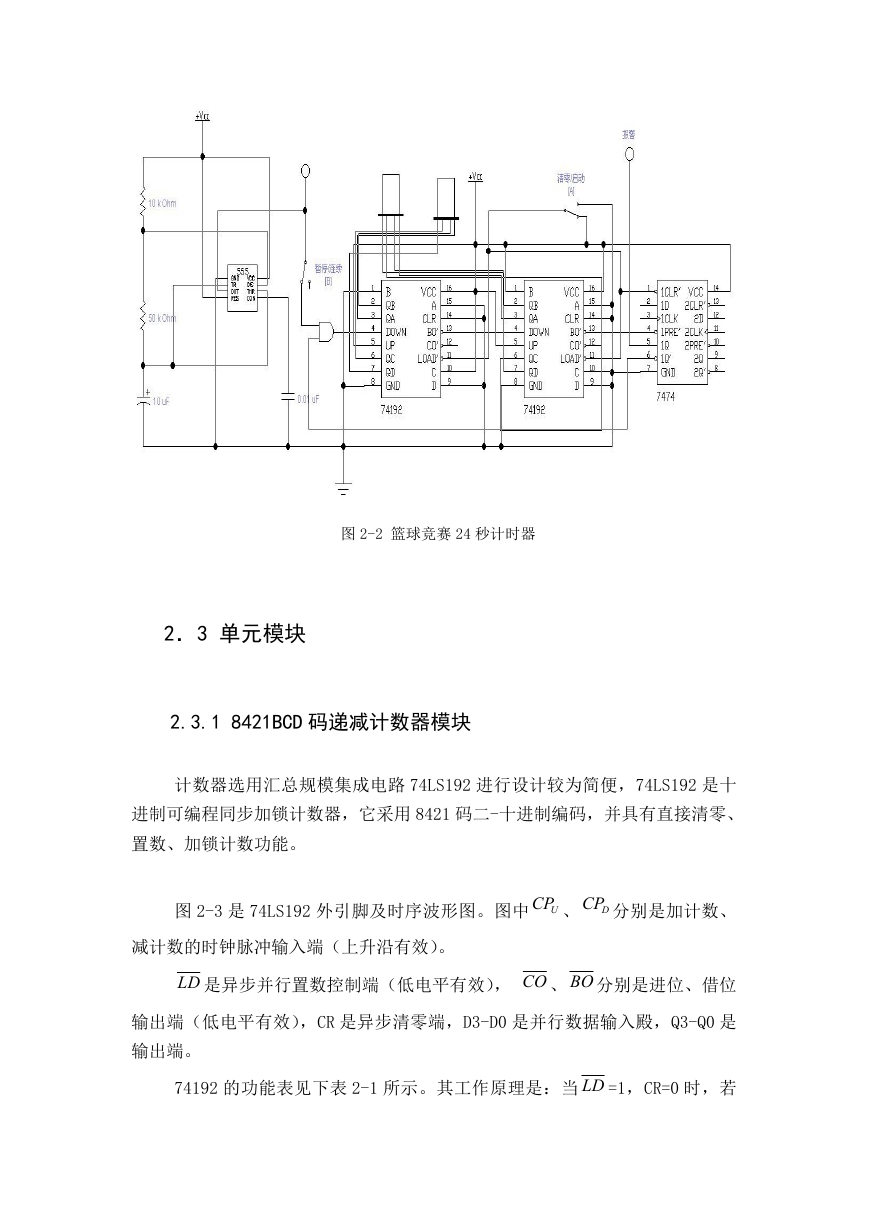

系统设计框图如图 2-1 所示。篮球竞赛 24 秒计时器实验电路如图 2-2 所示。

�

图 2-2 篮球竞赛 24 秒计时器

2.3 单元模块

2.3.1 8421BCD 码递减计数器模块

计数器选用汇总规模集成电路 74LS192 进行设计较为简便,74LS192 是十

进制可编程同步加锁计数器,它采用 8421 码二-十进制编码,并具有直接清零、

置数、加锁计数功能。

图 2-3 是 74LS192 外引脚及时序波形图。图中 UCP 、 DCP 分别是加计数、

减计数的时钟脉冲输入端(上升沿有效)。

LD 是异步并行置数控制端(低电平有效), CO 、 BO 分别是进位、借位

输出端(低电平有效),CR 是异步清零端,D3-D0 是并行数据输入殿,Q3-Q0 是

输出端。

74192 的功能表见下表 2-1 所示。其工作原理是:当 LD =1,CR=0 时,若

�

时钟脉冲加到 UCP 端,且 DCP =1

图 2-3

74LS192 外引脚及时序波形图

表 2-1

74LS192 功能表

RD

1

0

0

0

LD

x

0

1

1

CPU

x

x

1

CPD

x

x

1

功 能

清 零

置 数

加法计数

减法计数

�

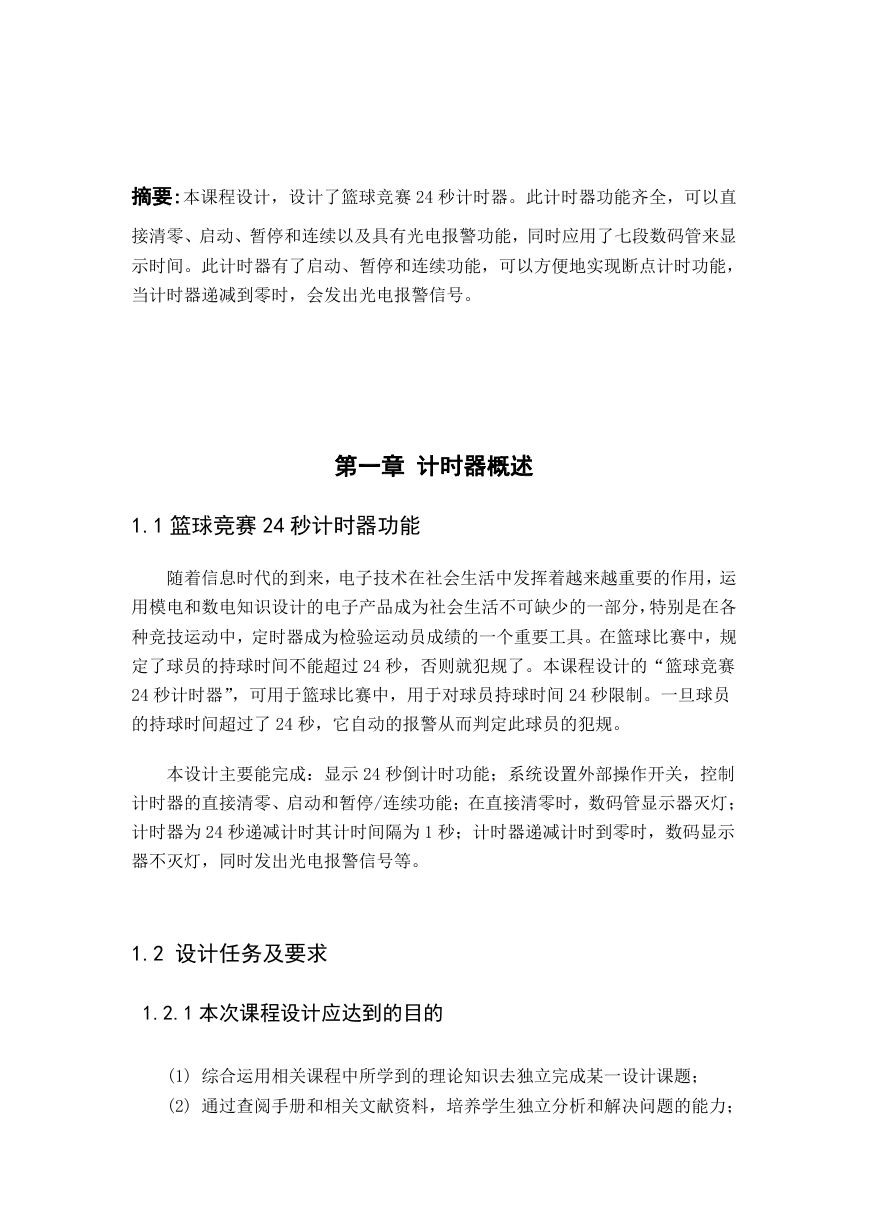

则计数器在预置数的基础上完成加计数功能,当加计数到 9 时, CO 端发

出进位下跳变脉冲;若时钟脉冲加到 DCP 端,且 UCP =1,则计数器在预置数的

基础上完成减计数功能,当减计数到 0 时, BO 端发出借位下跳变脉冲。由

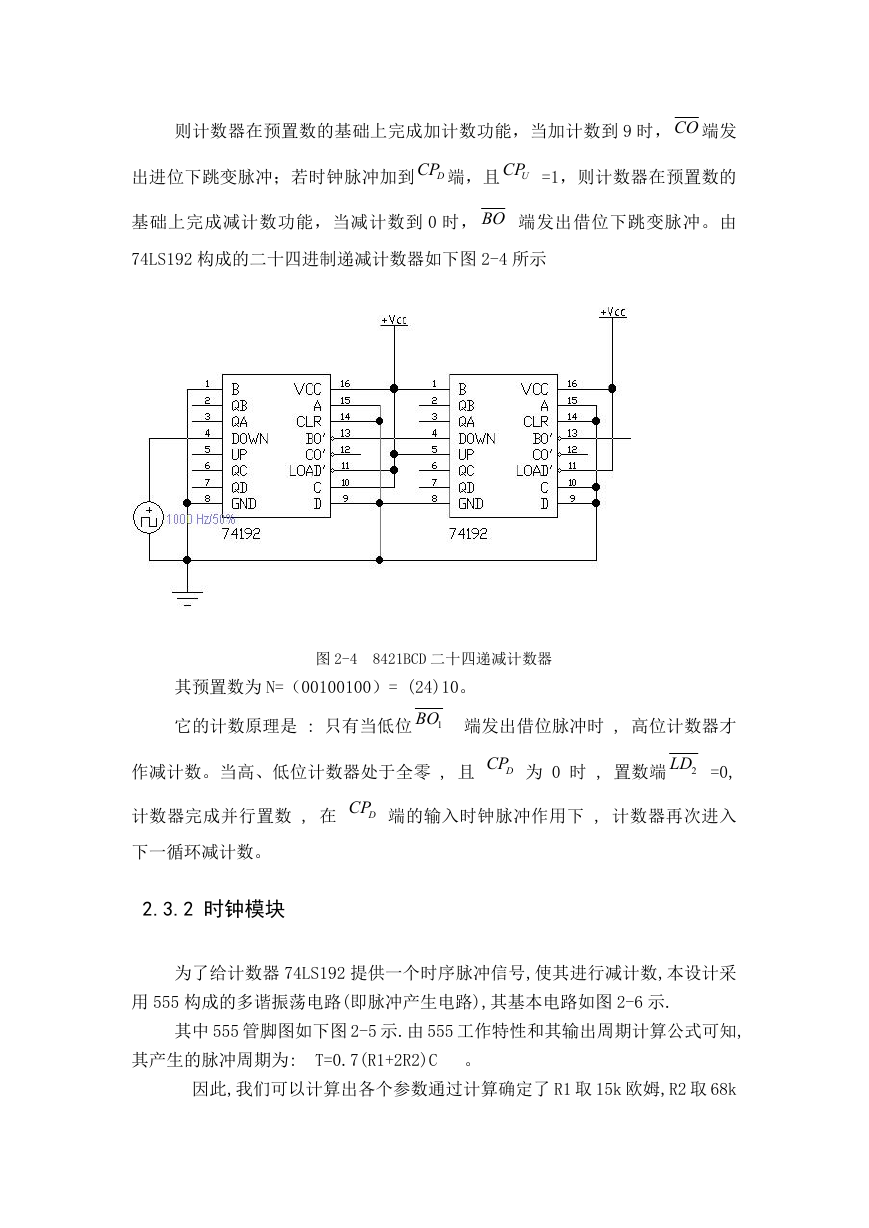

74LS192 构成的二十四进制递减计数器如下图 2-4 所示

图 2-4

8421BCD 二十四递减计数器

其预置数为 N=(00100100)= (24)10。

它的计数原理是 : 只有当低位 1BO 端发出借位脉冲时 , 高位计数器才

作减计数。当高、低位计数器处于全零 , 且 DCP 为 0 时 , 置数端 2LD =0,

计数器完成并行置数 , 在 DCP 端的输入时钟脉冲作用下 , 计数器再次进入

下一循环减计数。

2.3.2 时钟模块

为了给计数器 74LS192 提供一个时序脉冲信号,使其进行减计数,本设计采

用 555 构成的多谐振荡电路(即脉冲产生电路),其基本电路如图 2-6 示.

其中 555 管脚图如下图 2-5 示.由 555 工作特性和其输出周期计算公式可知,

其产生的脉冲周期为:

T=0.7(R1+2R2)C 。

因此,我们可以计算出各个参数通过计算确定了 R1 取 15k 欧姆,R2 取 68k

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc