武汉理工大学<<计算机组成原理>>课程设计说明书

目 录

课程设计任务书 ………………………………………………………………………………. 2

报告正文 …………………………………………………………………………………………………3

1 课程设计目的 …………………………………………………………………………3

2 课程设计设备 …………………………………………………………………………3

3 课程设计原理……………………………………………………………………………3

3.1 cpu 与存储器的连接 ……………………………………………………3

3.2 静态存储器电路原理图…………………………………………………4

3.3 集成 RAM 芯片 SRAM6264…………………………………………………4

3.4 存储容量的扩展…………………………………………………………………6

3.5 2-4 译码器……………………………………………………………………………7

4 电路设计………………………………………………………………………………………8

4.1 32k×16 位的 SRAM 的逻辑图…………………………………………… 8

4.2 32k×16 位的 SRAM 的管脚图…………………………………………… 9

4.3 内部连接图………………………………………………………………………… 10

4.4 存储器连接图 ……………………………………………………………… 11

5 运行过程及结果记录……………………………………………………………… 11

5.1 写数据操作………………………………………………………………………………… 11

5.2 读数据操作 …………………………………………………………………………… 12

5.3 实验数据记录………………………………………………………………………………12

6 总结……………………………………………………………………………………………… 13

7 参考文献 ………………………………………………………………………………… 13

评分表 …………………………………………………………………………………………………………

封 底 …………………………………………………………………………………………………………

�

武汉理工大学<<计算机组成原理>>课程设计说明书

课程设计任务书

学生姓名:

颜凤丽

专业班级: 计算机 0501

指导教师:

田小华

工作单位: 计算机学院

题 目: 静态存储器(6264)电路设计与实现

初始条件:

1.完成<<计算机组成原理>>课程教学与实验

2.TDN-CM 计算机组成原理教学实验系统

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)

1.掌握存储器的设计目标和功能特点,熟悉 SRAM6264 一的结构特点

2.利用 SRAM6264 和相关的基本电路设计 16 位地址的存储器电路

3.在 TDN-CM+实验系统中,用 SRAM6264 和门电路实现 16 位地址的存储器电路

4.以表格记录在学号加班号为起点的 16 个地址单元中,分别写入相应的反码

5.绘制带开关输入功能的存储器电路连接图,撰写相应的设计报告

时间安排:

1.第 18 周周日(元月 6 日):全体集中讲解课程设计方法与要求(鉴 3-302)

2.第 19 周周 1~5(元月 7~11 日):分班设计与调试, 撰写课程设计报告

指导教师签名:

2008 年 元 月 5 日

系主任(或责任教师)签名:

2008 年 元 月 5 日

2

�

武汉理工大学<<计算机组成原理>>课程设计说明书

静态存储器(6264)电路设计与实现

1 课程设计目的

1.1 通过课程设计实践,树立正确的设计思想,培养综合运用计算机组成原理课程和其他

先修课程的理论来分析和解决计算机一些基本设计问题的能力。

1.2 掌握静态随机存储器 RAM 的工作特性及使用方法,熟悉 SRAM6264 的结构特点。

1.3 了解半导体存储器存储和读数据的方法

1.4 运用说学的知识,基本掌握静态存储器的基本设计方法和思路,能够完成设计要求

2 课程设计设备

TDN-CM 计算机组成原理实验系统,排线若干;6264 芯片 8 片。

3 课程设计原理

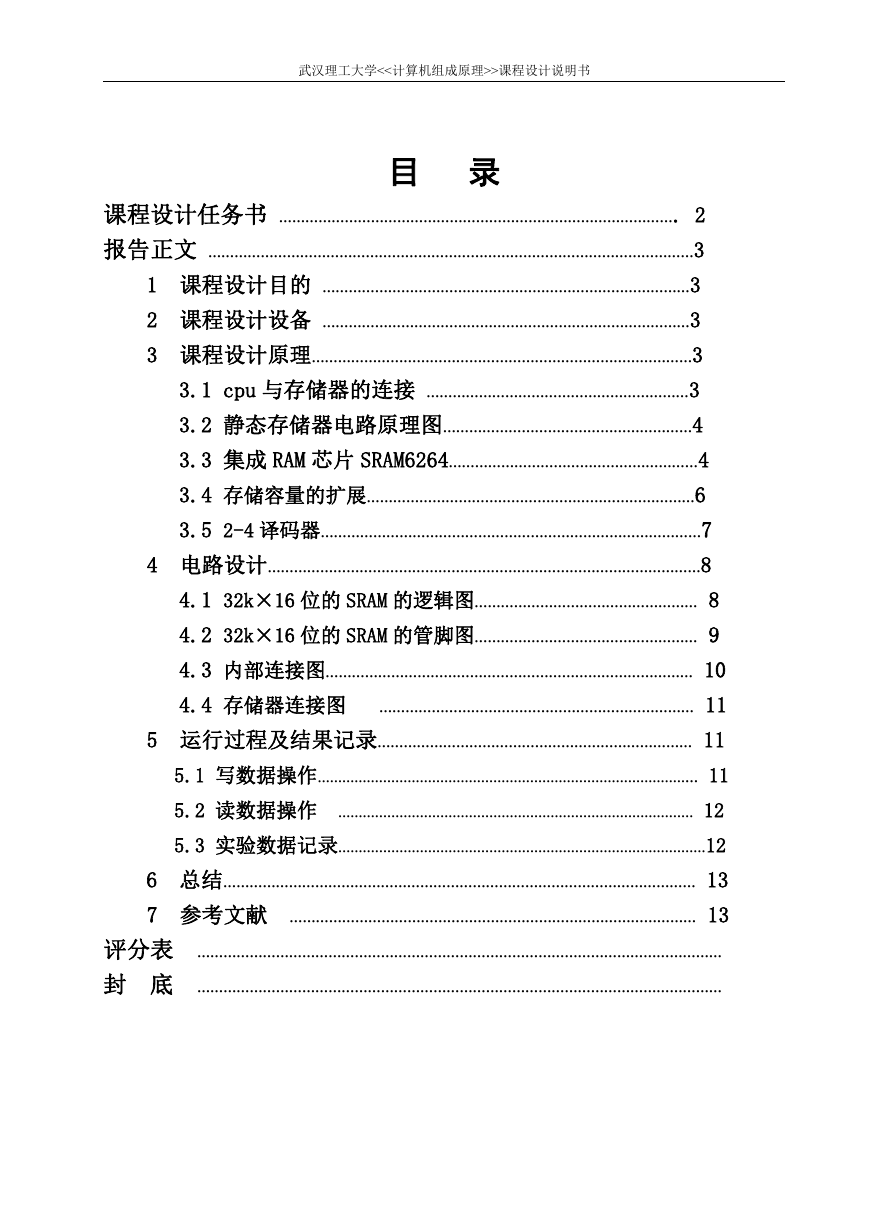

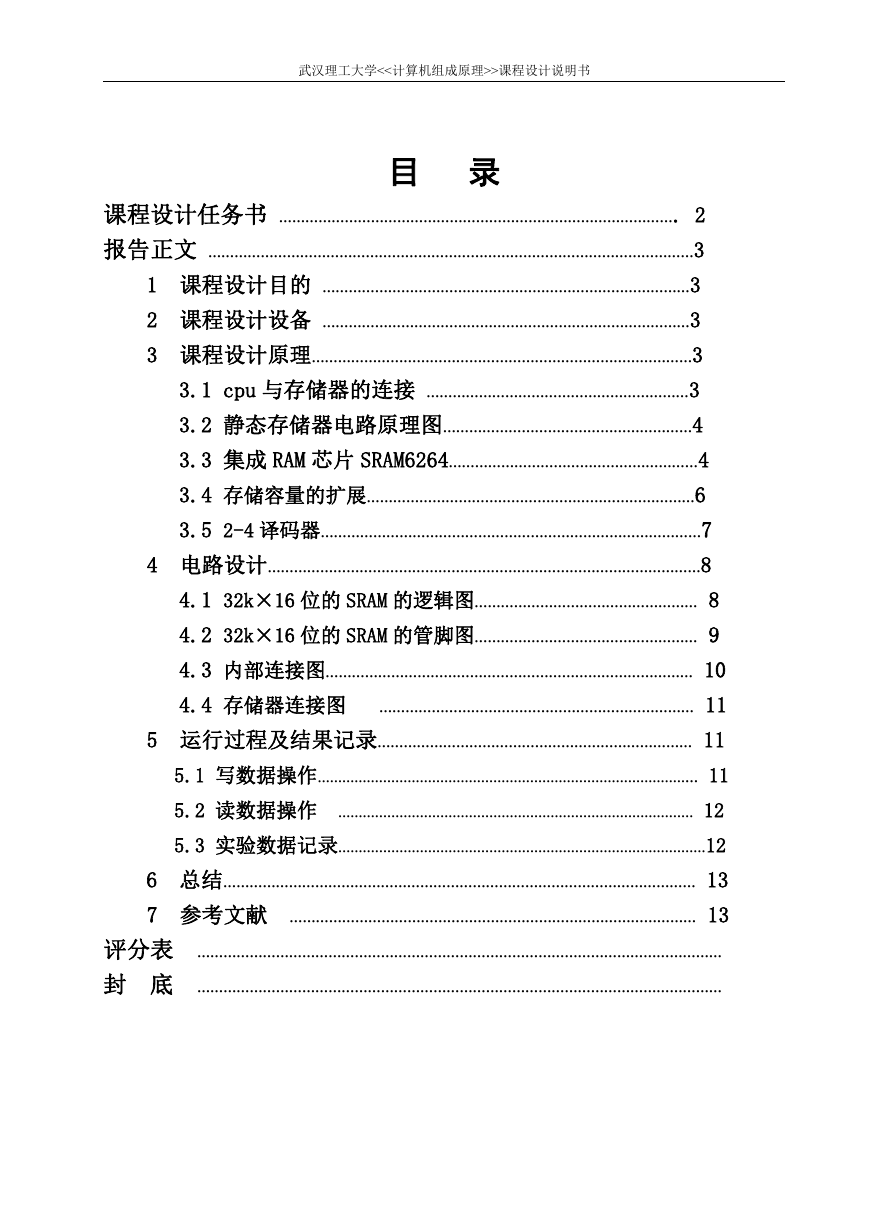

3.1cpu 与存储器的连接

微处理器通过数据总线、地址总线及控制总线与存储器连接,如下图所示:

地址总线

CPU

数据总线

存储器

控制总线

地址总线为地址信号,用来指明选中的存储单元地址。

数据总线为数据信号,它是微处理器送往存储器的信息或存储器送往微处理器的信息。

它包括指令和数据。

控制总线发出存储器读写信号,以便从 ROM、RAM 中读出指令或数据,或者向 RAM 写入

数据。

①把输入信息存储到由地址信号和控制信号指定的存储单元中。

②根据控制信号的读出要求,把存储在指定存储单元中的数据读出来。

3

�

武汉理工大学<<计算机组成原理>>课程设计说明书

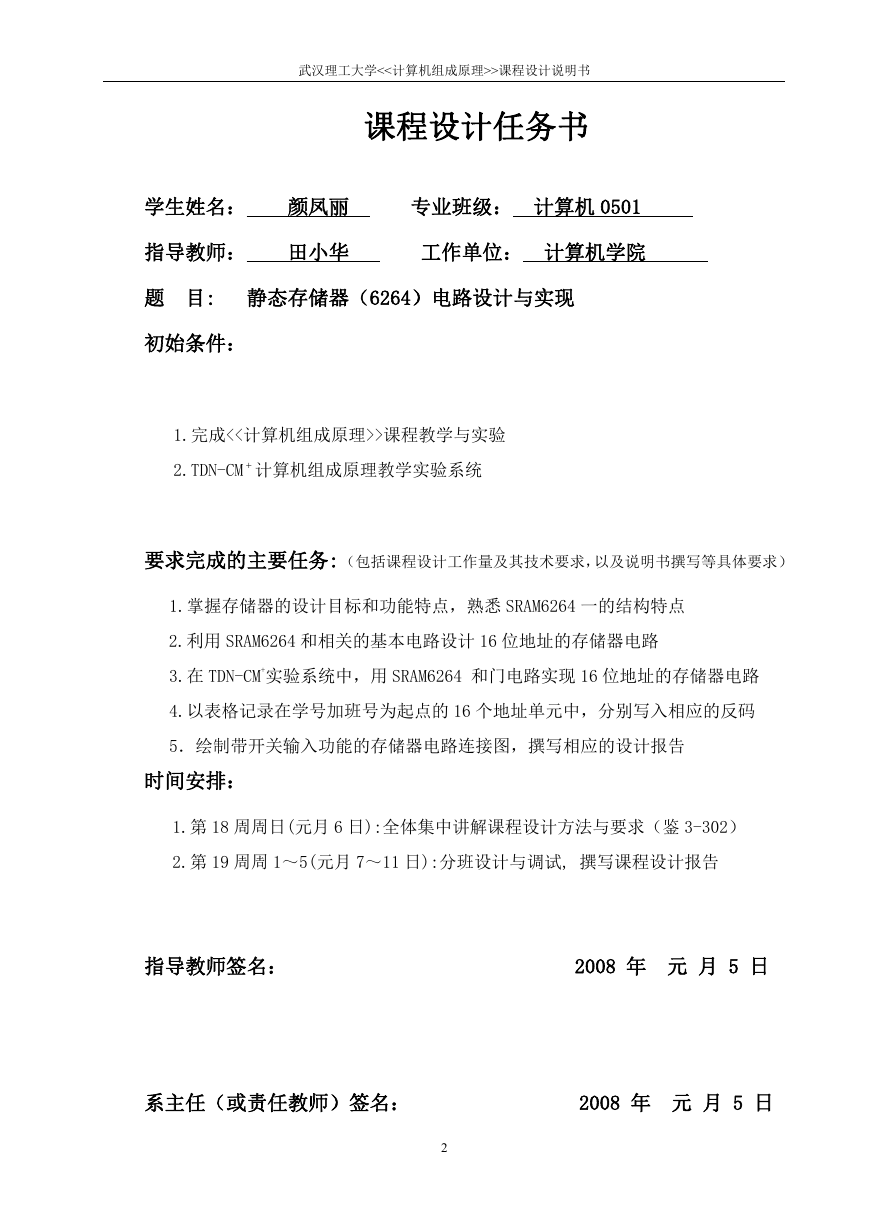

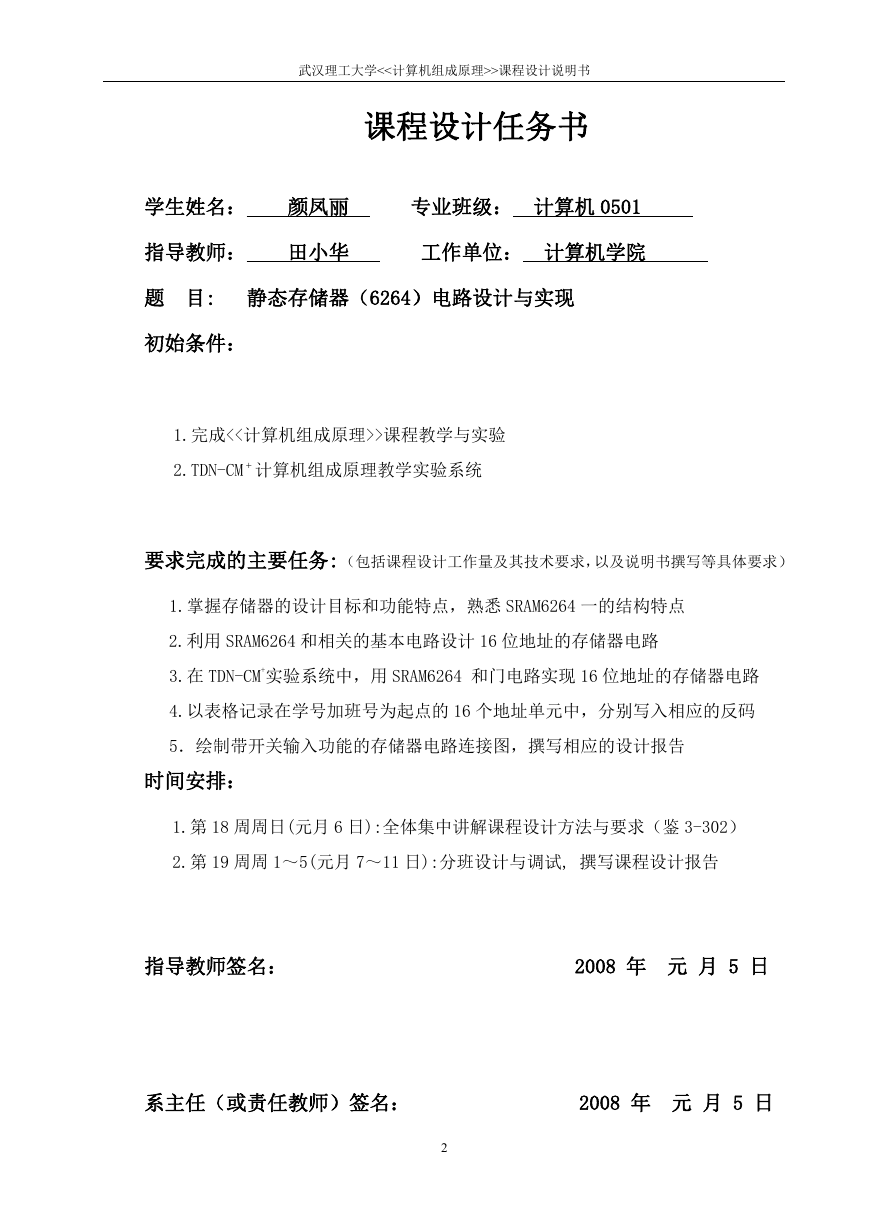

3.2 静态存储器电路原理图

有三个控制线:CE(片选线)、OE(读线)、WE(写线)。当片选有效(CE=0)时,OE=0

时进行读操作,WE=0 时进行写操作。本实验中将 OE 常接地,在此情况下,当 CE=0、WE=0

时进行读操作,CE-0、WE=1 时进行写操作,其写时间与 T3 脉冲宽度一致。

实验时将 T3 脉冲接致实验板上时序电路模块的 TS3 相应插孔中,其脉冲宽度可调,

其他电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中 SW-B 为低电平有效,

LDAR 为高电平有效。

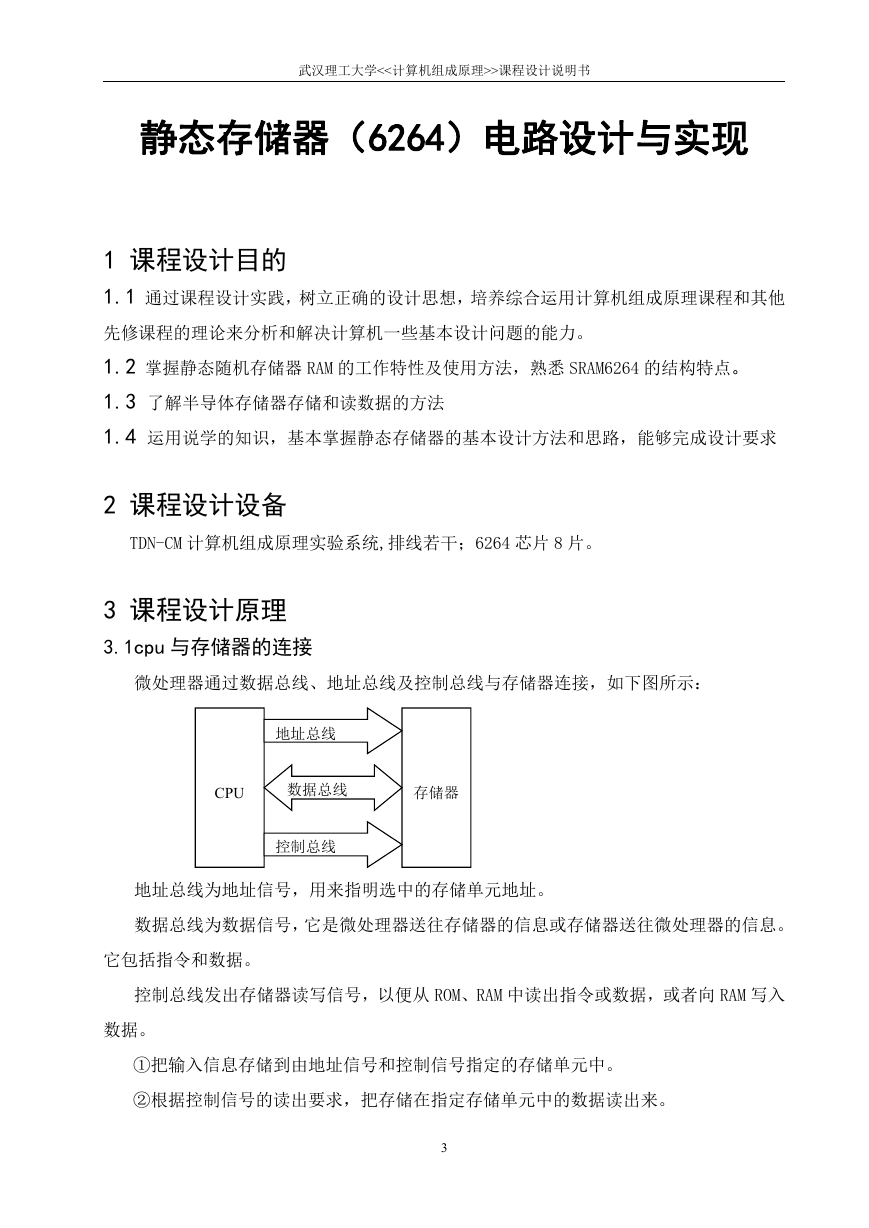

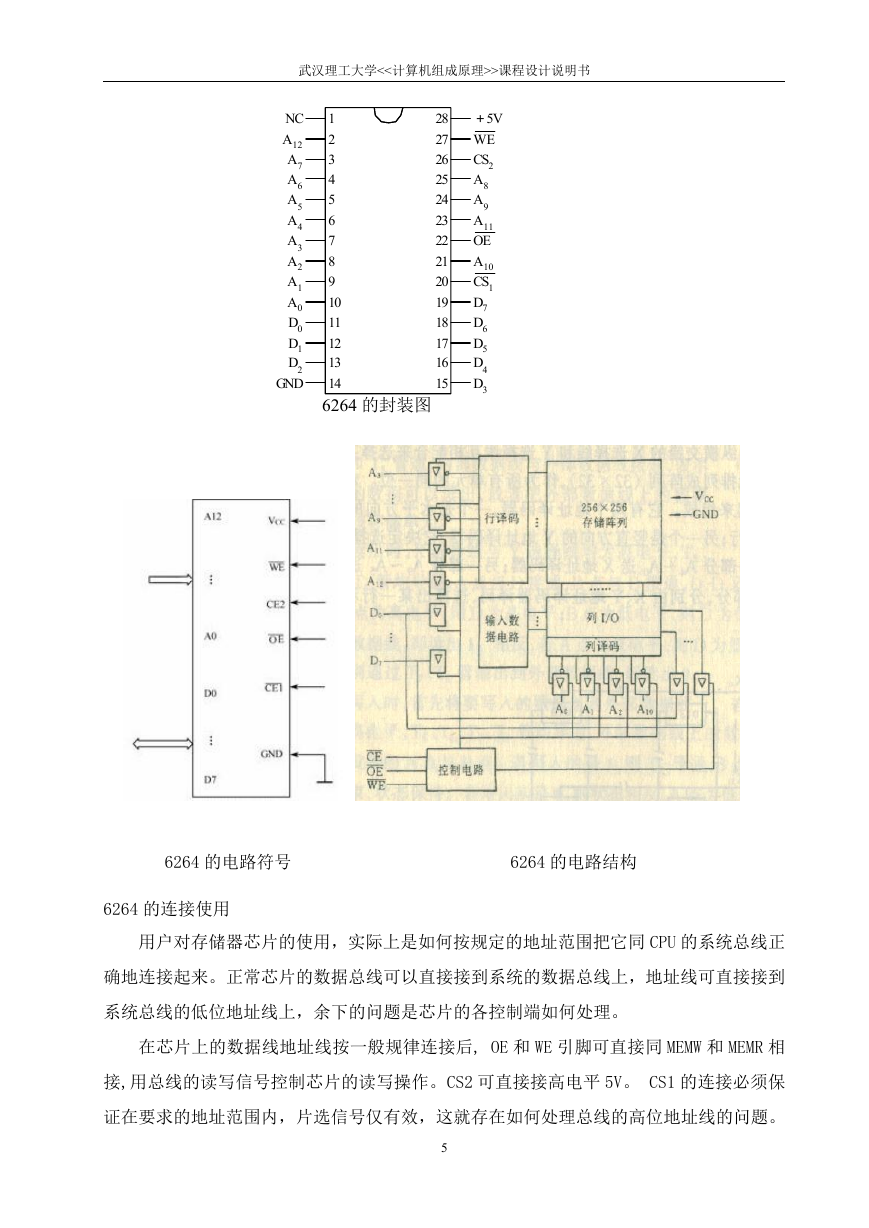

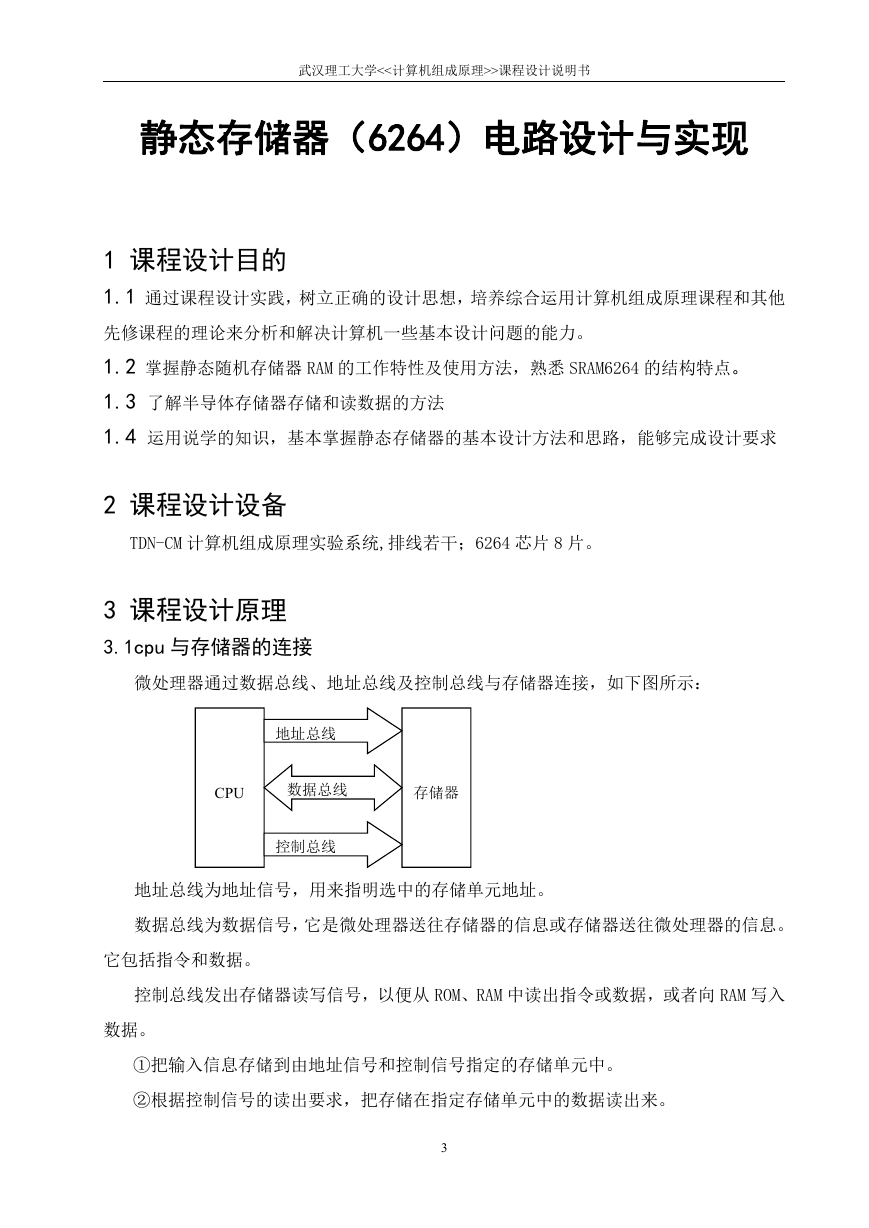

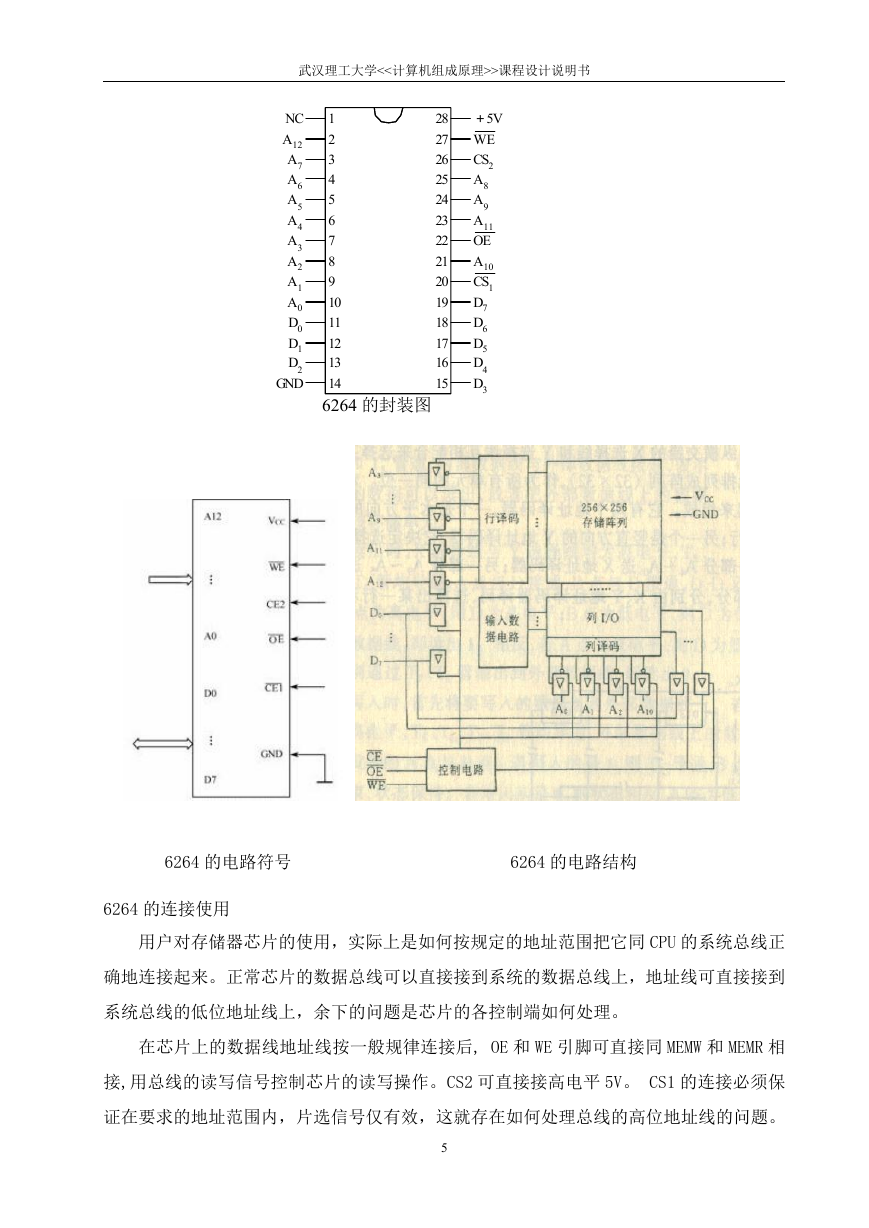

3.3 集成 RAM 芯片 SRAM6264

常用的普通集成 RAM 芯片 SRAM6264 的封装图、电路符号及内部结构分别如图所示。图

中 1CS , 2CS 是片选信号,WE 是允许与入信号,OE 是允许输出(即读出信号),A0~A12 是

地址输入代码;I∕O0~I∕O7 是 8 位数据输出,VDD 为电源电压,GND 接地,NC 悬空。

RAM 的容量用“字数×位数”,6264 的存储容量为“8192 字×8 位”。当存储容量不够

时,可以进行字位扩展。

4

�

武汉理工大学<<计算机组成原理>>课程设计说明书

NC

A12

A7

A6

A5

A4

A3

A2

A1

A0

D0

D1

D2

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

6264 的封装图

28

27

26

25

24

23

22

21

20

19

18

17

16

15

+5V

WE

CS2

A8

A9

A11

OE

A10

CS1

D7

D6

D5

D4

D3

6264 的电路符号

6264 的电路结构

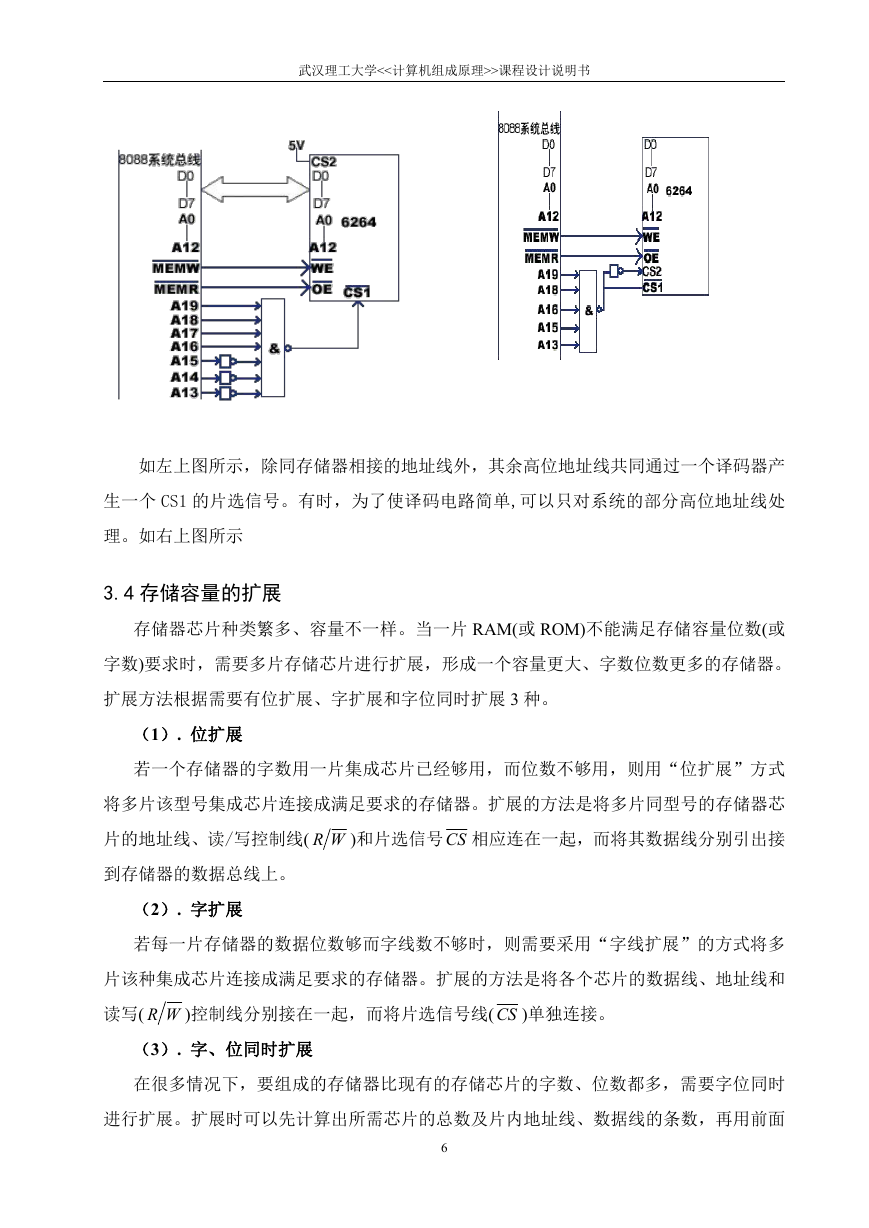

6264 的连接使用

用户对存储器芯片的使用,实际上是如何按规定的地址范围把它同 CPU 的系统总线正

确地连接起来。正常芯片的数据总线可以直接接到系统的数据总线上,地址线可直接接到

系统总线的低位地址线上,余下的问题是芯片的各控制端如何处理。

在芯片上的数据线地址线按一般规律连接后, OE 和 WE 引脚可直接同 MEMW 和 MEMR 相

接,用总线的读写信号控制芯片的读写操作。CS2 可直接接高电平 5V。 CS1 的连接必须保

证在要求的地址范围内,片选信号仅有效,这就存在如何处理总线的高位地址线的问题。

5

�

武汉理工大学<<计算机组成原理>>课程设计说明书

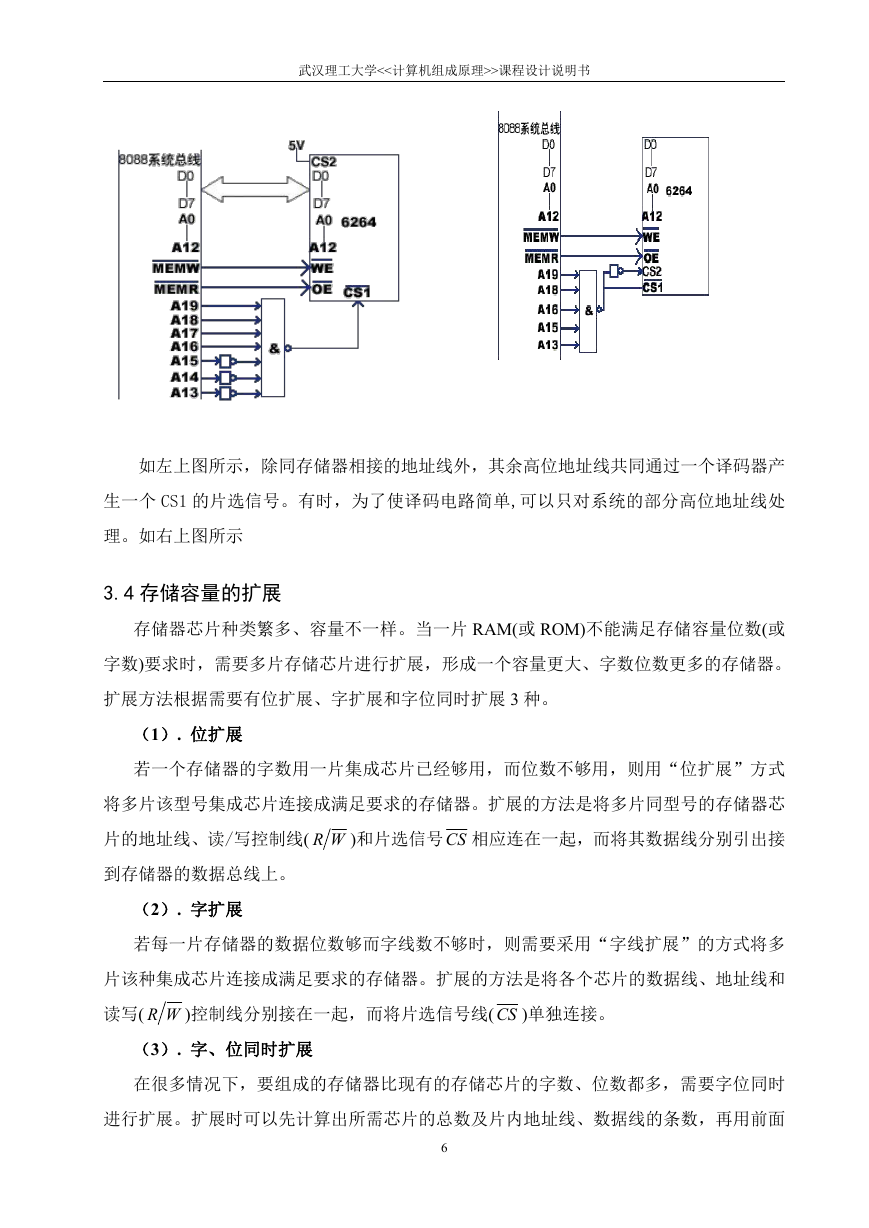

如左上图所示,除同存储器相接的地址线外,其余高位地址线共同通过一个译码器产

生一个 CS1 的片选信号。有时,为了使译码电路简单,可以只对系统的部分高位地址线处

理。如右上图所示

3.4 存储容量的扩展

存储器芯片种类繁多、容量不一样。当一片 RAM(或 ROM)不能满足存储容量位数(或

字数)要求时,需要多片存储芯片进行扩展,形成一个容量更大、字数位数更多的存储器。

扩展方法根据需要有位扩展、字扩展和字位同时扩展 3 种。

(1). 位扩展

若一个存储器的字数用一片集成芯片已经够用,而位数不够用,则用“位扩展”方式

将多片该型号集成芯片连接成满足要求的存储器。扩展的方法是将多片同型号的存储器芯

片的地址线、读/写控制线( WR

)和片选信号CS 相应连在一起,而将其数据线分别引出接

到存储器的数据总线上。

(2). 字扩展

若每一片存储器的数据位数够而字线数不够时,则需要采用“字线扩展”的方式将多

片该种集成芯片连接成满足要求的存储器。扩展的方法是将各个芯片的数据线、地址线和

读写( WR

)控制线分别接在一起,而将片选信号线(CS )单独连接。

(3). 字、位同时扩展

在很多情况下,要组成的存储器比现有的存储芯片的字数、位数都多,需要字位同时

进行扩展。扩展时可以先计算出所需芯片的总数及片内地址线、数据线的条数,再用前面

6

�

武汉理工大学<<计算机组成原理>>课程设计说明书

介绍的方法进行扩展,先进行位扩展,再进行字扩展。

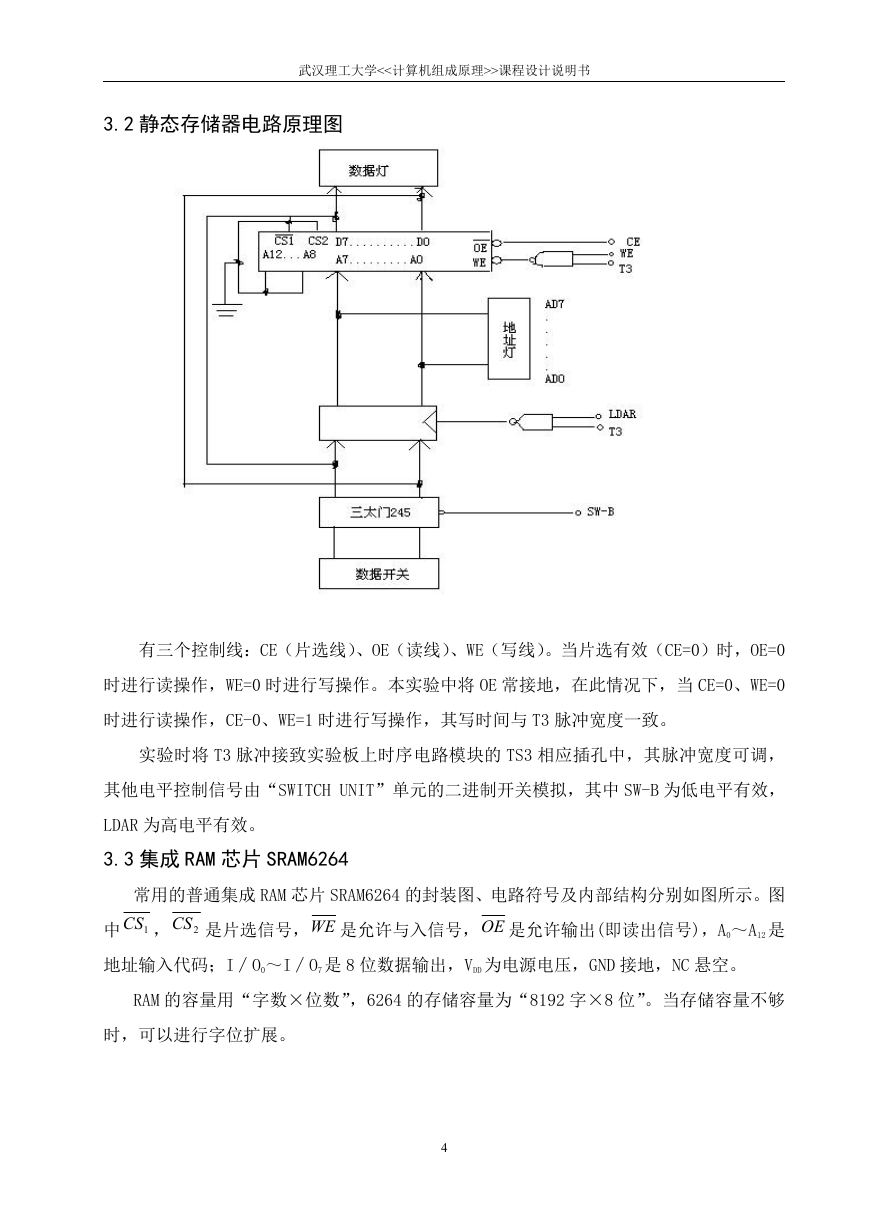

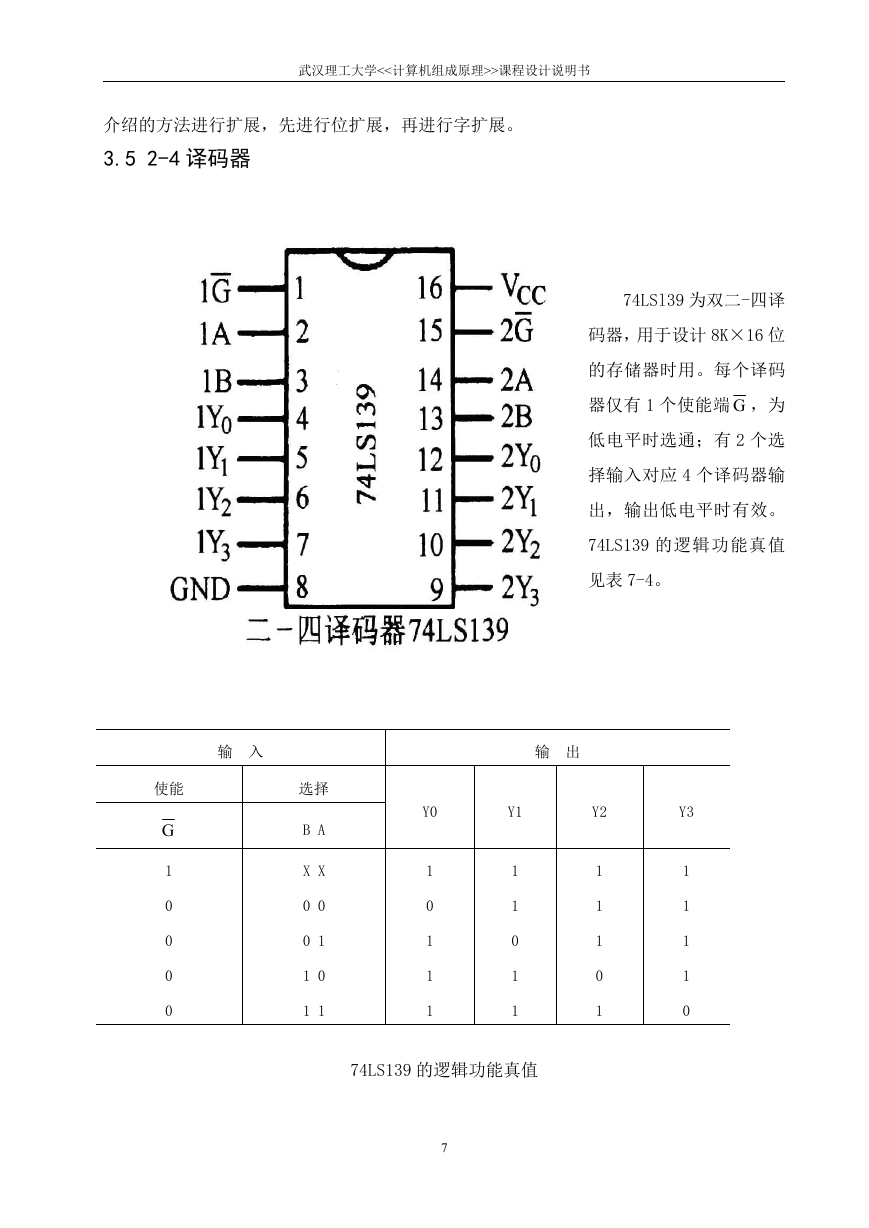

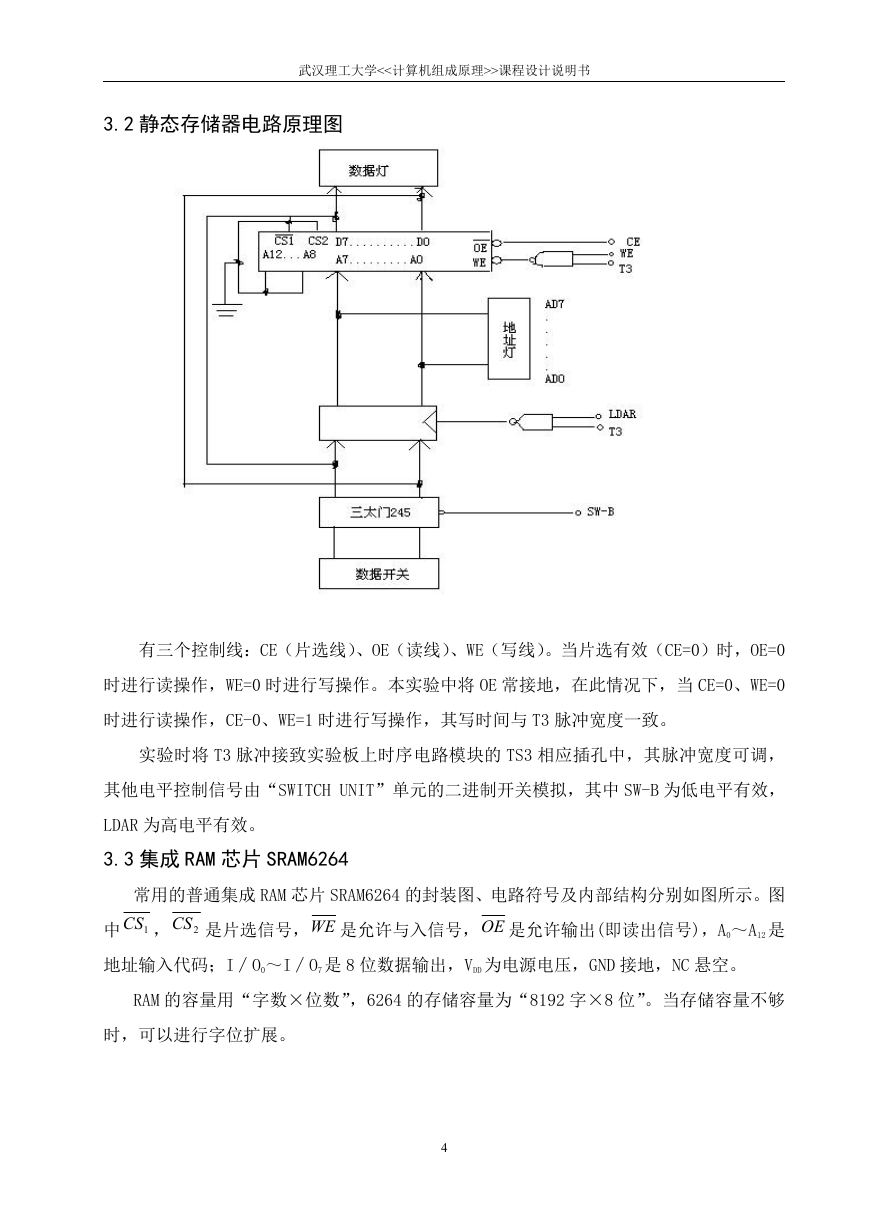

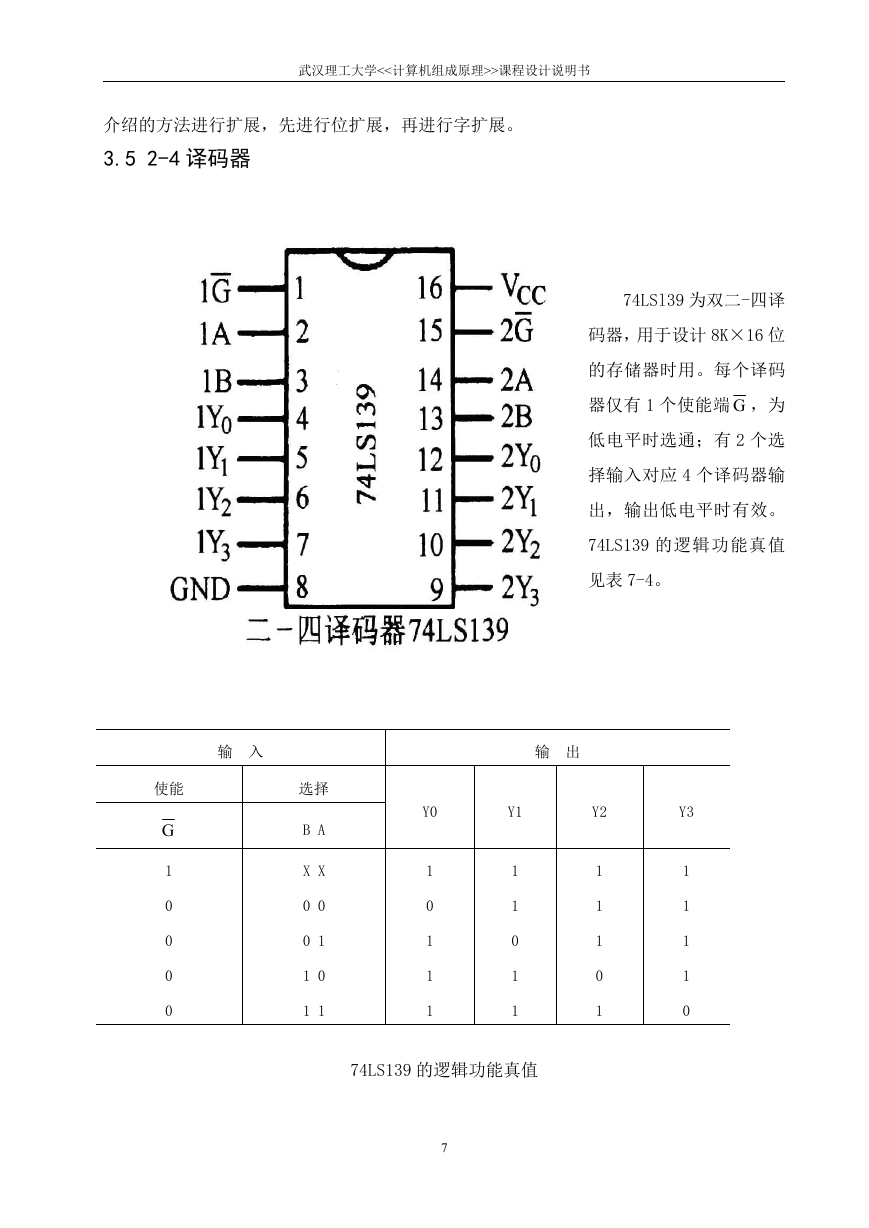

3.5 2-4 译码器

74LSl39 为双二-四译

码器,用于设计 8K×16 位

的存储器时用。每个译码

器仅有 1 个使能端 G ,为

低电平时选通;有 2 个选

择输入对应 4 个译码器输

出,输出低电平时有效。

74LS139 的逻辑功能真值

见表 7-4。

输 入

输 出

使能

选择

G

1

0

0

0

0

B A

X X

0 0

0 1

1 0

1 1

Y0

Y1

Y2

Y3

1

0

1

1

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

74LS139 的逻辑功能真值

7

�

武汉理工大学<<计算机组成原理>>课程设计说明书

4.电路设计

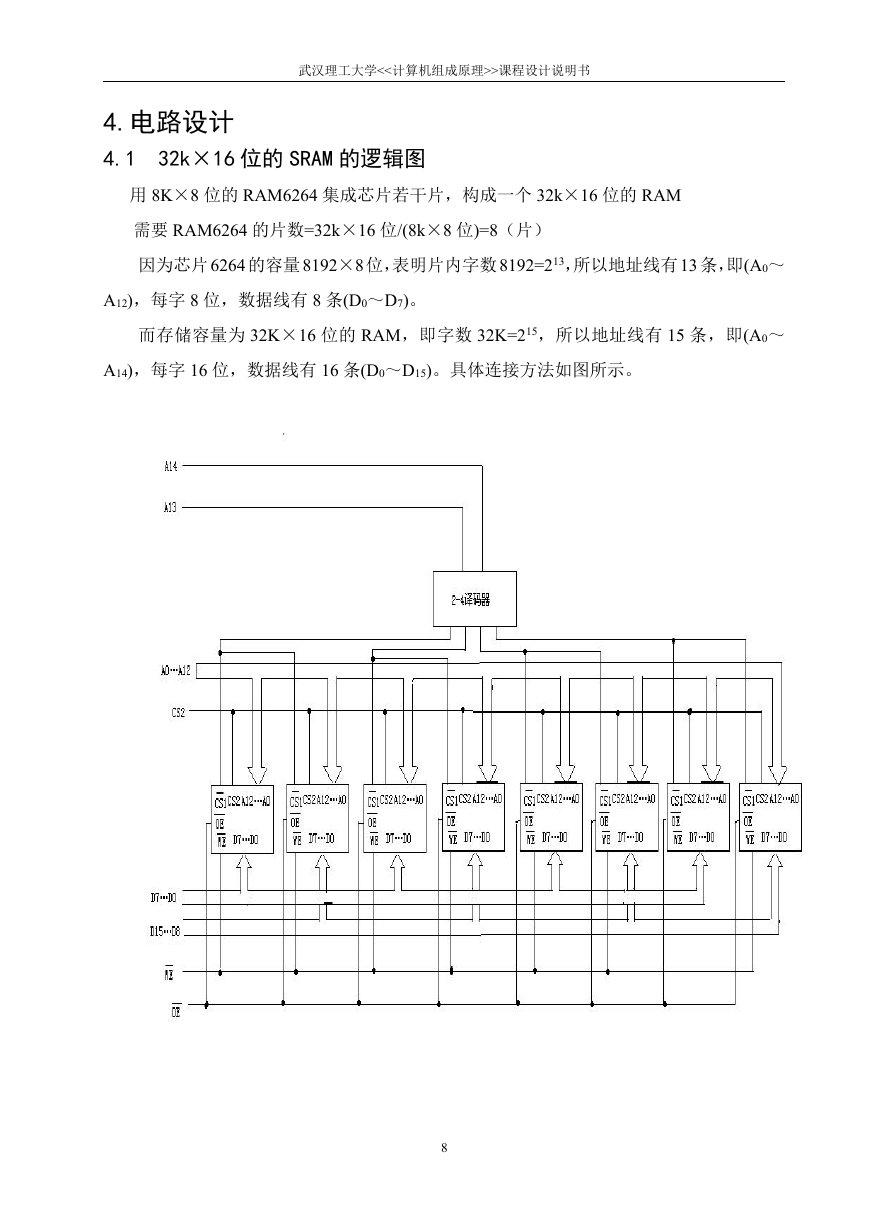

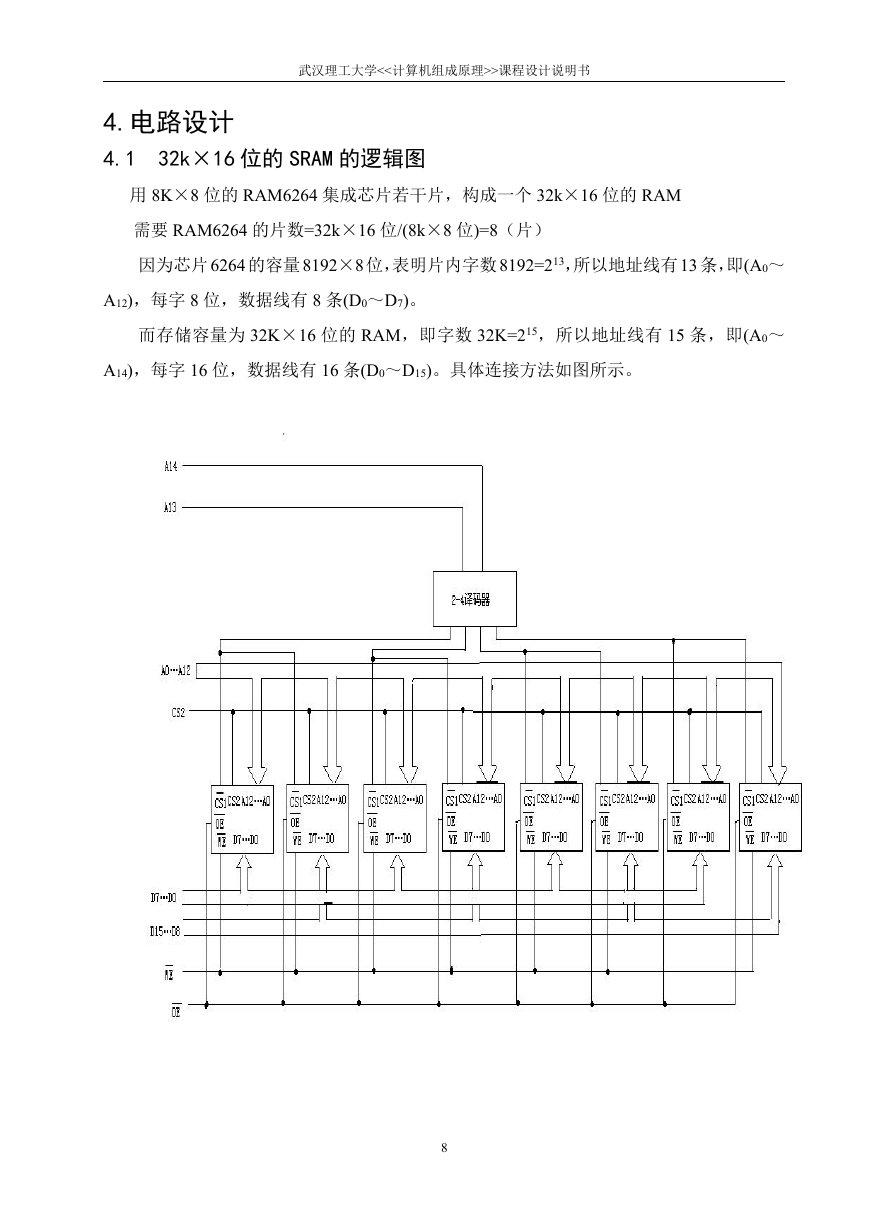

4.1 32k×16 位的 SRAM 的逻辑图

用 8K×8 位的 RAM6264 集成芯片若干片,构成一个 32k×16 位的 RAM

需要 RAM6264 的片数=32k×16 位/(8k×8 位)=8(片)

因为芯片6264 的容量8192×8 位,表明片内字数8192=213,所以地址线有13 条,即(A0~

A12),每字 8 位,数据线有 8 条(D0~D7)。

而存储容量为 32K×16 位的 RAM,即字数 32K=215,所以地址线有 15 条,即(A0~

A14),每字 16 位,数据线有 16 条(D0~D15)。具体连接方法如图所示。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc