长安大学 电子与控制工程学院 电子科学与技术系

实验八 VGA显示

一、实验目的:

通过对 VGA 接口的显示控制设计,理解 VGA 接口的时序工作原理,掌握

通过计数器产生时序控制信号的方法以及用 MEGEFUNCTION 制作锁相环的方

法。

二、实验条件:

1. 安装 WindowsXP 系统的 PC 机;

2. 安装 QuartusII6.0 EDA 软件;

3. GW48 型 SOPC 开发平台;

三、实验要求:

通过 VHDL 编程,在 VGA 显示器上实现竖形彩条的显示,显示模式为 640

×480 60Hz 刷新率。本实验需要使用 25MHz 的时钟,而开发平台中并没有这个

时钟资源,所以需要通过锁相环来实现,具体接口如下所示:

VGAPLL

inclk0

inclk0 f requency : 10.000 MHz

Operation Mode: Normal

c0

Clk Ratio Ph (dg) DC (%)

c0

50.00

0.00

5/2

inst1

Cy clone II

color

CLK

inst

HS

VS

RGB[2..0]

锁相环模块 VGAPLL:

inclk0:时钟输入端;

c0:时钟输出端(25MHz);

显示控制模块:

CLK:同步时钟输入端:

HS:行同步输出(低电平有效);

VS:帧同步输出(低电平有效);

RGB[2..0]:三色信号输出;

注:由于 RGB[2..0]输出的是数字量,所以只能够显示 8 种色彩。

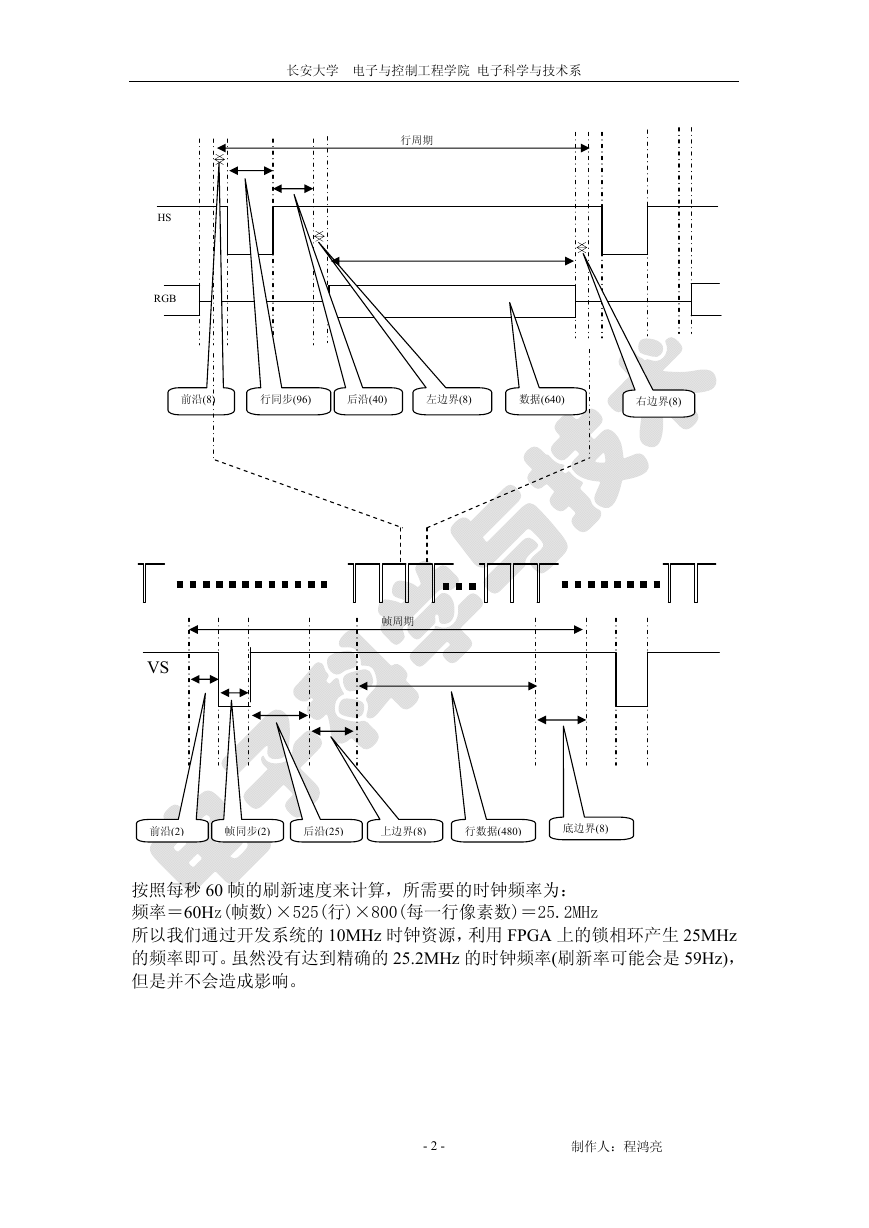

VGA 时序:

对 VGA 进行编程,必须要知道 VGA 的相关时序,下面列出 640×480 60Hz

显示模式的时序。

行同步信号(HS)

帧同步信号(VS)

时序名称

前沿

行同步

后沿

左边界

数据

右边界

总像素数

时钟数(像素数)

时序名称

8

96

40

8

640

8

800

前沿

帧同步

后沿

上边界

数据

底边界

总行数

行数

2

2

25

8

480

8

525

制作人:程鸿亮

- 1 -

�

长安大学 电子与控制工程学院 电子科学与技术系

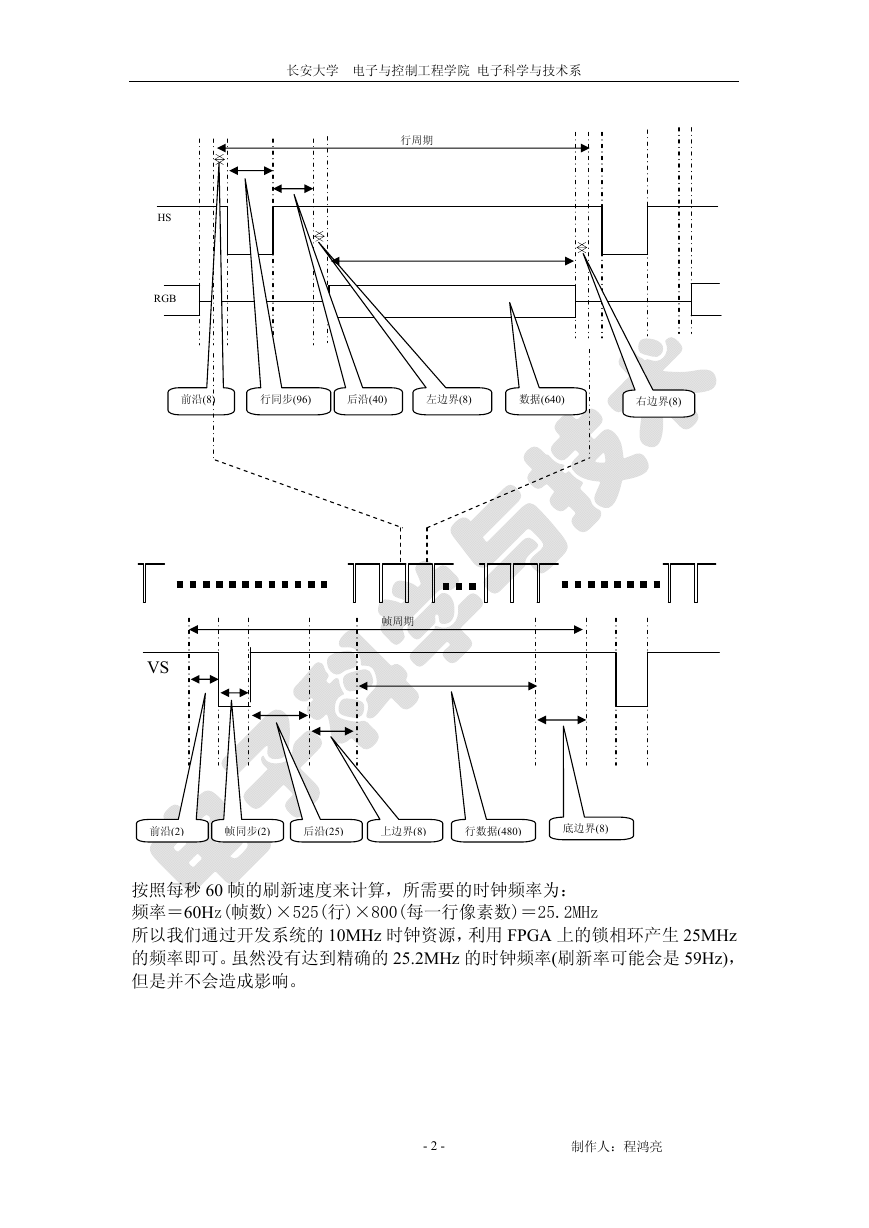

行周期

前沿(8)

后沿(40)

数据(640)

HS

RGB

左边界(8)

右边界(8)

行同步(96)

按照每秒 60 帧的刷新速度来计算,所需要的时钟频率为:

频率=60Hz(帧数)×525(行)×800(每一行像素数)=25.2MHz

所以我们通过开发系统的 10MHz 时钟资源,利用 FPGA 上的锁相环产生 25MHz

的频率即可。虽然没有达到精确的 25.2MHz 的时钟频率(刷新率可能会是 59Hz),

但是并不会造成影响。

行数据(480)

前沿(2)

帧同步(2)

后沿(25)

上边界(8)

底边界(8)

帧周期

VS

制作人:程鸿亮

- 2 -

�

长安大学 电子与控制工程学院 电子科学与技术系

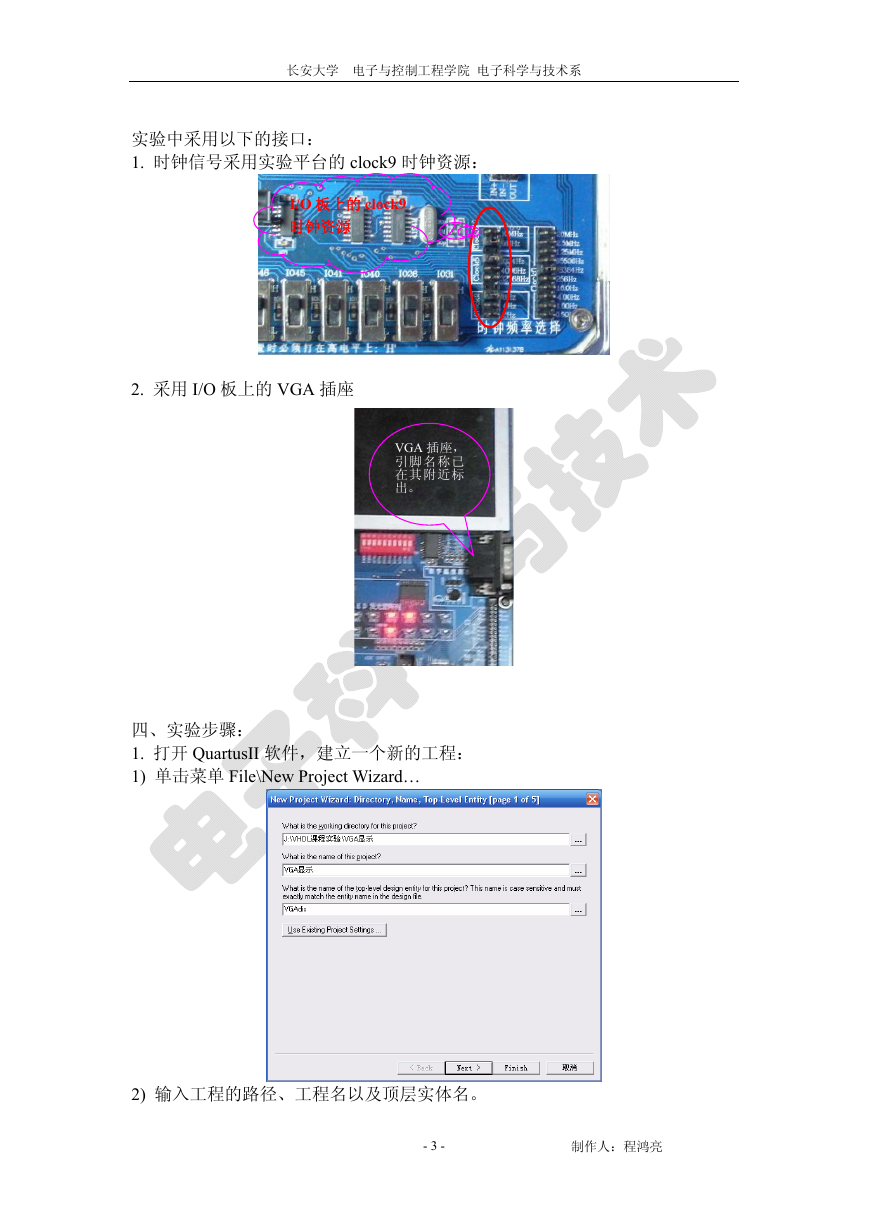

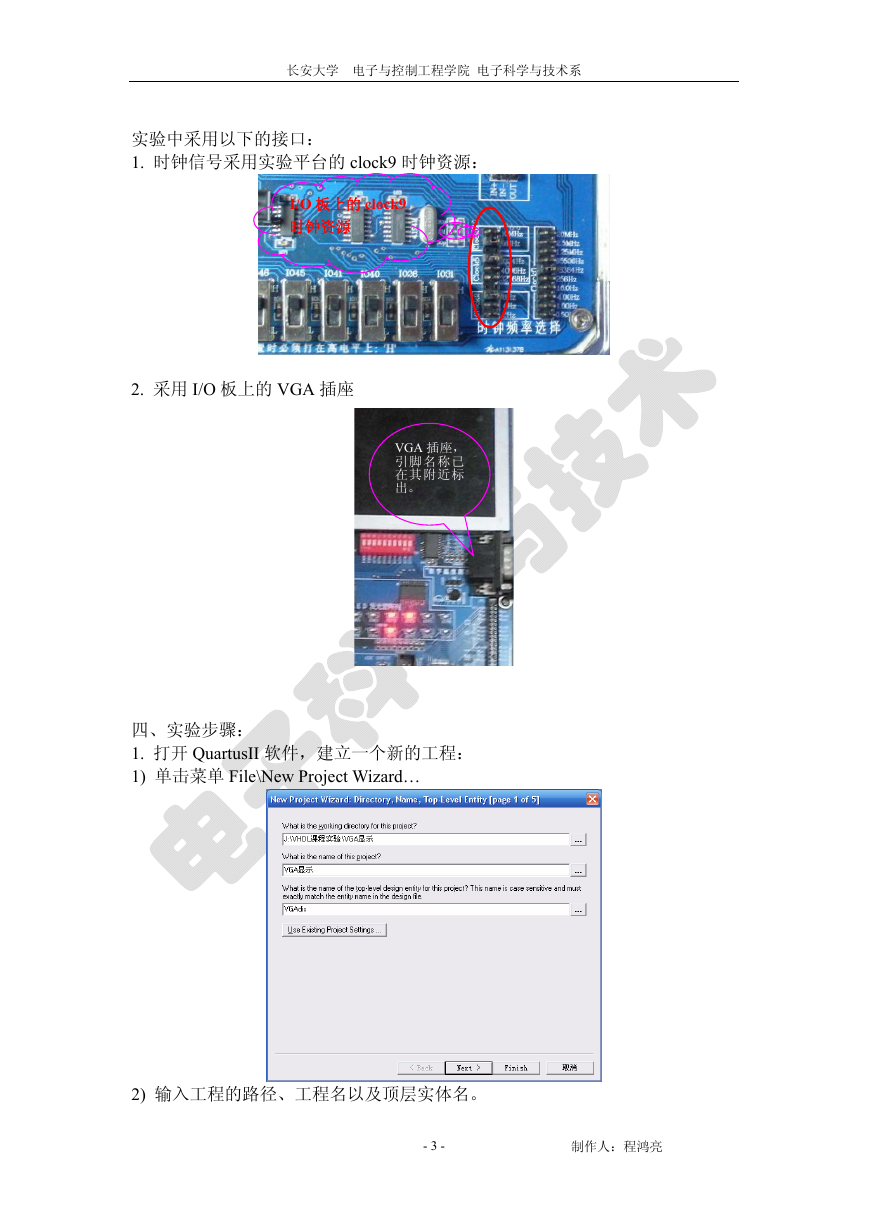

实验中采用以下的接口:

1. 时钟信号采用实验平台的 clock9 时钟资源:

I/O 板上的 clock9

时钟资源

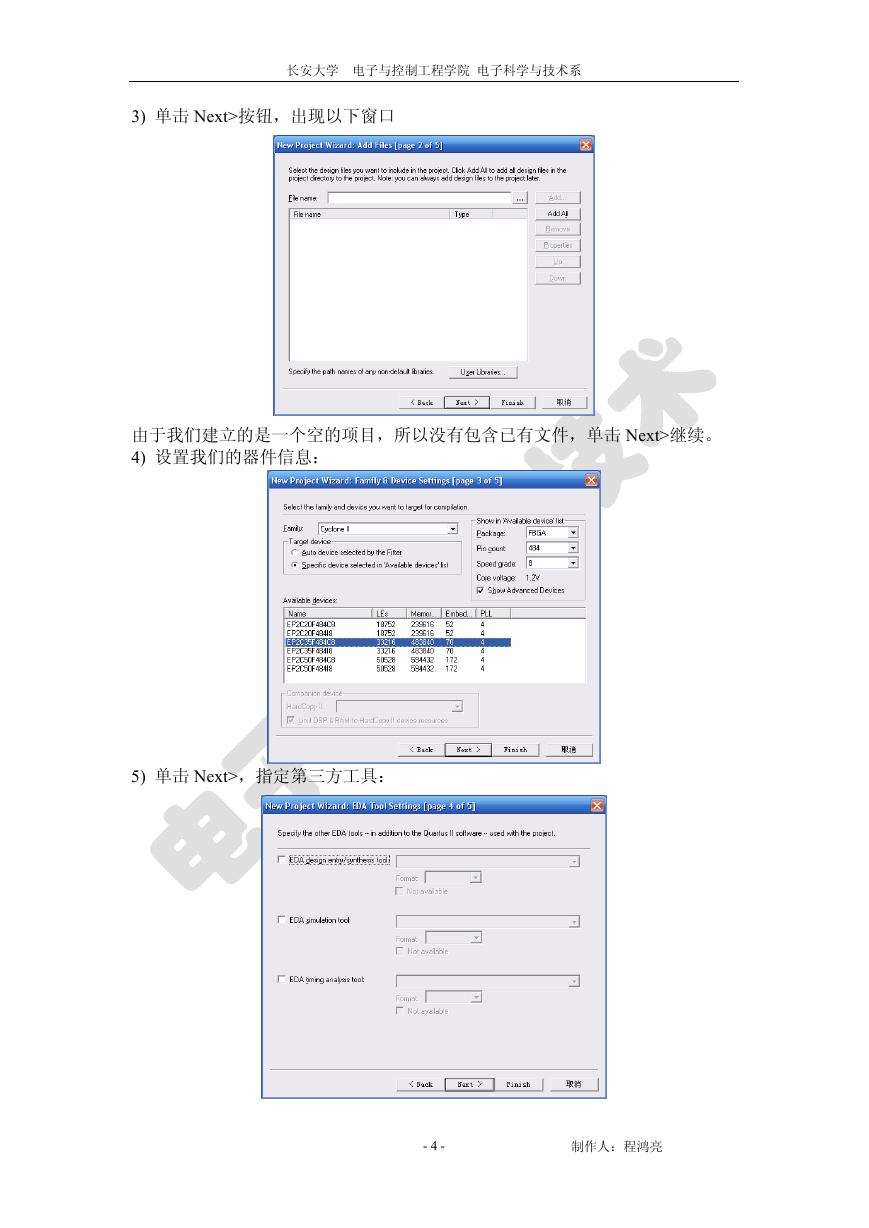

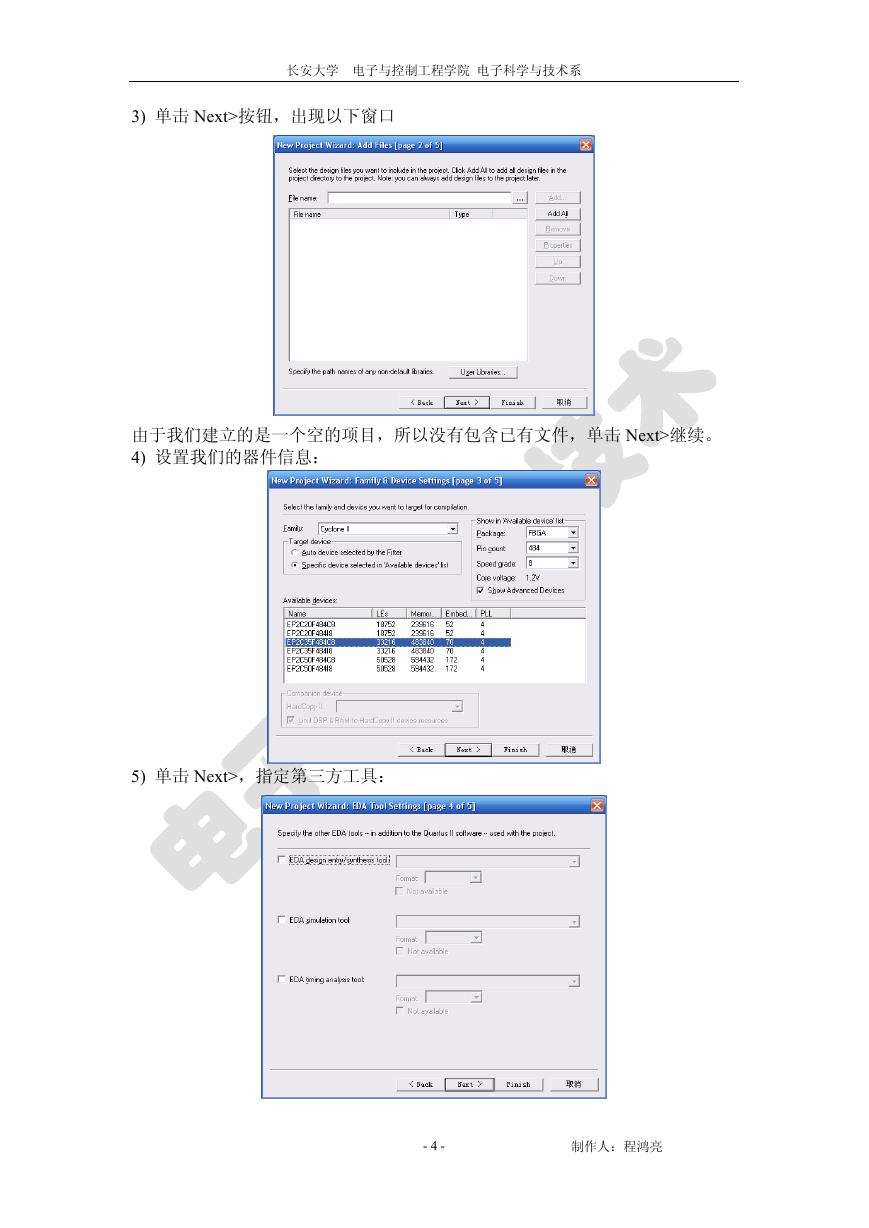

2. 采用 I/O 板上的 VGA 插座

VGA 插座,

引脚名称已

在其附近标

出。

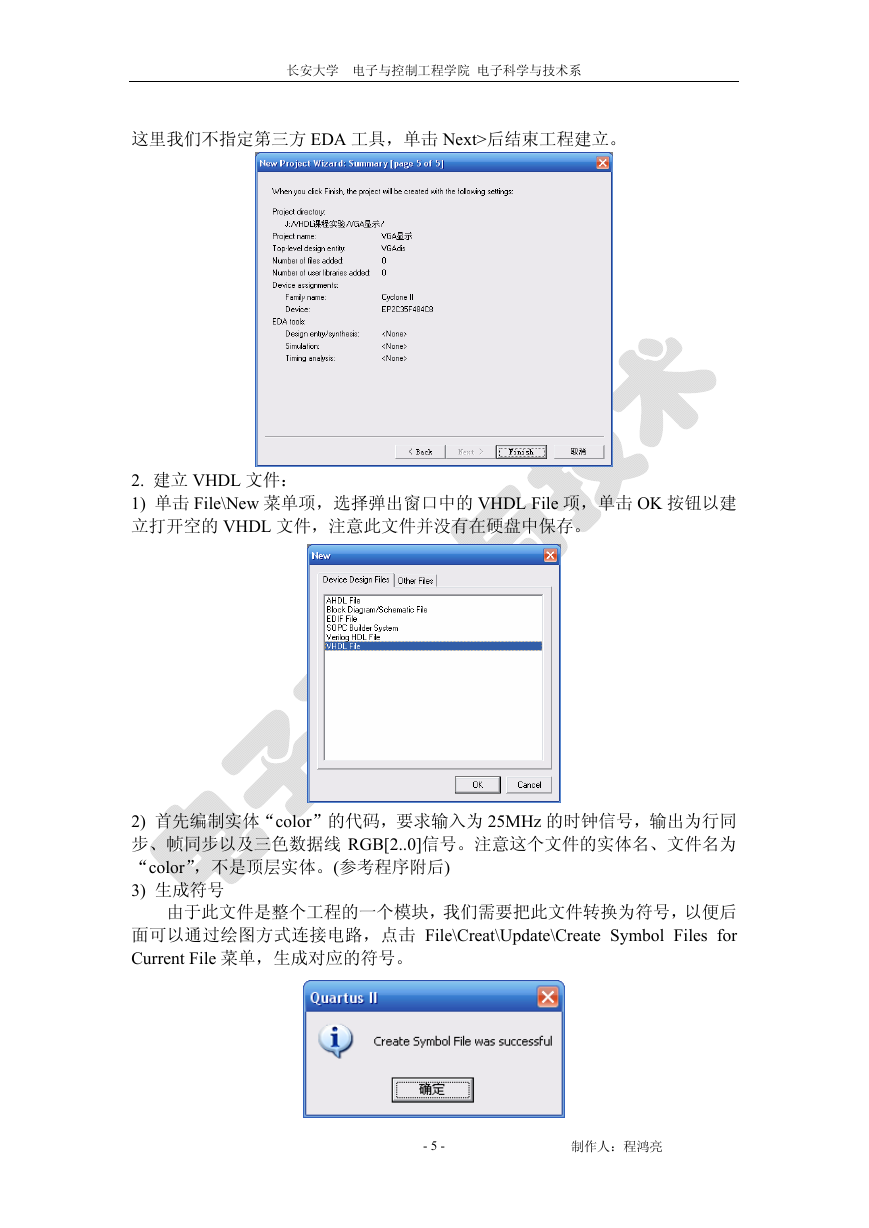

四、实验步骤:

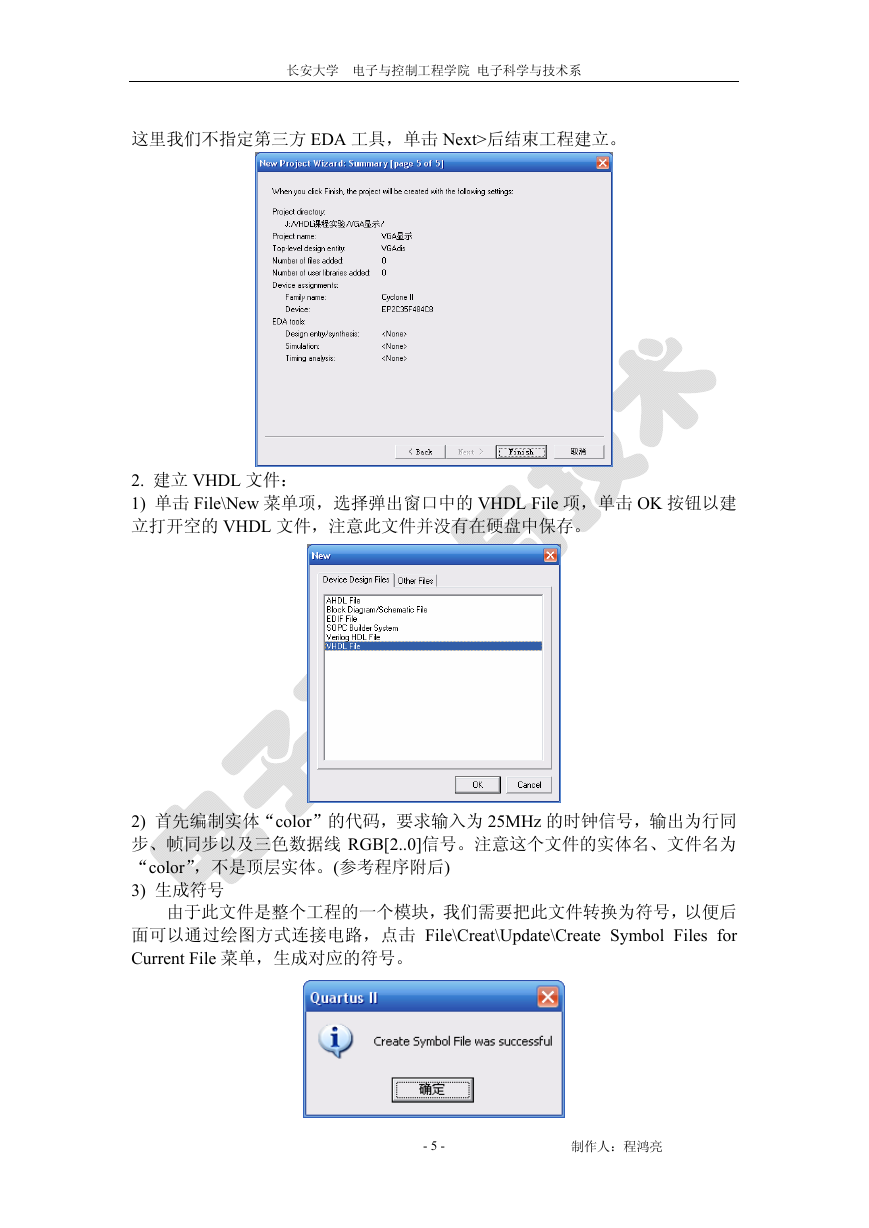

1. 打开 QuartusII 软件,建立一个新的工程:

1) 单击菜单 File\New Project Wizard…

2) 输入工程的路径、工程名以及顶层实体名。

制作人:程鸿亮

- 3 -

�

长安大学 电子与控制工程学院 电子科学与技术系

3) 单击 Next>按钮,出现以下窗口

由于我们建立的是一个空的项目,所以没有包含已有文件,单击 Next>继续。

4) 设置我们的器件信息:

5) 单击 Next>,指定第三方工具:

制作人:程鸿亮

- 4 -

�

长安大学 电子与控制工程学院 电子科学与技术系

这里我们不指定第三方 EDA 工具,单击 Next>后结束工程建立。

2. 建立 VHDL 文件:

1) 单击 File\New 菜单项,选择弹出窗口中的 VHDL File 项,单击 OK 按钮以建

立打开空的 VHDL 文件,注意此文件并没有在硬盘中保存。

2) 首先编制实体“color”的代码,要求输入为 25MHz 的时钟信号,输出为行同

步、帧同步以及三色数据线 RGB[2..0]信号。注意这个文件的实体名、文件名为

“color”,不是顶层实体。(参考程序附后)

3) 生成符号

由于此文件是整个工程的一个模块,我们需要把此文件转换为符号,以便后

面可以通过绘图方式连接电路,点击 File\Creat\Update\Create Symbol Files for

Current File 菜单,生成对应的符号。

制作人:程鸿亮

- 5 -

�

长安大学 电子与控制工程学院 电子科学与技术系

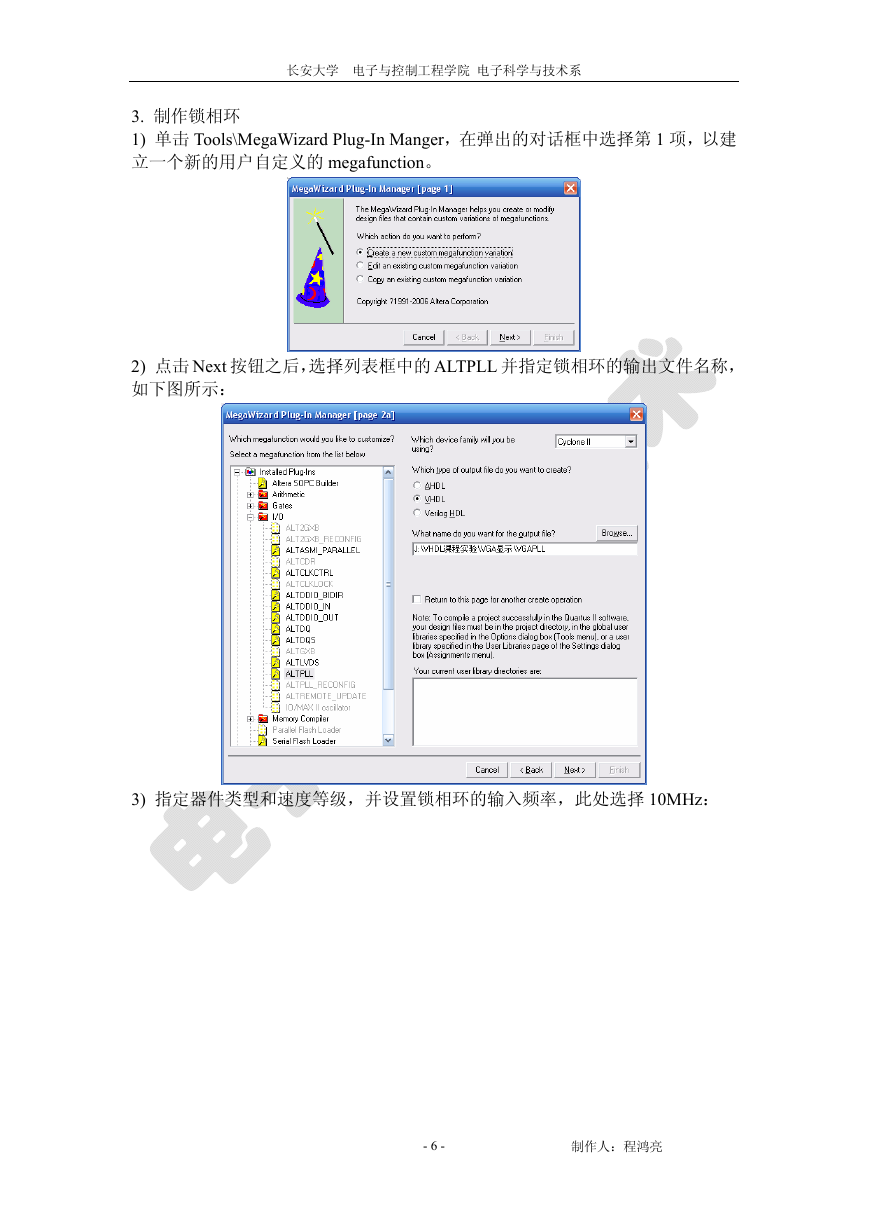

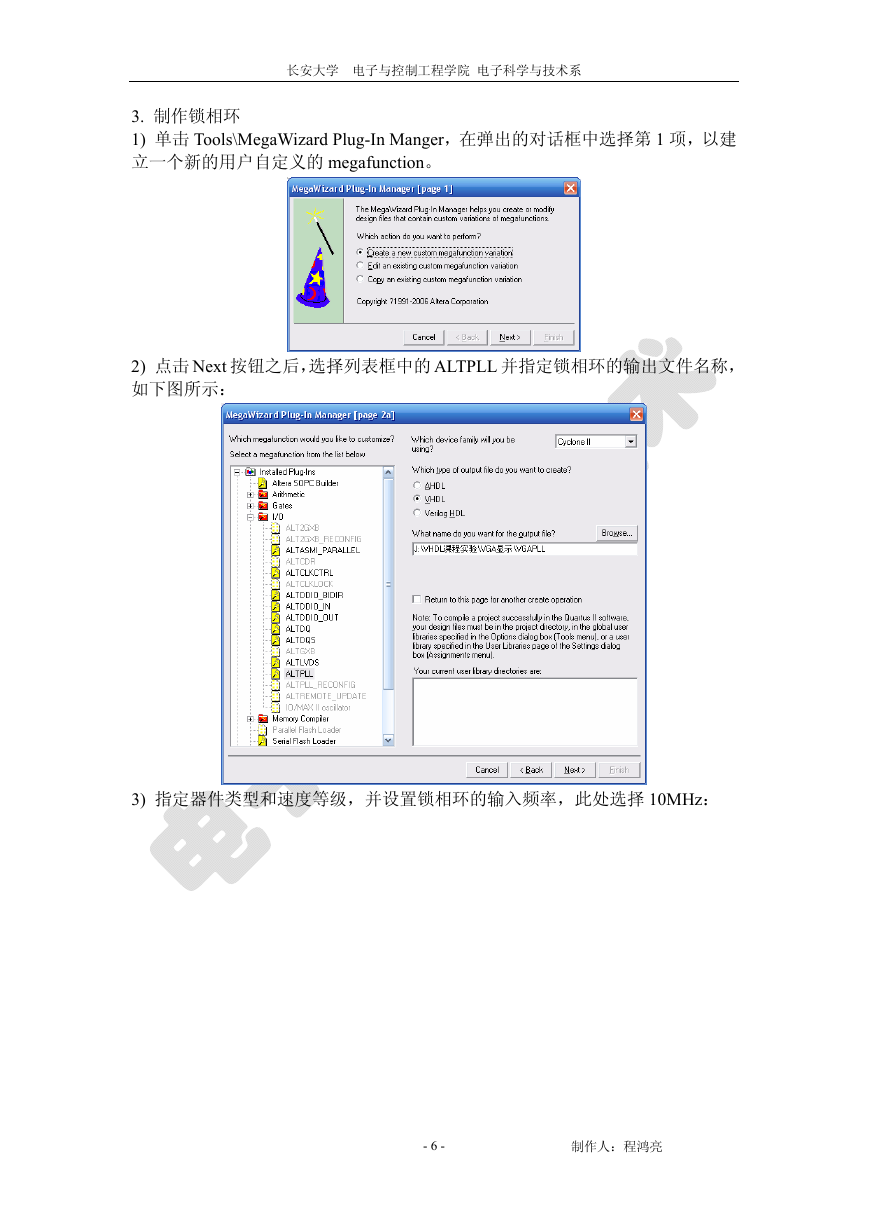

3. 制作锁相环

1) 单击 Tools\MegaWizard Plug-In Manger,在弹出的对话框中选择第 1 项,以建

立一个新的用户自定义的 megafunction。

2) 点击 Next 按钮之后,选择列表框中的 ALTPLL 并指定锁相环的输出文件名称,

如下图所示:

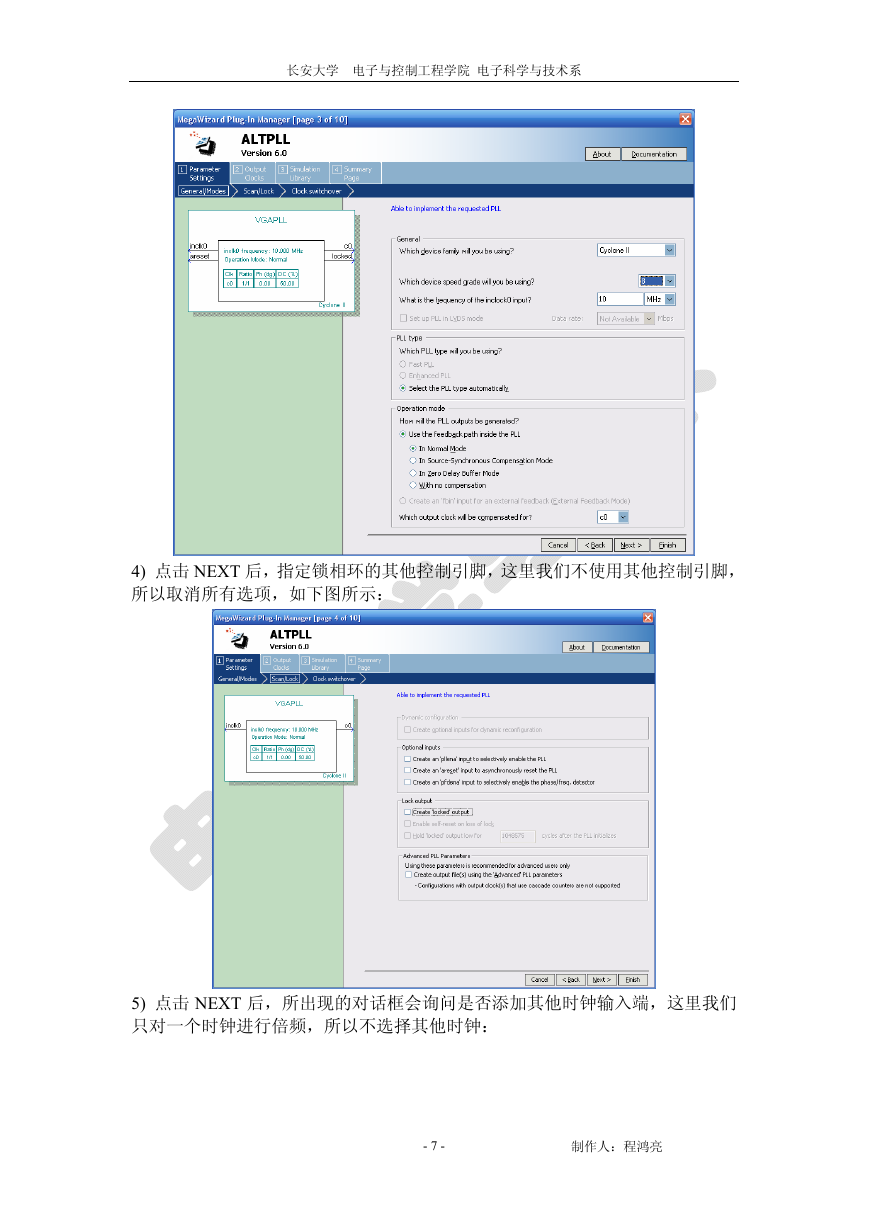

3) 指定器件类型和速度等级,并设置锁相环的输入频率,此处选择 10MHz:

制作人:程鸿亮

- 6 -

�

长安大学 电子与控制工程学院 电子科学与技术系

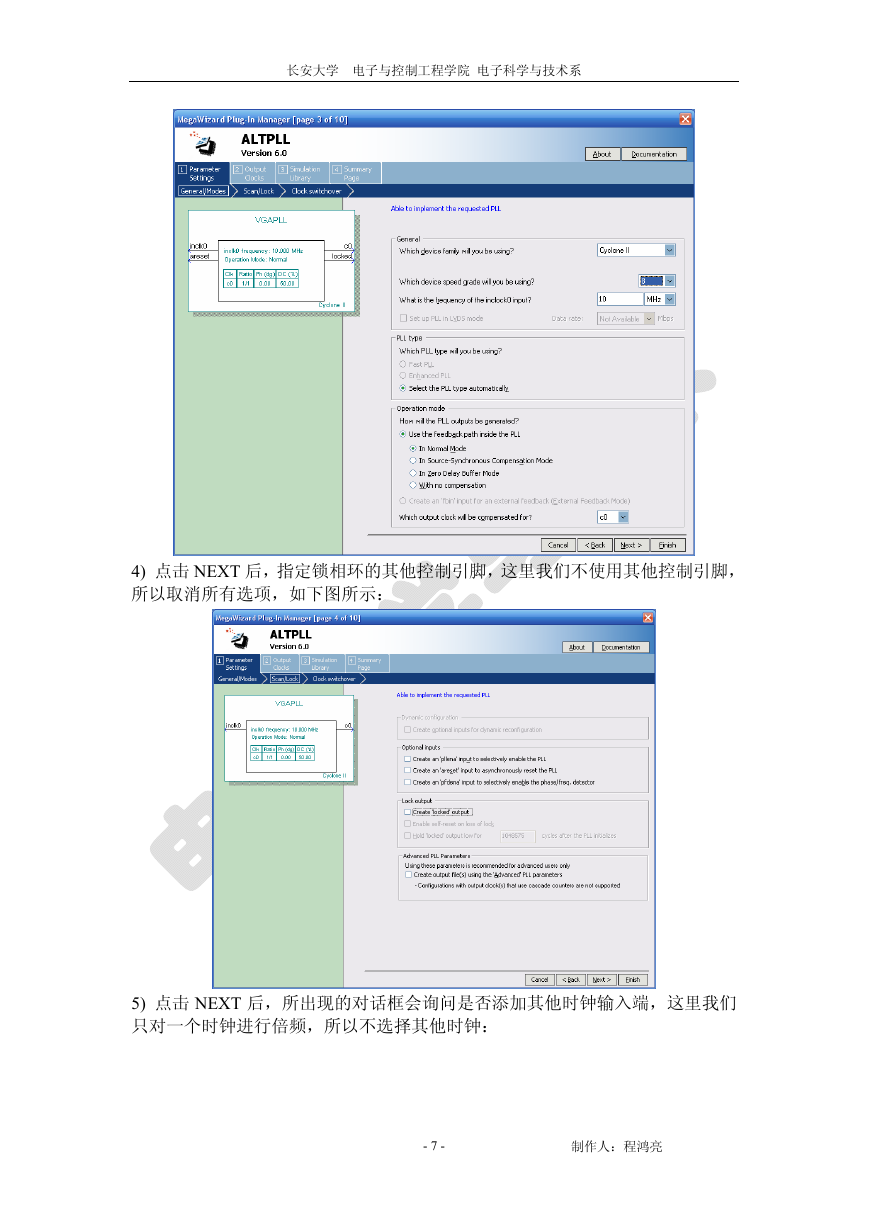

4) 点击 NEXT 后,指定锁相环的其他控制引脚,这里我们不使用其他控制引脚,

所以取消所有选项,如下图所示:

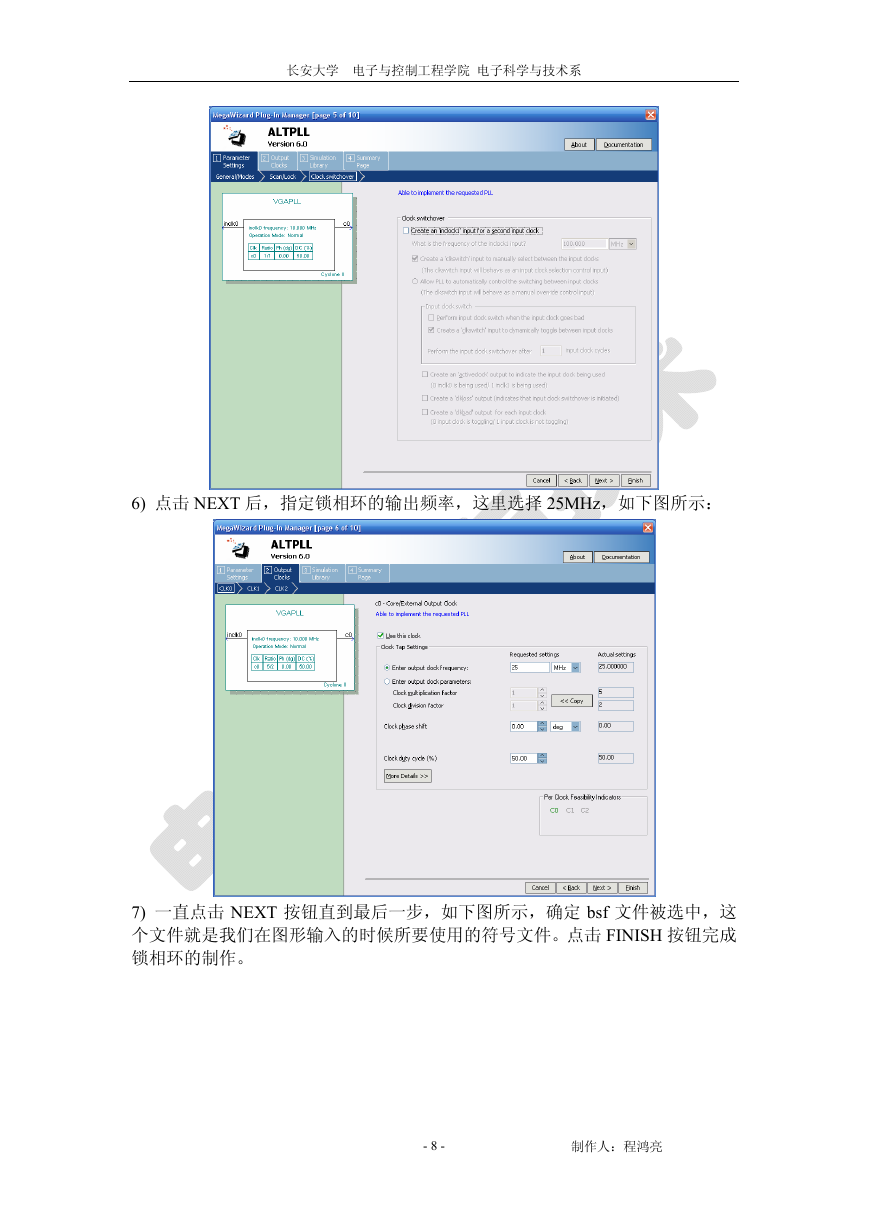

5) 点击 NEXT 后,所出现的对话框会询问是否添加其他时钟输入端,这里我们

只对一个时钟进行倍频,所以不选择其他时钟:

制作人:程鸿亮

- 7 -

�

长安大学 电子与控制工程学院 电子科学与技术系

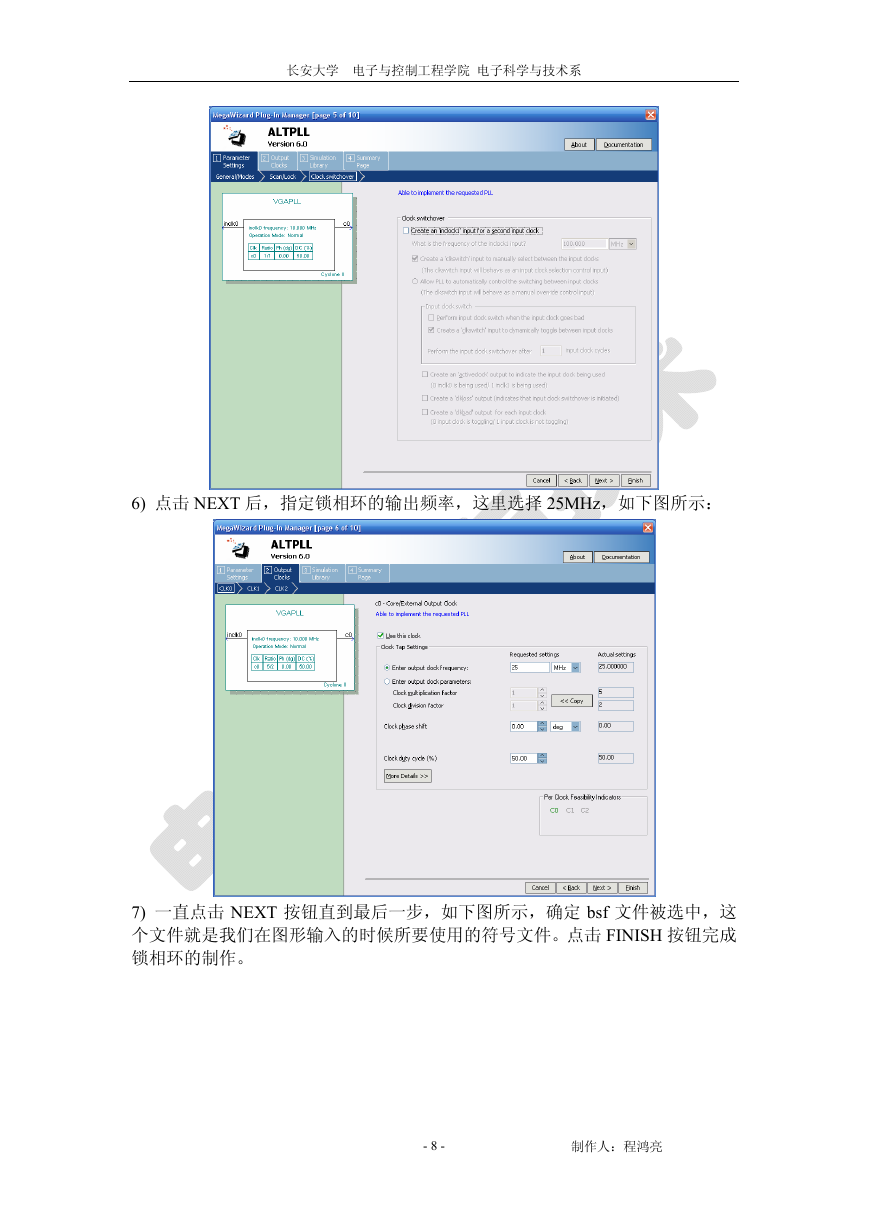

6) 点击 NEXT 后,指定锁相环的输出频率,这里选择 25MHz,如下图所示:

7) 一直点击 NEXT 按钮直到最后一步,如下图所示,确定 bsf 文件被选中,这

个文件就是我们在图形输入的时候所要使用的符号文件。点击 FINISH 按钮完成

锁相环的制作。

制作人:程鸿亮

- 8 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc