概述

1.0 概述

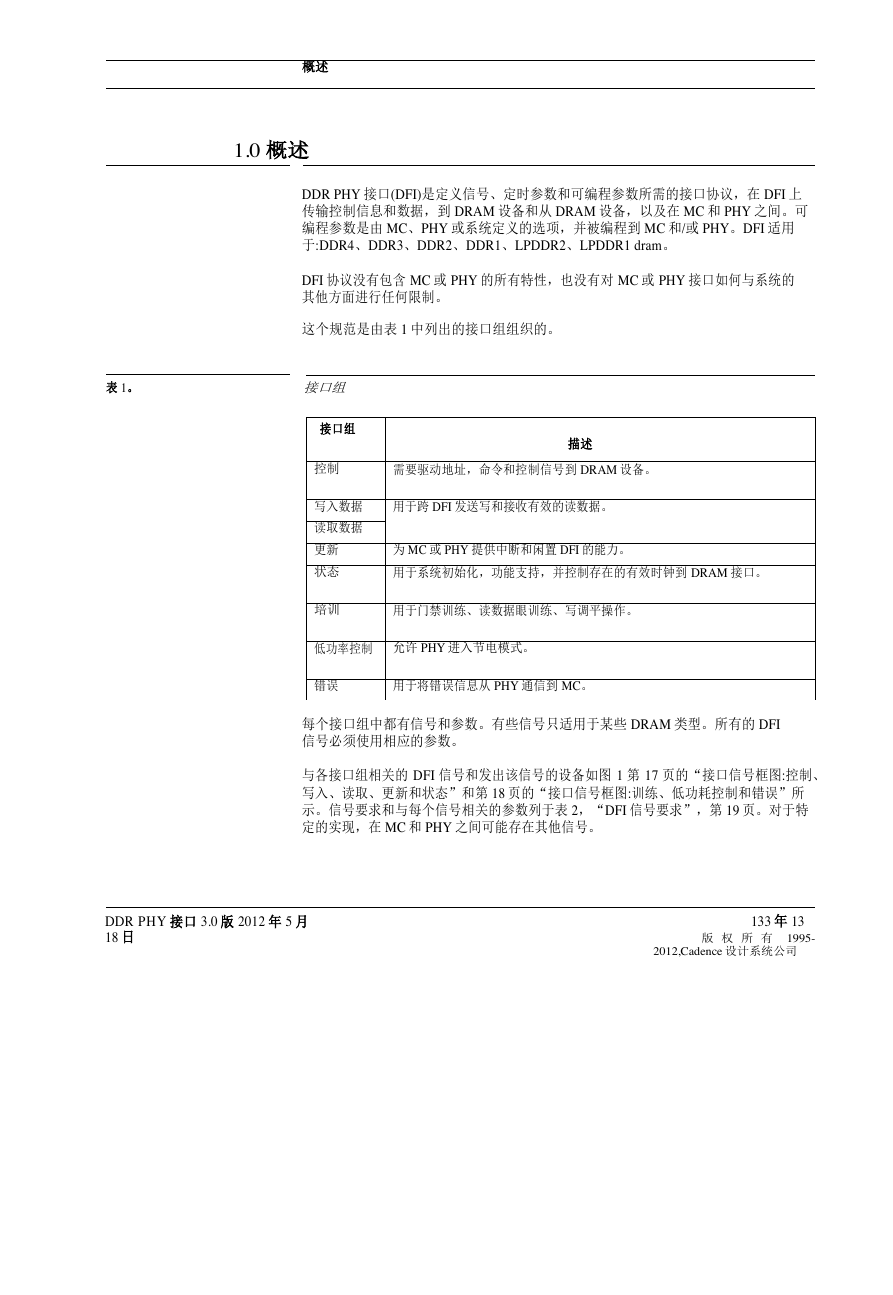

DDR PHY 接口(DFI)是定义信号、定时参数和可编程参数所需的接口协议,在 DFI 上

传输控制信息和数据,到 DRAM 设备和从 DRAM 设备,以及在 MC 和 PHY 之间。可

编程参数是由 MC、PHY 或系统定义的选项,并被编程到 MC 和/或 PHY。DFI 适用

于:DDR4、DDR3、DDR2、DDR1、LPDDR2、LPDDR1 dram。

DFI 协议没有包含 MC 或 PHY 的所有特性,也没有对 MC 或 PHY 接口如何与系统的

其他方面进行任何限制。

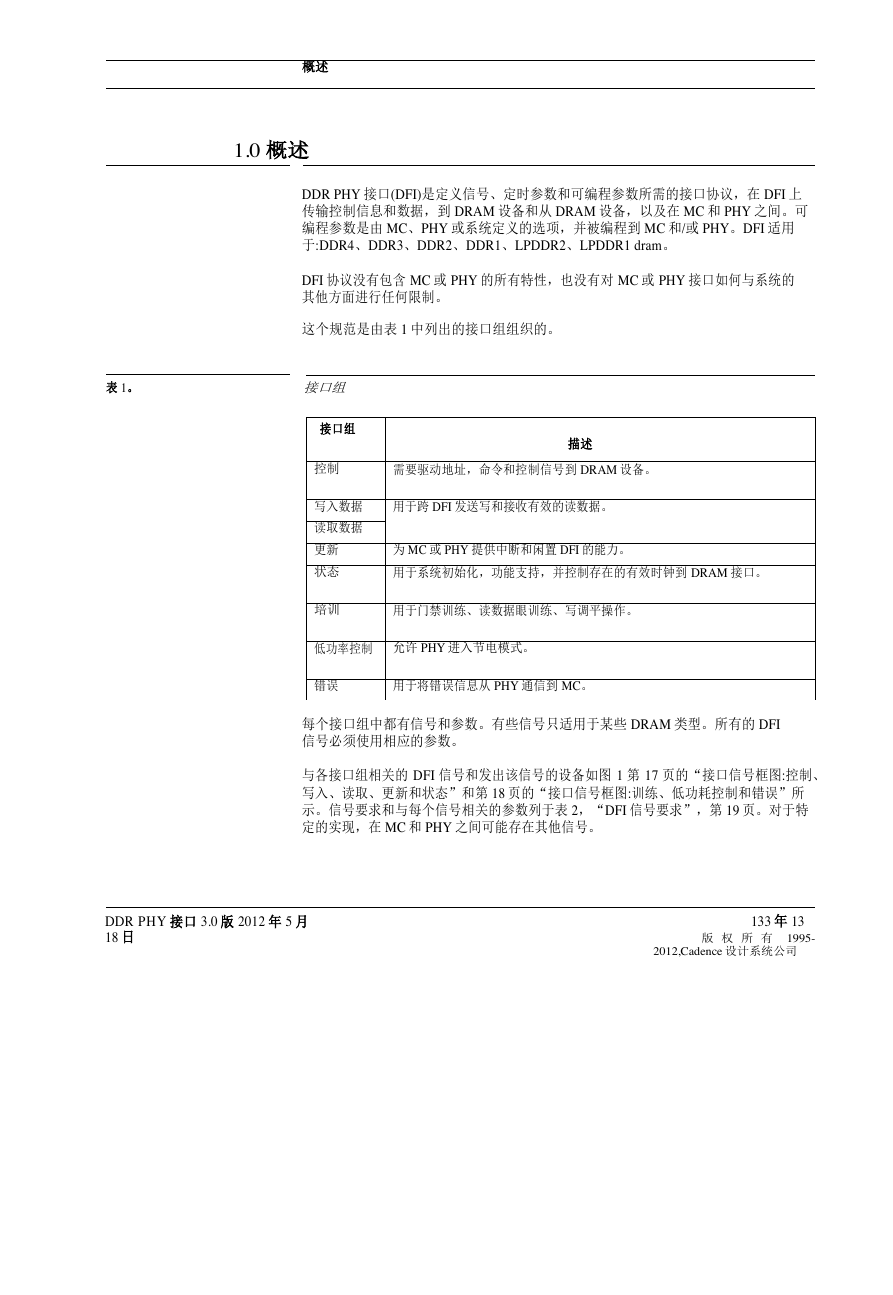

这个规范是由表 1 中列出的接口组组织的。

表 1。

接口组

接口组

描述

控制

需要驱动地址,命令和控制信号到 DRAM 设备。

写入数据

读取数据

更新

状态

用于跨 DFI 发送写和接收有效的读数据。

为 MC 或 PHY 提供中断和闲置 DFI 的能力。

用于系统初始化,功能支持,并控制存在的有效时钟到 DRAM 接口。

培训

用于门禁训练、读数据眼训练、写调平操作。

低功率控制 允许 PHY 进入节电模式。

错误

用于将错误信息从 PHY 通信到 MC。

每个接口组中都有信号和参数。有些信号只适用于某些 DRAM 类型。所有的 DFI

信号必须使用相应的参数。

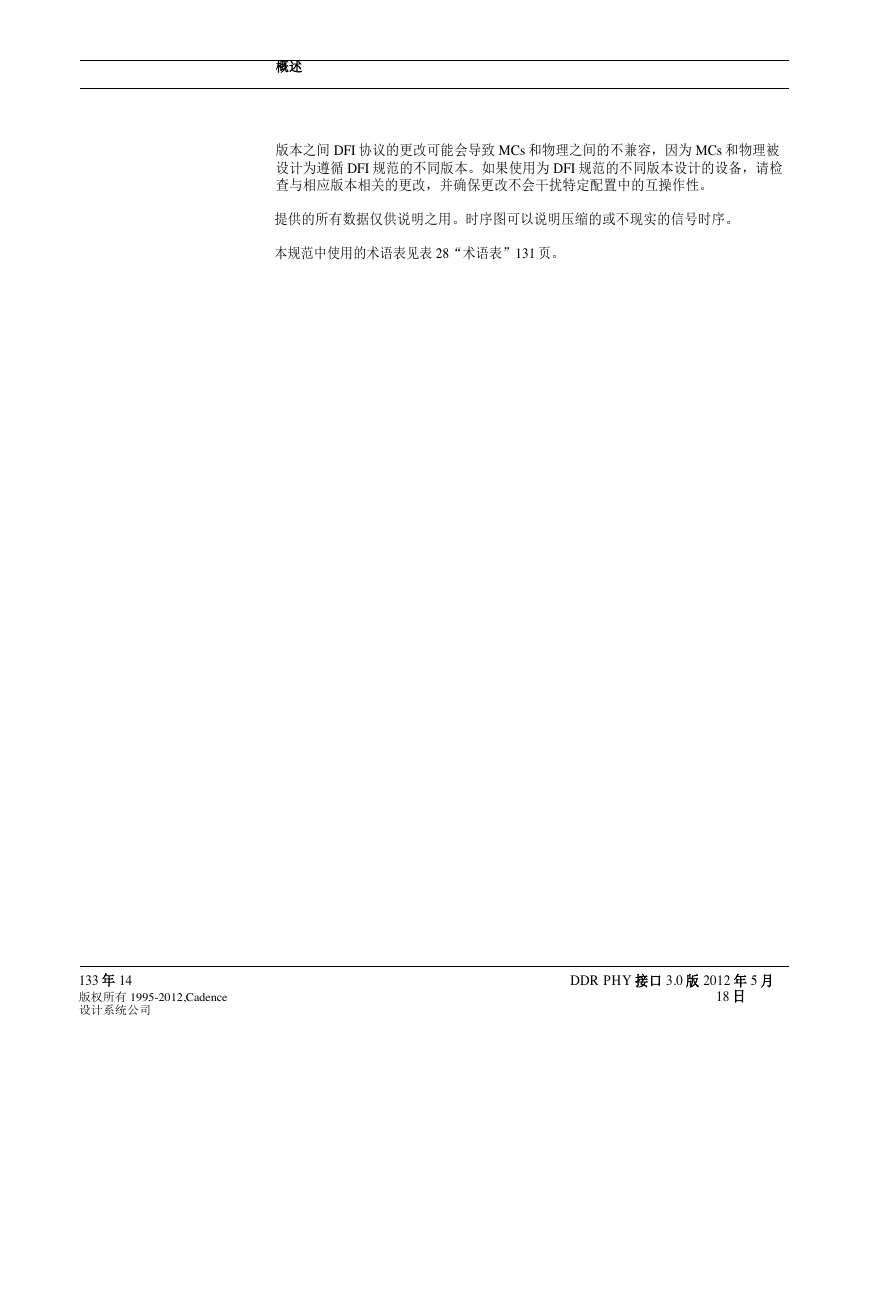

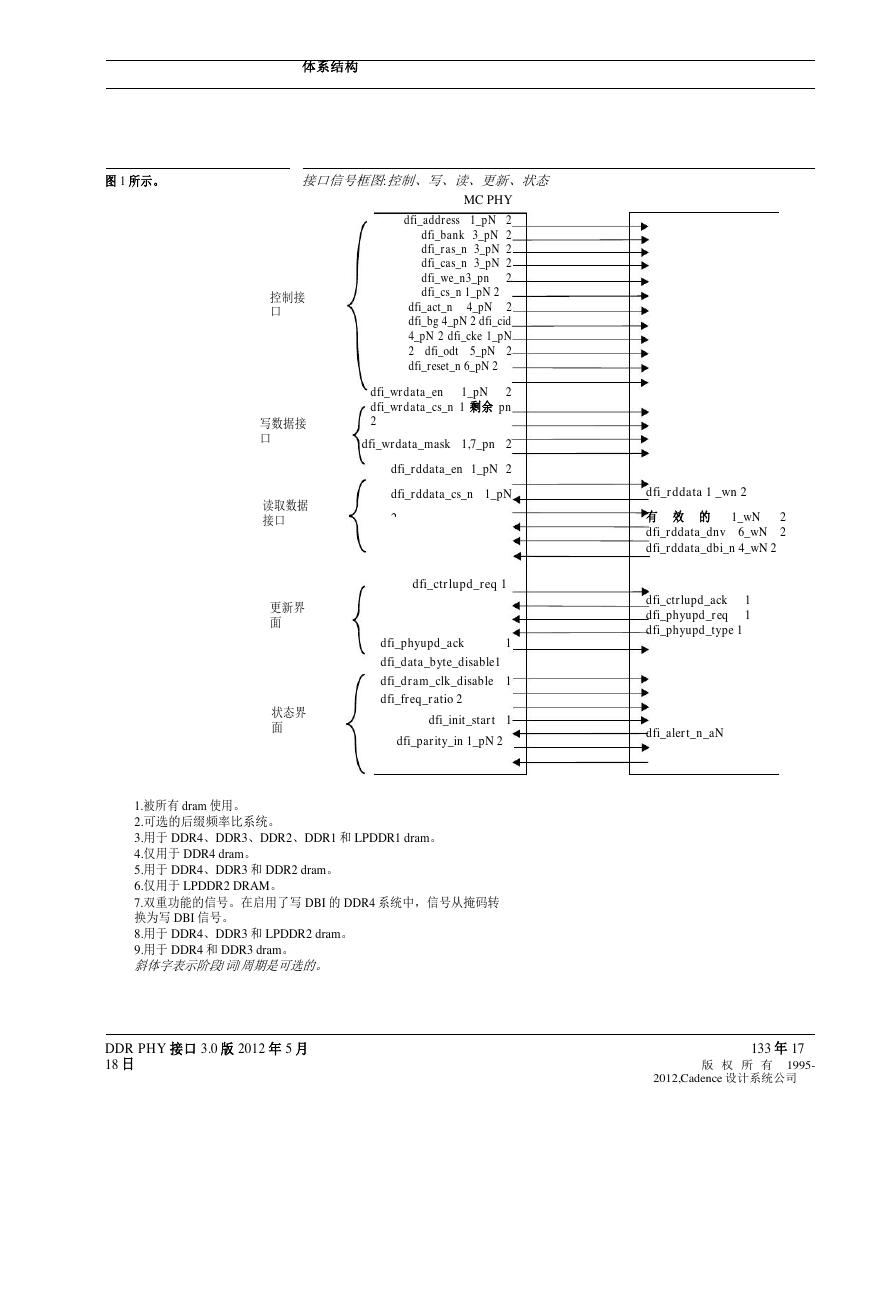

与各接口组相关的 DFI 信号和发出该信号的设备如图 1 第 17 页的“接口信号框图:控制、

写入、读取、更新和状态”和第 18 页的“接口信号框图:训练、低功耗控制和错误”所

示。信号要求和与每个信号相关的参数列于表 2,“DFI 信号要求”,第 19 页。对于特

定的实现,在 MC 和 PHY 之间可能存在其他信号。

DDR PHY 接口 3.0 版 2012 年 5 月

18 日

133 年 13

版 权 所 有 1995-

2012,Cadence 设计系统公司

�

概述

版本之间 DFI 协议的更改可能会导致 MCs 和物理之间的不兼容,因为 MCs 和物理被

设计为遵循 DFI 规范的不同版本。如果使用为 DFI 规范的不同版本设计的设备,请检

查与相应版本相关的更改,并确保更改不会干扰特定配置中的互操作性。

提供的所有数据仅供说明之用。时序图可以说明压缩的或不现实的信号时序。

本规范中使用的术语表见表 28“术语表”131 页。

133 年 14

版权所有 1995-2012,Cadence

设计系统公司

DDR PHY 接口 3.0 版 2012 年 5 月

18 日

�

体系结构

2.0 体系结构

DFI 规范需要一个 DFI 时钟和 DFI 定义的信号,必须由寄存器直接驱动到 DFI 时钟的

上升边缘。没有规则规定 DFI 时钟的来源,也没有限制如何 DFI 定义的信号被接收。

对于 MC 和 PHY 之间的 DFI 互操作性,请确保以下方面的兼容性:

•信号宽度

•连接时间

•时间参数

•频率比

•函数

在目标频率的 MC 和 PHY 之间的互连时间兼容性是由信号驱动的输出时间的规格和在

每个设备上 DFI 接收这些信号的设置和保持要求决定的,由设备定义。

DFI 规范没有规定每个设备必须支持的绝对延迟或固定的值范围。某些 DFI 定时参数

可以指定为固定值、最大值或基于系统中的其他值的常量。

当命令在 DFI 总线上执行时,DFI 定时参数必须保持不变;然而,如果必要,DFI 定时

参数可能在频率变化期间或当总线处于空闲状态被改变。有关定时的更多信息,请参

阅第 127 页 5.0 节“信号定时”。

DFI 规范根据对特定 DRAM 设备、可选特性和频率比率的支持来标识与特定实现相关

的 DFI 信号。有关哪些信号与特定实现相关的更多信息,请参阅第 19 页表 2“DFI 信

号要求”。

该 MC 和 PHY 必须操作在一个公共频率比。对于匹配的频率系统,DFI 写入数据总线

的宽度通常是 DRAM 数据总线宽度的两倍。对于频率比系统,DFI 写数据总线宽度将

乘成比例的频率比,以允许 MC 发送所有 DRAM 所需的写数据到 PHY 在一个单一的

DFI 时钟周期。写入数据必须以升序排列的 DFI 数据字交付。

•在一个匹配的频率系统中,MC 和 PHY 以 1:1 的比例运行。

•在频率比系统中,MC 和 PHY 以 1:2 或 1:4 的公共频率比运行;物理层必须能够接受任

何和所有阶段的命令。频率比取决于 MC 和 PHY 的参考时钟的关系。

以“_pN”为后缀,相位数为 N 的特定相位信号(例如:

dfi_wrdata_pN),替换控制匹配的频率信号,写入数据,

DDR PHY 接口 3.0 版 2012 年 5 月

18 日

133 年 15

版 权 所 有 1995-

2012,Cadence 设计系统公司

�

体系结构

读取数据和状态接口信号。特定相位信号允许 MC 在一个时钟周期内驱动多个命

令。

以“_wN”为后缀的数据字专用信号,DFI 数据字数 N(例如,dfi_rddata_wN),替

换读取接口匹配的频率信号,以区分 DRAM 字如何在 DFI 总线上传输。以“aN”

为后缀的可变脉冲宽度特定信号,与 PHY 时钟周期 N(例如,dfi_alert_n_aN),在

从内存系统向 PHY 传输错误信号时,替换状态接口的匹配频率信号以保持脉冲宽

度。

对于所有信号类型,后缀为相位 0/数据字 0/时钟周期 0 是可选的。有关频率比率

的更多信息,请参阅第 4.8 节“跨 DFI 的频率比率”。

可选协议处理数据总线反转(DBI),循环冗余检查(CRC),系统频率改变,命令/地址

(CA)奇偶校验,低功耗,和错误接口。有关可选协议的更多信息,请参阅第 64 页第

4.3 节“数据总线反转”,第 4.4.3 节“循环冗余校验”,第 73 页,

第 109 页第 4.9 节“频率变化”,第 4.10 节“奇偶校验”,第 111 页第 4.12 节“低功

率控制握手”,第 124 页,第 4.13 节“错误信号”,第 126 页。

DRAM 类型和系统配置确定系统可用的培训类型;一个系统可以也可以不使用每种类型

的培训。如果支持培训,系统可以使用 DFI 培训或支持不同的培训方法。

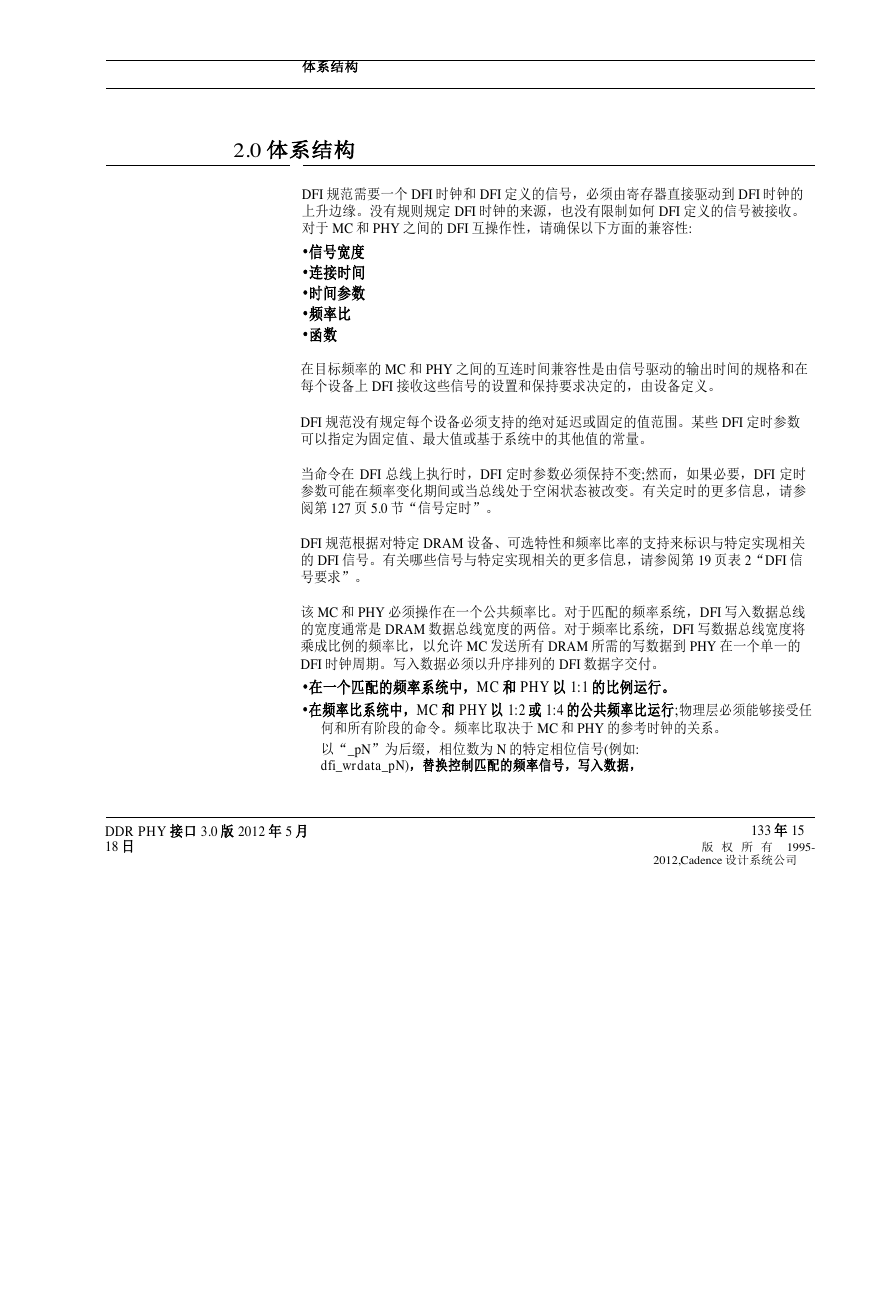

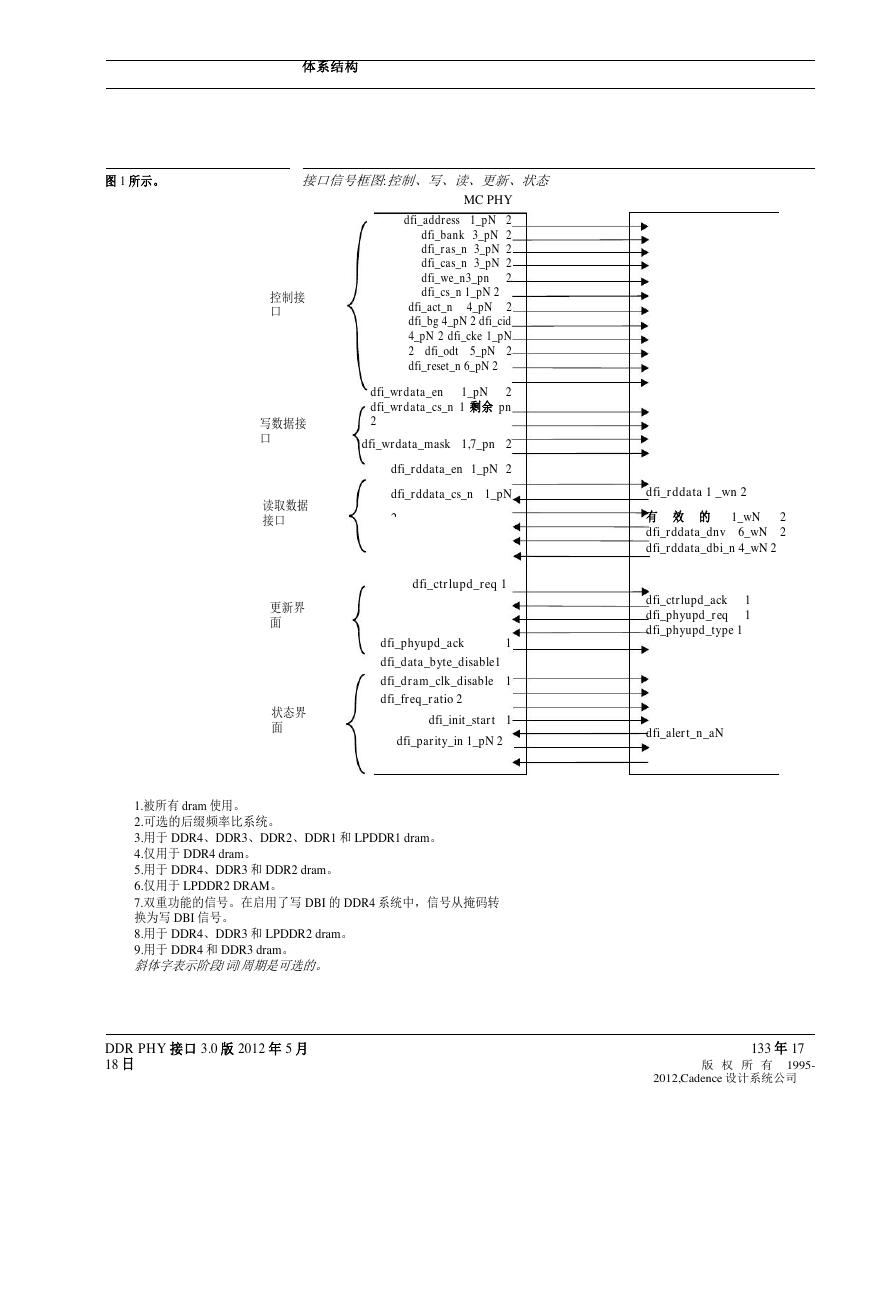

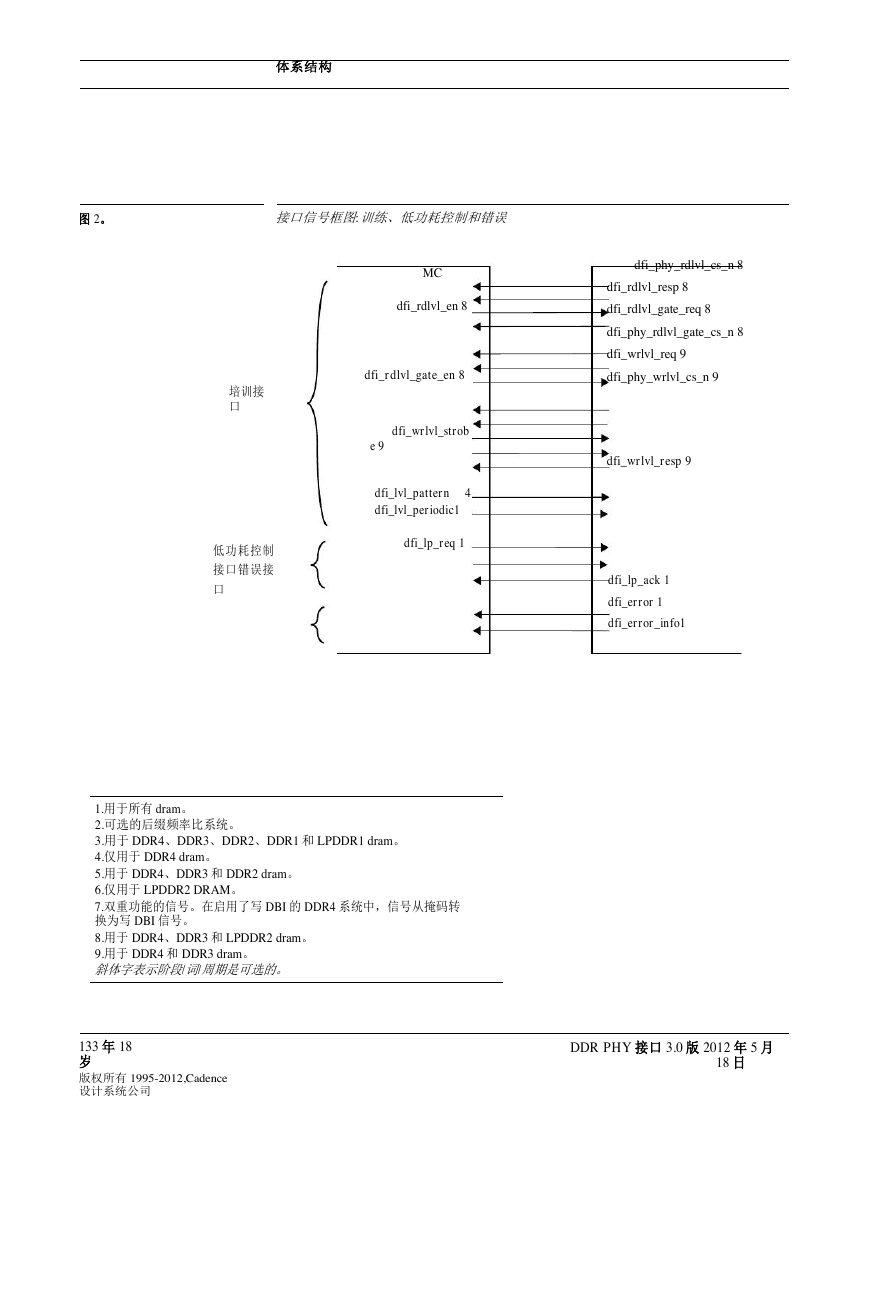

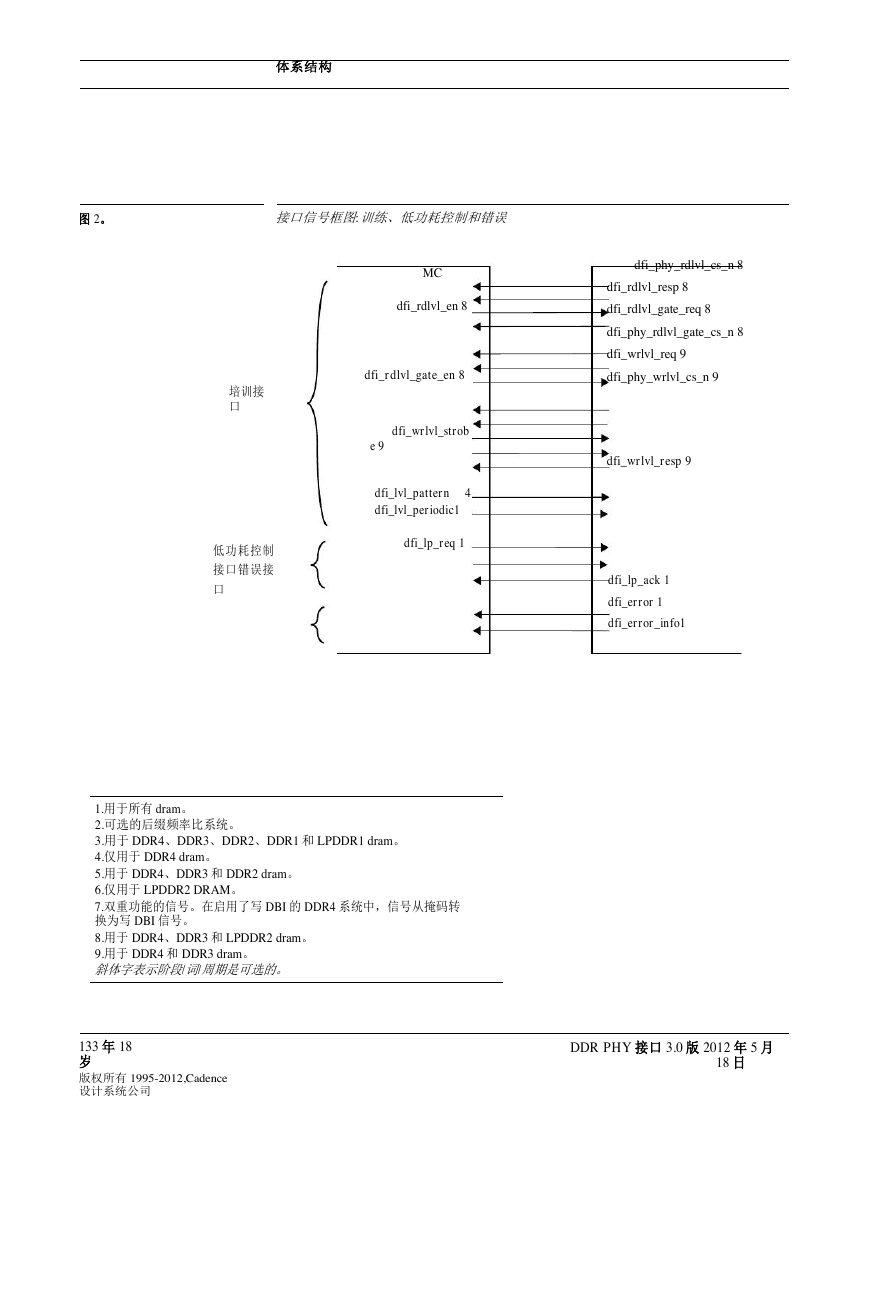

与控制/写入数据/读取数据/更新/状态接口组相关的 DFI 信号,以及发出信号的设备,

在图 1 第 17 页的“接口信号框图:控制、写入、读取、更新和状态”中功能列出。在第

18 页的图 2“接口信号框图:训练、低功率控制和错误”中,每个接口组中列出了与训

练/低功率/错误接口组相关的 DFI 信号和发出信号的设备。

133 年 16

日

版权所有 1995-2012,Cadence

设计系统公司

DDR PHY 接口 3.0 版 2012 年 5 月

18 日

�

体系结构

图 1 所示。

接口信号框图:控制、写、读、更新、状态

MC PHY

dfi_address 1_pN 2

dfi_bank 3_pN 2

dfi_ras_n 3_pN 2

dfi_cas_n 3_pN 2

dfi_we_n3_pn

2

dfi_cs_n 1_pN 2

4_pN

dfi_act_n

2

dfi_bg 4_pN 2 dfi_cid

4_pN 2 dfi_cke 1_pN

2 dfi_odt 5_pN 2

dfi_reset_n 6_pN 2

dfi_wrdata_en

2

dfi_wrdata_cs_n 1 剩余 pn

2

1_pN

dfi_wrdata_mask 1,7_pn 2

dfi_rddata_en 1_pN 2

dfi_rddata_cs_n 1_pN

2

dfi_ctrlupd_req 1

dfi_phyupd_ack

1

dfi_data_byte_disable1

dfi_dram_clk_disable 1

dfi_freq_ratio 2

dfi_init_start 1

dfi_parity_in 1_pN 2

控制接

口

写数据接

口

读取数据

接口

更新界

面

状态界

面

1.被所有 dram 使用。

2.可选的后缀频率比系统。

3.用于 DDR4、DDR3、DDR2、DDR1 和 LPDDR1 dram。

4.仅用于 DDR4 dram。

5.用于 DDR4、DDR3 和 DDR2 dram。

6.仅用于 LPDDR2 DRAM。

7.双重功能的信号。在启用了写 DBI 的 DDR4 系统中,信号从掩码转

换为写 DBI 信号。

8.用于 DDR4、DDR3 和 LPDDR2 dram。

9.用于 DDR4 和 DDR3 dram。

斜体字表示阶段/词/周期是可选的。

dfi_rddata 1 _wn 2

有 效 的 1_wN

2

dfi_rddata_dnv 6_wN 2

dfi_rddata_dbi_n 4_wN 2

dfi_ctrlupd_ack

1

dfi_phyupd_req

1

dfi_phyupd_type 1

dfi_alert_n_aN

DDR PHY 接口 3.0 版 2012 年 5 月

18 日

133 年 17

版 权 所 有 1995-

2012,Cadence 设计系统公司

�

体系结构

图 2。

接口信号框图:训练、低功耗控制和错误

MC

dfi_rdlvl_en 8

dfi_rdlvl_gate_en 8

dfi_wrlvl_strob

e 9

dfi_lvl_pattern

dfi_lvl_periodic1

4

dfi_lp_req 1

培训接

口

低功耗控制

接口错误接

口

dfi_phy_rdlvl_cs_n 8

dfi_rdlvl_resp 8

dfi_rdlvl_gate_req 8

dfi_phy_rdlvl_gate_cs_n 8

dfi_wrlvl_req 9

dfi_phy_wrlvl_cs_n 9

dfi_wrlvl_resp 9

dfi_lp_ack 1

dfi_error 1

dfi_error_info1

1.用于所有 dram。

2.可选的后缀频率比系统。

3.用于 DDR4、DDR3、DDR2、DDR1 和 LPDDR1 dram。

4.仅用于 DDR4 dram。

5.用于 DDR4、DDR3 和 DDR2 dram。

6.仅用于 LPDDR2 DRAM。

7.双重功能的信号。在启用了写 DBI 的 DDR4 系统中,信号从掩码转

换为写 DBI 信号。

8.用于 DDR4、DDR3 和 LPDDR2 dram。

9.用于 DDR4 和 DDR3 dram。

斜体字表示阶段/词/周期是可选的。

133 年 18

岁

版权所有 1995-2012,Cadence

设计系统公司

DDR PHY 接口 3.0 版 2012 年 5 月

18 日

�

体系结构

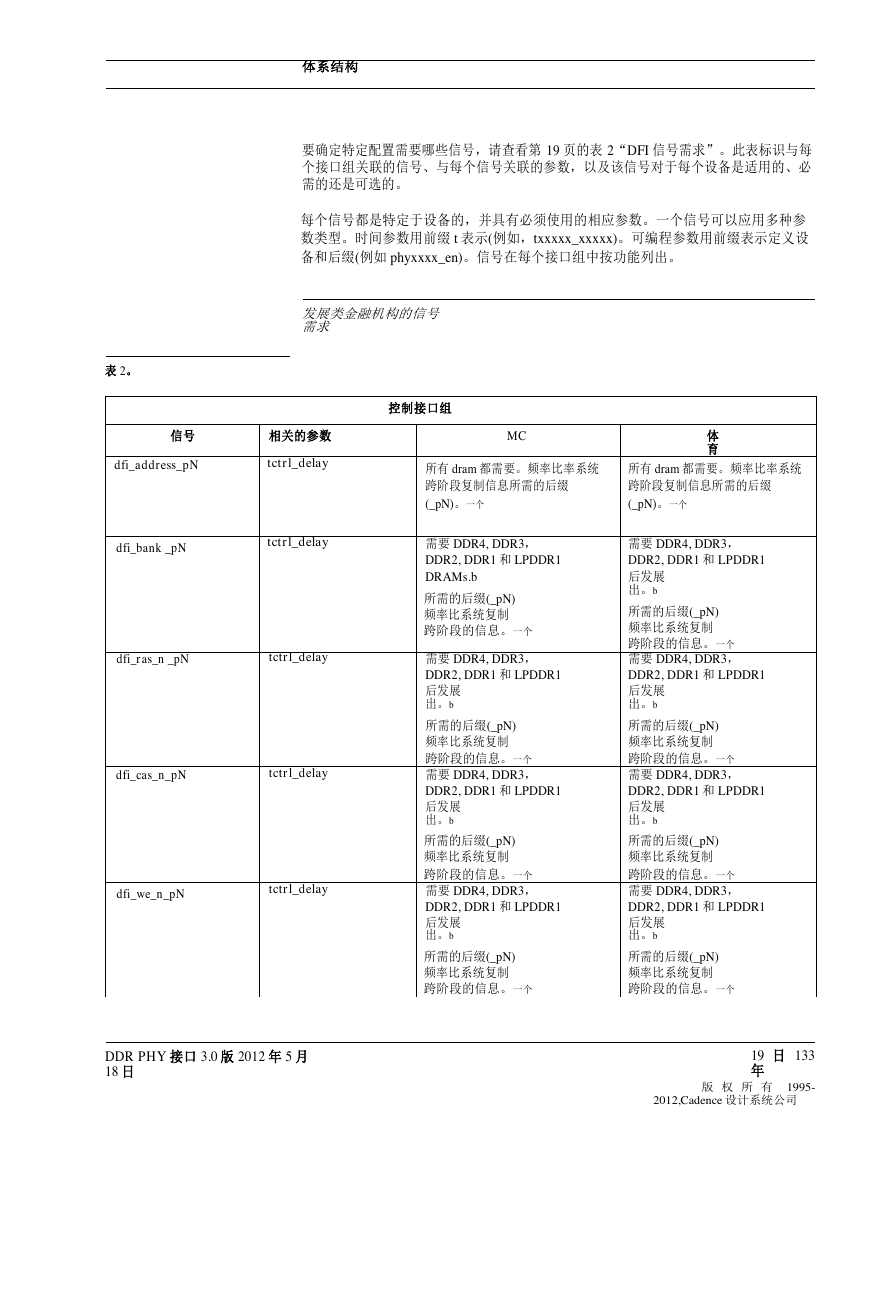

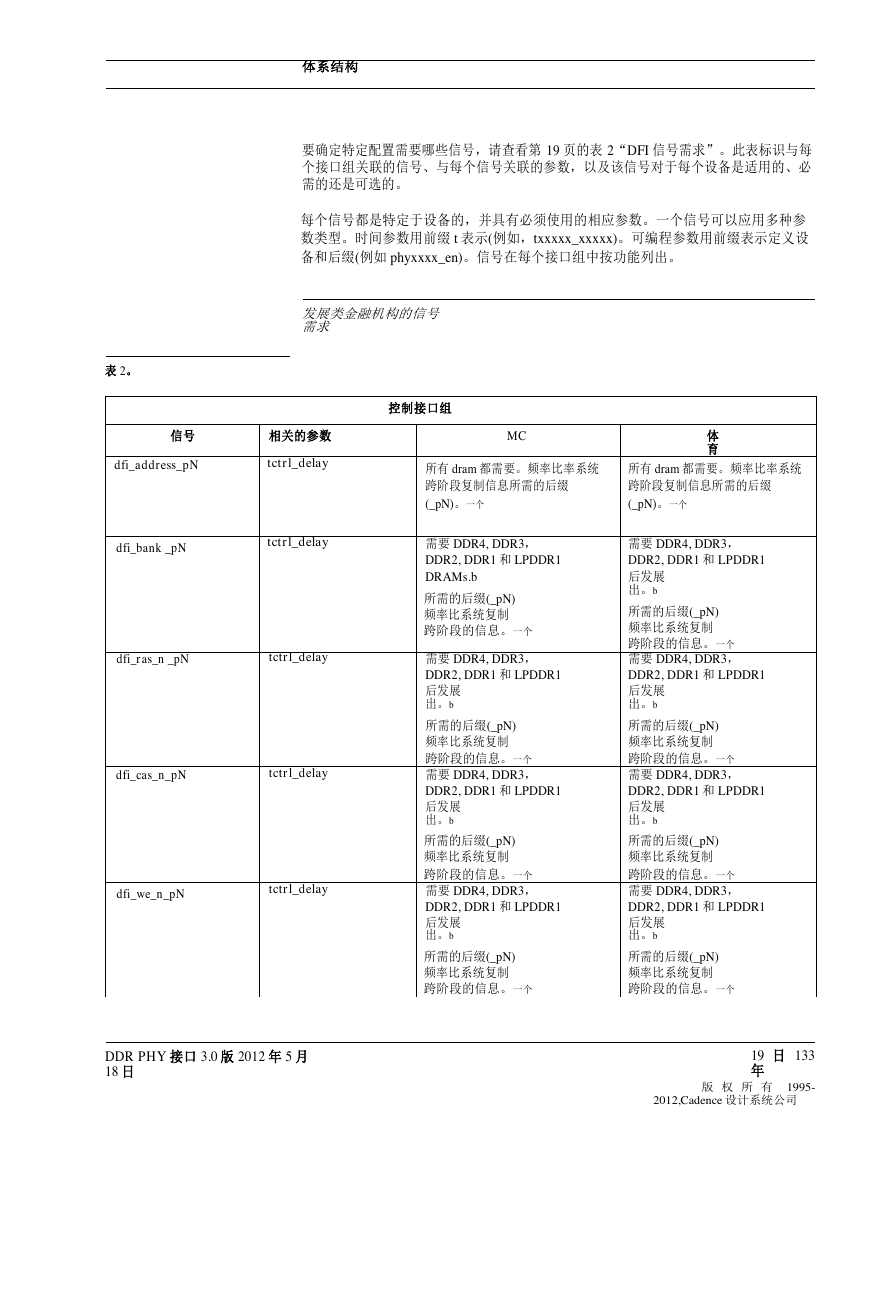

要确定特定配置需要哪些信号,请查看第 19 页的表 2“DFI 信号需求”。此表标识与每

个接口组关联的信号、与每个信号关联的参数,以及该信号对于每个设备是适用的、必

需的还是可选的。

每个信号都是特定于设备的,并具有必须使用的相应参数。一个信号可以应用多种参

数类型。时间参数用前缀 t 表示(例如,txxxxx_xxxxx)。可编程参数用前缀表示定义设

备和后缀(例如 phyxxxx_en)。信号在每个接口组中按功能列出。

发展类金融机构的信号

需求

表 2。

信号

dfi_address_pN

相关的参数

tctrl_delay

dfi_bank _pN

tctrl_delay

dfi_ras_n _pN

tctrl_delay

dfi_cas_n_pN

tctrl_delay

dfi_we_n_pN

tctrl_delay

控制接口组

MC

体

育

所有 dram 都需要。频率比率系统

跨阶段复制信息所需的后缀

(_pN)。一个

所有 dram 都需要。频率比率系统

跨阶段复制信息所需的后缀

(_pN)。一个

需要 DDR4, DDR3,

DDR2, DDR1 和 LPDDR1

DRAMs.b

所需的后缀(_pN)

频率比系统复制

跨阶段的信息。一个

需要 DDR4, DDR3,

DDR2, DDR1 和 LPDDR1

后发展

出。b

所需的后缀(_pN)

频率比系统复制

跨阶段的信息。一个

需要 DDR4, DDR3,

DDR2, DDR1 和 LPDDR1

后发展

出。b

所需的后缀(_pN)

频率比系统复制

跨阶段的信息。一个

需要 DDR4, DDR3,

DDR2, DDR1 和 LPDDR1

后发展

出。b

所需的后缀(_pN)

频率比系统复制

跨阶段的信息。一个

需要 DDR4, DDR3,

DDR2, DDR1 和 LPDDR1

后发展

出。b

所需的后缀(_pN)

频率比系统复制

跨阶段的信息。一个

需要 DDR4, DDR3,

DDR2, DDR1 和 LPDDR1

后发展

出。b

所需的后缀(_pN)

频率比系统复制

跨阶段的信息。一个

需要 DDR4, DDR3,

DDR2, DDR1 和 LPDDR1

后发展

出。b

所需的后缀(_pN)

频率比系统复制

跨阶段的信息。一个

需要 DDR4, DDR3,

DDR2, DDR1 和 LPDDR1

后发展

出。b

所需的后缀(_pN)

频率比系统复制

跨阶段的信息。一个

DDR PHY 接口 3.0 版 2012 年 5 月

18 日

19 日 133

年

版 权 所 有 1995-

2012,Cadence 设计系统公司

�

体系结构

dfi_cs_n_ pN

dfi_act_n_pN

dfi_bg_pN

dfi_cid_pN

dfi_cke_pN

dfi_odt_pN

tcmd_lat

tctrl_delay

tctrl_delay

tctrl_delay

tctrl_delay

tctrl_delay

所有 dram 都需要。频率比率系统

跨阶段复制信息所需的后缀

(_pN)。一个

所有 dram 都需要。频率比率系

统跨阶段复制信息所需的后缀

(_pN)。一个

DDR4 所必需的。b

DDR4 所必需的。b

DDR4 所必需的。b

DDR4 所必需的。b

DDR4 所必需的。b

DDR4 所必需的。b

频率比系统跨阶段复制信息所需的

所有 DRAMs 后缀(_pN)。一个

频率比系统跨阶段复制信息所需

的所有 DRAMs 后缀(_pN)。一个

phycrc_mode

tctrl_delay

需要 DDR4, DDR3 和 DDR2

dram。频率比率系统跨阶段复制信息所需

的 b 后缀(_pN)。一个

DDR4、DDR3 和 DDR2 dram 所

必需的。频率比率系统跨阶段复制信息

所需的 b 后缀(_pN)。一个

dfi_reset_n_pN

tctrl_delay

DDR4 和 DDR3 dram 必需的。频率

比率系统跨阶段复制信息所需的 b 后缀

(_pN)。一个

DDR4 和 DDR3 dram 必需的。频

率比率系统跨阶段复制信息所需的 b 后缀

(_pN)。一个

信号

相关的参数

MC

编写接口组

dfi_wrdata_en_pN

dfi_wrdata_pN

phycrc_mode

tcmd_lat

tphy_crcmax_lat

tphy_crcmin_lat

tphy_wrdata

twrdata_delay

tphy_wrlat

dfirw_length

phycrc_mode

tphy_wrdata

tphy_wrlat

体

育

所有 dram 都需要。频率比率系统

跨阶段复制信息所需的后缀

(_pN)。一个

所有 dram 都需要。频率比率系

统跨阶段复制信息所需的后缀

(_pN)。一个

所有 dram 都需要。频率比率系统

跨阶段复制信息所需的后缀

(_pN)。一个

所有 dram 都需要。频率比率系

统跨阶段复制信息所需的后缀

(_pN)。一个

133 年 20

版权所有 1995-2012,Cadence

设计系统公司

DDR PHY 接口 3.0 版 2012 年 5 月

18 日

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc