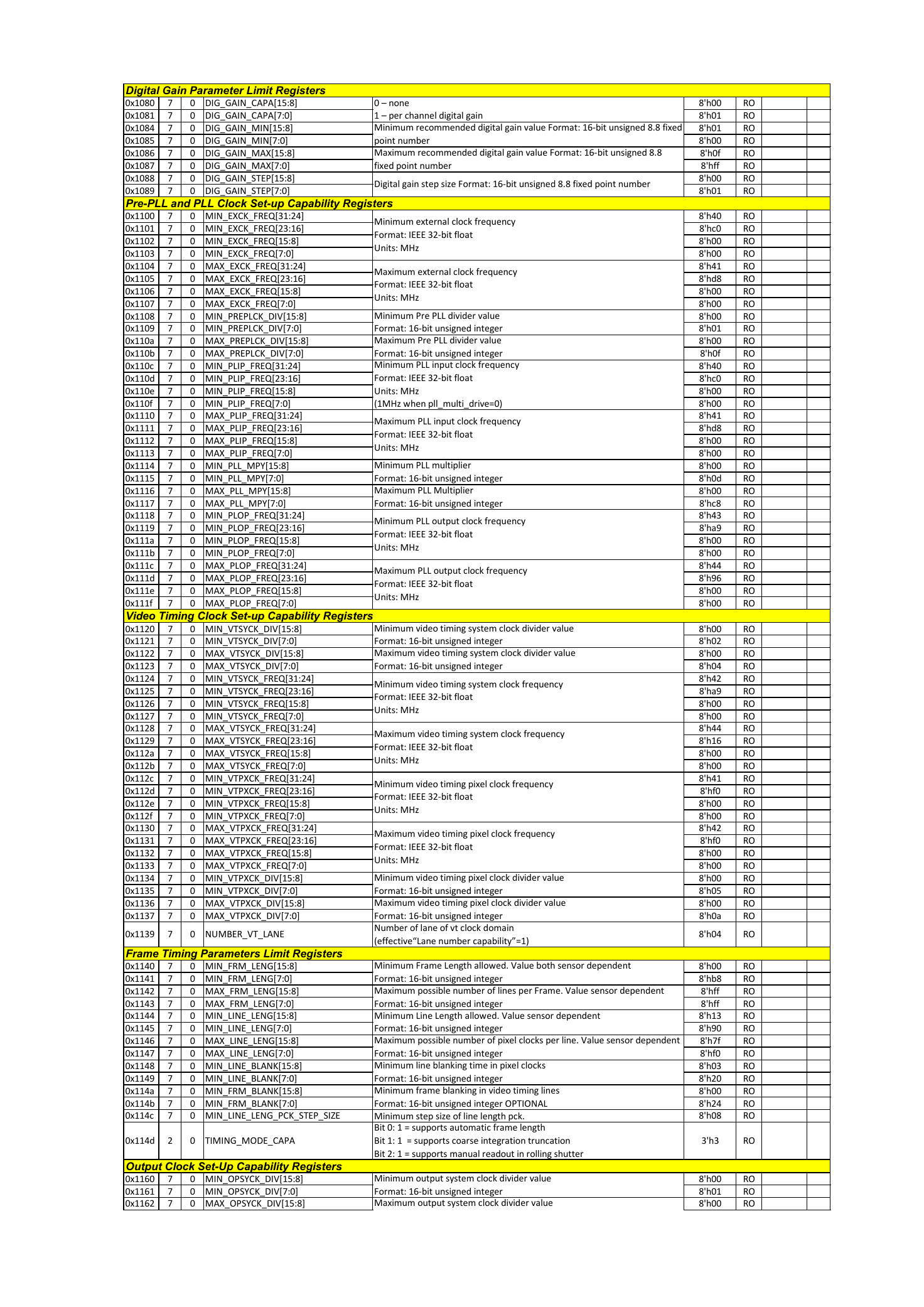

Addres

Bit

Register Name

Comment

initial value

(HEX)

R/W

reflection

(GPH)

EDL

16-bit camera module model number e.g. 552

Value is programmed in NVM

Revision identifier of camera module for DCC change

Revision identifier of camera module for DCC change

Value is programmed in NVM

Manufacturer ID

Revision identifier of camera module for DCC change

Value is programmed in NVM

9 – SMIA V0.9, 10 - SMIA V1.0, 11 – SMIA V1.1

8-bit (0-255) Frame counter value

Colour Pixel Order

Black level value on output of the sensor. Usually, value=0x40 in 10-bit

system (traditional SONY sensor has 0x3C).

Bit 0 : 0 = current definition, 1= new definition

8-bit, 10-bit or 12-bit pixel data REDUNDANT

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

the customer area of OTP

frame_format_model_type

frame_format_model_subtype

Valid only for frame_format_model_type 0x02

Valid only for frame_format_model_type 0x02

Valid only for frame_format_model_type 0x02

Analogue Gain Capability, 0 – single global analogue gain only, 1 – 4

separate channel analogue gains only

Minimum recommended analogue gain code Format: 16-bit unsigned

integer

Maximum recommended analogue gain code Format: 16-bit unsigned

integer

Analogue gain code step size Format: 16-bit unsigned integer

Analogue gain type Format: 16-bit unsigned integer

Analogue gain m0 constant Format: 16-bit signed integer

Analogue gain c0 constant Format: 16-bit signed integer

Analogue gain m1 constant Format: 16-bit signed integer

Analogue gain c1 constant Format: 16-bit signed integer

data_format_model_type

data_format_model_subtype

data_format_descriptor_0 (RAW8: 0x0808)

data_format_descriptor_1 (Comp6: 0x0A06)

data_format_descriptor_2 (Comp8 10to8: 0x0A08)

data_format_descriptor_3 (RAW10: 0x0A0A)

data_format_descriptor_3 (RAW12: 0x0C0C)

data_format_descriptor_3 (RAW14: 0x0E0E)

Prefixed embedded data

8'h00

8'h00

8'h00

8'h00

8'h0a

8'hff

2'h1

2'h0

8'h40

1'h1

8'h00

8'h00

8'h00

4'h0

4'h0

5'h00

3'h0

8'h02

8'h14

8'h00

8'h0b

8'h00

8'h00

8'h00

8'h00

8'h00

8'h02

8'h12

8'h50

8'h00

8'h10

8'h70

8'h10

8'h00

8'h00

8'h04

8'h50

8'h00

8'h0c

8'h30

8'h00

8'h00

8'h00

8'h00

8'h01

8'hc0

8'h00

8'h01

8'h00

8'h00

8'h00

8'h00

8'h02

8'h00

8'hff

8'hff

8'h02

8'h00

8'h01

8'h06

8'h08

8'h08

8'h0a

8'h06

8'h0a

8'h08

8'h0a

8'h0a

8'h0c

8'h0c

8'h0e

8'h0e

8'h00

8'h00

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

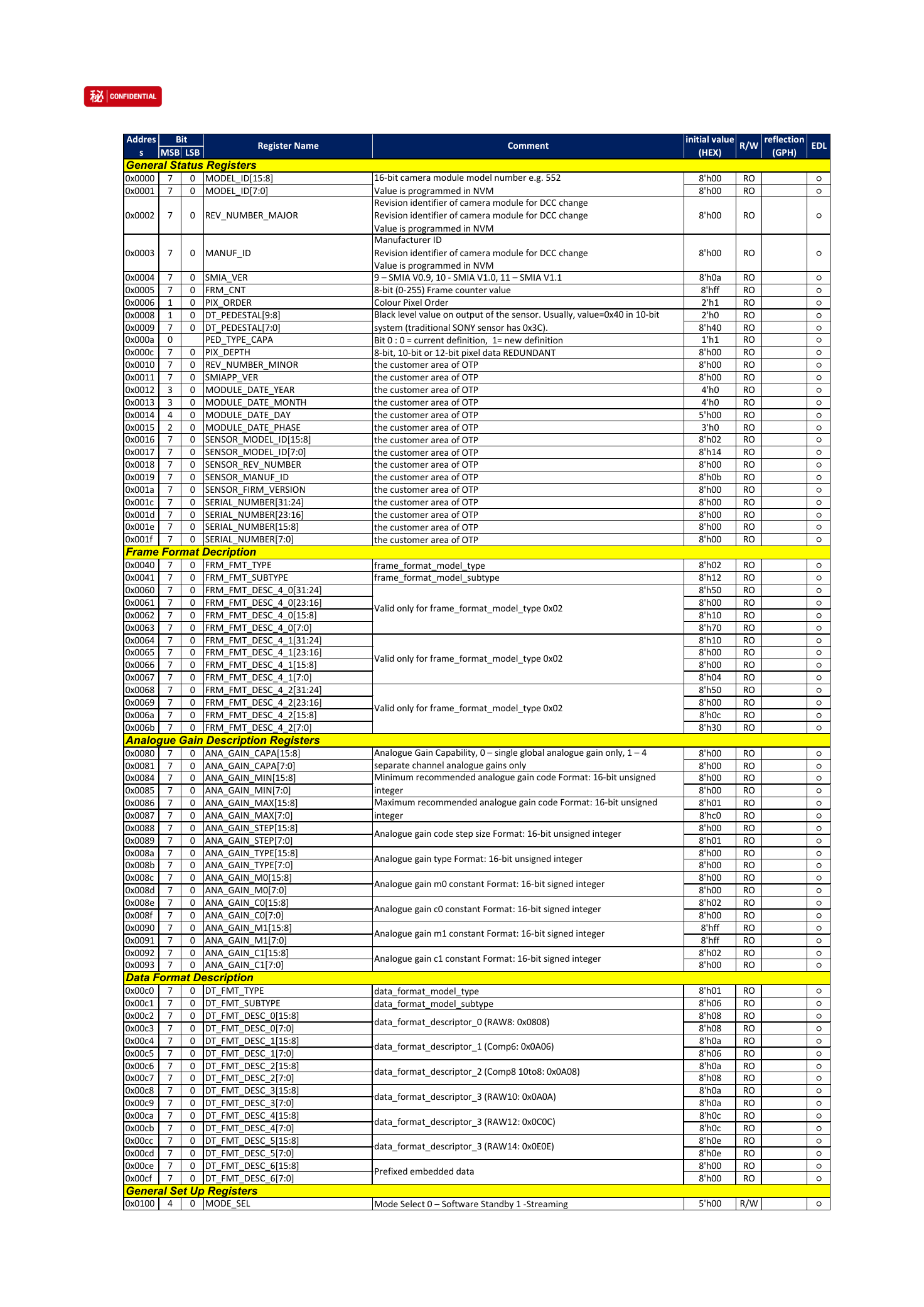

Mode Select 0 – Software Standby 1 -Streaming

5'h00

R/W

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

s

MSB LSB

General Status Registers

0x0000

0x0001

0 MODEL_ID[15:8]

0 MODEL_ID[7:0]

7

7

0x0002

0x0003

7

7

0 REV_NUMBER_MAJOR

0 MANUF_ID

PED_TYPE_CAPA

7

7

1

1

7

0

7

7

7

3

3

4

2

7

7

7

7

7

7

7

7

7

0 SMIA_VER

0 FRM_CNT

0 PIX_ORDER

0 DT_PEDESTAL[9:8]

0 DT_PEDESTAL[7:0]

0 FRM_FMT_TYPE

0 FRM_FMT_SUBTYPE

0 FRM_FMT_DESC_4_0[31:24]

0 FRM_FMT_DESC_4_0[23:16]

0 FRM_FMT_DESC_4_0[15:8]

0 FRM_FMT_DESC_4_0[7:0]

0 FRM_FMT_DESC_4_1[31:24]

0 FRM_FMT_DESC_4_1[23:16]

0 FRM_FMT_DESC_4_1[15:8]

0 FRM_FMT_DESC_4_1[7:0]

0 FRM_FMT_DESC_4_2[31:24]

0 FRM_FMT_DESC_4_2[23:16]

0 FRM_FMT_DESC_4_2[15:8]

0 FRM_FMT_DESC_4_2[7:0]

0 PIX_DEPTH

0 REV_NUMBER_MINOR

0 SMIAPP_VER

0 MODULE_DATE_YEAR

0 MODULE_DATE_MONTH

0 MODULE_DATE_DAY

0 MODULE_DATE_PHASE

0 SENSOR_MODEL_ID[15:8]

0 SENSOR_MODEL_ID[7:0]

0 SENSOR_REV_NUMBER

0 SENSOR_MANUF_ID

0 SENSOR_FIRM_VERSION

0 SERIAL_NUMBER[31:24]

0 SERIAL_NUMBER[23:16]

0 SERIAL_NUMBER[15:8]

0 SERIAL_NUMBER[7:0]

0x0004

0x0005

0x0006

0x0008

0x0009

0x000a

0x000c

0x0010

0x0011

0x0012

0x0013

0x0014

0x0015

0x0016

0x0017

0x0018

0x0019

0x001a

0x001c

0x001d

0x001e

0x001f

Frame Format Decription

0x0040

0x0041

0x0060

0x0061

0x0062

0x0063

0x0064

0x0065

0x0066

0x0067

0x0068

0x0069

0x006a

0x006b

Analogue Gain Description Registers

0x0080

0x0081

0x0084

0x0085

0x0086

0x0087

0x0088

0x0089

0x008a

0x008b

0x008c

0x008d

0x008e

0x008f

0x0090

0x0091

0x0092

0x0093

Data Format Description

0x00c0

0x00c1

0x00c2

0x00c3

0x00c4

0x00c5

0x00c6

0x00c7

0x00c8

0x00c9

0x00ca

0x00cb

0x00cc

0x00cd

0x00ce

0x00cf

General Set Up Registers

0x0100

0 MODE_SEL

0 ANA_GAIN_CAPA[15:8]

0 ANA_GAIN_CAPA[7:0]

0 ANA_GAIN_MIN[15:8]

0 ANA_GAIN_MIN[7:0]

0 ANA_GAIN_MAX[15:8]

0 ANA_GAIN_MAX[7:0]

0 ANA_GAIN_STEP[15:8]

0 ANA_GAIN_STEP[7:0]

0 ANA_GAIN_TYPE[15:8]

0 ANA_GAIN_TYPE[7:0]

0 ANA_GAIN_M0[15:8]

0 ANA_GAIN_M0[7:0]

0 ANA_GAIN_C0[15:8]

0 ANA_GAIN_C0[7:0]

0 ANA_GAIN_M1[15:8]

0 ANA_GAIN_M1[7:0]

0 ANA_GAIN_C1[15:8]

0 ANA_GAIN_C1[7:0]

0 DT_FMT_TYPE

0 DT_FMT_SUBTYPE

0 DT_FMT_DESC_0[15:8]

0 DT_FMT_DESC_0[7:0]

0 DT_FMT_DESC_1[15:8]

0 DT_FMT_DESC_1[7:0]

0 DT_FMT_DESC_2[15:8]

0 DT_FMT_DESC_2[7:0]

0 DT_FMT_DESC_3[15:8]

0 DT_FMT_DESC_3[7:0]

0 DT_FMT_DESC_4[15:8]

0 DT_FMT_DESC_4[7:0]

0 DT_FMT_DESC_5[15:8]

0 DT_FMT_DESC_5[7:0]

0 DT_FMT_DESC_6[15:8]

0 DT_FMT_DESC_6[7:0]

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

4

�

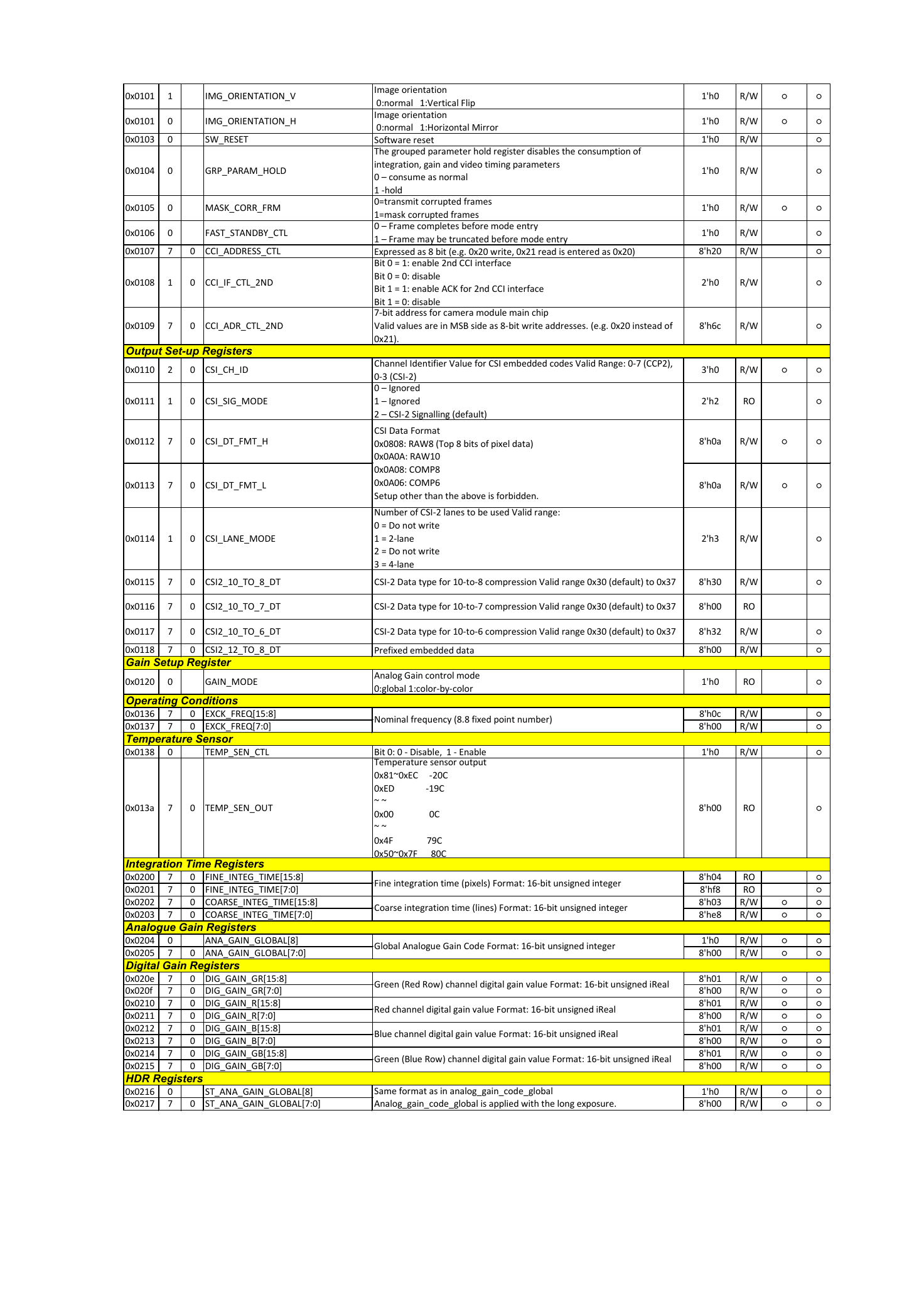

0x0101

0x0101

0x0103

0x0104

0x0105

0x0106

0x0107

0x0108

0x0109

1

0

0

0

0

0

7

1

7

IMG_ORIENTATION_V

IMG_ORIENTATION_H

SW_RESET

GRP_PARAM_HOLD

MASK_CORR_FRM

FAST_STANDBY_CTL

0 CCI_ADDRESS_CTL

0 CCI_IF_CTL_2ND

0 CCI_ADR_CTL_2ND

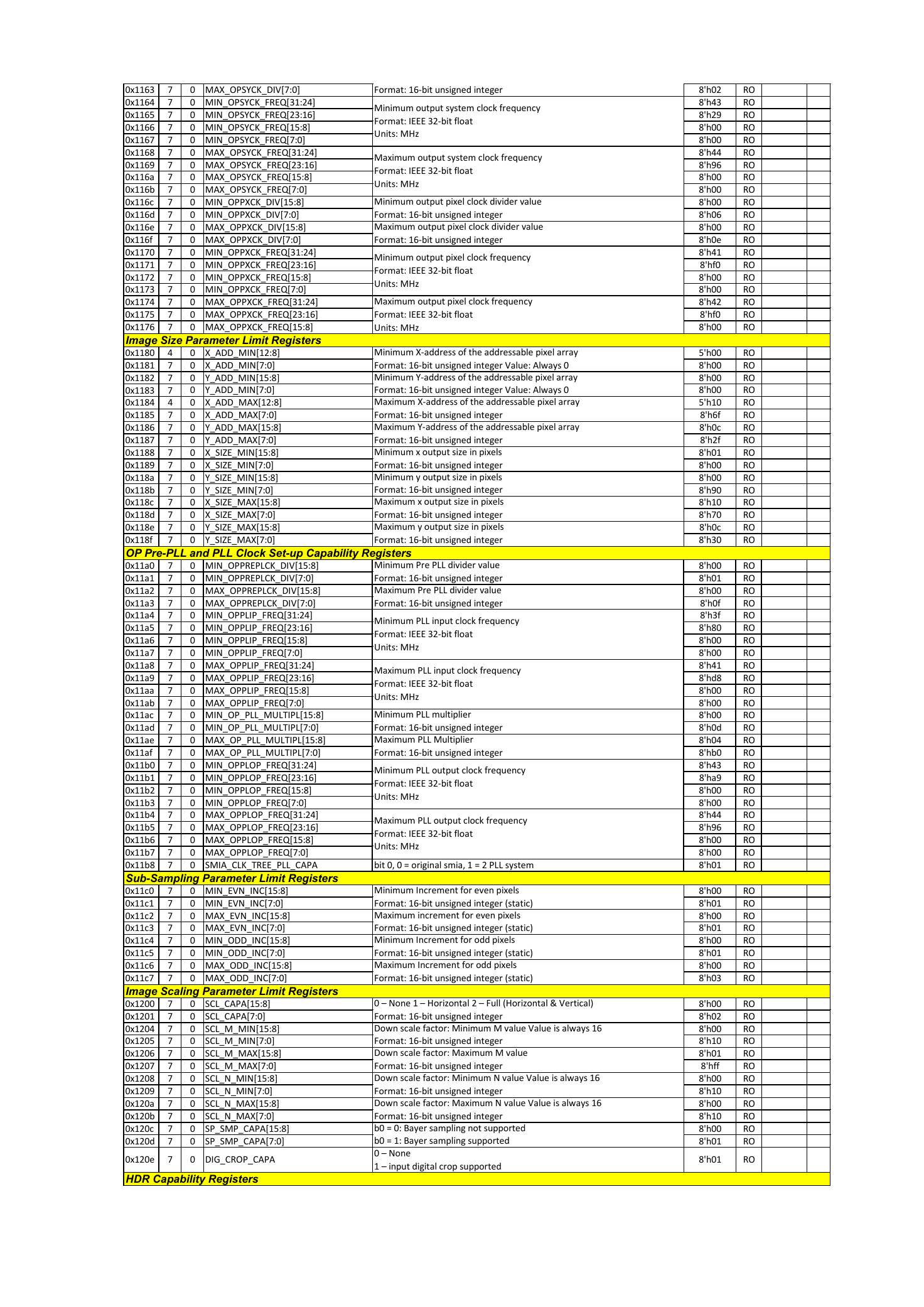

Output Set-up Registers

0x0110

0 CSI_CH_ID

2

0x0111

0x0112

0x0113

0x0114

0x0115

0x0116

1

7

7

1

7

7

0 CSI_SIG_MODE

0 CSI_DT_FMT_H

0 CSI_DT_FMT_L

0 CSI_LANE_MODE

0 CSI2_10_TO_8_DT

0 CSI2_10_TO_7_DT

0 CSI2_10_TO_6_DT

0 CSI2_12_TO_8_DT

GAIN_MODE

0

7

7

0x0117

0x0118

Gain Setup Register

0x0120

Operating Conditions

0x0136

0x0137

Temperature Sensor

0x0138

7

7

0

0 EXCK_FREQ[15:8]

0 EXCK_FREQ[7:0]

TEMP_SEN_CTL

0x013a

7

0 TEMP_SEN_OUT

ANA_GAIN_GLOBAL[8]

0 ANA_GAIN_GLOBAL[7:0]

0 FINE_INTEG_TIME[15:8]

0 FINE_INTEG_TIME[7:0]

0 COARSE_INTEG_TIME[15:8]

0 COARSE_INTEG_TIME[7:0]

0

7

7

7

7

7

Integration Time Registers

0x0200

0x0201

0x0202

0x0203

Analogue Gain Registers

0x0204

0x0205

Digital Gain Registers

0x020e

0x020f

0x0210

0x0211

0x0212

0x0213

0x0214

0x0215

HDR Registers

0x0216

0x0217

0 DIG_GAIN_GR[15:8]

0 DIG_GAIN_GR[7:0]

0 DIG_GAIN_R[15:8]

0 DIG_GAIN_R[7:0]

0 DIG_GAIN_B[15:8]

0 DIG_GAIN_B[7:0]

0 DIG_GAIN_GB[15:8]

0 DIG_GAIN_GB[7:0]

7

7

7

7

7

7

7

7

0

7

ST_ANA_GAIN_GLOBAL[8]

0 ST_ANA_GAIN_GLOBAL[7:0]

Image orientation

0:normal 1:Vertical Flip

Image orientation

0:normal 1:Horizontal Mirror

Software reset

The grouped parameter hold register disables the consumption of

integration, gain and video timing parameters

0 – consume as normal

1 -hold

0=transmit corrupted frames

1=mask corrupted frames

0 – Frame completes before mode entry

1 – Frame may be truncated before mode entry

Expressed as 8 bit (e.g. 0x20 write, 0x21 read is entered as 0x20)

Bit 0 = 1: enable 2nd CCI interface

Bit 0 = 0: disable

Bit 1 = 1: enable ACK for 2nd CCI interface

Bit 1 = 0: disable

7-bit address for camera module main chip

Valid values are in MSB side as 8-bit write addresses. (e.g. 0x20 instead of

0x21).

Channel Identifier Value for CSI embedded codes Valid Range: 0-7 (CCP2),

0-3 (CSI-2)

0 – Ignored

1 – Ignored

2 – CSI-2 Signalling (default)

CSI Data Format

0x0808: RAW8 (Top 8 bits of pixel data)

0x0A0A: RAW10

0x0A08: COMP8

0x0A06: COMP6

Setup other than the above is forbidden.

Number of CSI-2 lanes to be used Valid range:

0 = Do not write

1 = 2-lane

2 = Do not write

3 = 4-lane

CSI-2 Data type for 10-to-8 compression Valid range 0x30 (default) to 0x37

CSI-2 Data type for 10-to-7 compression Valid range 0x30 (default) to 0x37

CSI-2 Data type for 10-to-6 compression Valid range 0x30 (default) to 0x37

Prefixed embedded data

Analog Gain control mode

0:global 1:color-by-color

Nominal frequency (8.8 fixed point number)

Bit 0: 0 - Disable, 1 - Enable

Temperature sensor output

0x81~0xEC -20C

0xED -19C

~ ~

0x00 0C

~ ~

0x4F 79C

0x50~0x7F 80C

Fine integration time (pixels) Format: 16-bit unsigned integer

Coarse integration time (lines) Format: 16-bit unsigned integer

Global Analogue Gain Code Format: 16-bit unsigned integer

Green (Red Row) channel digital gain value Format: 16-bit unsigned iReal

Red channel digital gain value Format: 16-bit unsigned iReal

Blue channel digital gain value Format: 16-bit unsigned iReal

Green (Blue Row) channel digital gain value Format: 16-bit unsigned iReal

Same format as in analog_gain_code_global

Analog_gain_code_global is applied with the long exposure.

○

○

○

1'h0

1'h0

1'h0

R/W

R/W

R/W

1'h0

R/W

1'h0

1'h0

8'h20

R/W

R/W

R/W

2'h0

R/W

8'h6c

R/W

3'h0

R/W

○

2'h2

RO

8'h0a

R/W

8'h0a

R/W

2'h3

R/W

8'h30

R/W

8'h00

8'h32

8'h00

RO

R/W

R/W

1'h0

RO

8'h0c

8'h00

1'h0

R/W

R/W

R/W

8'h00

RO

8'h04

8'hf8

8'h03

8'he8

1'h0

8'h00

8'h01

8'h00

8'h01

8'h00

8'h01

8'h00

8'h01

8'h00

1'h0

8'h00

RO

RO

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

�

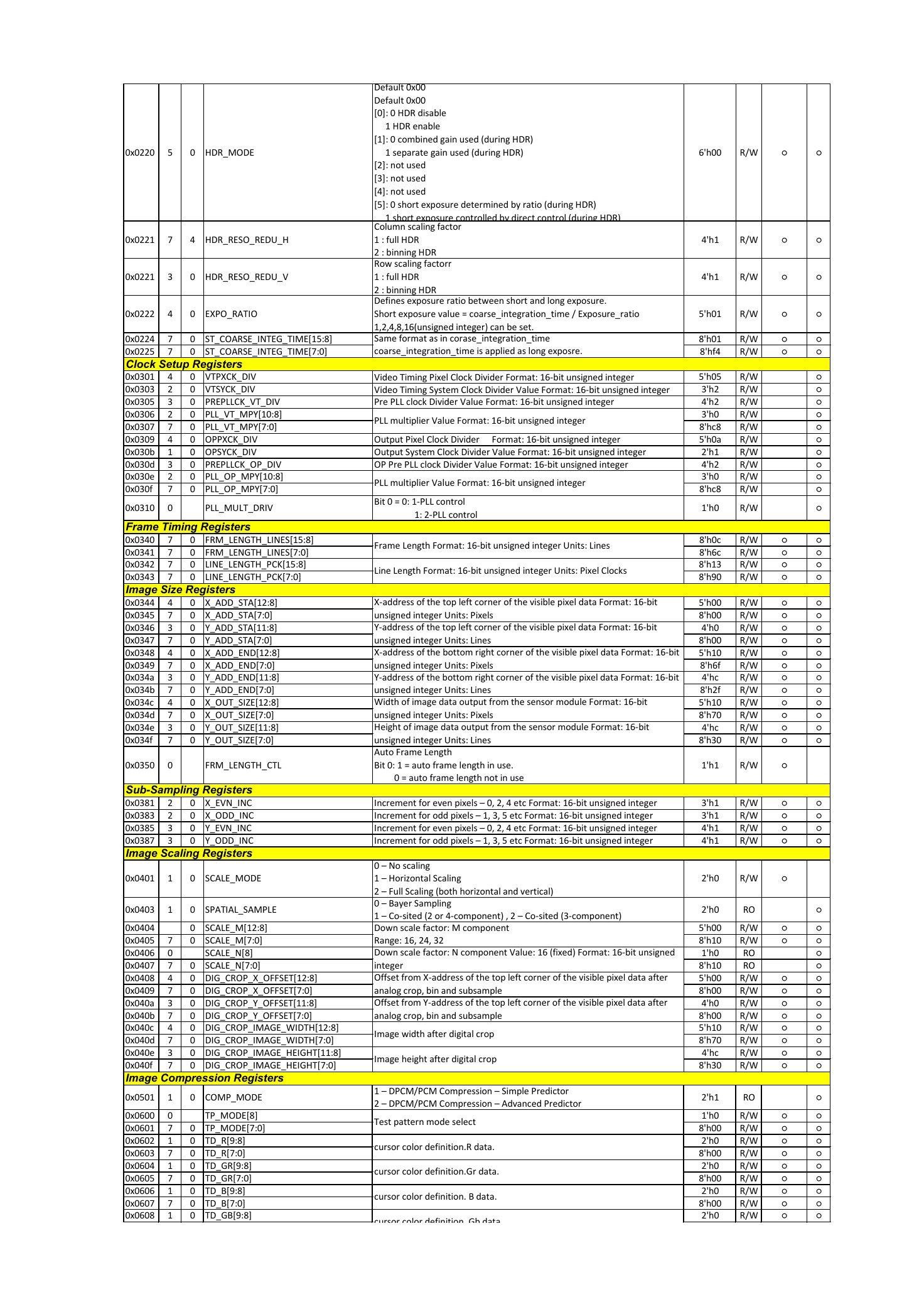

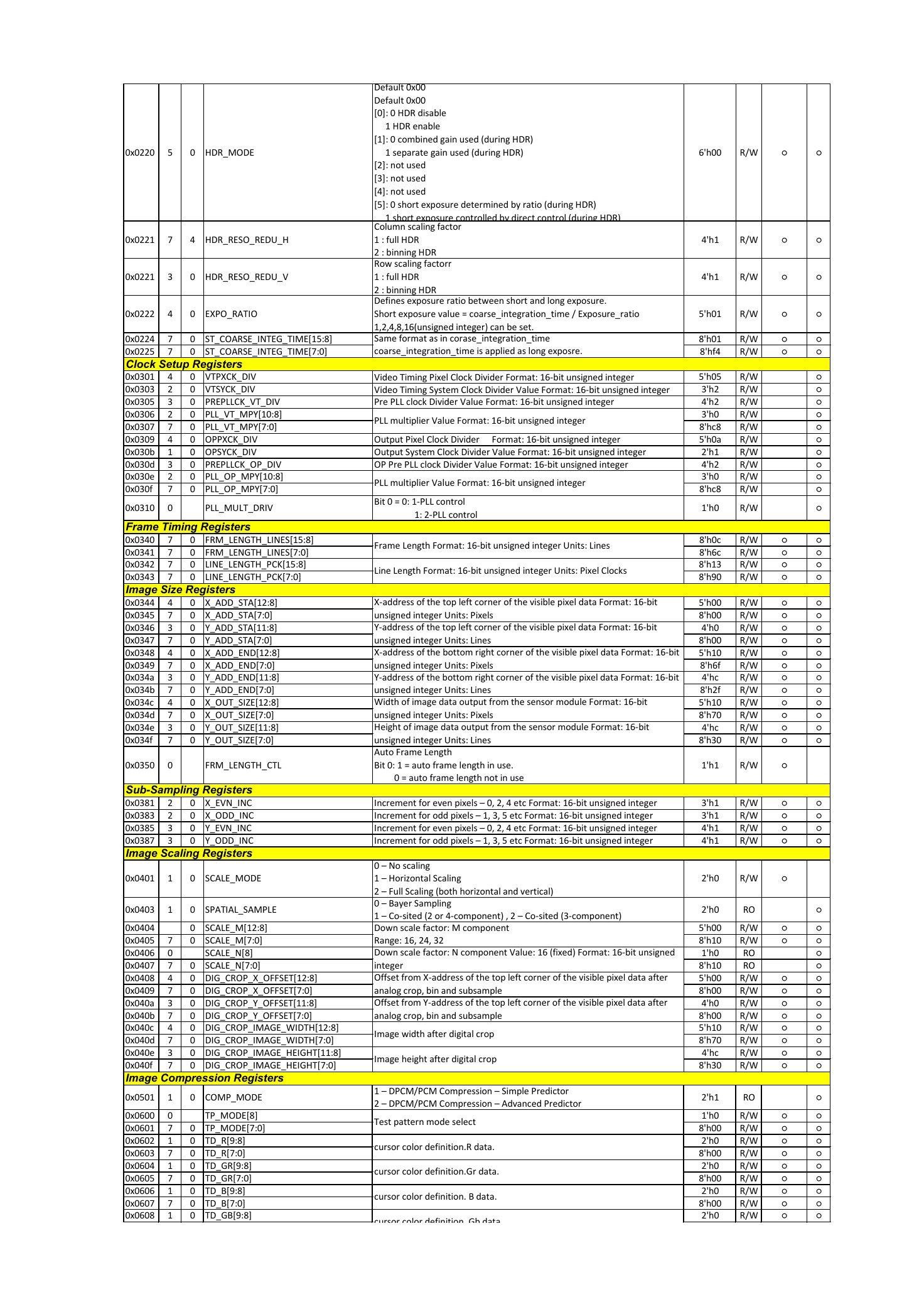

0x0220

5

0 HDR_MODE

0x0221

0x0221

0x0222

7

3

4

4 HDR_RESO_REDU_H

0 HDR_RESO_REDU_V

0 EXPO_RATIO

7

7

4

2

3

2

7

4

1

3

2

7

0

0 VTPXCK_DIV

0 VTSYCK_DIV

0 PREPLLCK_VT_DIV

0 PLL_VT_MPY[10:8]

0 PLL_VT_MPY[7:0]

0 OPPXCK_DIV

0 OPSYCK_DIV

0 PREPLLCK_OP_DIV

0 PLL_OP_MPY[10:8]

0 PLL_OP_MPY[7:0]

PLL_MULT_DRIV

0x0224

0x0225

Clock Setup Registers

0x0301

0x0303

0x0305

0x0306

0x0307

0x0309

0x030b

0x030d

0x030e

0x030f

0x0310

Frame Timing Registers

0x0340

0x0341

0x0342

0x0343

Image Size Registers

0x0344

0x0345

0x0346

0x0347

0x0348

0x0349

0x034a

0x034b

0x034c

0x034d

0x034e

0x034f

0 X_ADD_STA[12:8]

0 X_ADD_STA[7:0]

0 Y_ADD_STA[11:8]

0 Y_ADD_STA[7:0]

0 X_ADD_END[12:8]

0 X_ADD_END[7:0]

0 Y_ADD_END[11:8]

0 Y_ADD_END[7:0]

0 X_OUT_SIZE[12:8]

0 X_OUT_SIZE[7:0]

0 Y_OUT_SIZE[11:8]

0 Y_OUT_SIZE[7:0]

4

7

3

7

4

7

3

7

4

7

3

7

7

7

7

7

0 ST_COARSE_INTEG_TIME[15:8]

0 ST_COARSE_INTEG_TIME[7:0]

0 FRM_LENGTH_LINES[15:8]

0 FRM_LENGTH_LINES[7:0]

0 LINE_LENGTH_PCK[15:8]

0 LINE_LENGTH_PCK[7:0]

0x0350

0

FRM_LENGTH_CTL

Sub-Sampling Registers

0x0381

0 X_EVN_INC

0x0383

0 X_ODD_INC

0x0385

0 Y_EVN_INC

0x0387

0 Y_ODD_INC

Image Scaling Registers

2

2

3

3

0x0401

1

0 SCALE_MODE

0 SCALE_N[7:0]

0 DIG_CROP_X_OFFSET[12:8]

0 DIG_CROP_X_OFFSET[7:0]

0 DIG_CROP_Y_OFFSET[11:8]

0 DIG_CROP_Y_OFFSET[7:0]

0 DIG_CROP_IMAGE_WIDTH[12:8]

0 DIG_CROP_IMAGE_WIDTH[7:0]

0 DIG_CROP_IMAGE_HEIGHT[11:8]

0 DIG_CROP_IMAGE_HEIGHT[7:0]

1

SCALE_N[8]

7

0

7

4

7

3

7

4

7

3

7

0 SPATIAL_SAMPLE

0 SCALE_M[12:8]

0 SCALE_M[7:0]

0x0403

0x0404

0x0405

0x0406

0x0407

0x0408

0x0409

0x040a

0x040b

0x040c

0x040d

0x040e

0x040f

Image Compression Registers

0x0501

0x0600

0x0601

0x0602

0x0603

0x0604

0x0605

0x0606

0x0607

0x0608

0 TP_MODE[7:0]

0 TD_R[9:8]

0 TD_R[7:0]

0 TD_GR[9:8]

0 TD_GR[7:0]

0 TD_B[9:8]

0 TD_B[7:0]

0 TD_GB[9:8]

0 COMP_MODE

TP_MODE[8]

1

0

7

1

7

1

7

1

7

1

Default 0x00

Default 0x00

[0]: 0 HDR disable

1 HDR enable

[1]: 0 combined gain used (during HDR)

1 separate gain used (during HDR)

[2]: not used

[3]: not used

[4]: not used

[5]: 0 short exposure determined by ratio (during HDR)

1 short exposure controlled by direct control (during HDR)

Column scaling factor

1 : full HDR

2 : binning HDR

Row scaling factorr

1 : full HDR

2 : binning HDR

Defines exposure ratio between short and long exposure.

Short exposure value = coarse_integration_time / Exposure_ratio

1,2,4,8,16(unsigned integer) can be set.

Same format as in corase_integration_time

coarse_integration_time is applied as long exposre.

Video Timing Pixel Clock Divider Format: 16-bit unsigned integer

Video Timing System Clock Divider Value Format: 16-bit unsigned integer

Pre PLL clock Divider Value Format: 16-bit unsigned integer

PLL multiplier Value Format: 16-bit unsigned integer

Output Pixel Clock Divider Format: 16-bit unsigned integer

Output System Clock Divider Value Format: 16-bit unsigned integer

OP Pre PLL clock Divider Value Format: 16-bit unsigned integer

PLL multiplier Value Format: 16-bit unsigned integer

Bit 0 = 0: 1-PLL control

1: 2-PLL control

Frame Length Format: 16-bit unsigned integer Units: Lines

Line Length Format: 16-bit unsigned integer Units: Pixel Clocks

X-address of the top left corner of the visible pixel data Format: 16-bit

unsigned integer Units: Pixels

Y-address of the top left corner of the visible pixel data Format: 16-bit

unsigned integer Units: Lines

X-address of the bottom right corner of the visible pixel data Format: 16-bit

unsigned integer Units: Pixels

Y-address of the bottom right corner of the visible pixel data Format: 16-bit

unsigned integer Units: Lines

Width of image data output from the sensor module Format: 16-bit

unsigned integer Units: Pixels

Height of image data output from the sensor module Format: 16-bit

unsigned integer Units: Lines

Auto Frame Length

Bit 0: 1 = auto frame length in use.

0 = auto frame length not in use

Increment for even pixels – 0, 2, 4 etc Format: 16-bit unsigned integer

Increment for odd pixels – 1, 3, 5 etc Format: 16-bit unsigned integer

Increment for even pixels – 0, 2, 4 etc Format: 16-bit unsigned integer

Increment for odd pixels – 1, 3, 5 etc Format: 16-bit unsigned integer

0 – No scaling

1 – Horizontal Scaling

2 – Full Scaling (both horizontal and vertical)

0 – Bayer Sampling

1 – Co-sited (2 or 4-component) , 2 – Co-sited (3-component)

Down scale factor: M component

Range: 16, 24, 32

Down scale factor: N component Value: 16 (fixed) Format: 16-bit unsigned

integer

Offset from X-address of the top left corner of the visible pixel data after

analog crop, bin and subsample

Offset from Y-address of the top left corner of the visible pixel data after

analog crop, bin and subsample

Image width after digital crop

Image height after digital crop

1 – DPCM/PCM Compression – Simple Predictor

2 – DPCM/PCM Compression – Advanced Predictor

Test pattern mode select

cursor color definition.R data.

cursor color definition.Gr data.

cursor color definition. B data.

cursor color definition Gb data

6'h00

R/W

○

○

4'h1

R/W

4'h1

R/W

5'h01

8'h01

8'hf4

5'h05

3'h2

4'h2

3'h0

8'hc8

5'h0a

2'h1

4'h2

3'h0

8'hc8

1'h0

8'h0c

8'h6c

8'h13

8'h90

5'h00

8'h00

4'h0

8'h00

5'h10

8'h6f

4'hc

8'h2f

5'h10

8'h70

4'hc

8'h30

1'h1

3'h1

3'h1

4'h1

4'h1

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

2'h0

R/W

2'h0

5'h00

8'h10

1'h0

8'h10

5'h00

8'h00

4'h0

8'h00

5'h10

8'h70

4'hc

8'h30

2'h1

1'h0

8'h00

2'h0

8'h00

2'h0

8'h00

2'h0

8'h00

2'h0

RO

R/W

R/W

RO

RO

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RO

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

�

7

7

7

7

7

7

7

7

7

0 TD_GB[7:0]

0x0609

0 H_CUR_WIDTH[15:8]

0x060a

0 H_CUR_WIDTH[7:0]

0x060b

0 H_CUR_POS[15:8]

0x060c

0 H_CUR_POS[7:0]

0x060d

0 V_CUR_WIDTH[15:8]

0x060e

0 V_CUR_WIDTH[7:0]

0x060f

0 V_CUR_POS[15:8]

0x0610

0 V_CUR_POS[7:0]

0x0611

FIFO Configuration Registers

0x0700

0x0701

CSI-2 Configuration Registers

0 FIFO_WATERMARK[15:8]

0 FIFO_WATERMARK[7:0]

7

7

0x0808

1

0 DPHY_CTRL

TCLK_POST_EX[8]

0 THS_TRAIL_EX[7:0]

0 THS_PREPARE_EX[7:0]

THS_ZERO_MIN_EX[8]

0 TCLK_POST_EX[7:0]

THS_PREPARE_EX[8]

0x080a

0x080b

0x080c

0x080d

0x080e

0x080f

0x0810

0x0811

0x0812

0x0813

0x0814

0x0815

0x0816

0x0817

0x0818

0x0819

Binning Configuration Registers

0x0820

0x0821

0x0822

0x0823

0x0900

0 TCLK_ZERO_EX[7:0]

TCLK_PREPARE_EX[8]

0

7

0

7

0

7

0

7

0

7

0

7

0

7

0

7

7

7

7

7

0

TCLK_ZERO_EX[8]

TLPX_EX[8]

0 TLPX_EX[7:0]

BINNING_MODE

0 THS_ZERO_MIN_EX[7:0]

THS_TRAIL_EX[8]

TCLK_TRAIL_MIN_EX[8]

0 TCLK_TRAIL_MIN_EX[7:0]

0 TCLK_PREPARE_EX[7:0]

0 REQ_LINK_BIT_RATE_MBPS[31:24]

0 REQ_LINK_BIT_RATE_MBPS[23:16]

0 REQ_LINK_BIT_RATE_MBPS[15:8]

0 REQ_LINK_BIT_RATE_MBPS[7:0]

0x0901

0x0901

0x0902

7

3

7

4 BINNING_TYPE_H

0 BINNING_TYPE_V

0 BINNING_WEIGHTING

ctrl_clr

ctrl_wen

ctrl_en

status_imprp

status_crptd

status_wrrdy

status_rdrdy

Data Upload/Download Configuration Registers

0x0a00

0x0a00

0x0a00

0x0a01

0x0a01

0x0a01

0x0a01

0x0a02

0x0a04

0x0a05

0x0a06

0x0a07

0x0a08

0x0a09

0x0a0a

0x0a0b

0x0a0c

0x0a0d

0x0a0e

0x0a0f

0x0a10

0x0a11

0x0a12

0x0a13

0x0a14

0x0a15

0x0a16

0x0a17

0x0a18

0x0a19

0x0a1a

0x0a1b

0x0a1c

0x0a1d

0x0a1e

0x0a1f

0x0a20

0x0a21

0x0a22

0x0a23

0x0a24

0 page

0 data0

0 data1

0 data2

0 data3

0 data4

0 data5

0 data6

0 data7

0 data8

0 data9

0 data10

0 data11

0 data12

0 data13

0 data14

0 data15

0 data16

0 data17

0 data18

0 data19

0 data20

0 data21

0 data22

0 data23

0 data24

0 data25

0 data26

0 data27

0 data28

0 data29

0 data30

0 data31

0 data32

2

1

0

3

2

1

0

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

cursor color definition. Gb data.

Test Cursor Control

defines the width of th horizontal cursor (in pixels)

Test Cursor Control

defines the top edge of the horizontal cursor

Test Cursor Control

defines the width of the vertical cursor

Test Cursor Control

defines the left hand edge of the vertical cursor.

FIFO usage level triggering CCP line output Format: 16-bit unsigned integer

REDUNDANT

Value 0: Use automatic control

Value 1: Use UI control

Value 2: Use register control

Global Timing Parameter

Global Timing Parameter

Global Timing Parameter

Global Timing Parameter

Global Timing Parameter

Global Timing Parameter

Global Timing Parameter

Global Timing Parameter

Target frequency (32-bit unsigned iReal)

0=None

1=Enabled

0x2=2x2binning

0x4=4x4binning

Other values ignored.

0x2=2x2binning

0x4=4x4binning

Other values ignored.

0x00: averaged weighting

0x01: summed (for low light)

0x02: bayer weighting

0x03: ignored

OTP control register

Initially, interface is disabled(ctrl.bit0=0), then status is all0.

Initially, interface is disabled(ctrl.bit0=0), then status is all0.

Initially, interface is disabled(ctrl.bit0=0), then status is all0.

Initially, interface is disabled(ctrl.bit0=0), then status is all0.

OTP control register

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

2'h1

1'h0

8'h00

1'h0

8'h00

1'h0

8'h00

1'h0

8'h00

1'h0

8'h00

1'h0

8'h00

1'h0

8'h00

1'h0

8'h00

8'h00

8'h00

8'h00

8'h00

1'h0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RO

RO

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

4'h0

R/W

4'h0

R/W

8'h00

R/W

1'h0

1'h0

1'h0

1'h0

1'h0

1'h0

1'h0

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

R/W

R/W

R/W

RO

RO

RO

RO

R/W

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

�

7

0x0a25

7

0x0a26

7

0x0a27

7

0x0a28

0x0a29

7

7

0x0a2a

7

0x0a2b

7

0x0a2c

7

0x0a2d

7

0x0a2e

7

0x0a2f

7

0x0a30

7

0x0a31

7

0x0a32

7

0x0a33

7

0x0a34

7

0x0a35

7

0x0a36

7

0x0a37

7

0x0a38

7

0x0a39

0x0a3a

7

7

0x0a3b

7

0x0a3c

7

0x0a3d

7

0x0a3e

7

0x0a3f

0x0a40

7

7

0x0a41

7

0x0a42

7

0x0a43

Ideal Raw

0x0b04

0

0 data33

0 data34

0 data35

0 data36

0 data37

0 data38

0 data39

0 data40

0 data41

0 data42

0 data43

0 data44

0 data45

0 data46

0 data47

0 data48

0 data49

0 data50

0 data51

0 data52

0 data53

0 data54

0 data55

0 data56

0 data57

0 data58

0 data59

0 data60

0 data61

0 data62

0 data63

BLK_LEV_CORR_EN

0x0b05

0

MAP_COUP_CORR_EN

0

SING_DEF_CORR_EN

0x0b06

Colour Temperature Feedback

0x0b8e

0 ABS_GAIN_GR[15:8]

0 ABS_GAIN_GR[7:0]

0x0b8f

0x0b90

0 ABS_GAIN_R[15:8]

0 ABS_GAIN_R[7:0]

0x0b91

0 ABS_GAIN_B[15:8]

0x0b92

0 ABS_GAIN_B[7:0]

0x0b93

0x0b94

0 ABS_GAIN_GB[15:8]

0x0b95

0 ABS_GAIN_GB[7:0]

Flash and special actuator control

0x0c12

0x0c14

0x0c15

0x0c16

0x0c17

0x0c18

0x0c19

0 FLASH_STRB_ADJ

0 FLASH_STRB_START_POINT[15:8]

0 FLASH_STRB_START_POINT[7:0]

0 TFLASH_STRB_DLY_RS_CTL[15:8]

0 TFLASH_STRB_DLY_RS_CTL[7:0]

0 TFLASH_STRB_WIDT_H_RS_CTL[15:8]

0 TFLASH_STRB_WIDT_H_RS_CTL[7:0]

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

0x0c1a

7

0 FLASH_MD_RS

0x0c1b

0x0c1c

7

7

0 FLASH_TRIG_RS

0 FLASH_STAT

7

7

7

7

7

0x0c26

0x0c27

0x0c28

0x0c29

0x0c2a

Bracketing Interface Configuration

0 TFLASH_STRB_WIDT2_H_RS_CTL[15:8]

0 TFLASH_STRB_WIDT2_H_RS_CTL[7:0]

0 TFLASH_STRB_WIDT_L_RS_CTL[15:8]

0 TFLASH_STRB_WIDT_L_RS_CTL[7:0]

0 TFLASH_STRB_CNT_RS_CTL

0x0e00

7

0 BRACKETING_LUT_CTL

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

Data for OTP write

0 – Black level correction disabled

1 – black level correction enabled default = 1

0 – Mapped couplet correction disabled

1 – Mapped couplet correction enabled

0 – dynamic singlet correction disabled

1 – dynamic singlet correction enabled

Calculated gain for green-red channel

Calculated gain for red channel

Calculated gain for blue channel

Calculated gain for greenb channel

Flash_strobe_adjustment 1-255

Register to select reference point for flash strobe. Adjustable in one line

steps.

Adjustable in one line steps.

Range 0 – last line

Used to control flash strobe width in rolling shutter mode 1-65535(INCK

domain)

Bit 0:

0 – Strobe usage in single trigger mode.

1 – Strobe usage in continuous mode.

Bit 1:

0 – Complete strobe mode in rolling shutter continuous mode.

1 – Truncated strobe in rolling shutter in continuous mode.

Bit 2:

0 – Start of exposure is reference point.

1 – Start of readout is reference point. Used with flash strobe in rolling

shutter mode.

Bit 3:

0 – Synchronous flash strobe.

1 – Asynchronous (not support)

Bit 4:

0-Reserved

Bit 5:

0 - Single Flash strobe.

1 - Multiple flash strobes

Bit 0:

1 – Trigger flash (auto clear in single mode).

0 – Disable strobe generation.

RO dynamic – in config section because needed in embedded line

Bit 0:

0 – Flash strobe is not retimed to this frame.

1 – Flash strobe is retimed to this frame.

Used to control flash strobe width of 2nd pulse for high period in rolling

shutter mode. Has effect only if flash strobe count rs ctrl is 2. 1-65535(INCK

Used to control flash strobe width for low period in rolling shutter mode 1-

65535(INCK domain)

Used to control flash strobe count in rolling shutter mode 1-255.

0 = disabled

1 …n = bracketing over n frames. Maximum value on n is

Bracketing_LUT_size.

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

1'h1

1'h1

1'h1

8'h01

8'h00

8'h01

8'h00

8'h01

8'h00

8'h01

8'h00

8'h01

8'h00

8'h00

8'h00

8'h00

8'h00

8'h01

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

○

○

○

○

○

○

○

○

○

○

○

○

○

8'h00

R/W

8'h00

R/W

○

8'h00

RO

8'h00

8'h01

8'h00

8'h01

8'h01

R/W

R/W

R/W

R/W

R/W

8'h00

R/W

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

�

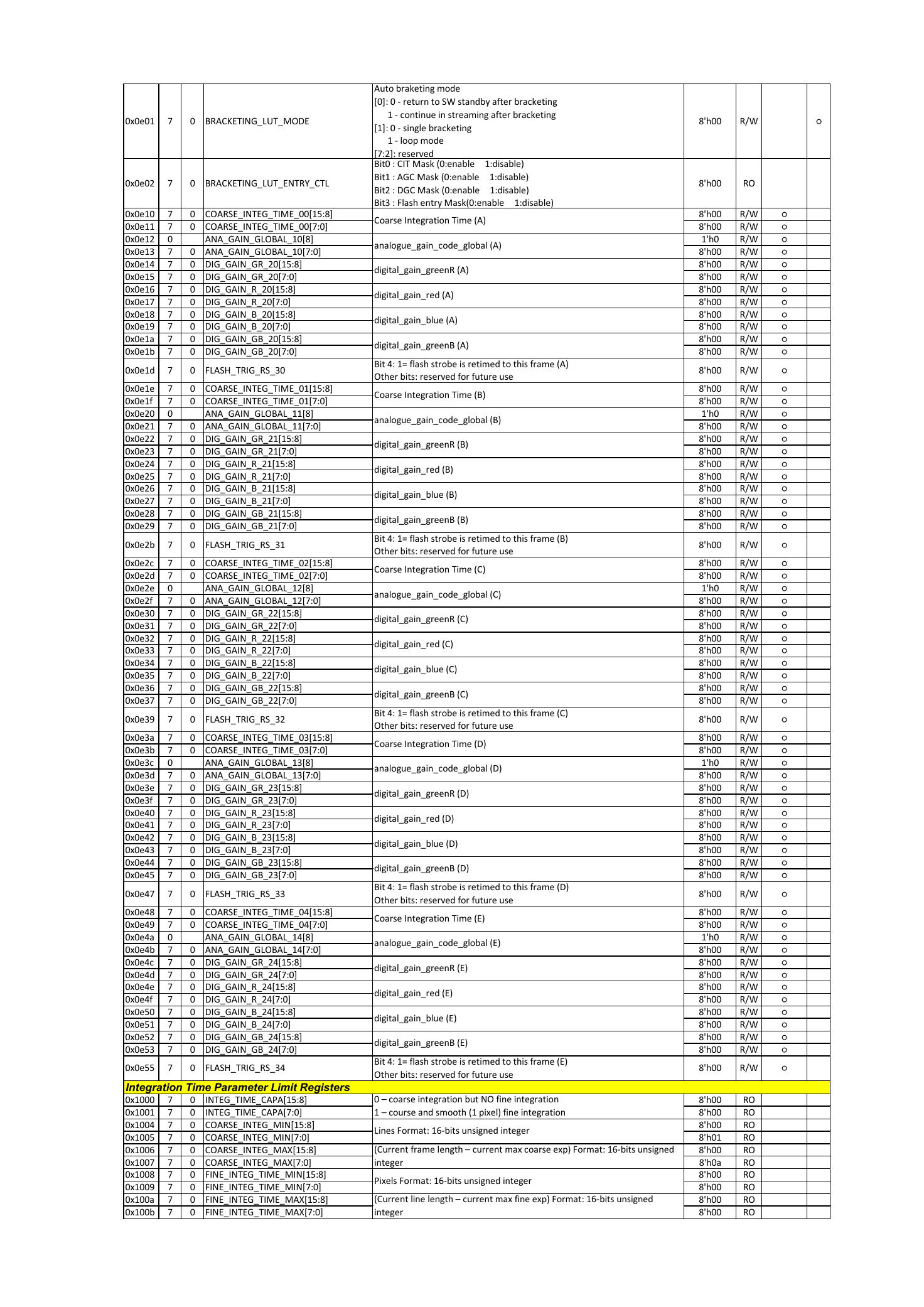

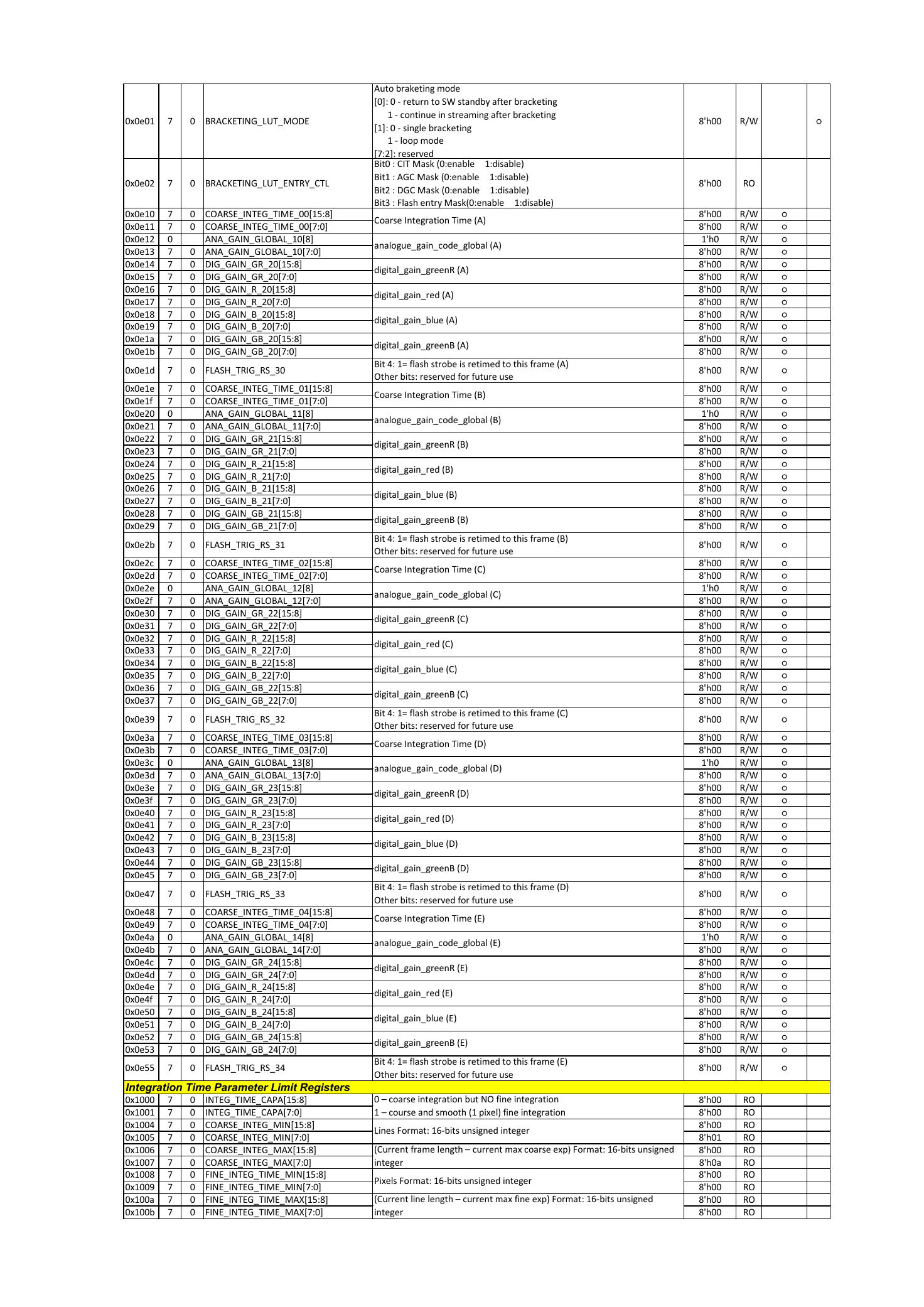

0x0e01

7

0 BRACKETING_LUT_MODE

0x0e02

7

0 BRACKETING_LUT_ENTRY_CTL

ANA_GAIN_GLOBAL_11[8]

ANA_GAIN_GLOBAL_12[8]

ANA_GAIN_GLOBAL_13[8]

0 COARSE_INTEG_TIME_00[15:8]

0 COARSE_INTEG_TIME_00[7:0]

ANA_GAIN_GLOBAL_10[8]

0 ANA_GAIN_GLOBAL_11[7:0]

0 DIG_GAIN_GR_21[15:8]

0 DIG_GAIN_GR_21[7:0]

0 DIG_GAIN_R_21[15:8]

0 DIG_GAIN_R_21[7:0]

0 DIG_GAIN_B_21[15:8]

0 DIG_GAIN_B_21[7:0]

0 DIG_GAIN_GB_21[15:8]

0 DIG_GAIN_GB_21[7:0]

0 FLASH_TRIG_RS_31

0 COARSE_INTEG_TIME_02[15:8]

0 COARSE_INTEG_TIME_02[7:0]

0 ANA_GAIN_GLOBAL_12[7:0]

0 DIG_GAIN_GR_22[15:8]

0 DIG_GAIN_GR_22[7:0]

0 DIG_GAIN_R_22[15:8]

0 DIG_GAIN_R_22[7:0]

0 DIG_GAIN_B_22[15:8]

0 DIG_GAIN_B_22[7:0]

0 DIG_GAIN_GB_22[15:8]

0 DIG_GAIN_GB_22[7:0]

0 FLASH_TRIG_RS_32

0 COARSE_INTEG_TIME_03[15:8]

0 COARSE_INTEG_TIME_03[7:0]

0 ANA_GAIN_GLOBAL_10[7:0]

0 DIG_GAIN_GR_20[15:8]

0 DIG_GAIN_GR_20[7:0]

0 DIG_GAIN_R_20[15:8]

0 DIG_GAIN_R_20[7:0]

0 DIG_GAIN_B_20[15:8]

0 DIG_GAIN_B_20[7:0]

0 DIG_GAIN_GB_20[15:8]

0 DIG_GAIN_GB_20[7:0]

0 FLASH_TRIG_RS_30

0 COARSE_INTEG_TIME_01[15:8]

0 COARSE_INTEG_TIME_01[7:0]

0x0e10

0x0e11

0x0e12

0x0e13

0x0e14

0x0e15

0x0e16

0x0e17

0x0e18

0x0e19

0x0e1a

0x0e1b

0x0e1d

0x0e1e

0x0e1f

0x0e20

0x0e21

0x0e22

0x0e23

0x0e24

0x0e25

0x0e26

0x0e27

0x0e28

0x0e29

0x0e2b

0x0e2c

0x0e2d

0x0e2e

0x0e2f

0x0e30

0x0e31

0x0e32

0x0e33

0x0e34

0x0e35

0x0e36

0x0e37

0x0e39

0x0e3a

0x0e3b

0x0e3c

0x0e3d

0x0e3e

0x0e3f

0x0e40

0x0e41

0x0e42

0x0e43

0x0e44

0x0e45

0x0e47

0x0e48

0x0e49

0x0e4a

0x0e4b

0x0e4c

0x0e4d

0x0e4e

0x0e4f

0x0e50

0x0e51

0x0e52

0x0e53

0x0e55

Integration Time Parameter Limit Registers

0x1000

0x1001

0x1004

0x1005

0x1006

0x1007

0x1008

0x1009

0x100a

0x100b

0 ANA_GAIN_GLOBAL_13[7:0]

0 DIG_GAIN_GR_23[15:8]

0 DIG_GAIN_GR_23[7:0]

0 DIG_GAIN_R_23[15:8]

0 DIG_GAIN_R_23[7:0]

0 DIG_GAIN_B_23[15:8]

0 DIG_GAIN_B_23[7:0]

0 DIG_GAIN_GB_23[15:8]

0 DIG_GAIN_GB_23[7:0]

0 FLASH_TRIG_RS_33

0 COARSE_INTEG_TIME_04[15:8]

0 COARSE_INTEG_TIME_04[7:0]

ANA_GAIN_GLOBAL_14[8]

0 ANA_GAIN_GLOBAL_14[7:0]

0 DIG_GAIN_GR_24[15:8]

0 DIG_GAIN_GR_24[7:0]

0 DIG_GAIN_R_24[15:8]

0 DIG_GAIN_R_24[7:0]

0 DIG_GAIN_B_24[15:8]

0 DIG_GAIN_B_24[7:0]

0 DIG_GAIN_GB_24[15:8]

0 DIG_GAIN_GB_24[7:0]

0 FLASH_TRIG_RS_34

0 INTEG_TIME_CAPA[15:8]

0 INTEG_TIME_CAPA[7:0]

0 COARSE_INTEG_MIN[15:8]

0 COARSE_INTEG_MIN[7:0]

0 COARSE_INTEG_MAX[15:8]

0 COARSE_INTEG_MAX[7:0]

0 FINE_INTEG_TIME_MIN[15:8]

0 FINE_INTEG_TIME_MIN[7:0]

0 FINE_INTEG_TIME_MAX[15:8]

0 FINE_INTEG_TIME_MAX[7:0]

7

7

0

7

7

7

7

7

7

7

7

7

7

7

7

0

7

7

7

7

7

7

7

7

7

7

7

7

0

7

7

7

7

7

7

7

7

7

7

7

7

0

7

7

7

7

7

7

7

7

7

7

7

7

0

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

Auto braketing mode

[0]: 0 - return to SW standby after bracketing

1 - continue in streaming after bracketing

[1]: 0 - single bracketing

1 - loop mode

[7:2]: reserved

Bit0 : CIT Mask (0:enable 1:disable)

Bit1 : AGC Mask (0:enable 1:disable)

Bit2 : DGC Mask (0:enable 1:disable)

Bit3 : Flash entry Mask(0:enable 1:disable)

Coarse Integration Time (A)

analogue_gain_code_global (A)

digital_gain_greenR (A)

digital_gain_red (A)

digital_gain_blue (A)

digital_gain_greenB (A)

Bit 4: 1= flash strobe is retimed to this frame (A)

Other bits: reserved for future use

Coarse Integration Time (B)

analogue_gain_code_global (B)

digital_gain_greenR (B)

digital_gain_red (B)

digital_gain_blue (B)

digital_gain_greenB (B)

Bit 4: 1= flash strobe is retimed to this frame (B)

Other bits: reserved for future use

Coarse Integration Time (C)

analogue_gain_code_global (C)

digital_gain_greenR (C)

digital_gain_red (C)

digital_gain_blue (C)

digital_gain_greenB (C)

Bit 4: 1= flash strobe is retimed to this frame (C)

Other bits: reserved for future use

Coarse Integration Time (D)

analogue_gain_code_global (D)

digital_gain_greenR (D)

digital_gain_red (D)

digital_gain_blue (D)

digital_gain_greenB (D)

Bit 4: 1= flash strobe is retimed to this frame (D)

Other bits: reserved for future use

Coarse Integration Time (E)

analogue_gain_code_global (E)

digital_gain_greenR (E)

digital_gain_red (E)

digital_gain_blue (E)

digital_gain_greenB (E)

Bit 4: 1= flash strobe is retimed to this frame (E)

Other bits: reserved for future use

0 – coarse integration but NO fine integration

1 – course and smooth (1 pixel) fine integration

Lines Format: 16-bits unsigned integer

(Current frame length – current max coarse exp) Format: 16-bits unsigned

integer

Pixels Format: 16-bits unsigned integer

(Current line length – current max fine exp) Format: 16-bits unsigned

integer

8'h00

R/W

○

8'h00

RO

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

8'h00

8'h00

1'h0

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

1'h0

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

1'h0

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

1'h0

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

1'h0

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h00

8'h01

8'h00

8'h0a

8'h00

8'h00

8'h00

8'h00

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

�

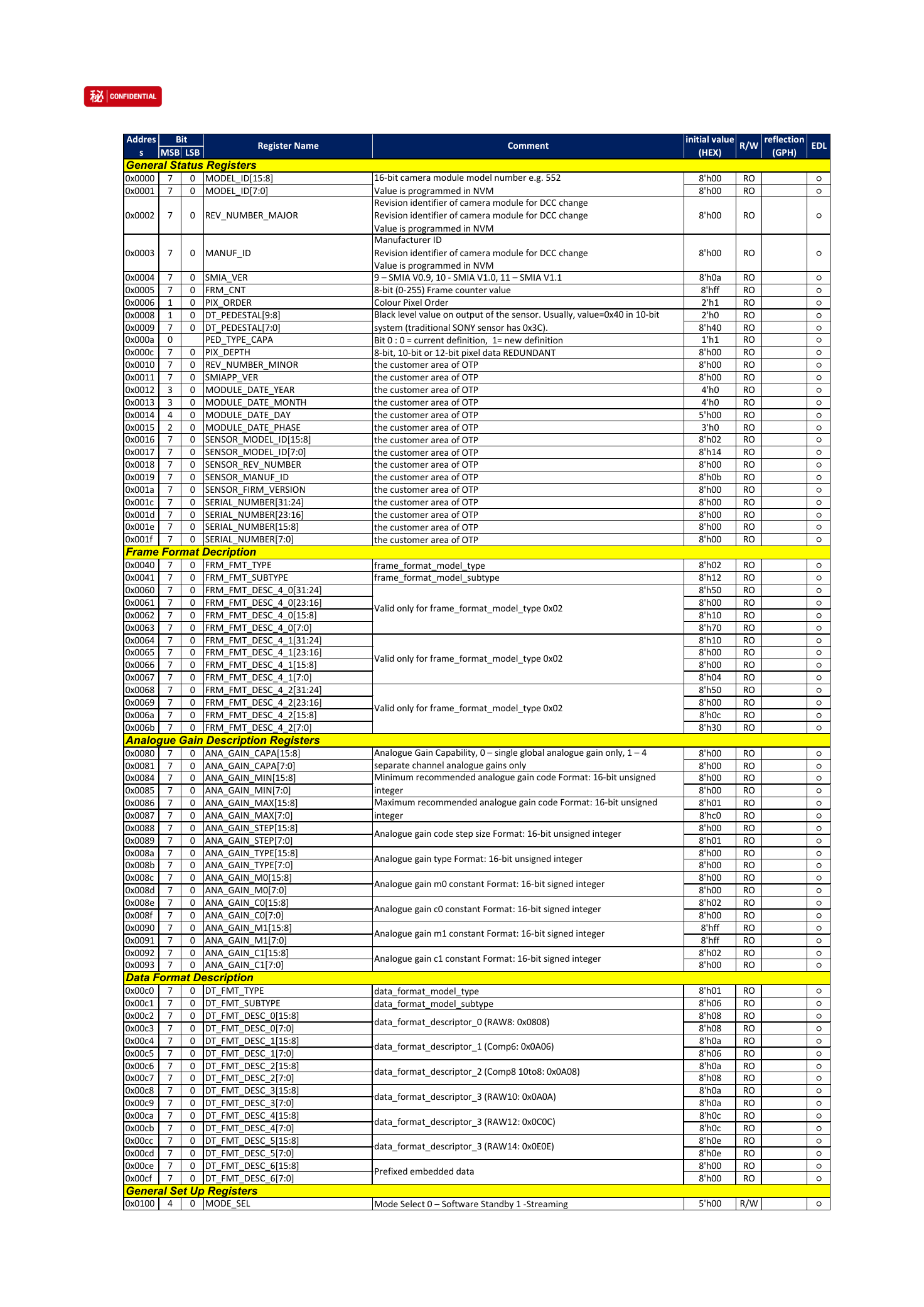

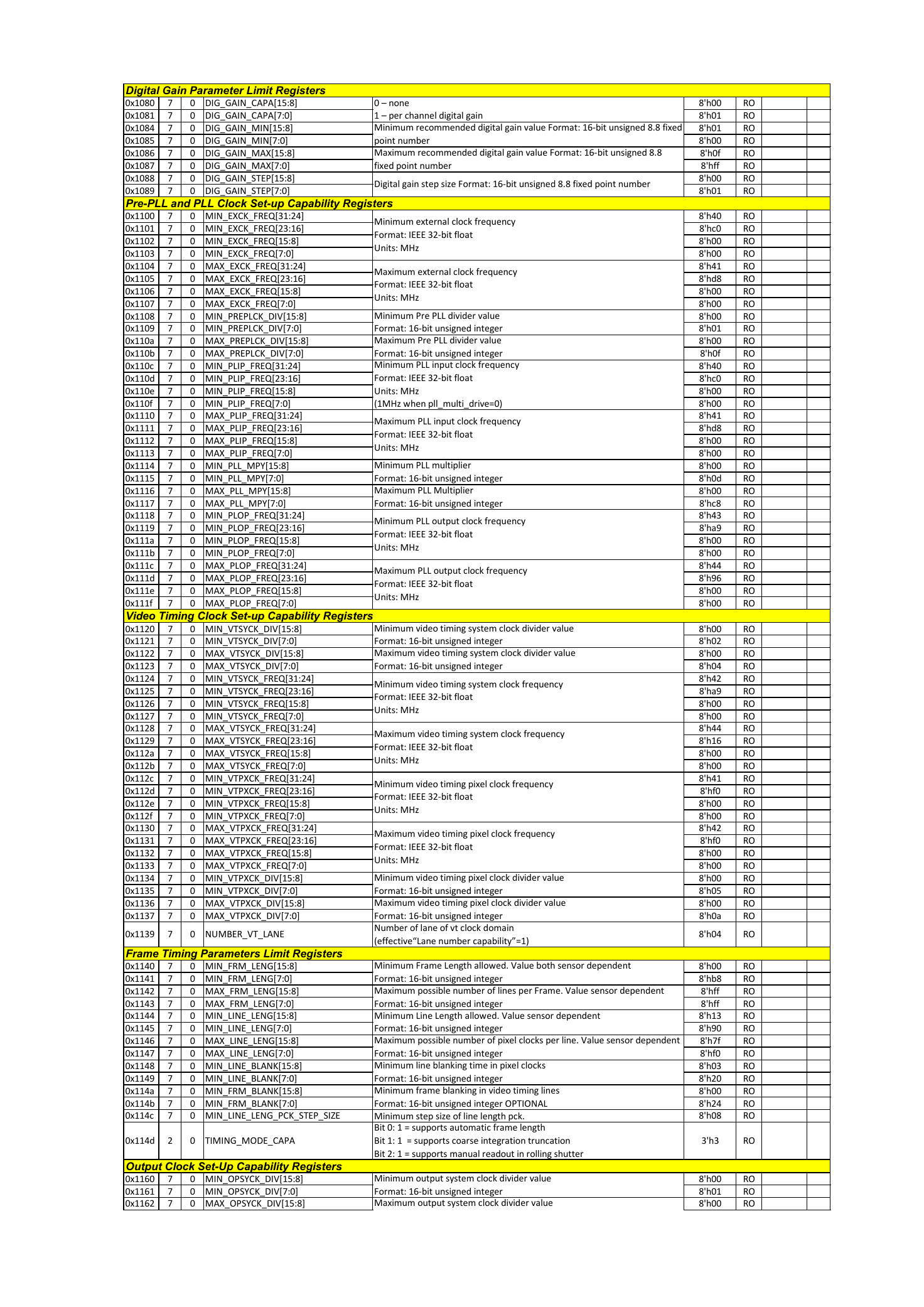

Minimum external clock frequency

Format: IEEE 32-bit float

Units: MHz

Maximum external clock frequency

Format: IEEE 32-bit float

Units: MHz

Minimum Pre PLL divider value

Format: 16-bit unsigned integer

Maximum Pre PLL divider value

Format: 16-bit unsigned integer

Minimum PLL input clock frequency

Format: IEEE 32-bit float

Units: MHz

(1MHz when pll_multi_drive=0)

Maximum PLL input clock frequency

Format: IEEE 32-bit float

Units: MHz

Minimum PLL multiplier

Format: 16-bit unsigned integer

Maximum PLL Multiplier

Format: 16-bit unsigned integer

Minimum PLL output clock frequency

Format: IEEE 32-bit float

Units: MHz

Maximum PLL output clock frequency

Format: IEEE 32-bit float

Units: MHz

Minimum video timing system clock divider value

Format: 16-bit unsigned integer

Maximum video timing system clock divider value

Format: 16-bit unsigned integer

Minimum video timing system clock frequency

Format: IEEE 32-bit float

Units: MHz

Maximum video timing system clock frequency

Format: IEEE 32-bit float

Units: MHz

Minimum video timing pixel clock frequency

Format: IEEE 32-bit float

Units: MHz

Maximum video timing pixel clock frequency

Format: IEEE 32-bit float

Units: MHz

Minimum video timing pixel clock divider value

Format: 16-bit unsigned integer

Maximum video timing pixel clock divider value

Format: 16-bit unsigned integer

Number of lane of vt clock domain

(effective“Lane number capability”=1)

0 DIG_GAIN_CAPA[15:8]

0 DIG_GAIN_CAPA[7:0]

0 DIG_GAIN_MIN[15:8]

0 DIG_GAIN_MIN[7:0]

0 DIG_GAIN_MAX[15:8]

0 DIG_GAIN_MAX[7:0]

0 DIG_GAIN_STEP[15:8]

0 DIG_GAIN_STEP[7:0]

0 MIN_EXCK_FREQ[31:24]

0 MIN_EXCK_FREQ[23:16]

0 MIN_EXCK_FREQ[15:8]

0 MIN_EXCK_FREQ[7:0]

0 MAX_EXCK_FREQ[31:24]

0 MAX_EXCK_FREQ[23:16]

0 MAX_EXCK_FREQ[15:8]

0 MAX_EXCK_FREQ[7:0]

0 MIN_PREPLCK_DIV[15:8]

0 MIN_PREPLCK_DIV[7:0]

0 MAX_PREPLCK_DIV[15:8]

0 MAX_PREPLCK_DIV[7:0]

0 MIN_PLIP_FREQ[31:24]

0 MIN_PLIP_FREQ[23:16]

0 MIN_PLIP_FREQ[15:8]

0 MIN_PLIP_FREQ[7:0]

0 MAX_PLIP_FREQ[31:24]

0 MAX_PLIP_FREQ[23:16]

0 MAX_PLIP_FREQ[15:8]

0 MAX_PLIP_FREQ[7:0]

0 MIN_PLL_MPY[15:8]

0 MIN_PLL_MPY[7:0]

0 MAX_PLL_MPY[15:8]

0 MAX_PLL_MPY[7:0]

0 MIN_PLOP_FREQ[31:24]

0 MIN_PLOP_FREQ[23:16]

0 MIN_PLOP_FREQ[15:8]

0 MIN_PLOP_FREQ[7:0]

0 MAX_PLOP_FREQ[31:24]

0 MAX_PLOP_FREQ[23:16]

0 MAX_PLOP_FREQ[15:8]

0 MAX_PLOP_FREQ[7:0]

Digital Gain Parameter Limit Registers

0x1080

0x1081

0x1084

0x1085

0x1086

0x1087

0x1088

0x1089

Pre-PLL and PLL Clock Set-up Capability Registers

0x1100

0x1101

0x1102

0x1103

0x1104

0x1105

0x1106

0x1107

0x1108

0x1109

0x110a

0x110b

0x110c

0x110d

0x110e

0x110f

0x1110

0x1111

0x1112

0x1113

0x1114

0x1115

0x1116

0x1117

0x1118

0x1119

0x111a

0x111b

0x111c

0x111d

0x111e

0x111f

Video Timing Clock Set-up Capability Registers

0x1120

0x1121

0x1122

0x1123

0x1124

0x1125

0x1126

0x1127

0x1128

0x1129

0x112a

0x112b

0x112c

0x112d

0x112e

0x112f

0x1130

0x1131

0x1132

0x1133

0x1134

0x1135

0x1136

0x1137

0x1139

Frame Timing Parameters Limit Registers

0x1140

0x1141

0x1142

0x1143

0x1144

0x1145

0x1146

0x1147

0x1148

0x1149

0x114a

0x114b

0x114c

0 MIN_VTSYCK_DIV[15:8]

0 MIN_VTSYCK_DIV[7:0]

0 MAX_VTSYCK_DIV[15:8]

0 MAX_VTSYCK_DIV[7:0]

0 MIN_VTSYCK_FREQ[31:24]

0 MIN_VTSYCK_FREQ[23:16]

0 MIN_VTSYCK_FREQ[15:8]

0 MIN_VTSYCK_FREQ[7:0]

0 MAX_VTSYCK_FREQ[31:24]

0 MAX_VTSYCK_FREQ[23:16]

0 MAX_VTSYCK_FREQ[15:8]

0 MAX_VTSYCK_FREQ[7:0]

0 MIN_VTPXCK_FREQ[31:24]

0 MIN_VTPXCK_FREQ[23:16]

0 MIN_VTPXCK_FREQ[15:8]

0 MIN_VTPXCK_FREQ[7:0]

0 MAX_VTPXCK_FREQ[31:24]

0 MAX_VTPXCK_FREQ[23:16]

0 MAX_VTPXCK_FREQ[15:8]

0 MAX_VTPXCK_FREQ[7:0]

0 MIN_VTPXCK_DIV[15:8]

0 MIN_VTPXCK_DIV[7:0]

0 MAX_VTPXCK_DIV[15:8]

0 MAX_VTPXCK_DIV[7:0]

0 NUMBER_VT_LANE

0 MIN_FRM_LENG[15:8]

0 MIN_FRM_LENG[7:0]

0 MAX_FRM_LENG[15:8]

0 MAX_FRM_LENG[7:0]

0 MIN_LINE_LENG[15:8]

0 MIN_LINE_LENG[7:0]

0 MAX_LINE_LENG[15:8]

0 MAX_LINE_LENG[7:0]

0 MIN_LINE_BLANK[15:8]

0 MIN_LINE_BLANK[7:0]

0 MIN_FRM_BLANK[15:8]

0 MIN_FRM_BLANK[7:0]

0 MIN_LINE_LENG_PCK_STEP_SIZE

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

0x114d

2

0 TIMING_MODE_CAPA

Output Clock Set-Up Capability Registers

0x1160

0x1161

0x1162

0 MIN_OPSYCK_DIV[15:8]

0 MIN_OPSYCK_DIV[7:0]

0 MAX_OPSYCK_DIV[15:8]

7

7

7

0 – none

1 – per channel digital gain

Minimum recommended digital gain value Format: 16-bit unsigned 8.8 fixed

point number

Maximum recommended digital gain value Format: 16-bit unsigned 8.8

fixed point number

Digital gain step size Format: 16-bit unsigned 8.8 fixed point number

Minimum Frame Length allowed. Value both sensor dependent

Format: 16-bit unsigned integer

Maximum possible number of lines per Frame. Value sensor dependent

Format: 16-bit unsigned integer

Minimum Line Length allowed. Value sensor dependent

Format: 16-bit unsigned integer

Maximum possible number of pixel clocks per line. Value sensor dependent

Format: 16-bit unsigned integer

Minimum line blanking time in pixel clocks

Format: 16-bit unsigned integer

Minimum frame blanking in video timing lines

Format: 16-bit unsigned integer OPTIONAL

Minimum step size of line length pck.

Bit 0: 1 = supports automatic frame length

Bit 1: 1 = supports coarse integration truncation

Bit 2: 1 = supports manual readout in rolling shutter

Minimum output system clock divider value

Format: 16-bit unsigned integer

Maximum output system clock divider value

8'h00

8'h01

8'h01

8'h00

8'h0f

8'hff

8'h00

8'h01

8'h40

8'hc0

8'h00

8'h00

8'h41

8'hd8

8'h00

8'h00

8'h00

8'h01

8'h00

8'h0f

8'h40

8'hc0

8'h00

8'h00

8'h41

8'hd8

8'h00

8'h00

8'h00

8'h0d

8'h00

8'hc8

8'h43

8'ha9

8'h00

8'h00

8'h44

8'h96

8'h00

8'h00

8'h00

8'h02

8'h00

8'h04

8'h42

8'ha9

8'h00

8'h00

8'h44

8'h16

8'h00

8'h00

8'h41

8'hf0

8'h00

8'h00

8'h42

8'hf0

8'h00

8'h00

8'h00

8'h05

8'h00

8'h0a

8'h04

8'h00

8'hb8

8'hff

8'hff

8'h13

8'h90

8'h7f

8'hf0

8'h03

8'h20

8'h00

8'h24

8'h08

3'h3

8'h00

8'h01

8'h00

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

�

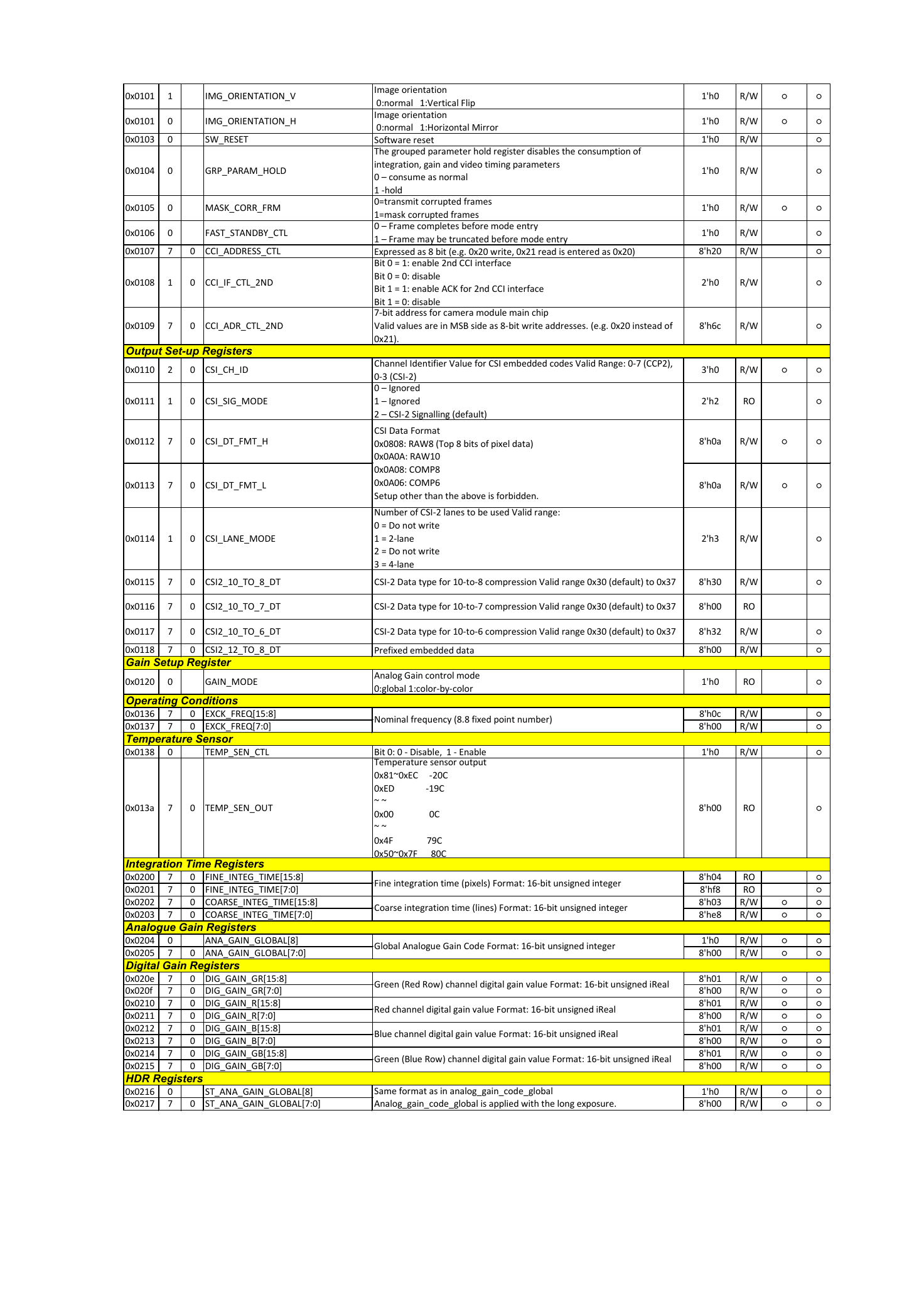

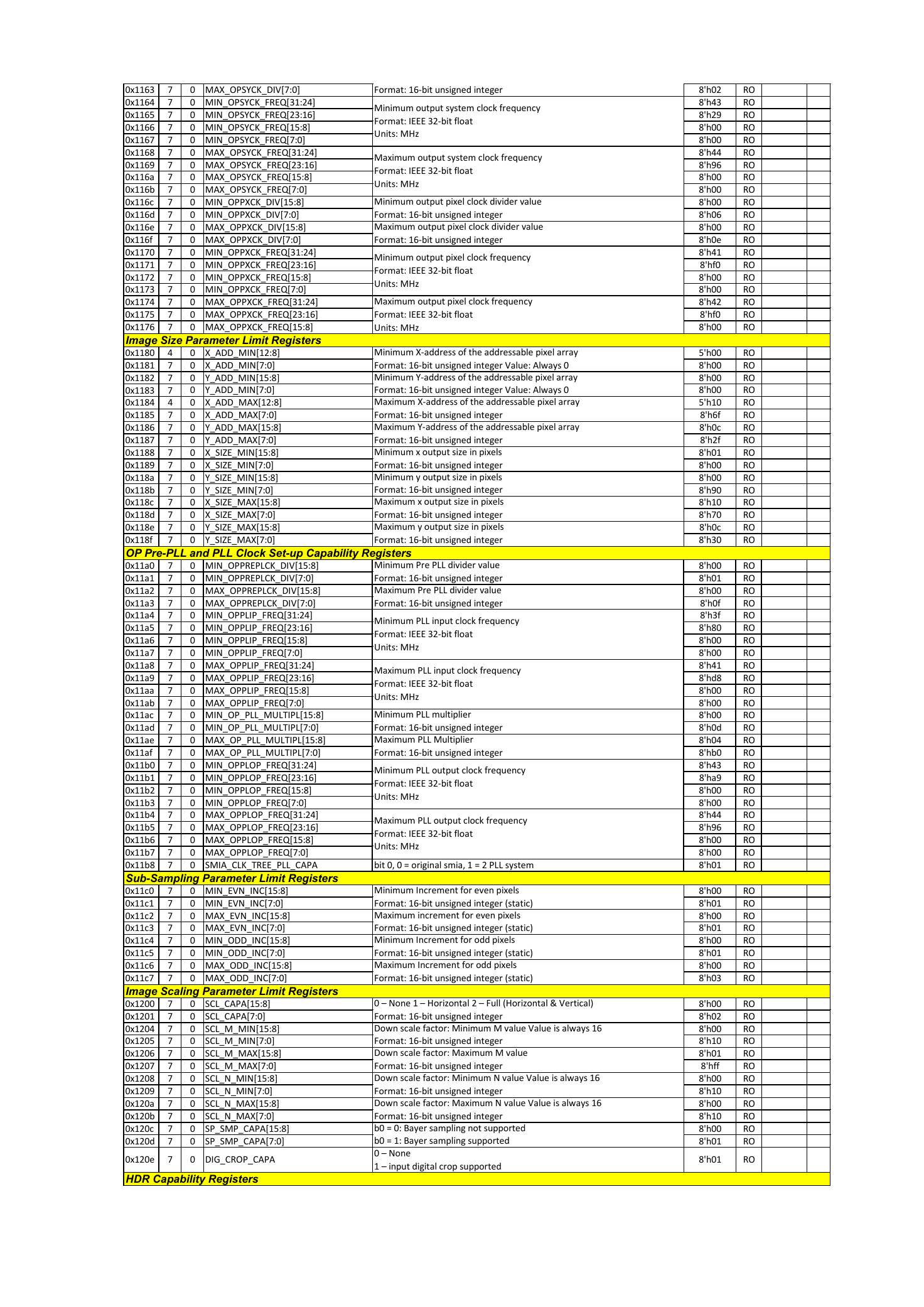

Format: 16-bit unsigned integer

Minimum output system clock frequency

Format: IEEE 32-bit float

Units: MHz

Maximum output system clock frequency

Format: IEEE 32-bit float

Units: MHz

Minimum output pixel clock divider value

Format: 16-bit unsigned integer

Maximum output pixel clock divider value

Format: 16-bit unsigned integer

Minimum output pixel clock frequency

Format: IEEE 32-bit float

Units: MHz

Maximum output pixel clock frequency

Format: IEEE 32-bit float

Units: MHz

Minimum X-address of the addressable pixel array

Format: 16-bit unsigned integer Value: Always 0

Minimum Y-address of the addressable pixel array

Format: 16-bit unsigned integer Value: Always 0

Maximum X-address of the addressable pixel array

Format: 16-bit unsigned integer

Maximum Y-address of the addressable pixel array

Format: 16-bit unsigned integer

Minimum x output size in pixels

Format: 16-bit unsigned integer

Minimum y output size in pixels

Format: 16-bit unsigned integer

Maximum x output size in pixels

Format: 16-bit unsigned integer

Maximum y output size in pixels

Format: 16-bit unsigned integer

4

7

7

7

4

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

0 X_ADD_MIN[12:8]

0 X_ADD_MIN[7:0]

0 Y_ADD_MIN[15:8]

0 Y_ADD_MIN[7:0]

0 X_ADD_MAX[12:8]

0 X_ADD_MAX[7:0]

0 Y_ADD_MAX[15:8]

0 Y_ADD_MAX[7:0]

0 X_SIZE_MIN[15:8]

0 X_SIZE_MIN[7:0]

0 Y_SIZE_MIN[15:8]

0 Y_SIZE_MIN[7:0]

0 X_SIZE_MAX[15:8]

0 X_SIZE_MAX[7:0]

0 Y_SIZE_MAX[15:8]

0 Y_SIZE_MAX[7:0]

0 MAX_OPSYCK_DIV[7:0]

0 MIN_OPSYCK_FREQ[31:24]

0 MIN_OPSYCK_FREQ[23:16]

0 MIN_OPSYCK_FREQ[15:8]

0 MIN_OPSYCK_FREQ[7:0]

0 MAX_OPSYCK_FREQ[31:24]

0 MAX_OPSYCK_FREQ[23:16]

0 MAX_OPSYCK_FREQ[15:8]

0 MAX_OPSYCK_FREQ[7:0]

0 MIN_OPPXCK_DIV[15:8]

0 MIN_OPPXCK_DIV[7:0]

0 MAX_OPPXCK_DIV[15:8]

0 MAX_OPPXCK_DIV[7:0]

0 MIN_OPPXCK_FREQ[31:24]

0 MIN_OPPXCK_FREQ[23:16]

0 MIN_OPPXCK_FREQ[15:8]

0 MIN_OPPXCK_FREQ[7:0]

0 MAX_OPPXCK_FREQ[31:24]

0 MAX_OPPXCK_FREQ[23:16]

0 MAX_OPPXCK_FREQ[15:8]

0x1163

0x1164

0x1165

0x1166

0x1167

0x1168

0x1169

0x116a

0x116b

0x116c

0x116d

0x116e

0x116f

0x1170

0x1171

0x1172

0x1173

0x1174

0x1175

0x1176

Image Size Parameter Limit Registers

0x1180

0x1181

0x1182

0x1183

0x1184

0x1185

0x1186

0x1187

0x1188

0x1189

0x118a

0x118b

0x118c

0x118d

0x118e

0x118f

OP Pre-PLL and PLL Clock Set-up Capability Registers

0x11a0

0x11a1

0x11a2

0x11a3

0x11a4

0x11a5

0x11a6

0x11a7

0x11a8

0x11a9

0x11aa

0x11ab

0x11ac

0x11ad

0x11ae

0x11af

0x11b0

0x11b1

0x11b2

0x11b3

0x11b4

0x11b5

0x11b6

0x11b7

0x11b8

Sub-Sampling Parameter Limit Registers

0x11c0

0x11c1

0x11c2

0x11c3

0x11c4

0x11c5

0x11c6

0x11c7

Image Scaling Parameter Limit Registers

0x1200

0x1201

0x1204

0x1205

0x1206

0x1207

0x1208

0x1209

0x120a

0x120b

0x120c

0x120d

0x120e

HDR Capability Registers

0 MIN_OPPREPLCK_DIV[15:8]

0 MIN_OPPREPLCK_DIV[7:0]

0 MAX_OPPREPLCK_DIV[15:8]

0 MAX_OPPREPLCK_DIV[7:0]

0 MIN_OPPLIP_FREQ[31:24]

0 MIN_OPPLIP_FREQ[23:16]

0 MIN_OPPLIP_FREQ[15:8]

0 MIN_OPPLIP_FREQ[7:0]

0 MAX_OPPLIP_FREQ[31:24]

0 MAX_OPPLIP_FREQ[23:16]

0 MAX_OPPLIP_FREQ[15:8]

0 MAX_OPPLIP_FREQ[7:0]

0 MIN_OP_PLL_MULTIPL[15:8]

0 MIN_OP_PLL_MULTIPL[7:0]

0 MAX_OP_PLL_MULTIPL[15:8]

0 MAX_OP_PLL_MULTIPL[7:0]

0 MIN_OPPLOP_FREQ[31:24]

0 MIN_OPPLOP_FREQ[23:16]

0 MIN_OPPLOP_FREQ[15:8]

0 MIN_OPPLOP_FREQ[7:0]

0 MAX_OPPLOP_FREQ[31:24]

0 MAX_OPPLOP_FREQ[23:16]

0 MAX_OPPLOP_FREQ[15:8]

0 MAX_OPPLOP_FREQ[7:0]

0 SMIA_CLK_TREE_PLL_CAPA

0 SCL_CAPA[15:8]

0 SCL_CAPA[7:0]

0 SCL_M_MIN[15:8]

0 SCL_M_MIN[7:0]

0 SCL_M_MAX[15:8]

0 SCL_M_MAX[7:0]

0 SCL_N_MIN[15:8]

0 SCL_N_MIN[7:0]

0 SCL_N_MAX[15:8]

0 SCL_N_MAX[7:0]

0 SP_SMP_CAPA[15:8]

0 SP_SMP_CAPA[7:0]

0 DIG_CROP_CAPA

0 MIN_EVN_INC[15:8]

0 MIN_EVN_INC[7:0]

0 MAX_EVN_INC[15:8]

0 MAX_EVN_INC[7:0]

0 MIN_ODD_INC[15:8]

0 MIN_ODD_INC[7:0]

0 MAX_ODD_INC[15:8]

0 MAX_ODD_INC[7:0]

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

Minimum Pre PLL divider value

Format: 16-bit unsigned integer

Maximum Pre PLL divider value

Format: 16-bit unsigned integer

Minimum PLL input clock frequency

Format: IEEE 32-bit float

Units: MHz

Maximum PLL input clock frequency

Format: IEEE 32-bit float

Units: MHz

Minimum PLL multiplier

Format: 16-bit unsigned integer

Maximum PLL Multiplier

Format: 16-bit unsigned integer

Minimum PLL output clock frequency

Format: IEEE 32-bit float

Units: MHz

Maximum PLL output clock frequency

Format: IEEE 32-bit float

Units: MHz

bit 0, 0 = original smia, 1 = 2 PLL system

Minimum Increment for even pixels

Format: 16-bit unsigned integer (static)

Maximum increment for even pixels

Format: 16-bit unsigned integer (static)

Minimum Increment for odd pixels

Format: 16-bit unsigned integer (static)

Maximum Increment for odd pixels

Format: 16-bit unsigned integer (static)

0 – None 1 – Horizontal 2 – Full (Horizontal & Vertical)

Format: 16-bit unsigned integer

Down scale factor: Minimum M value Value is always 16

Format: 16-bit unsigned integer

Down scale factor: Maximum M value

Format: 16-bit unsigned integer

Down scale factor: Minimum N value Value is always 16

Format: 16-bit unsigned integer

Down scale factor: Maximum N value Value is always 16

Format: 16-bit unsigned integer

b0 = 0: Bayer sampling not supported

b0 = 1: Bayer sampling supported

0 – None

1 – input digital crop supported

8'h02

8'h43

8'h29

8'h00

8'h00

8'h44

8'h96

8'h00

8'h00

8'h00

8'h06

8'h00

8'h0e

8'h41

8'hf0

8'h00

8'h00

8'h42

8'hf0

8'h00

5'h00

8'h00

8'h00

8'h00

5'h10

8'h6f

8'h0c

8'h2f

8'h01

8'h00

8'h00

8'h90

8'h10

8'h70

8'h0c

8'h30

8'h00

8'h01

8'h00

8'h0f

8'h3f

8'h80

8'h00

8'h00

8'h41

8'hd8

8'h00

8'h00

8'h00

8'h0d

8'h04

8'hb0

8'h43

8'ha9

8'h00

8'h00

8'h44

8'h96

8'h00

8'h00

8'h01

8'h00

8'h01

8'h00

8'h01

8'h00

8'h01

8'h00

8'h03

8'h00

8'h02

8'h00

8'h10

8'h01

8'hff

8'h00

8'h10

8'h00

8'h10

8'h00

8'h01

8'h01

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc