Keep safety first in your circuit designs!

Notes regarding these materials

Using This Manual

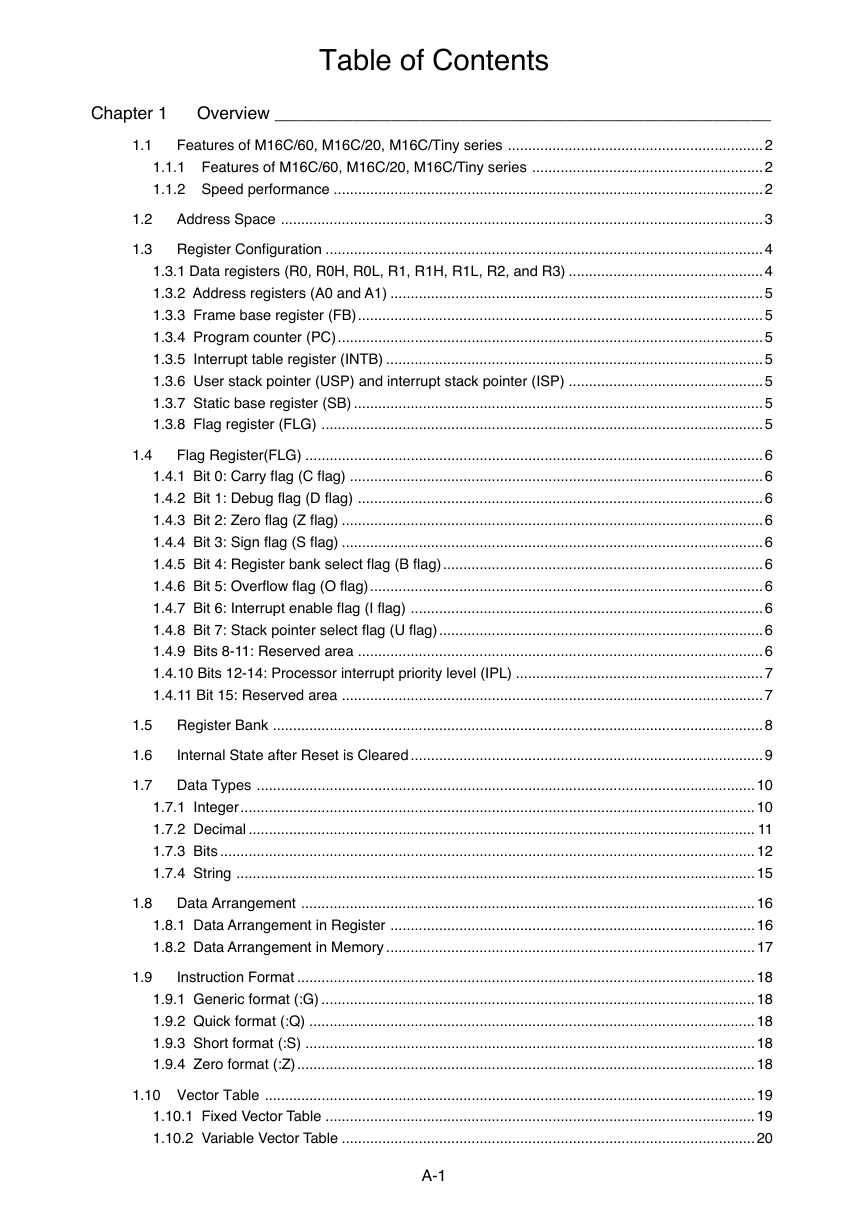

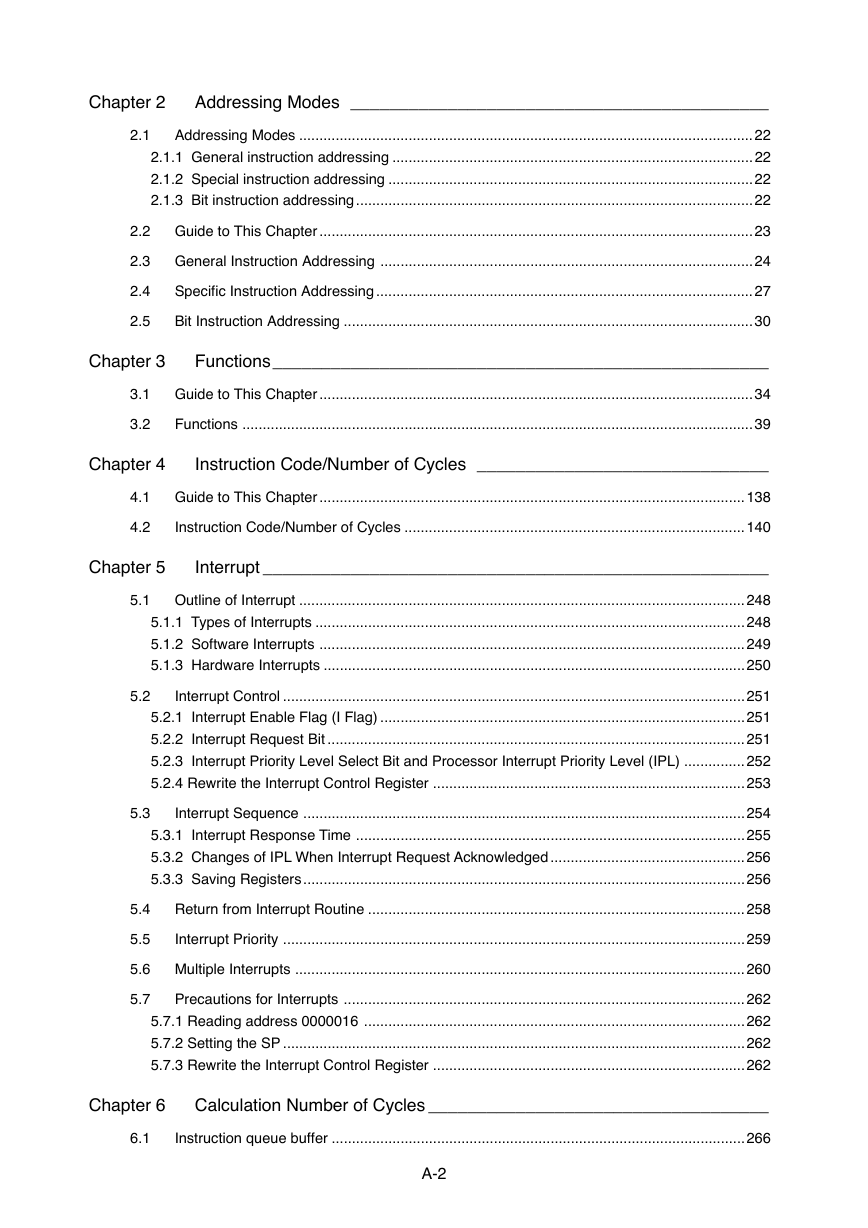

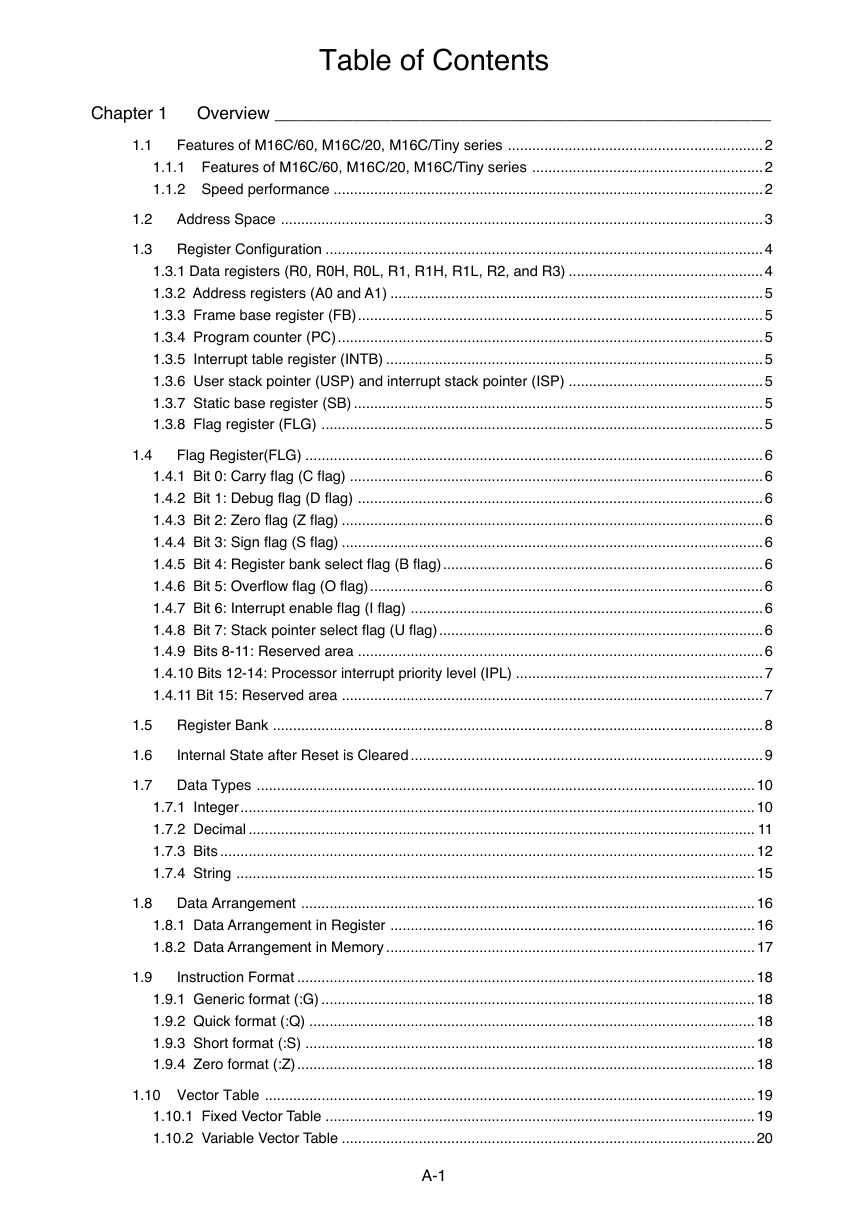

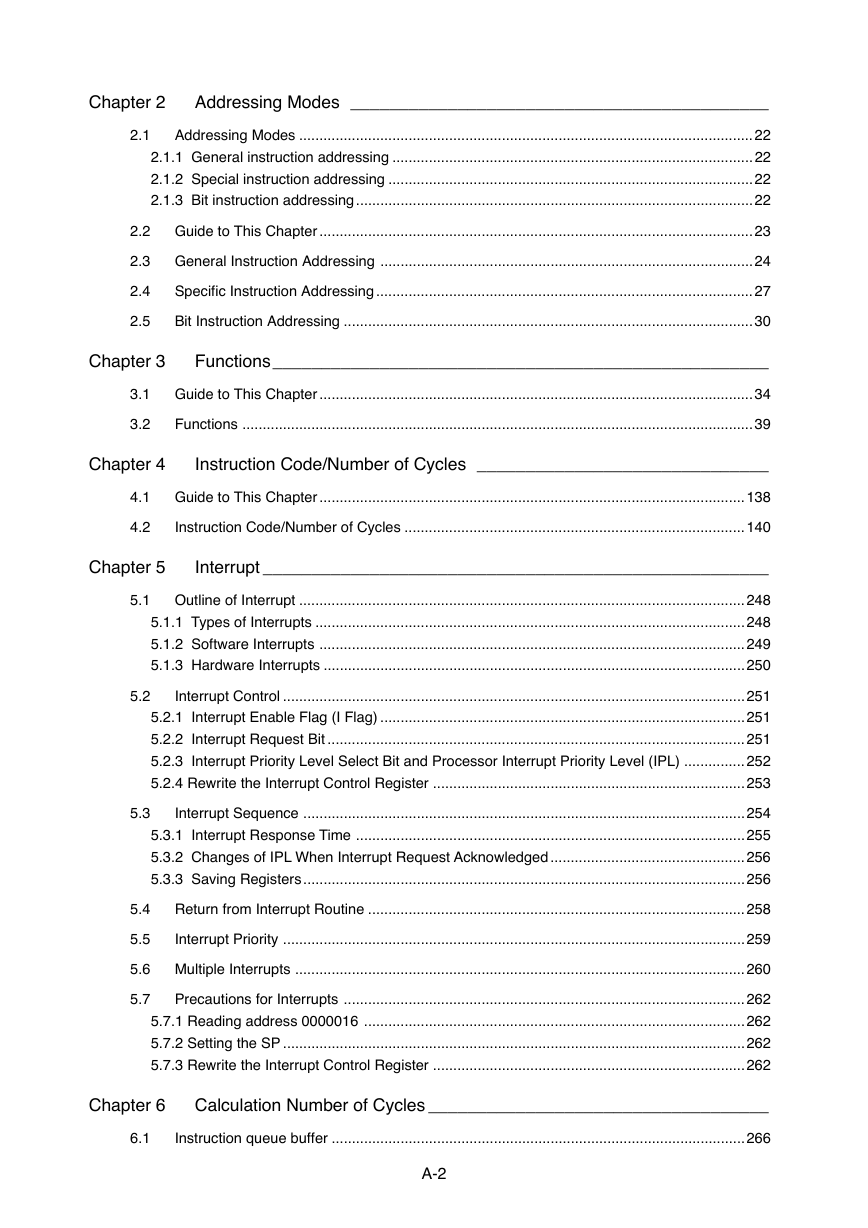

Table of Contents

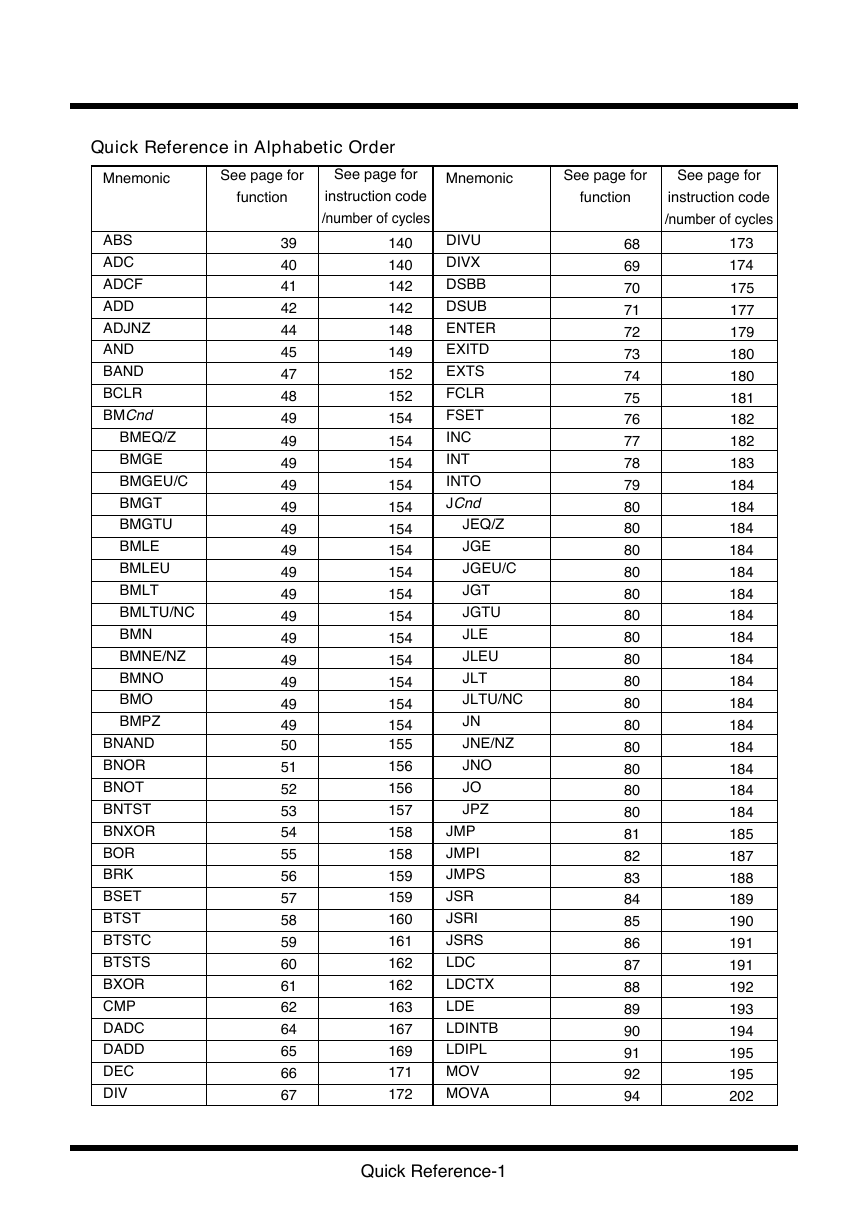

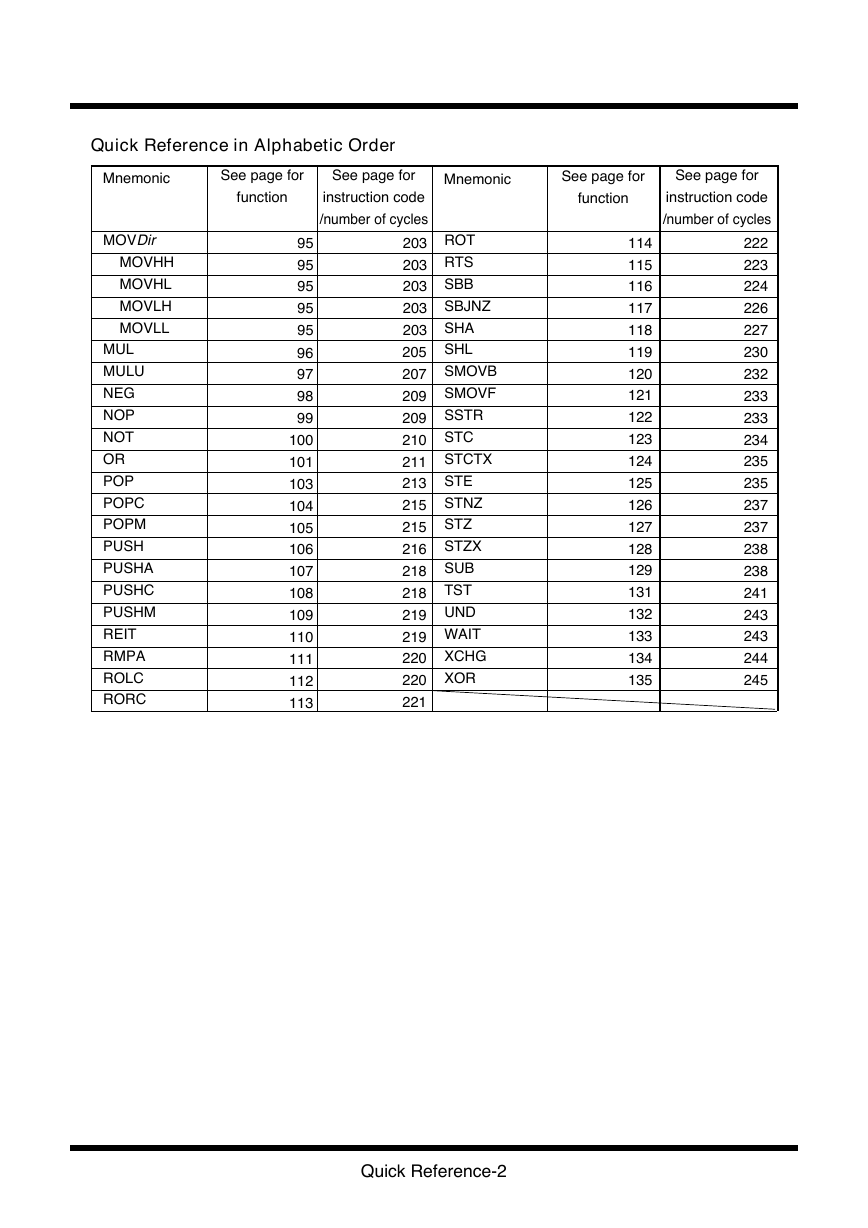

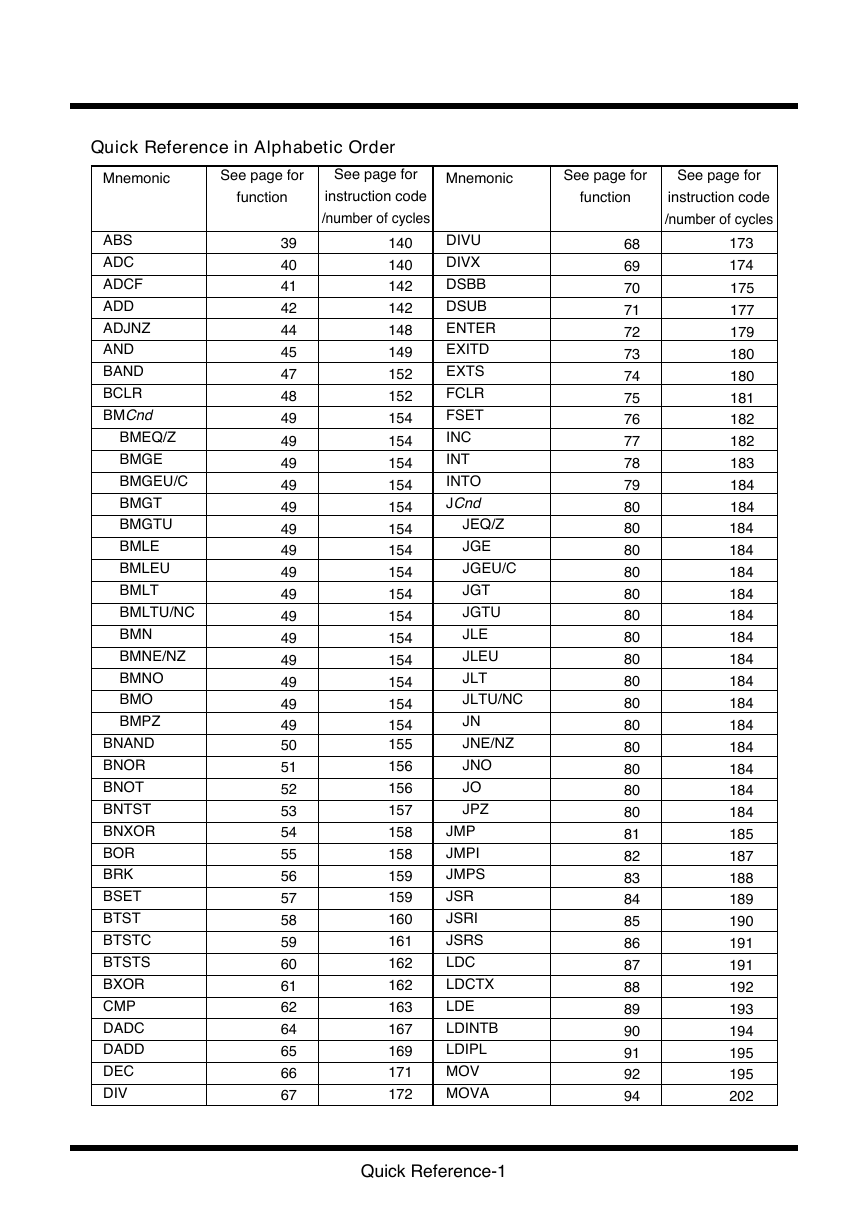

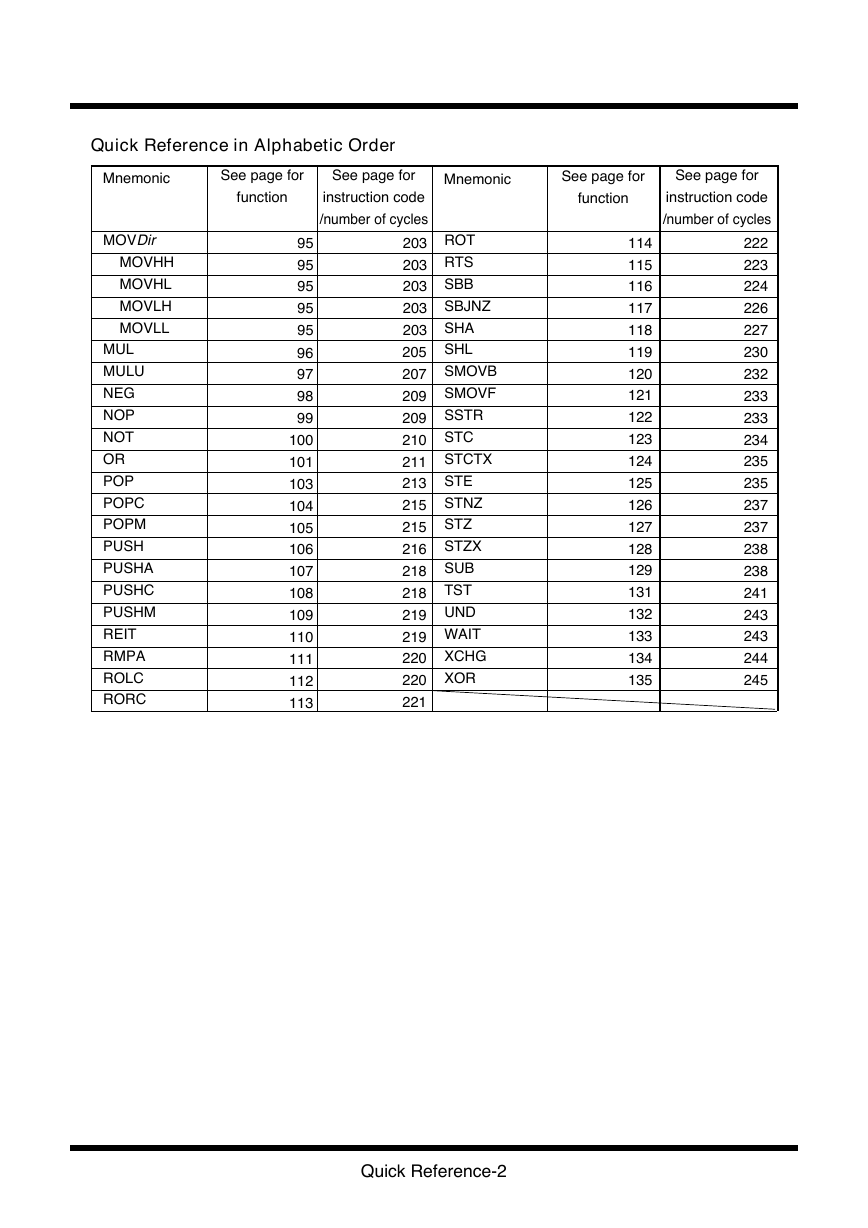

Quick Reference in Alphabetic Order

Quick Reference by Function

Quick Reference by Addressing (general instruction addressing)

Quick Reference by Addressing (special instruction addressing)

Quick Reference by Addressing (bit instruction addressing)

Chapter 1 Overview

1.1 Features of M16C/60,M16C/20,M16C/Tiny series

1.1.1 Features of M16C/60,M16C/20,M16C/Tiny series

1.1.2 Speed performance

1.2 Address Space

1.3 Register Configuration

1.3.1 Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, and R3)

1.3.2 Address registers (A0 and A1)

1.3.3 Frame base register (FB)

1.3.4 Program counter (PC)

1.3.5 Interrupt table register (INTB)

1.3.6 User stack pointer (USP) and interrupt stack pointer (ISP)

1.3.7 Static base register (SB)

1.3.8 Flag register (FLG)

1.4 Flag Register (FLG)

1.4.1 Bit 0: Carry flag (C flag)

1.4.2 Bit 1: Debug flag (D flag)

1.4.3 Bit 2: Zero flag (Z flag)

1.4.4 Bit 3: Sign flag (S flag)

1.4.5 Bit 4: Register bank select flag (B flag)

1.4.6 Bit 5: Overflow flag (O flag)

1.4.7 Bit 6: Interrupt enable flag (I flag)

1.4.8 Bit 7: Stack pointer select flag (U flag)

1.4.9 Bits 8-11: Reserved area

1.4.10 Bits 12-14: Processor interrupt priority level (IPL)

1.4.11 Bit 15: Reserved area

1.5 Register Bank

1.6 Internal State after Reset is Cleared

1.7 Data Types

1.7.1 Integer

1.7.2 Decimal

1.7.3 Bits

1.7.4 String

1.8 Data Arrangement

1.8.1 Data Arrangement in Register

1.8.2 Data Arrangement in Memory

1.9 Instruction Format

1.9.1 Generic format (:G)

1.9.2 Quick format (:Q)

1.9.3 Short format (:S)

1.9.4 Zero format (:Z)

1.10 Vector Table

1.10.1 Fixed Vector Table

1.10.2 Variable Vector Table

Chapter 2 Addressing Modes

2.1 Addressing Modes

2.1.1 General instruction addressing

2.1.2 Special instruction addressing

2.1.3 Bit instruction addressing

2.2 Guide to This Chapter

2.3 General Instruction Addressing

2.4 Special Instruction Addressing

2.5 Bit Instruction Addressing

Chapter 3 Functions

3.1 Guide to This Chapter

3.2 Functions

Chapter 4 Instruction Code/Number of Cycles

4.1 Guide to This Chapter

4.2 Instruction Code/Number of Cycles

Chapter 5 Interrupt

5.1 Outline of Interrupt

5.1.1 Types of Interrupts

5.1.2 Software Interrupts

5.1.3 Hardware Interrupts

5.2 Interrupt Control

5.2.1 Interrupt Enable Flag (I Flag)

5.2.2 Interrupt Request Bit

5.2.3 Interrupt Priority Level Select Bit and Processor Interrupt Priority Level (IPL)

5.2.4 Rewrite the Interrupt Control Register

5.3 Interrupt Sequence

5.3.1 Interrupt Response Time

5.3.2 Changes of IPL When Interrupt Request Acknowledged

5.3.3 Saving Registers

5.4 Return from Interrupt Routine

5.5 Interrupt Priority

5.6 Multiple Interrupts

5.7 Precautions for Interrupts

5.7.1 Reading address 0000016

5.7.2 Setting the SP

5.7.3 Rewrite the Interrupt Control Register

Chapter 6 Calculation Number of Cycles

6.1 Instruction queue buffer

Q & A

Glossary

Table of symbols

Index

REVISION HISTORY

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc