大规模集成电路秒表设计

专题实习报告

一、 实习题目:

大规模集成电路秒表设计

二、 模块名称:

计数器,控制逻辑,译码器,数据选择器

三、 实习目的:

对 quartusII 软件的使用,同时增强对 Verilog HDL 语言的编程与运用;将软件与硬件的使

用结合起来。掌握秒表设计的思路,各模块的设计方法,培养缜密的设计思想。

四、 模块源程序:

1、控制逻辑:

module miaoobiao(CLK,CLR,PAUSE,MSH,MSL,SH,SL,MH,ML);

input CLK,CLR,PAUSE; output[3:0] MSH,MSL,SH,SL,MH,ML;

reg[3:0] MSH,MSL,SH,SL,MH,ML;

reg cn1,cn2;

always @(posedge CLK or posedge CLR)

begin if(CLR) begin{MSH,MSL}<=8'h00; cn1<=0; end

else if(!PAUSE)

begin

if(MSL==9) begin MSL<=0;

if(MSH==9) begin MSH<=0; cn1<=1; end

else MSH<=MSH+1;

end

else begin MSL<=MSL+1; cn1<=0; end

end

end

always @(posedge cn1 or posedge CLR)

begin if(CLR) begin {SH,SL}<=8'h00; cn2<=0; end

if(SL==9)

else

begin SL<=0;

if(SH==5) begin SH<=0; cn2<=1; end

else

end

else begin SL<=SL+1;cn2<=0; end

SH<=SH+1;

end

always @(posedge cn2 or posedge CLR)

begin if(CLR) begin {MH,ML}<=8'h00;end

else

if(ML==9)

1

�

begin ML<=0;

if(MH==5) MH<=0;

else MH<=MH+1;

end

else ML<=ML+1;

end

Endmodule

2、计数器程序:

module jishuqi(clk,state);

input clk;

output[2:0]state;

reg [2:0]state;

always @(posedge clk)

if (state==5)

state=0;

else

state=state+1;

Endmodule

3、数据选择器源程序:

module mux6_1(out,in0,in1,in2,in3,in4,in5,sel);

input[3:0] in0,in1,in2,in3,in4,in5;

input[2:0] sel;

output[3:0] out; reg[3:0] out;

always @(in0 or in1 or in2 or sel)

begin case (sel)

3'b000:out=in1;

3'b001:out=in0;

3'b010:out=in3;

3'b011:out=in2;

3'b100:out=in5;

default:out=in4;

endcase

end

Endmodule

4.译码器

module decode47(decodeout,dec_in);

input[3:0] dec_in;

output[6:0] decodeout; reg[6:0] decodeout;

always @(dec_in)

begin case(dec_in)

4'd0:decodeout=7'b1111110;

2

�

4'd1:decodeout=7'b0110000;

4'd2:decodeout=7'b1101101;

4'd3:decodeout=7'b1111001;

4'd4:decodeout=7'b0110011;

4'd5:decodeout=7'b1011011;

4'd6:decodeout=7'b1011111;

4'd7:decodeout=7'b1110000;

4'd8:decodeout=7'b1111111;

4'd9:decodeout=7'b1111011;

default:decodeout=7'bx;

endcase

end

endmodule

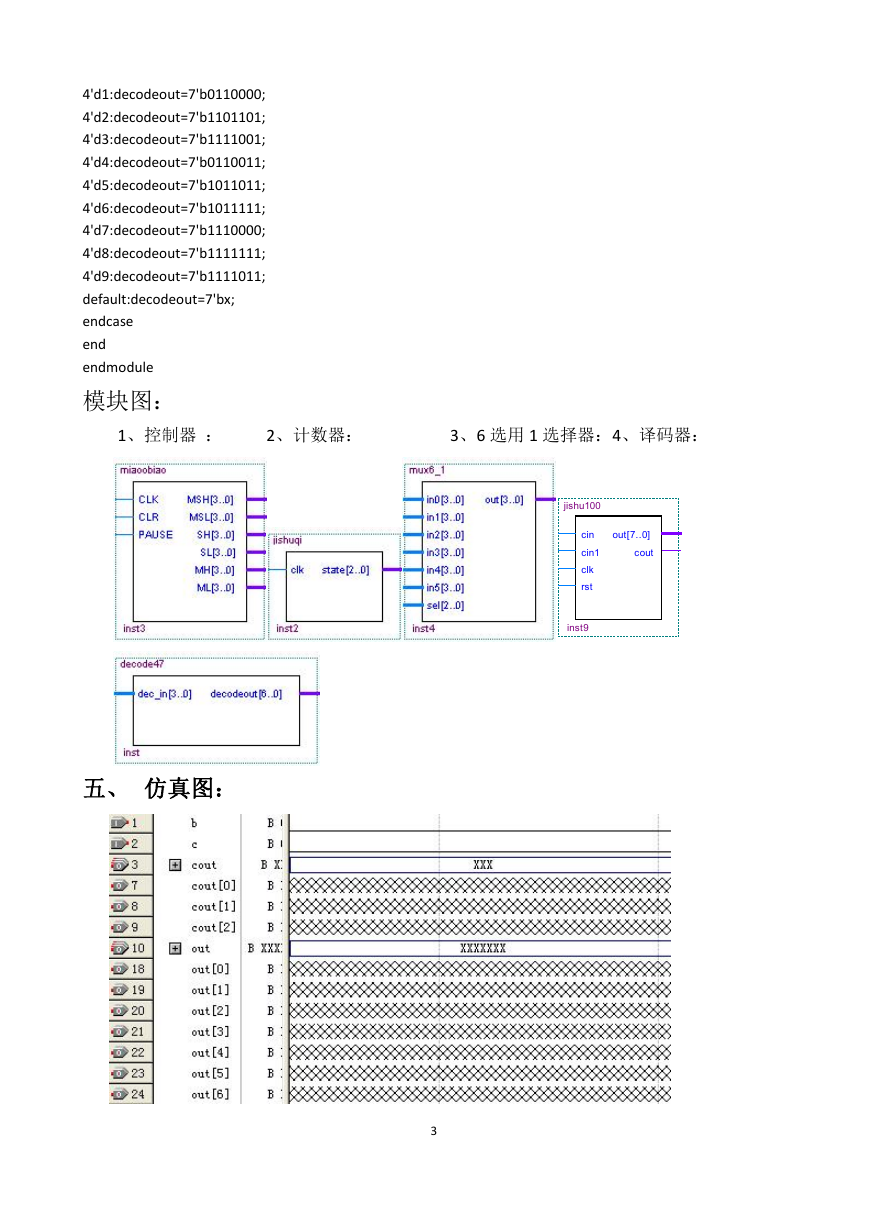

模块图:

1、控制器 :

2、计数器:

3、6 选用 1 选择器:4、译码器:

out[7..0]

cout

jishu100

cin

cin1

clk

rst

inst9

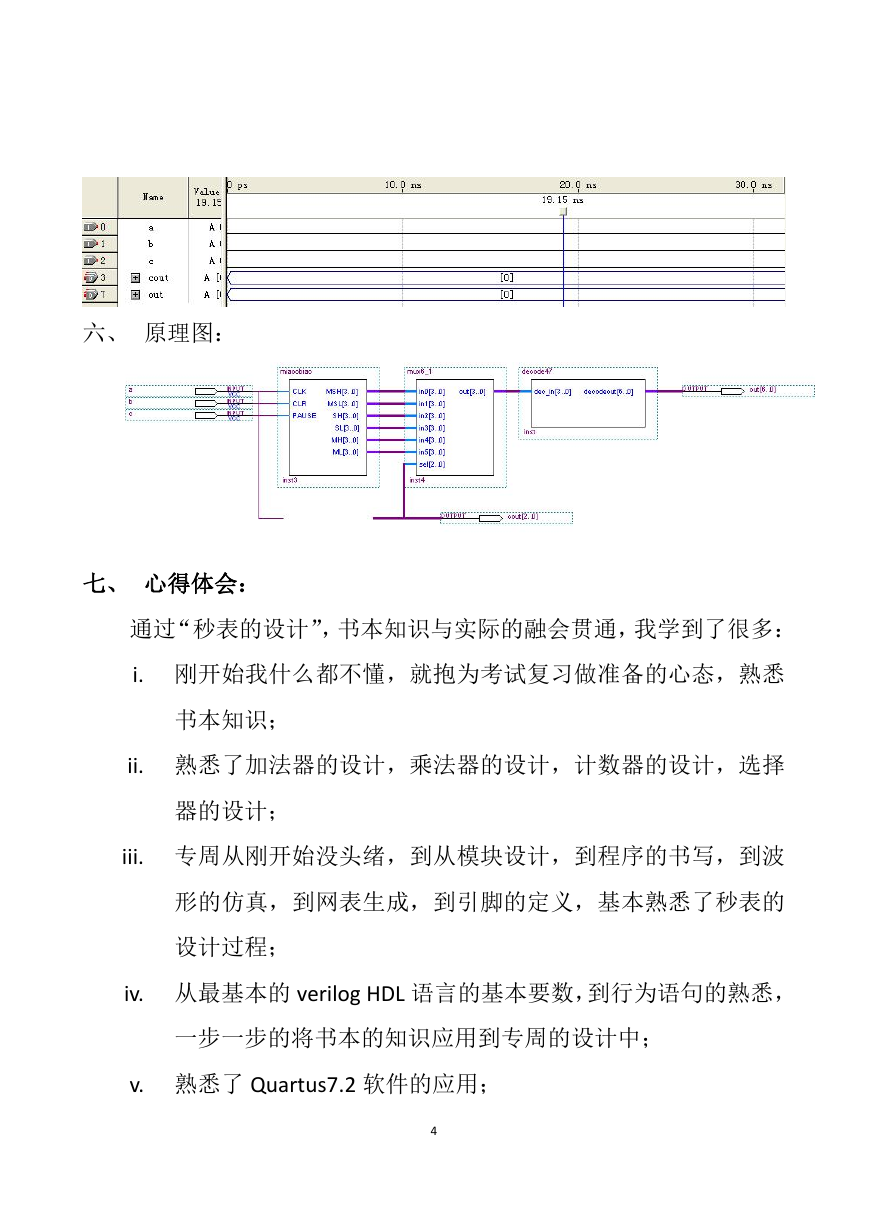

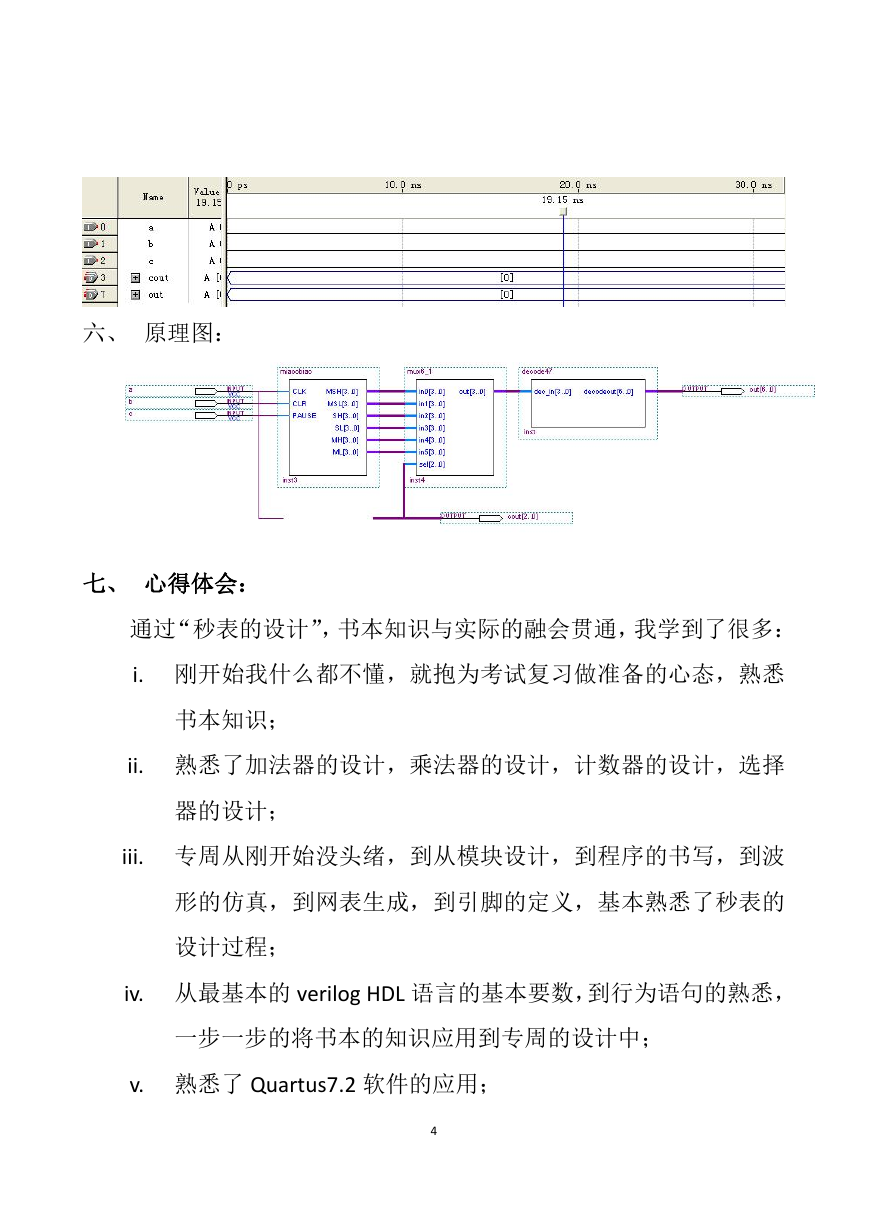

五、 仿真图:

3

�

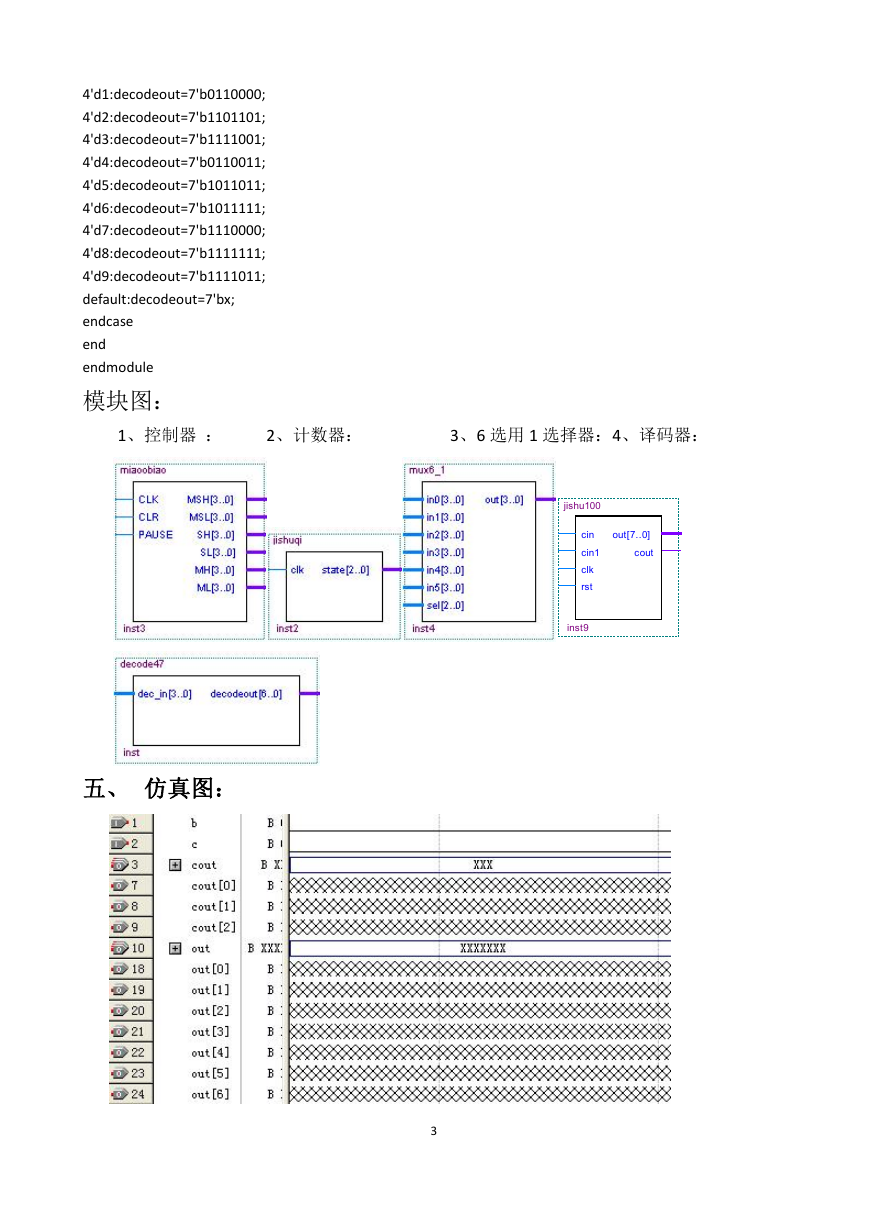

六、 原理图:

七、 心得体会:

通过“秒表的设计”,书本知识与实际的融会贯通,我学到了很多:

i. 刚开始我什么都不懂,就抱为考试复习做准备的心态,熟悉

书本知识;

ii. 熟悉了加法器的设计,乘法器的设计,计数器的设计,选择

器的设计;

iii. 专周从刚开始没头绪,到从模块设计,到程序的书写,到波

形的仿真,到网表生成,到引脚的定义,基本熟悉了秒表的

设计过程;

iv. 从最基本的 verilog HDL 语言的基本要数,到行为语句的熟悉,

一步一步的将书本的知识应用到专周的设计中;

v. 熟悉了 Quartus7.2 软件的应用;

4

�

vi.

Verilog HDL 过程赋值语句,“always”过程语句通常带触发条

件,assign 为持续赋值语句;

vii. 条件语句 case 多用于译码器,数据选择器中,一般 case(敏感

表达式);

viii. 复习了同步清零和异步清零的区别;

ix. 中间我们遇到的问题是怎么选位和怎么选段;

x. 以及怎么将编辑的模块联系起来;

5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc