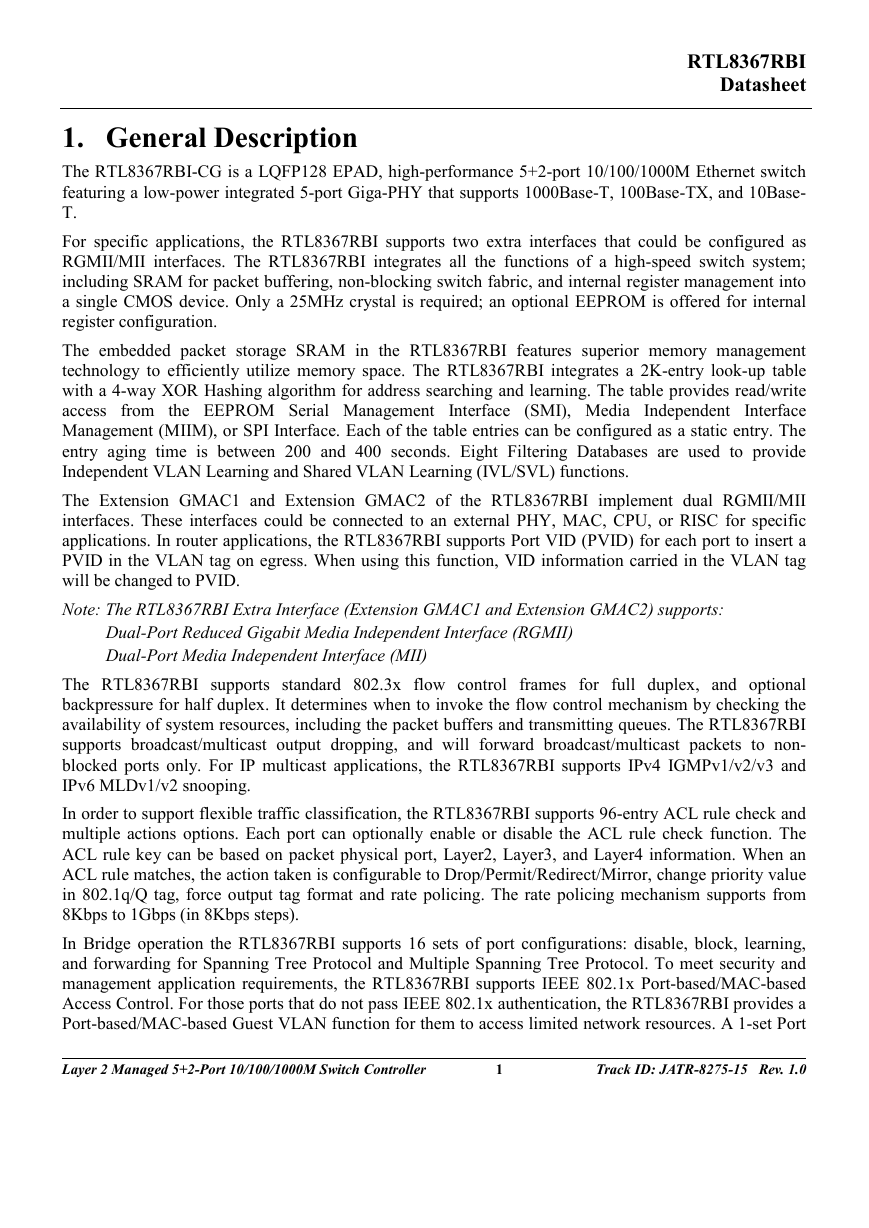

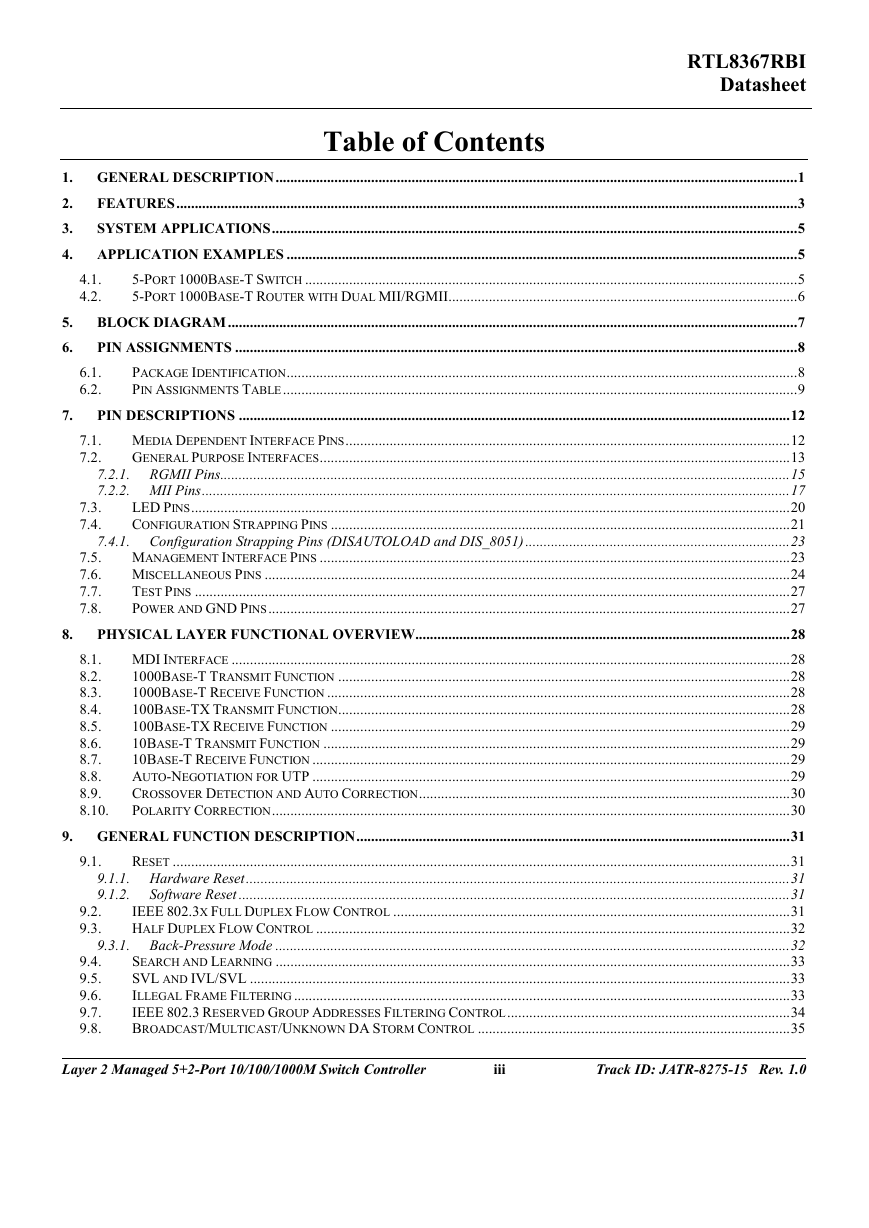

1. General Description

2. Features

3. System Applications

4. Application Examples

4.1. 5-Port 1000Base-T Switch

4.2. 5-Port 1000Base-T Router with Dual MII/RGMII

5. Block Diagram

6. Pin Assignments

6.1. Package Identification

6.2. Pin Assignments Table

7. Pin Descriptions

7.1. Media Dependent Interface Pins

7.2. General Purpose Interfaces

7.2.1. RGMII Pins

7.2.2. MII Pins

7.3. LED Pins

7.4. Configuration Strapping Pins

7.4.1. Configuration Strapping Pins (DISAUTOLOAD and DIS_8051)

7.5. Management Interface Pins

7.6. Miscellaneous Pins

7.7. Test Pins

7.8. Power and GND Pins

8. Physical Layer Functional Overview

8.1. MDI Interface

8.2. 1000Base-T Transmit Function

8.3. 1000Base-T Receive Function

8.4. 100Base-TX Transmit Function

8.5. 100Base-TX Receive Function

8.6. 10Base-T Transmit Function

8.7. 10Base-T Receive Function

8.8. Auto-Negotiation for UTP

8.9. Crossover Detection and Auto Correction

8.10. Polarity Correction

9. General Function Description

9.1. Reset

9.1.1. Hardware Reset

9.1.2. Software Reset

9.1.2.1 CHIP_RESET

9.1.2.2 SOFT_RESET

9.2. IEEE 802.3x Full Duplex Flow Control

9.3. Half Duplex Flow Control

9.3.1. Back-Pressure Mode

9.4. Search and Learning

9.5. SVL and IVL/SVL

9.6. Illegal Frame Filtering

9.7. IEEE 802.3 Reserved Group Addresses Filtering Control

9.8. Broadcast/Multicast/Unknown DA Storm Control

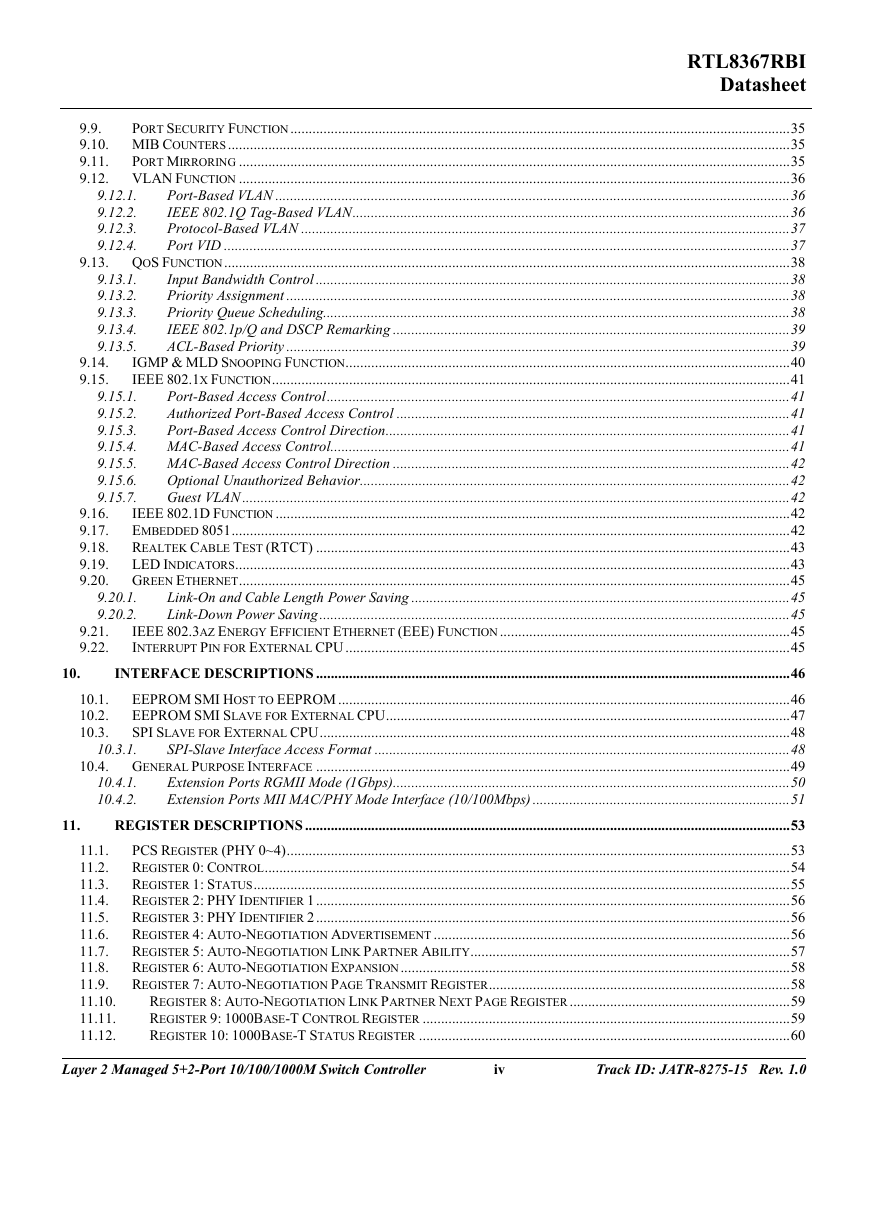

9.9. Port Security Function

9.10. MIB Counters

9.11. Port Mirroring

9.12. VLAN Function

9.12.1. Port-Based VLAN

9.12.2. IEEE 802.1Q Tag-Based VLAN

9.12.3. Protocol-Based VLAN

9.12.4. Port VID

9.13. QoS Function

9.13.1. Input Bandwidth Control

9.13.2. Priority Assignment

9.13.3. Priority Queue Scheduling

9.13.4. IEEE 802.1p/Q and DSCP Remarking

9.13.5. ACL-Based Priority

9.14. IGMP & MLD Snooping Function

9.15. IEEE 802.1x Function

9.15.1. Port-Based Access Control

9.15.2. Authorized Port-Based Access Control

9.15.3. Port-Based Access Control Direction

9.15.4. MAC-Based Access Control

9.15.5. MAC-Based Access Control Direction

9.15.6. Optional Unauthorized Behavior

9.15.7. Guest VLAN

9.16. IEEE 802.1D Function

9.17. Embedded 8051

9.18. Realtek Cable Test (RTCT)

9.19. LED Indicators

9.20. Green Ethernet

9.20.1. Link-On and Cable Length Power Saving

9.20.2. Link-Down Power Saving

9.21. IEEE 802.3az Energy Efficient Ethernet (EEE) Function

9.22. Interrupt Pin for External CPU

10. Interface Descriptions

10.1. EEPROM SMI Host to EEPROM

10.2. EEPROM SMI Slave for External CPU

10.3. SPI Slave for External CPU

10.3.1. SPI-Slave Interface Access Format

10.4. General Purpose Interface

10.4.1. Extension Ports RGMII Mode (1Gbps)

10.4.2. Extension Ports MII MAC/PHY Mode Interface (10/100Mbps)

11. Register Descriptions

11.1. PCS Register (PHY 0~4)

11.2. Register 0: Control

11.3. Register 1: Status

11.4. Register 2: PHY Identifier 1

11.5. Register 3: PHY Identifier 2

11.6. Register 4: Auto-Negotiation Advertisement

11.7. Register 5: Auto-Negotiation Link Partner Ability

11.8. Register 6: Auto-Negotiation Expansion

11.9. Register 7: Auto-Negotiation Page Transmit Register

11.10. Register 8: Auto-Negotiation Link Partner Next Page Register

11.11. Register 9: 1000Base-T Control Register

11.12. Register 10: 1000Base-T Status Register

11.13. Register 15: Extended Status

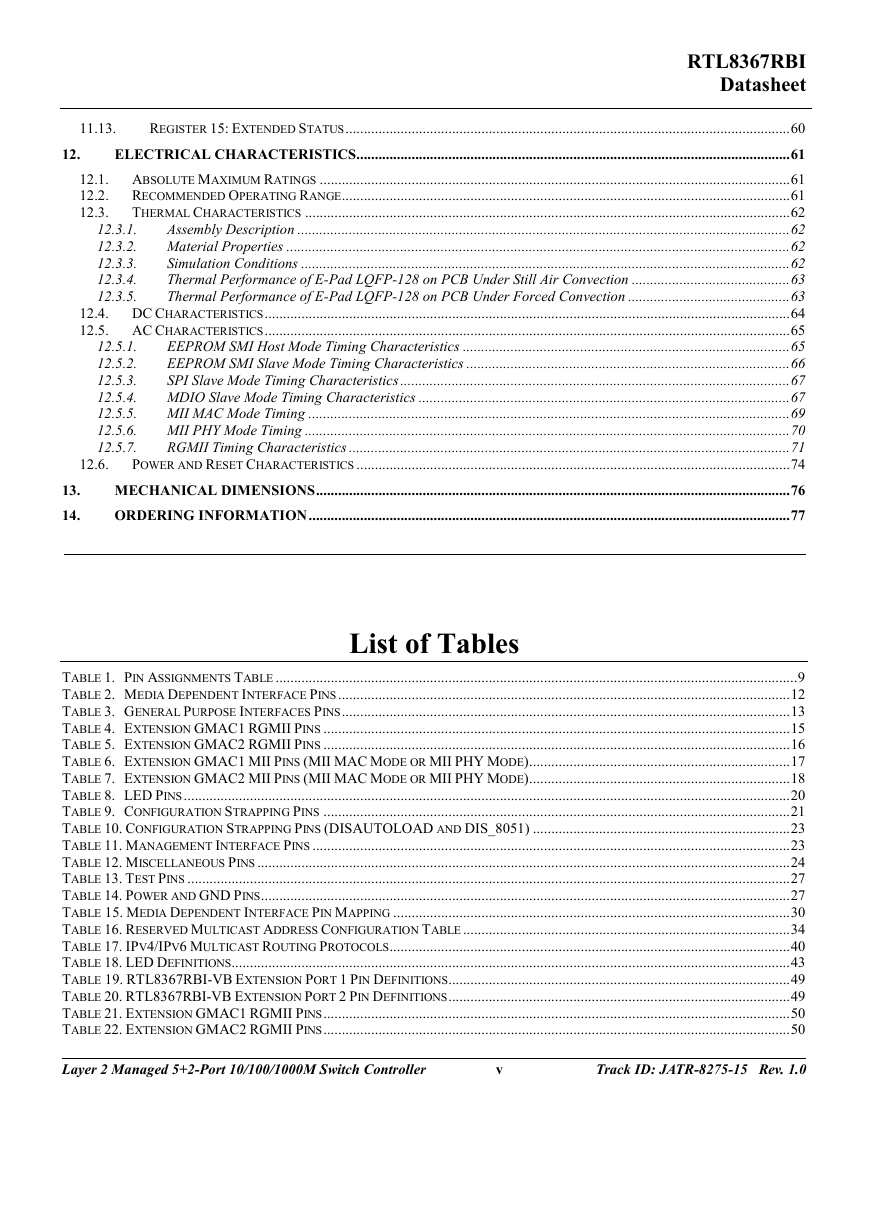

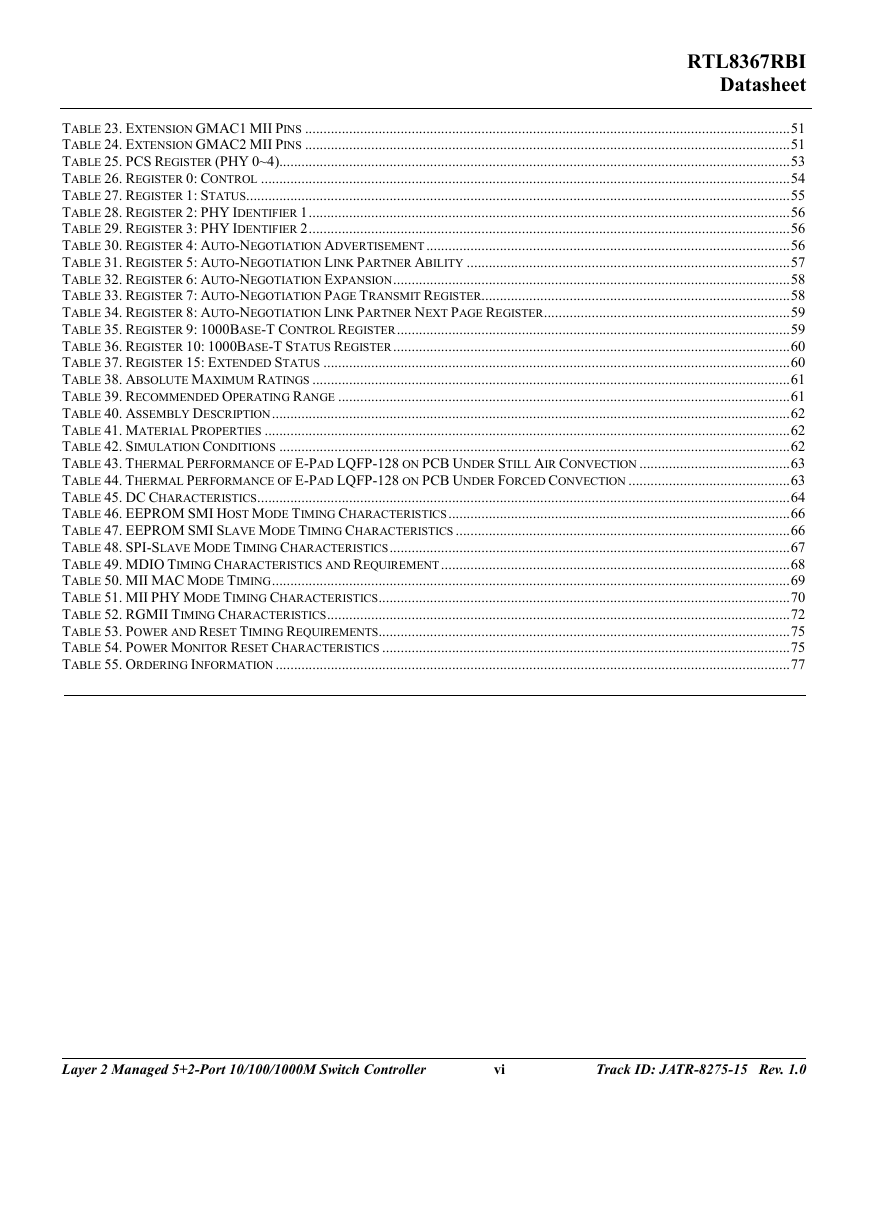

12. Electrical Characteristics

12.1. Absolute Maximum Ratings

12.2. Recommended Operating Range

12.3. Thermal Characteristics

12.3.1. Assembly Description

12.3.2. Material Properties

12.3.3. Simulation Conditions

12.3.4. Thermal Performance of E-Pad LQFP-128 on PCB Under Still Air Convection

12.3.5. Thermal Performance of E-Pad LQFP-128 on PCB Under Forced Convection

12.4. DC Characteristics

12.5. AC Characteristics

12.5.1. EEPROM SMI Host Mode Timing Characteristics

12.5.2. EEPROM SMI Slave Mode Timing Characteristics

12.5.3. SPI Slave Mode Timing Characteristics

12.5.4. MDIO Slave Mode Timing Characteristics

12.5.5. MII MAC Mode Timing

12.5.6. MII PHY Mode Timing

12.5.7. RGMII Timing Characteristics

12.6. Power and Reset Characteristics

13. Mechanical Dimensions

14. Ordering Information

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc