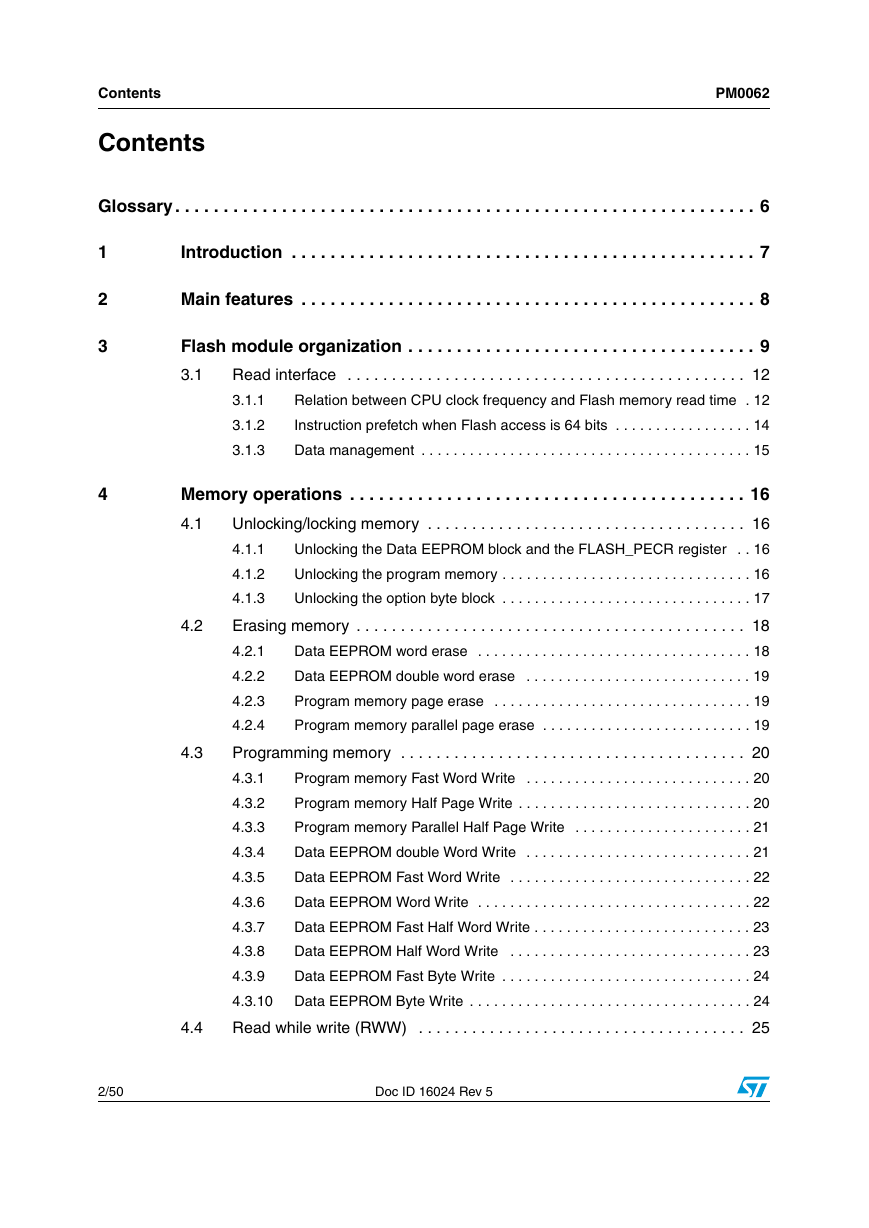

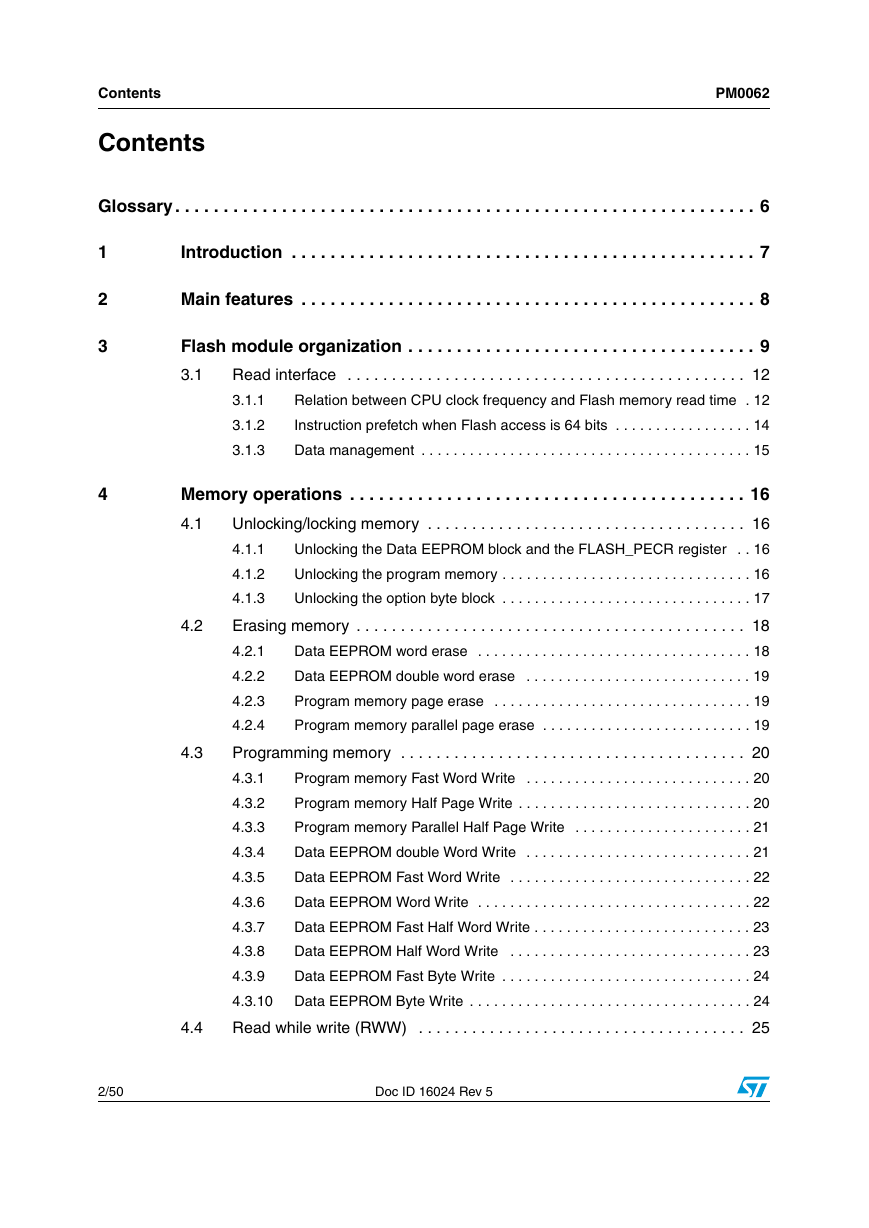

Figure 1. Flash memory programming overview

Glossary

1 Introduction

2 Main features

3 Flash module organization

Table 1. Flash module organization (medium density devices)

Table 2. Flash module organization (medium+ devices)

Table 3. Flash module organization (high density devices)

3.1 Read interface

3.1.1 Relation between CPU clock frequency and Flash memory read time

Table 4. Number of wait states (WS) according to CPU clock (HCLK) frequency

3.1.2 Instruction prefetch when Flash access is 64 bits

Figure 2. Sequential 32 bits instructions execution

3.1.3 Data management

4 Memory operations

4.1 Unlocking/locking memory

4.1.1 Unlocking the Data EEPROM block and the FLASH_PECR register

4.1.2 Unlocking the program memory

4.1.3 Unlocking the option byte block

4.2 Erasing memory

4.2.1 Data EEPROM word erase

4.2.2 Data EEPROM double word erase

4.2.3 Program memory page erase

4.2.4 Program memory parallel page erase

4.3 Programming memory

4.3.1 Program memory Fast Word Write

4.3.2 Program memory Half Page Write

4.3.3 Program memory Parallel Half Page Write

4.3.4 Data EEPROM double Word Write

4.3.5 Data EEPROM Fast Word Write

4.3.6 Data EEPROM Word Write

4.3.7 Data EEPROM Fast Half Word Write

4.3.8 Data EEPROM Half Word Write

4.3.9 Data EEPROM Fast Byte Write

4.3.10 Data EEPROM Byte Write

Table 6. Data EEPROM programming times

4.4 Read while write (RWW)

Table 7. Read While Write Summary

4.4.1 Alignment error flag

4.4.2 Size error flag

Table 8. Prohibited operations

4.4.3 Bus error (Cortex-M3 hardfault or Busfault)

5 Option byte description

Table 9. Option byte organization

Table 10. Description of the option bytes

5.1 Option byte block programming

6 Quick reference to programming/erase functions

Table 11. Programming/erase functions (medium density devices)

Table 12. Programming/erase functions (high density devices)

7 Memory protection

7.1 Readout protection (RDP) of the program and data EEPROMs

7.1.1 Level 1: memory read protection enabled

7.1.2 Level 2: memory read protection enabled and all debug features disabled

Figure 3. RDP levels

Table 13. Flash memory module protection according to RDP and its complement

7.2 Write protection (WRP) of the program memory

7.3 Write protection error flag

8 Interrupts

Table 14. Interrupts

9 Register description

9.1 Access control register (FLASH_ACR)

Note: 32-bit access is a low power mode. It is used only at low frequencies, that is with 0 wait state of latency and prefetch off.

Note: This bit cannot be written at the same time as the LATENCY and PRFTEN bits.

Note: Prefetch can be enabled only when ACC64 is set. This bit can be set or cleared only if ACC64 is set.

Note: Latency can be set only when ACC64 is set. This bit can be set or cleared only if ACC64 is set.

9.2 Program/erase control register (FLASH_PECR)

Note: This bit is available in high density devices only.

9.3 Power down key register (FLASH_PDKEYR)

9.4 Program/erase key register (FLASH_PEKEYR)

9.5 Program memory key register (FLASH_PRGKEYR)

9.6 Option byte key register (FLASH_OPTKEYR)

9.7 Status register (FLASH_SR)

Note: This bit is available in high density devices only.

9.8 Option byte register (FLASH_OBR)

Note: This bit is available in high density devices only.

Note: If the BOR is disabled, a “grey zone” exists between 1.65 V and the VPDR threshold (this means that VDD33 may be below the minimum operating voltage (1.65 V) without causing a reset until it crosses the VPDR threshold)

9.9 Write protection register (FLASH_WRPRx)

Note: FLASH_WRP2 is available in medium+ and high density devices

FLASH_WRP3 is available in high density devices only.

9.10 Register map

Table 15. Register map and reset values

10 Revision history

Table 16. Document revision history

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc