FPGA+DSP 的高速 AD 采集处理开发详解

副标题:Kintex-7 与 C6678 通过 SRIO 通信

一、案例说明

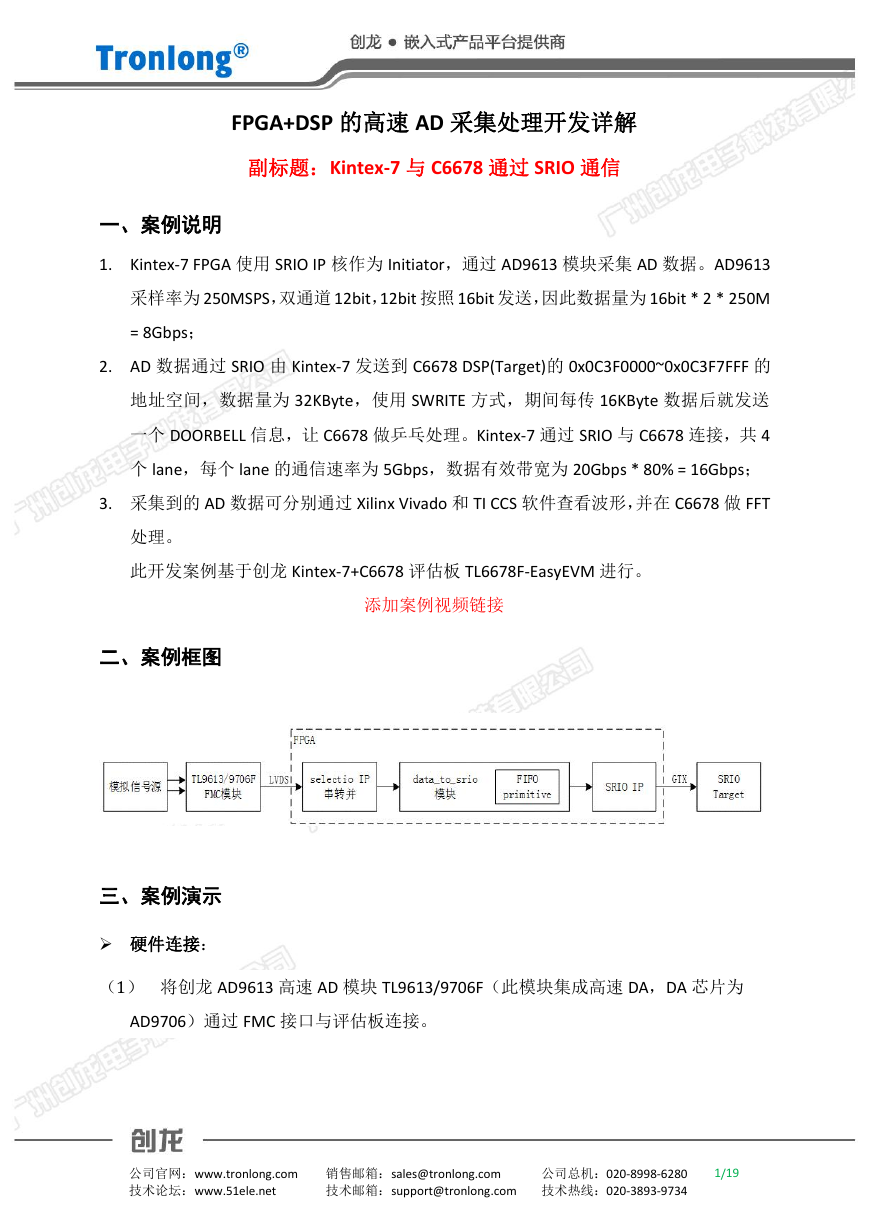

1. Kintex-7 FPGA 使用 SRIO IP 核作为 Initiator,通过 AD9613 模块采集 AD 数据。AD9613

采样率为 250MSPS,双通道 12bit,12bit 按照 16bit 发送,因此数据量为 16bit * 2 * 250M

= 8Gbps;

2. AD 数据通过 SRIO 由 Kintex-7 发送到 C6678 DSP(Target)的 0x0C3F0000~0x0C3F7FFF 的

地址空间,数据量为 32KByte,使用 SWRITE 方式,期间每传 16KByte 数据后就发送

一个 DOORBELL 信息,让 C6678 做乒乓处理。Kintex-7 通过 SRIO 与 C6678 连接,共 4

个 lane,每个 lane 的通信速率为 5Gbps,数据有效带宽为 20Gbps * 80% = 16Gbps;

3. 采集到的 AD 数据可分别通过 Xilinx Vivado 和 TI CCS 软件查看波形,并在 C6678 做 FFT

处理。

此开发案例基于创龙 Kintex-7+C6678 评估板 TL6678F-EasyEVM 进行。

添加案例视频链接

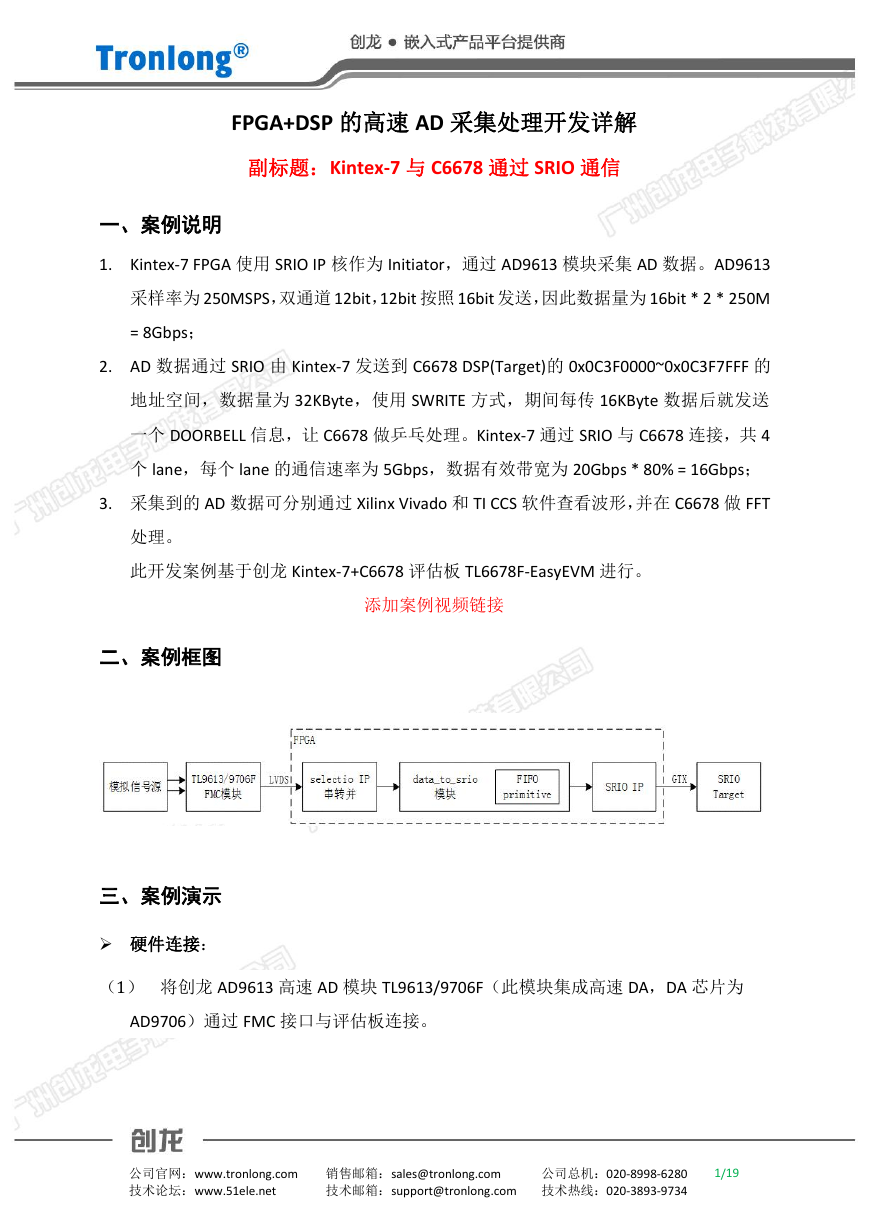

二、案例框图

三、案例演示

硬件连接:

(1) 将创龙 AD9613 高速 AD 模块 TL9613/9706F(此模块集成高速 DA,DA 芯片为

AD9706)通过 FMC 接口与评估板连接。

公司官网:www.tronlong.com

技术论坛:www.51ele.net

销售邮箱:sales@tronlong.com

公司总机:020-8998-6280

技术邮箱:support@tronlong.com 技术热线:020-3893-9734

1/19

�

(2) 信号发生器设置成两路正弦波输出,幅度设置:1.5Vpp 以及无直流偏置,频率设

(3) 信号发生器的两路输出分别连接到模块的 ADC_CHA、ADC_CHB。

置:1MHz。

评估板型号

TL6678F-EasyEVM

FMC 接口

CON15

BANK 电压配置接口

J1

配置电压

1.8V

TL9613/9706F 模块与 TL6678F-EasyEVM 评估板 FMC 接口图示(需技术支持提供):

1.FPGA 端

参考 TL6678F-EasyEVM 评估板光盘用户手册《基于下载器的程序固化与加载》文档

中“Vivado 下 bit 文件加载步骤”章节,将 tl_fmc_ad9613_srio_tl6678f_xc7k325t.bit 文件

烧录到 FPGA。烧写 bit 文件时,指定调试文件 tl_fmc_ad9613_srio_tl6678f_xc7k325t.ltx,

可以观察到 ILA 调试信号,查看 ADC 采样波形。

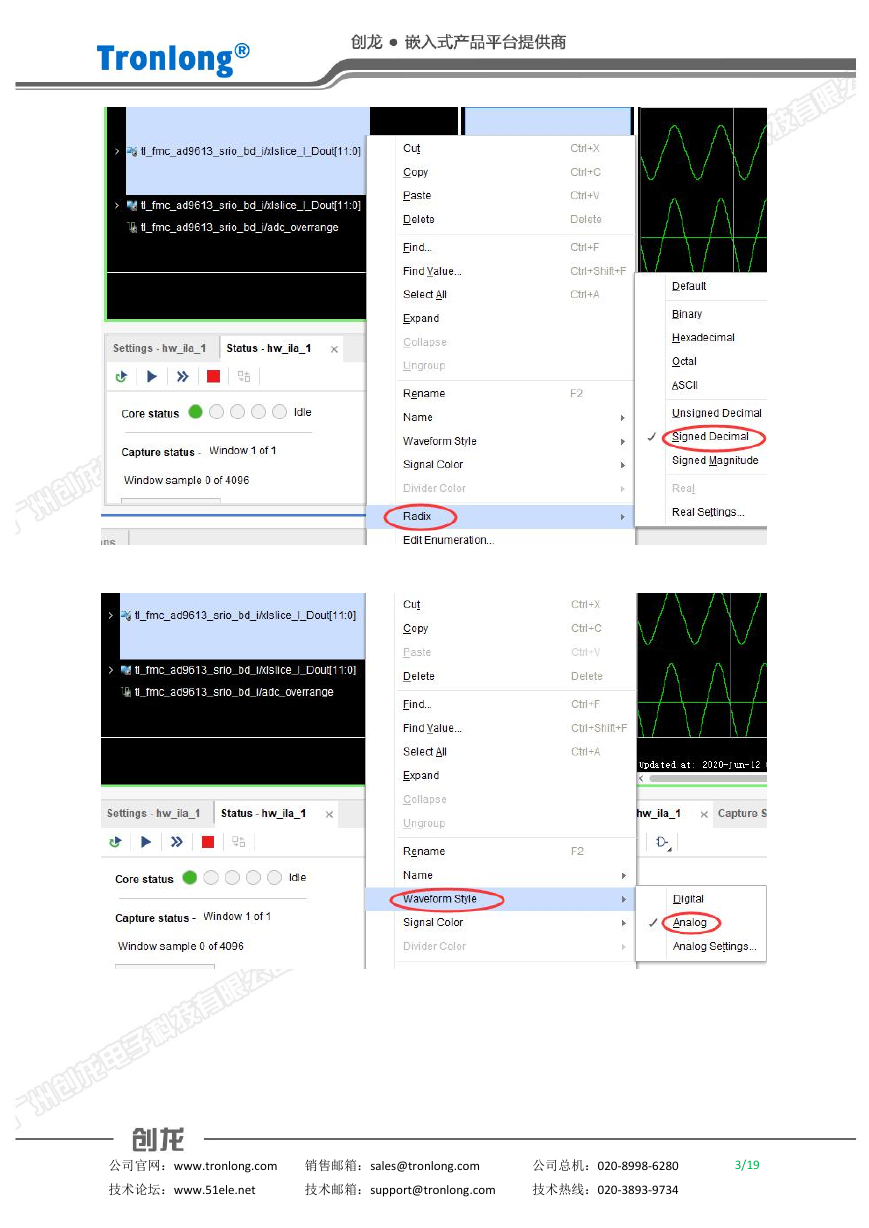

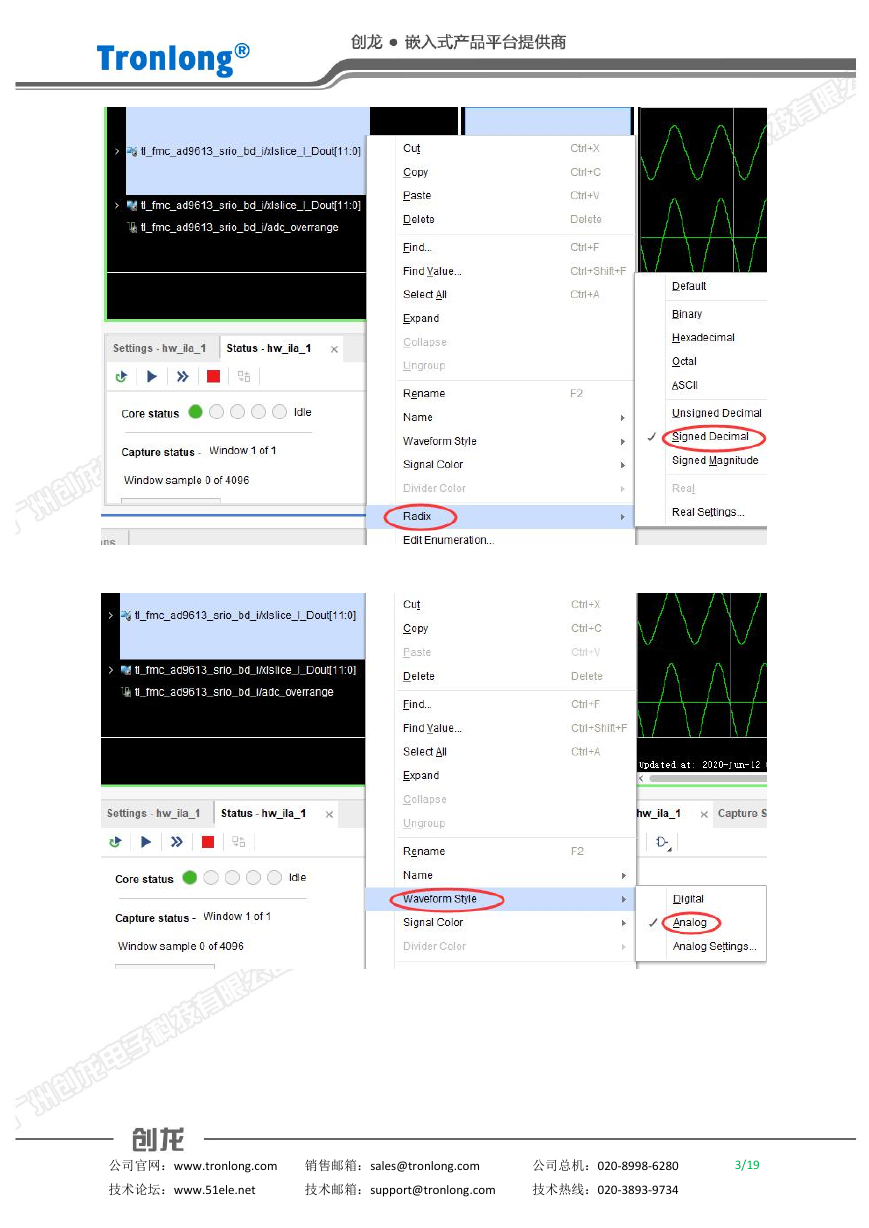

ADC 两路信号 tl_fmc_ad9613_srio_bd_i/xlslice_l_Dout[11:0]

和 tl_fmc_ad9613_srio_bd_i/xlslice_l_Dout[11:0]在 ILA 内嵌逻辑分析仪中均设置为有

符号数、模拟波形显示,如下图所示:

公司官网:www.tronlong.com

技术论坛:www.51ele.net

销售邮箱:sales@tronlong.com

技术邮箱:support@tronlong.com

公司总机:020-8998-6280

技术热线:020-3893-9734

2/19

�

公司官网:www.tronlong.com

技术论坛:www.51ele.net

销售邮箱:sales@tronlong.com

技术邮箱:support@tronlong.com

公司总机:020-8998-6280

技术热线:020-3893-9734

3/19

�

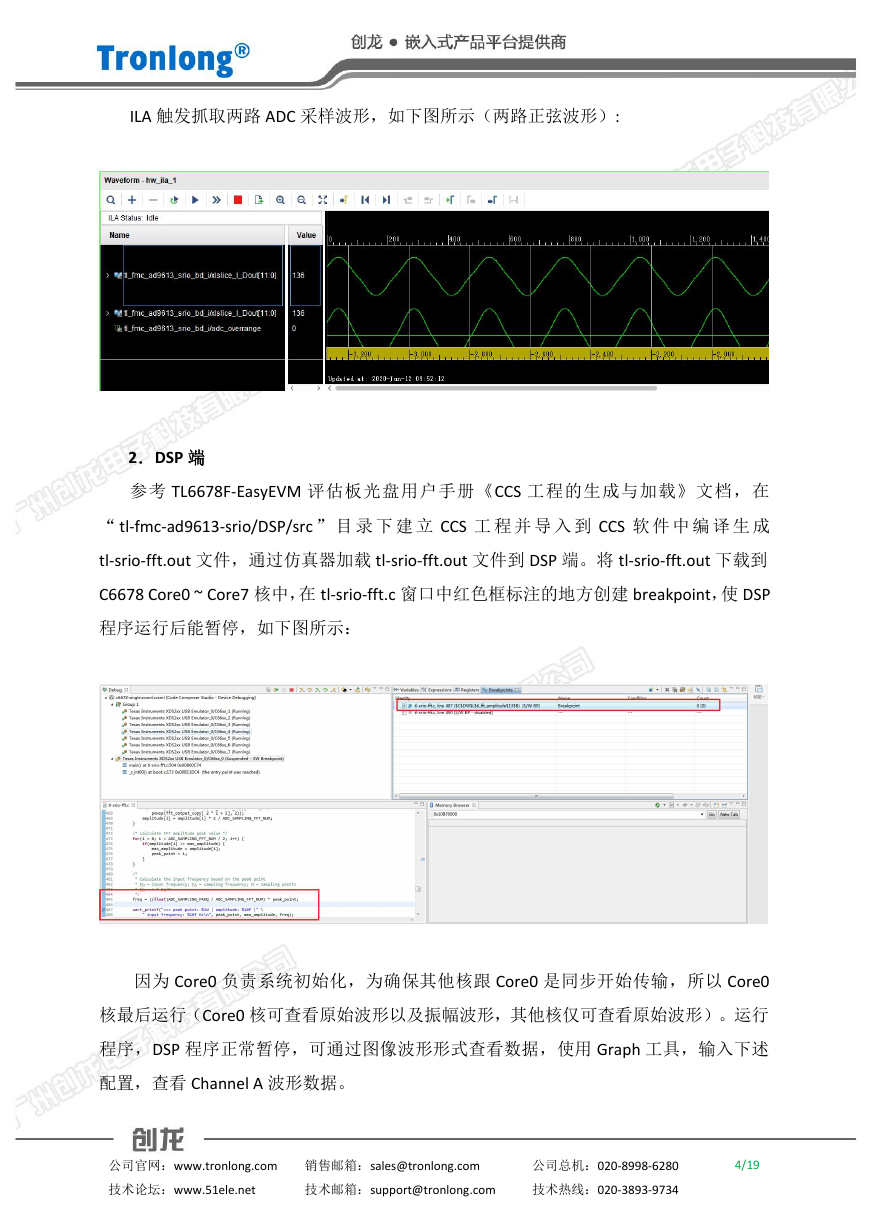

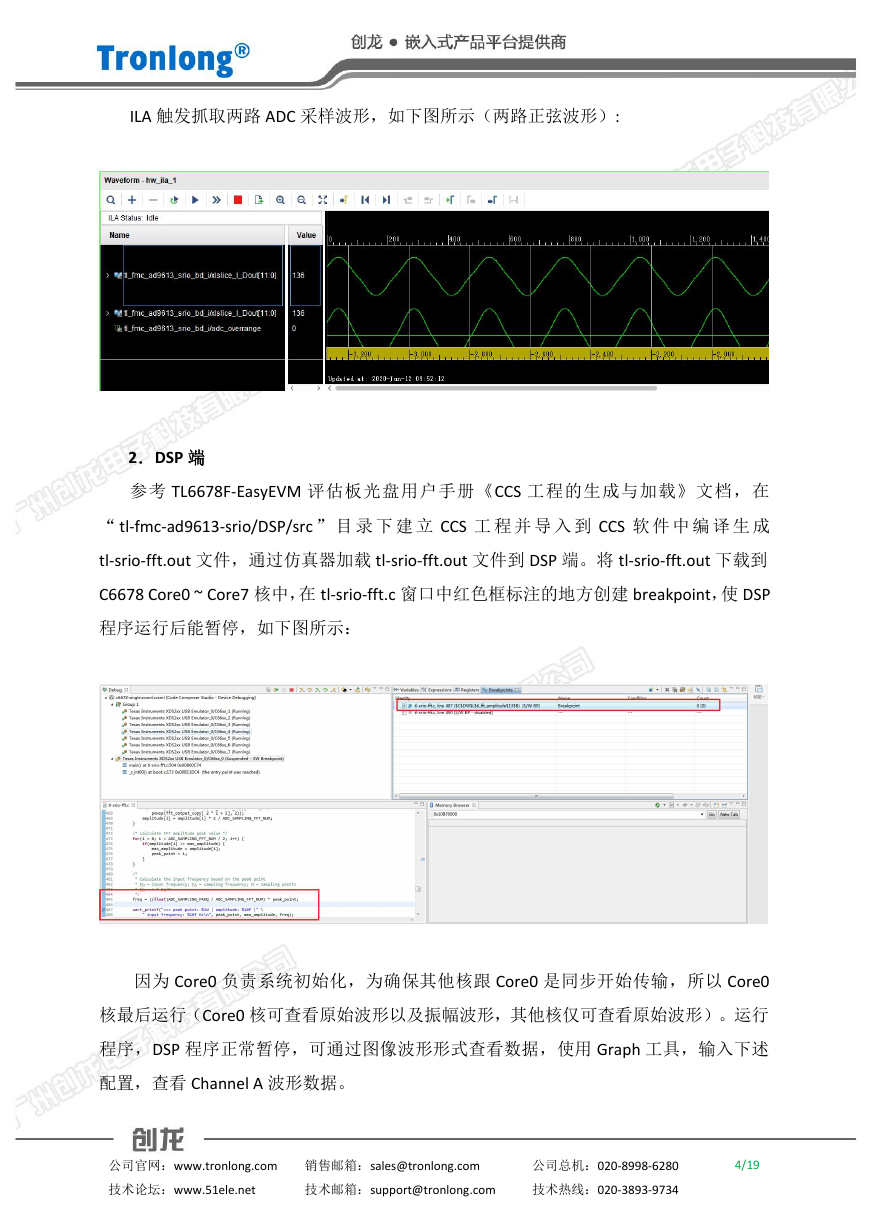

ILA 触发抓取两路 ADC 采样波形,如下图所示(两路正弦波形):

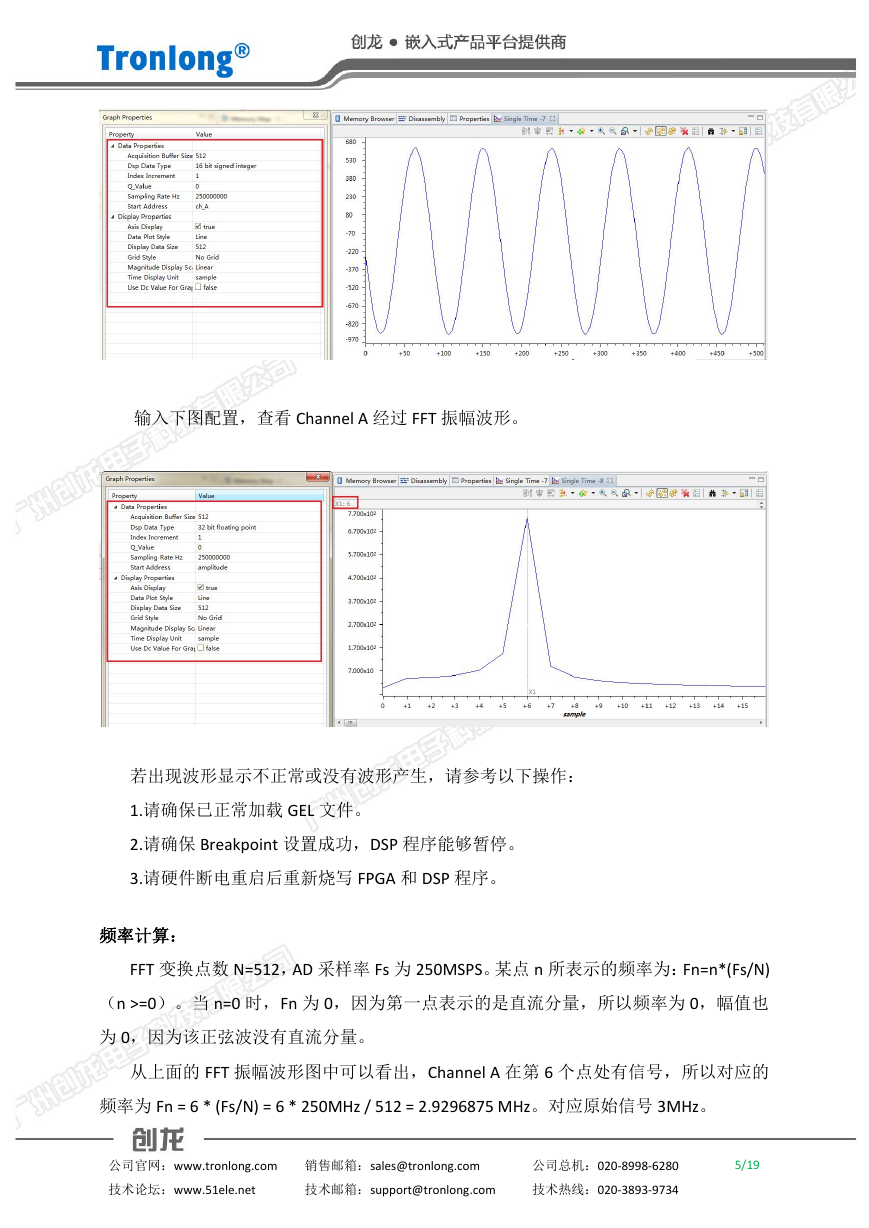

2.DSP 端

参考 TL6678F-EasyEVM 评估板光盘用户手册《CCS 工程的生成与加载》文档,在

“ tl-fmc-ad9613-srio/DSP/src ” 目 录 下 建 立 CCS 工 程 并 导 入 到 CCS 软 件 中 编 译 生 成

tl-srio-fft.out 文件,通过仿真器加载 tl-srio-fft.out 文件到 DSP 端。将 tl-srio-fft.out 下载到

C6678 Core0 ~ Core7 核中,在 tl-srio-fft.c 窗口中红色框标注的地方创建 breakpoint,使 DSP

程序运行后能暂停,如下图所示:

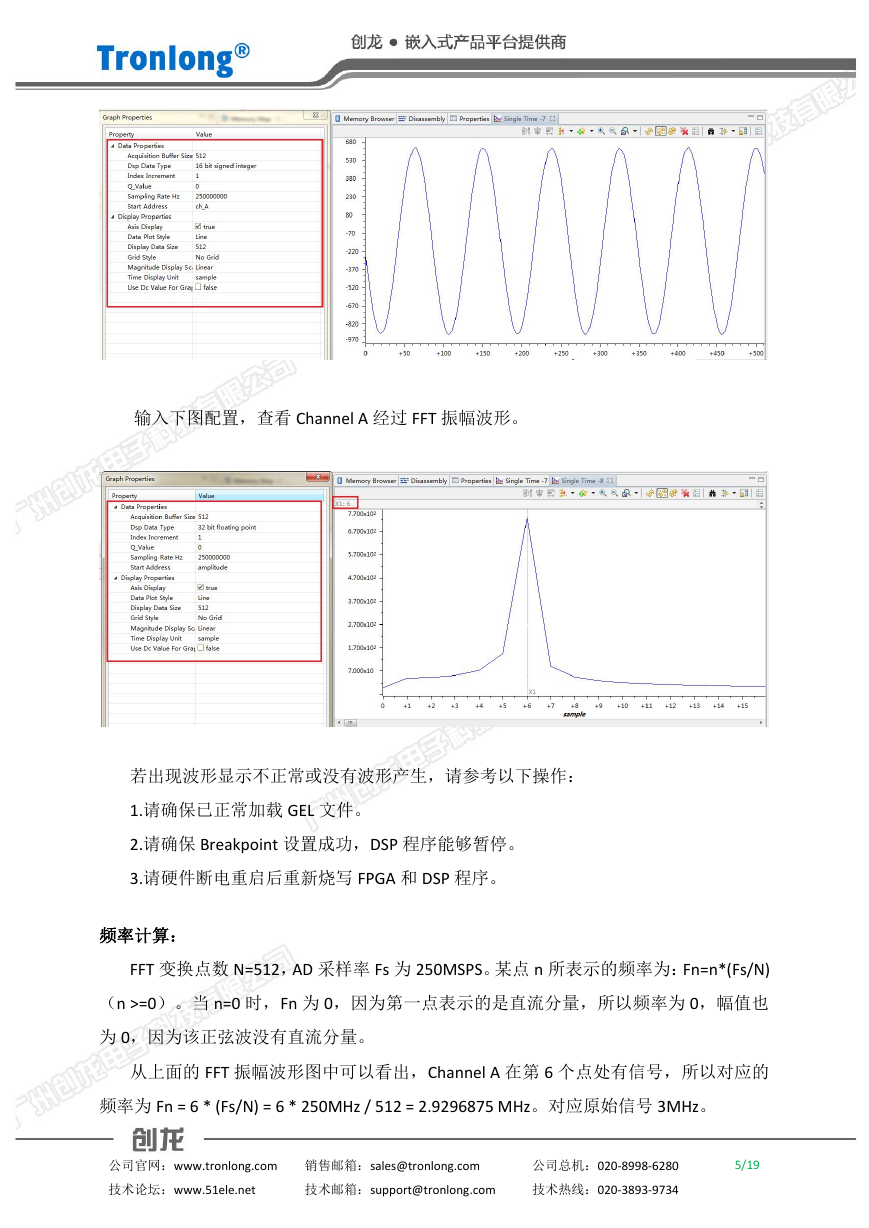

因为 Core0 负责系统初始化,为确保其他核跟 Core0 是同步开始传输,所以 Core0

核最后运行(Core0 核可查看原始波形以及振幅波形,其他核仅可查看原始波形)。运行

程序,DSP 程序正常暂停,可通过图像波形形式查看数据,使用 Graph 工具,输入下述

配置,查看 Channel A 波形数据。

公司官网:www.tronlong.com

技术论坛:www.51ele.net

销售邮箱:sales@tronlong.com

技术邮箱:support@tronlong.com

公司总机:020-8998-6280

技术热线:020-3893-9734

4/19

�

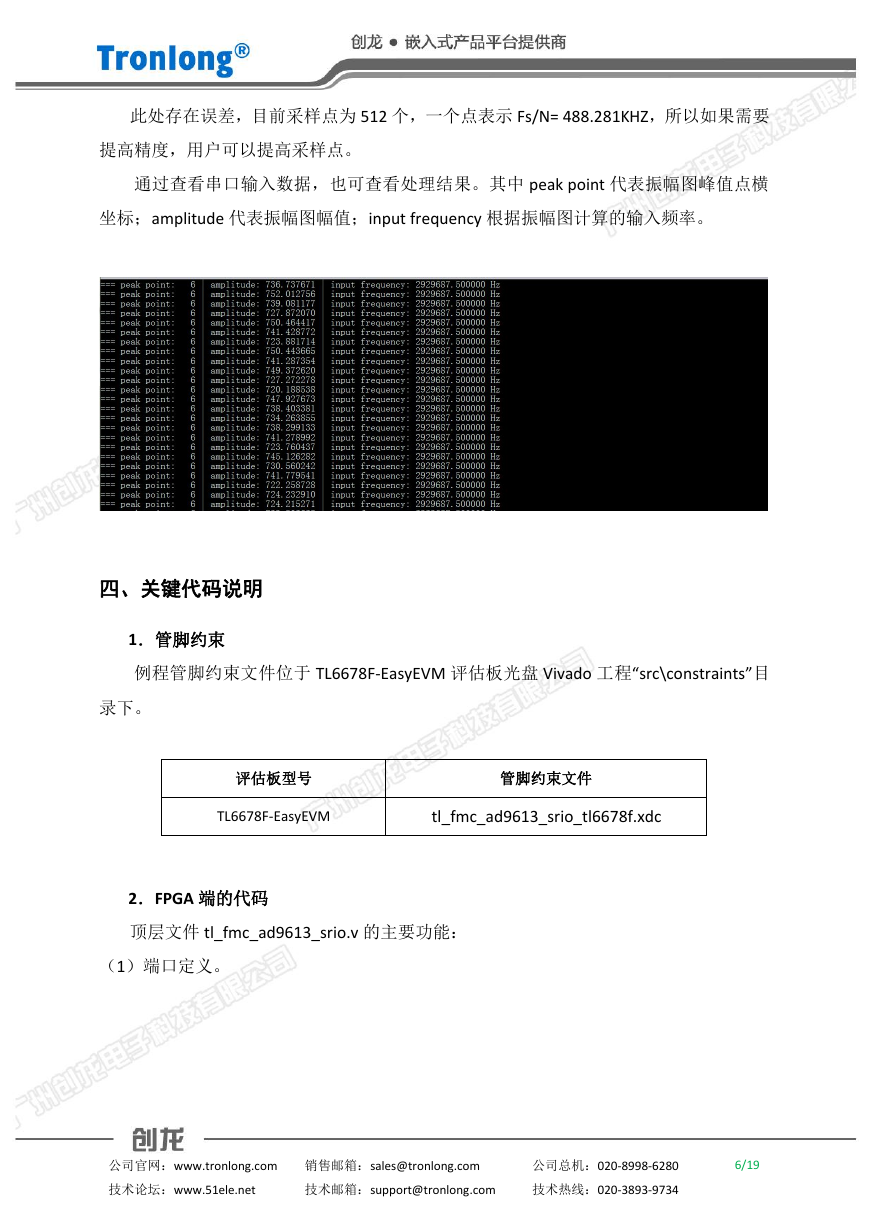

输入下图配置,查看 Channel A 经过 FFT 振幅波形。

若出现波形显示不正常或没有波形产生,请参考以下操作:

1.请确保已正常加载 GEL 文件。

2.请确保 Breakpoint 设置成功,DSP 程序能够暂停。

3.请硬件断电重启后重新烧写 FPGA 和 DSP 程序。

频率计算:

FFT 变换点数 N=512,AD 采样率 Fs 为 250MSPS。某点 n 所表示的频率为:Fn=n*(Fs/N)

(n >=0)。当 n=0 时,Fn 为 0,因为第一点表示的是直流分量,所以频率为 0,幅值也

为 0,因为该正弦波没有直流分量。

从上面的 FFT 振幅波形图中可以看出,Channel A 在第 6 个点处有信号,所以对应的

频率为 Fn = 6 * (Fs/N) = 6 * 250MHz / 512 = 2.9296875 MHz。对应原始信号 3MHz。

公司官网:www.tronlong.com

技术论坛:www.51ele.net

销售邮箱:sales@tronlong.com

技术邮箱:support@tronlong.com

公司总机:020-8998-6280

技术热线:020-3893-9734

5/19

�

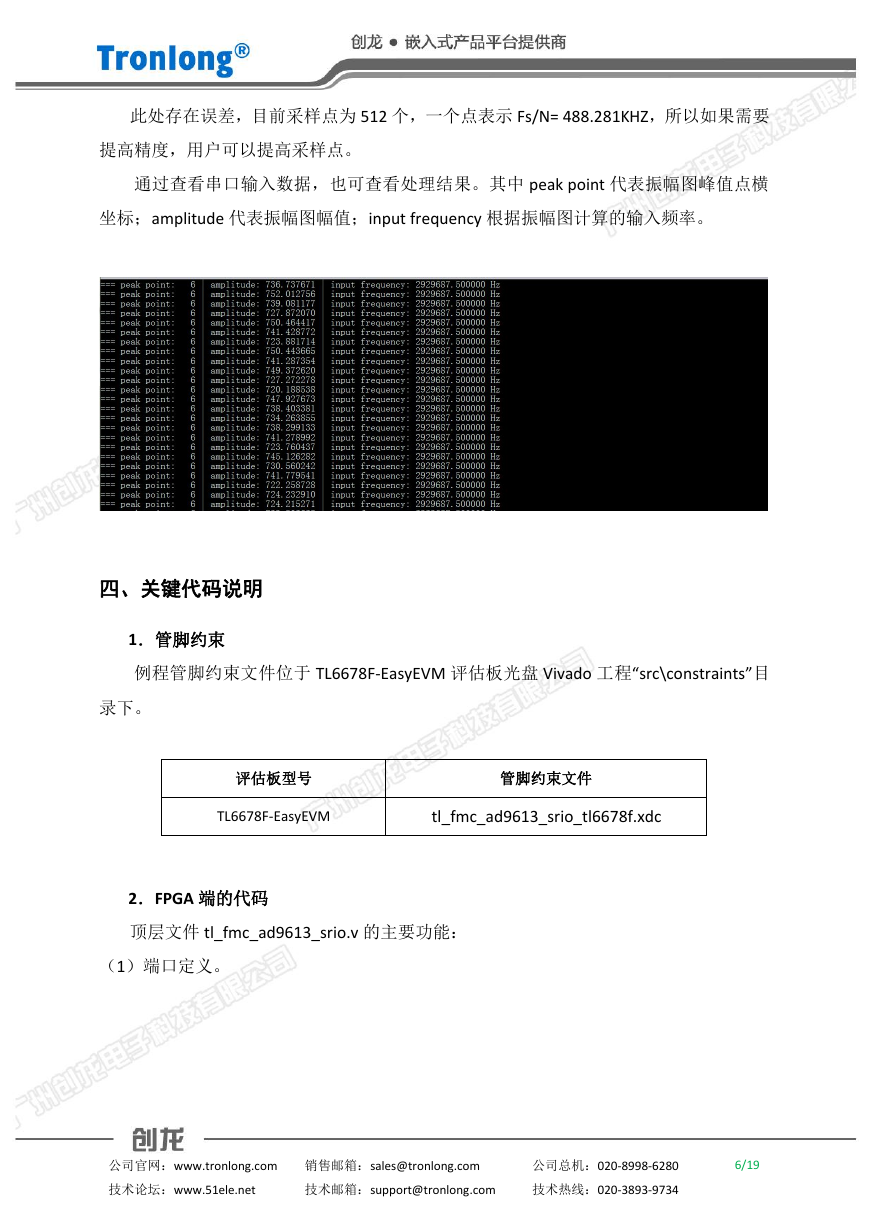

此处存在误差,目前采样点为 512 个,一个点表示 Fs/N= 488.281KHZ,所以如果需要

提高精度,用户可以提高采样点。

通过查看串口输入数据,也可查看处理结果。其中 peak point 代表振幅图峰值点横

坐标;amplitude 代表振幅图幅值;input frequency 根据振幅图计算的输入频率。

四、关键代码说明

1.管脚约束

例程管脚约束文件位于 TL6678F-EasyEVM 评估板光盘 Vivado 工程“src\constraints”目

录下。

评估板型号

管脚约束文件

TL6678F-EasyEVM

tl_fmc_ad9613_srio_tl6678f.xdc

2.FPGA 端的代码

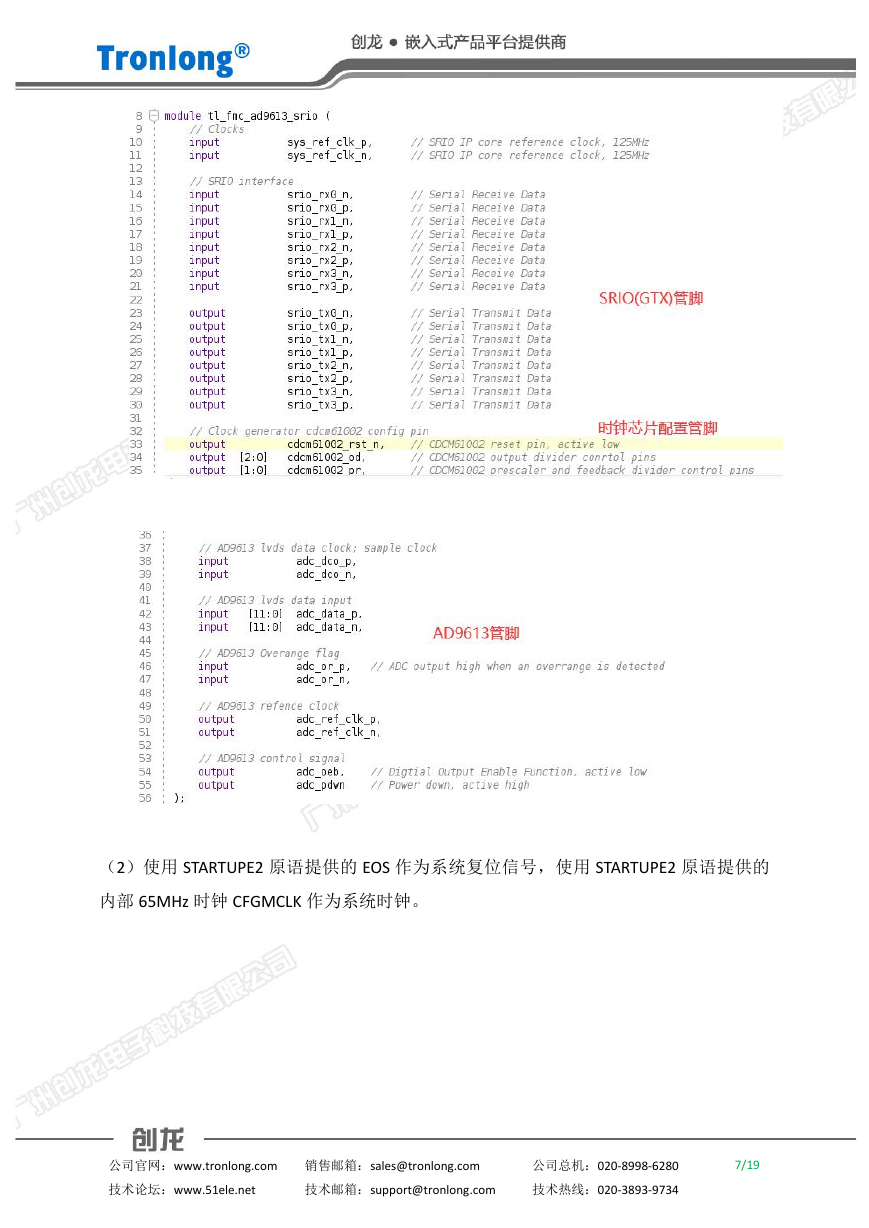

顶层文件 tl_fmc_ad9613_srio.v 的主要功能:

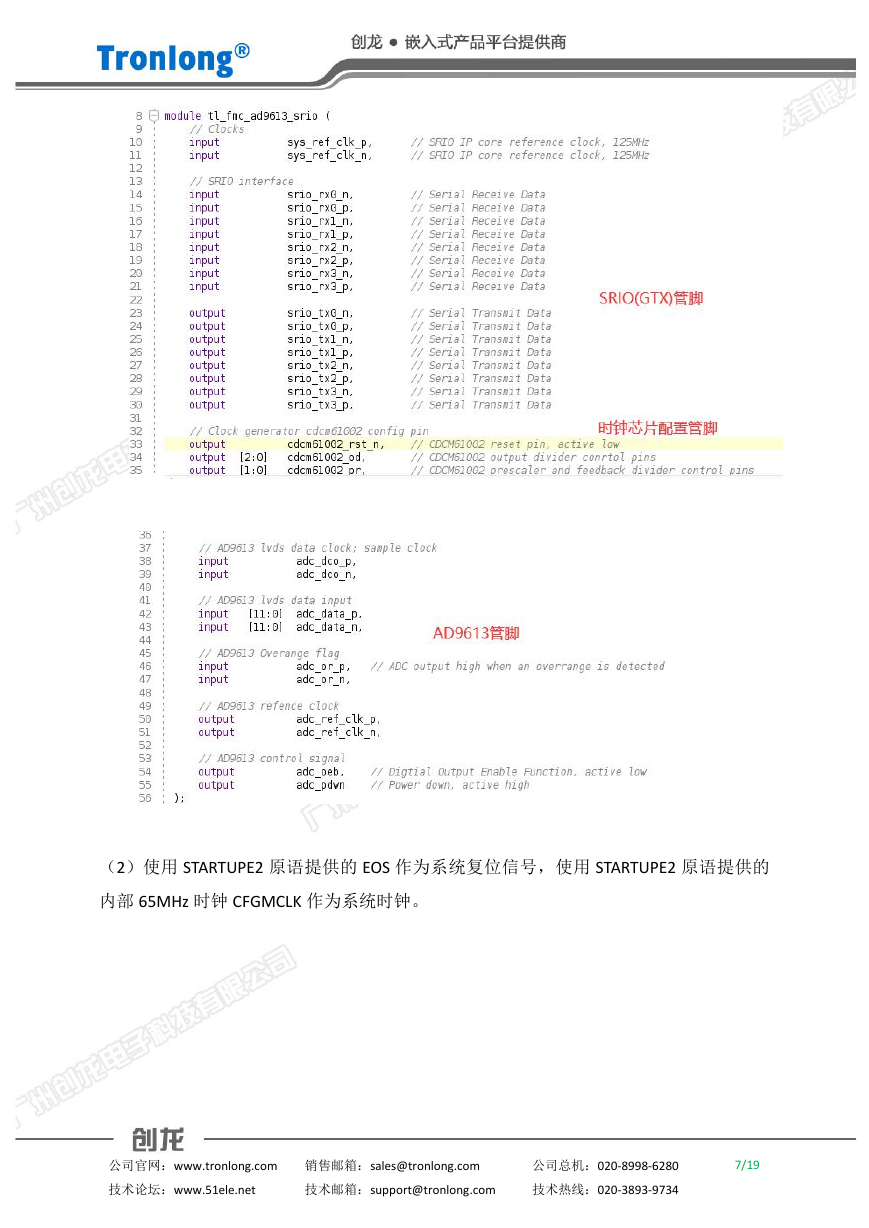

(1)端口定义。

公司官网:www.tronlong.com

技术论坛:www.51ele.net

销售邮箱:sales@tronlong.com

技术邮箱:support@tronlong.com

公司总机:020-8998-6280

技术热线:020-3893-9734

6/19

�

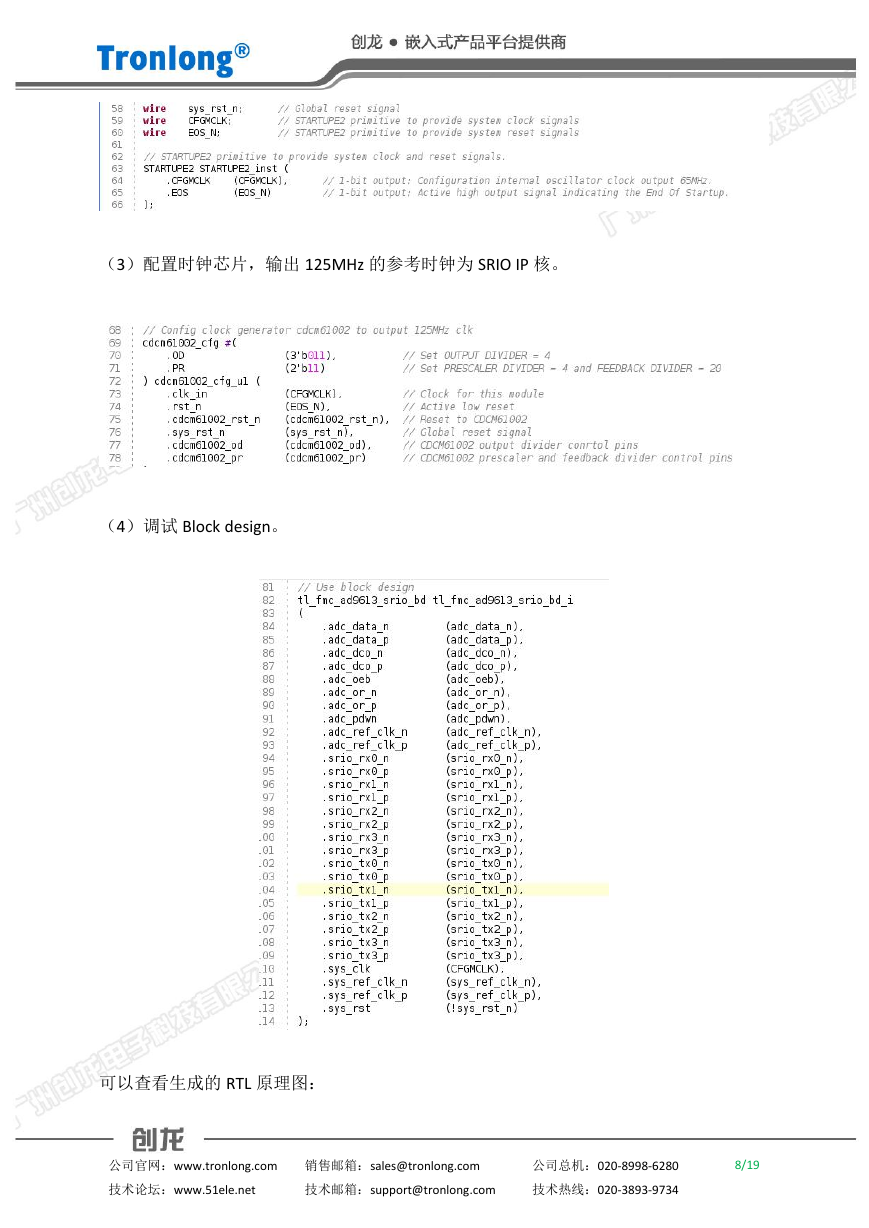

(2)使用 STARTUPE2 原语提供的 EOS 作为系统复位信号,使用 STARTUPE2 原语提供的

内部 65MHz 时钟 CFGMCLK 作为系统时钟。

公司官网:www.tronlong.com

技术论坛:www.51ele.net

销售邮箱:sales@tronlong.com

技术邮箱:support@tronlong.com

公司总机:020-8998-6280

技术热线:020-3893-9734

7/19

�

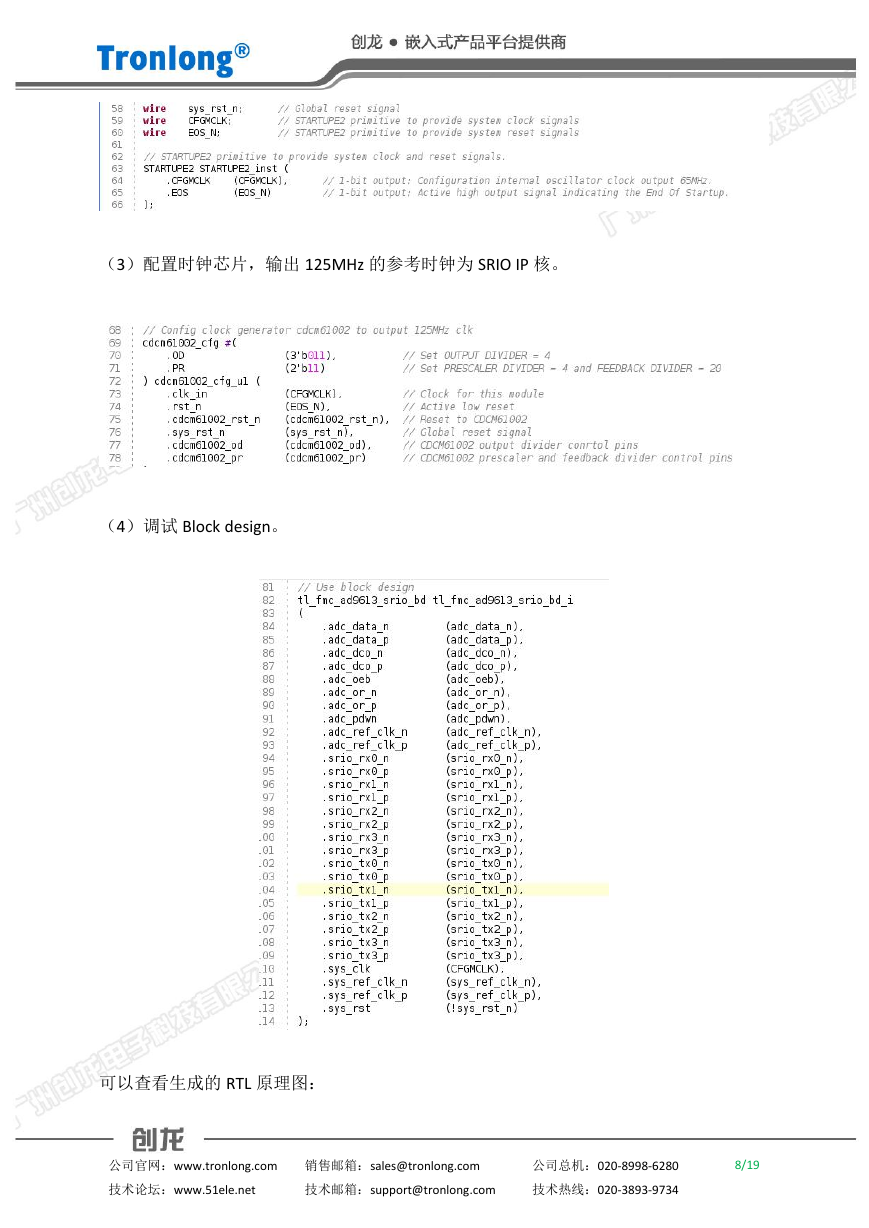

(3)配置时钟芯片,输出 125MHz 的参考时钟为 SRIO IP 核。

(4)调试 Block design。

可以查看生成的 RTL 原理图:

公司官网:www.tronlong.com

技术论坛:www.51ele.net

销售邮箱:sales@tronlong.com

技术邮箱:support@tronlong.com

公司总机:020-8998-6280

技术热线:020-3893-9734

8/19

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc