内容摘要

抢答器是为智力竞赛参赛者答题时进行抢答而设计的一种优先

判决器电路,竞赛者可以分为若干组,抢答时各组对主持人提出的问

题要在最短的时间内做出判断,并按下抢答按键回答问题。当第一个

人按下按键后,则在显示器上显示该组的号码,对应的灯亮,同时电

路将其他各组按键封锁,使其不起作用。若抢答时间内无人抢答,则

报警灯亮。回答完问题后,由主持人将所有按键恢复,重新开始下一

轮抢答。因此要完成抢答器的逻辑功能,该电路应包括抢答器鉴别模

块、抢答器计数模块、报警模块、译码模块、分频模块。

关键词:抢答鉴别 封锁 计数 报警

Abstract

Responder is the answer for the quiz participants to answer in the design

when a priority decision circuit, and the race can be divided into several groups,

answer in each group on the host issues raised in the shortest possible time to make

judgments , and press the answer in answer key. After pressing the button when the

first person, then the display shows the number of the group, the corresponding

lights, while other groups will be key circuit block, it does not work. If the answer

in time, no answer in, the alarm lights. Answering questions, all the keys from the

host to restore and re-start the next round of the Responder. So to complete the

answering

Responder

identification module, Responder counting module, alarm module, decoding module,

frequency module.

functions,

include

the

circuit

device

logic

should

KEY:

Responder Identification

Blockade

Count

Alarm

1

�

一、 设计要求

1.抢答器同时供 4 名选手或 4 个代表队比赛,分别用 4 个按钮 S0~ S3 表示。

2.设置一个系统清除和抢答控制开关 rst,该开关由主持人控制。

3.抢答器具有锁存与显示功能。即选手按动按钮,锁存相应的编号,并在 LED 和数

码管上显示,同时提示灯亮。选手抢答实行优先锁存,优先抢答选手的编号一直

保持到主持人将系统清除为止。

4. 抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如 20 秒)

5. 如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示

器上显示 20。

二、方案设计与论证

1、 概述

将该任务分成五个模块进行设计,分别为:抢答器鉴别模块、抢答器计时模块、报

警模块、分频模块、译码模块。

2、 抢答器鉴别模块:

在这个模块中主要实现抢答过程中的抢答功能,并能对超前抢答进行警告,还能记

录无论是正常抢答还是朝前抢答者的台号,并且能实现当有一路抢答按键按下时,

该路抢答信号将其余的抢答信号封锁的功能。其中有四个抢答信号 s0、s1、s2、s3;

抢答状态显示信号 states;抢答与警报时钟信号 clk2;系统复位信号 rst;警报信号

warm。

3、 抢答器计数模块:

在这个模块中主要实现抢答过程中的计时功能,在有抢答开始后进行 20 秒的倒计

时,并且在 20 秒倒计时后无人抢答显示超时并报警。其中有抢答时钟信号 clk1;系

统复位信号 rst;抢答使能信号 start;无人抢答警报信号 warn;计时中止信号 stop;

计时十位和个位信号 tb,ta。

4、 报警模块:

在这个模块中主要实现抢答过程中的报警功能,当主持人按下控制键,有限时间内

人抢答或是计数到时蜂鸣器开始报警,计数停止信号 stop;状态输出信号 alm;计数

脉冲 clk。

5、 译码模块:

在这个模块中主要实现抢答过程中将 BCD 码转换成 7 段的功能。

6、 分频模块:

在这个模块中主要实现抢答过程中所需的时钟信号。

7、 顶层文件:

在这个模块中是对前五个模块的综合编写的顶层文件。

2

�

三、单元电路设计

(一)抢答鉴别模块

1.VHDL 源程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xuanshou is

port(rst,clk2:in std_logic;

s0,s1,s2,s3:in std_logic;

states:buffer std_logic_vector(3 downto 0);

light:buffer std_logic_vector(3 downto 0);

warm:out std_logic);

end xuanshou ;

architecture one of xuanshou

is

signal st:std_logic_vector(3 downto 0);

begin

p1:process(s0,rst,s1,s2,s3,clk2)

begin

if rst='0'

then

warm<='0';st<="0000";

elsif clk2'event and clk2='1' then

if (s0='1' or st(0)='1')and not( st(1)='1' or st(2)='1' or st(3)='1' )

then st(0)<='1';

end if ;

if (s1='1' or st(1)='1')and not( st(0)='1' or st(2)='1' or st(3)='1' )

then st(1)<='1';

end if ;

if (s2='1' or st(2)='1')and not( st(0)='1' or st(1)='1' or st(3)='1' )

then st(2)<='1';

end if ;

if (s3='1' or st(3)='1')and not( st(0)='1' or st(1)='1' or st(2)='1' )

then st(3)<='1';

end if ;

warm<=st(0) or st(1) or st(2) or st(3);

end if ;

end process p1;

p2:process(states(0),states(1),states(2),states(3),light)

begin

if (st="0000") then states<="0000";

elsif (st<="0001") then states<="0001";

elsif (st<="0010") then states<="0010";

elsif (st<="0100") then states<="0011";

3

�

elsif (st<="1000") then states<="0100";

end if;

light<=st;

end process p2;

end one;

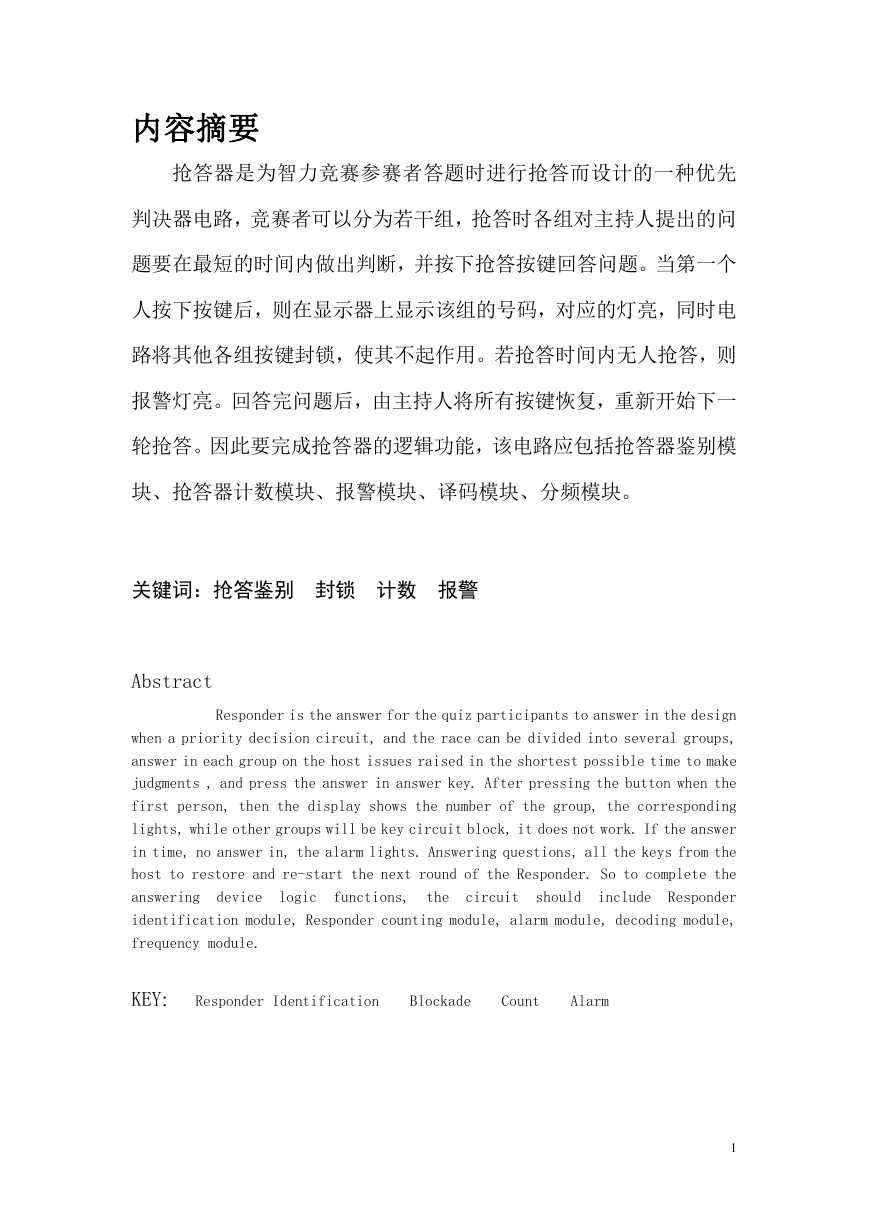

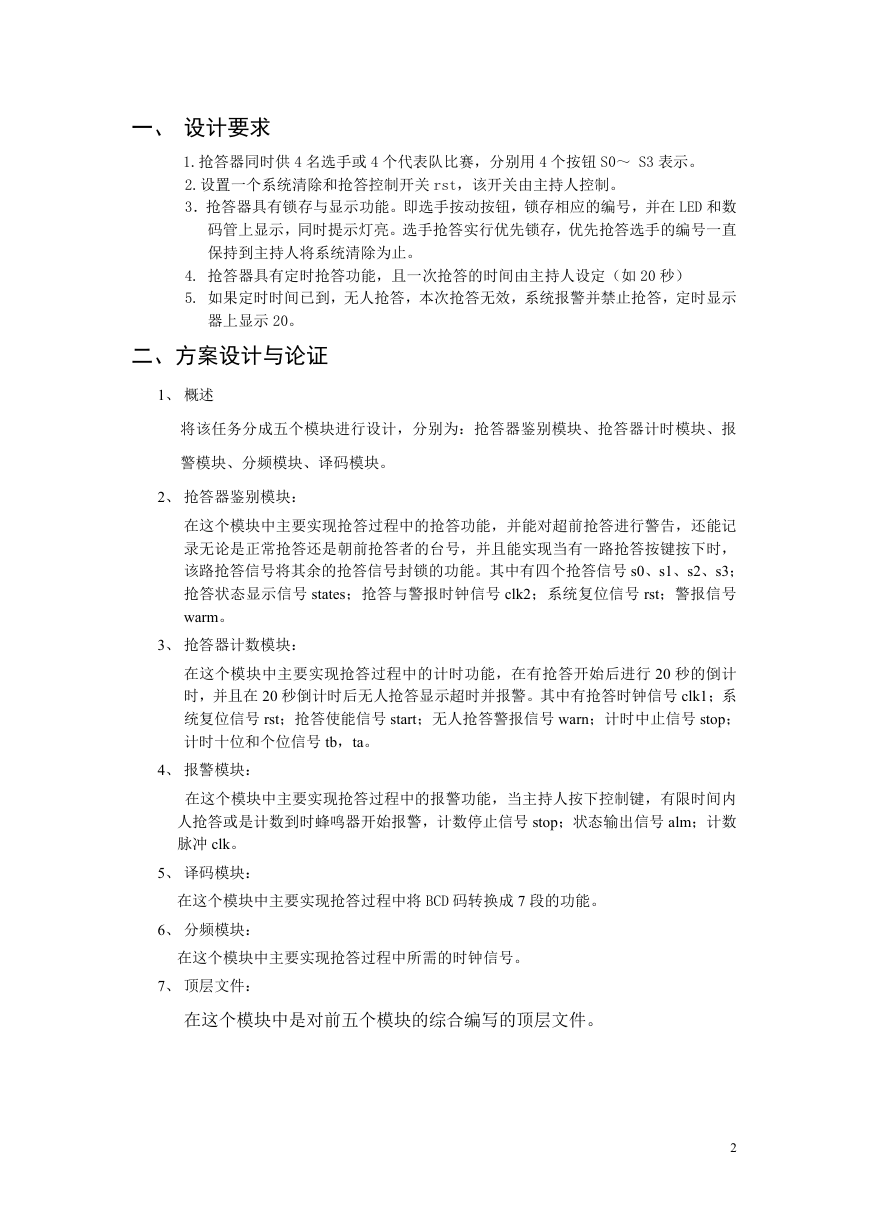

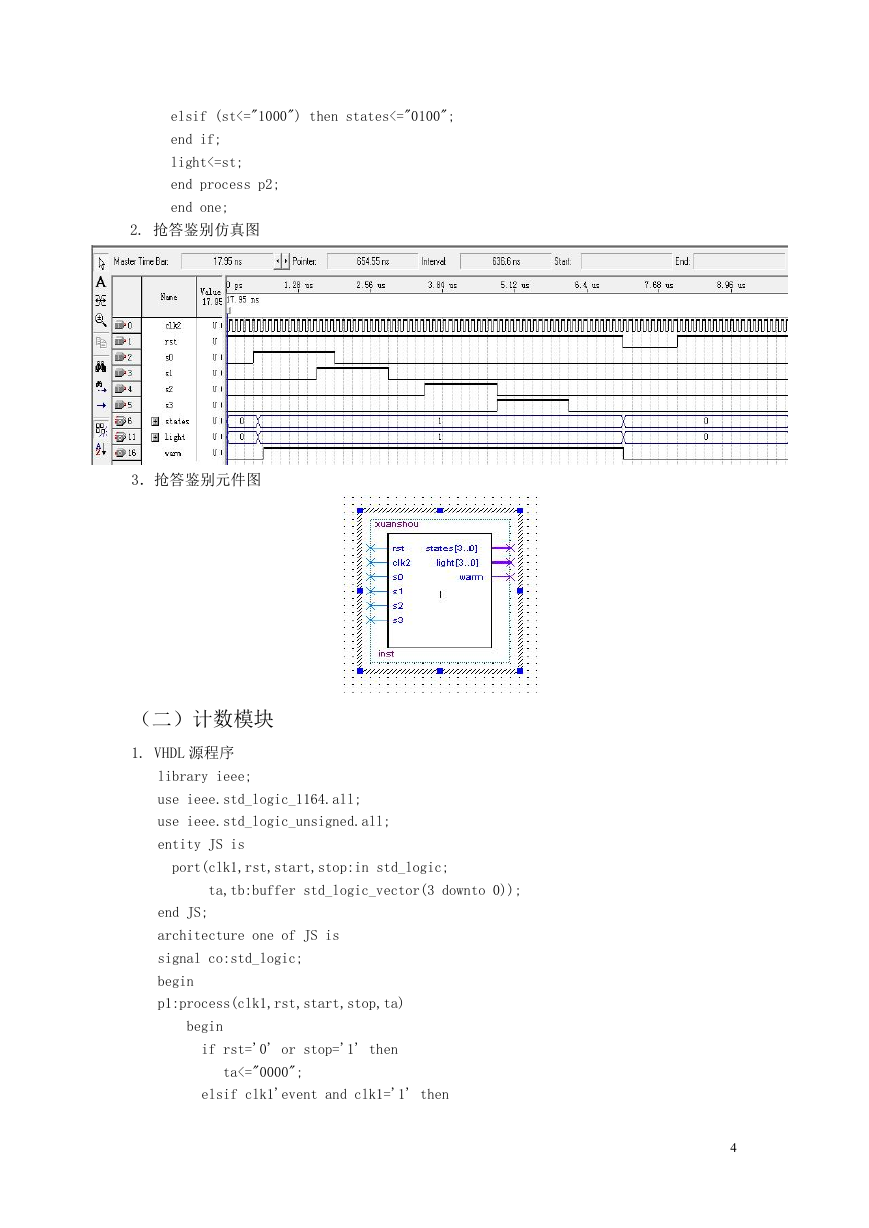

2. 抢答鉴别仿真图

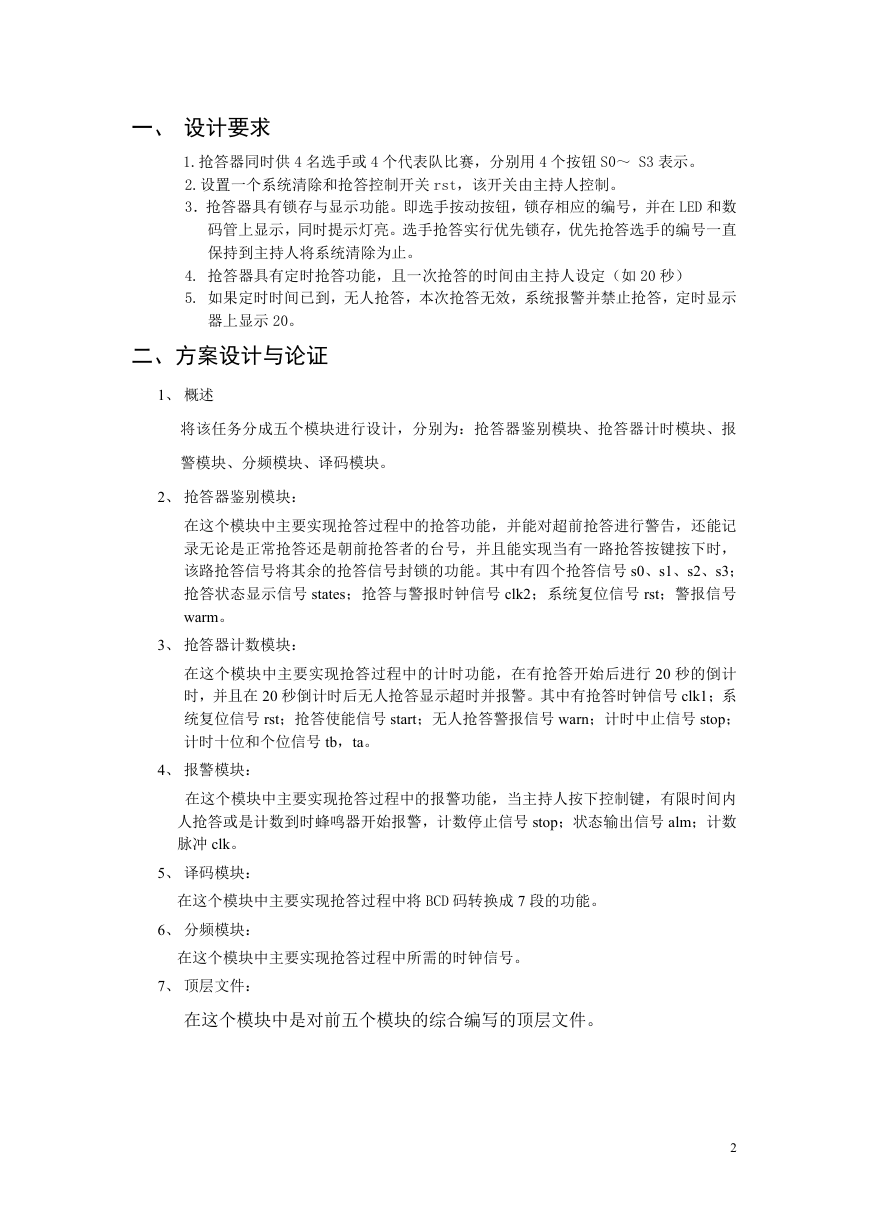

3.抢答鉴别元件图

(二)计数模块

1. VHDL 源程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity JS is

port(clk1,rst,start,stop:in std_logic;

ta,tb:buffer std_logic_vector(3 downto 0));

end JS;

architecture one of JS is

signal co:std_logic;

begin

p1:process(clk1,rst,start,stop,ta)

begin

if rst='0' or stop='1' then

ta<="0000";

elsif clk1'event and clk1='1' then

4

�

co<='0';

if start='1' then

if ta="0000" then

ta<="1001";co<='1';

else ta<=ta-1;

end if;

end if;

end if;

end process p1;

p2:process(co,rst,start,stop,tb)

begin

if rst='0' or stop='1' then

tb<="0010";

elsif co'event and co='1' then

if start='1' then

if tb="0000" then tb<="0011";

else tb<=tb-1;

end if;

end if;

end if;

end process p2;

end one ;

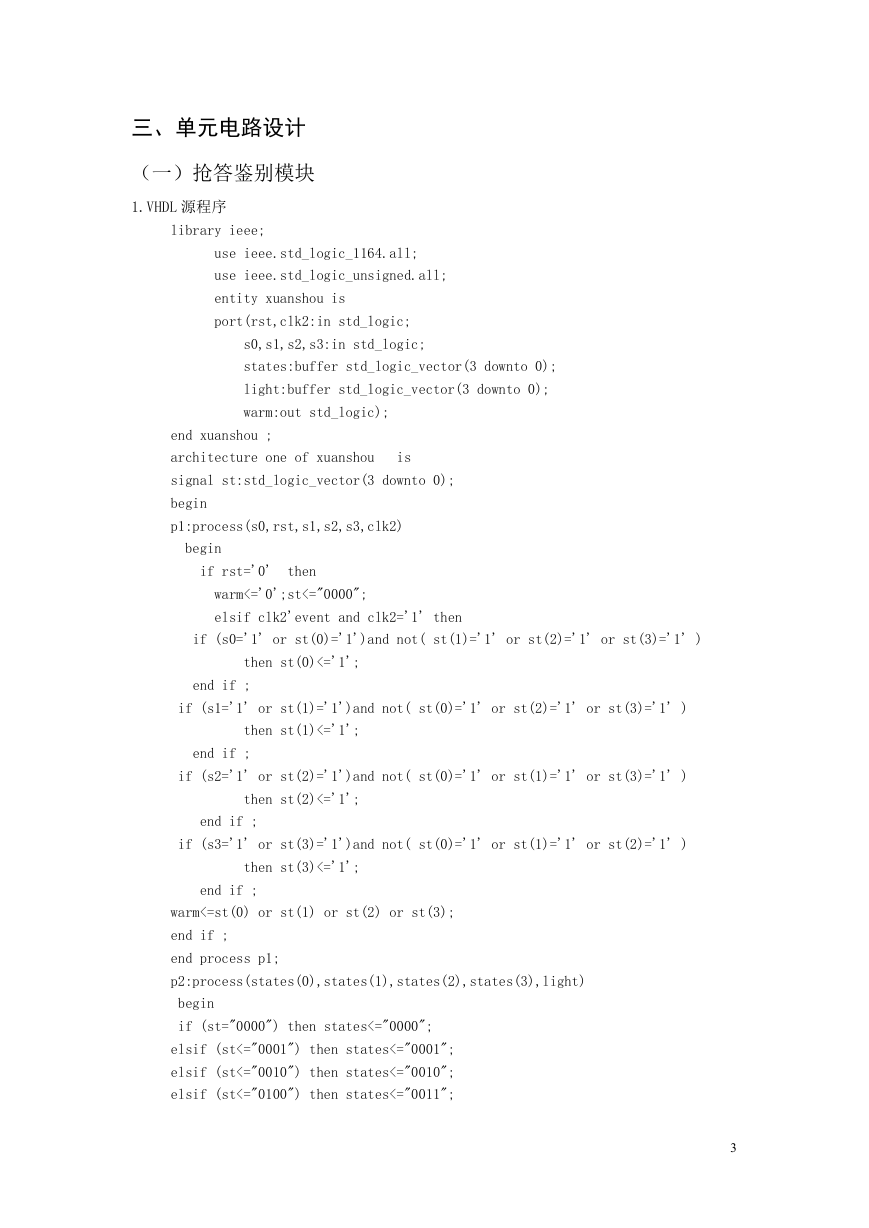

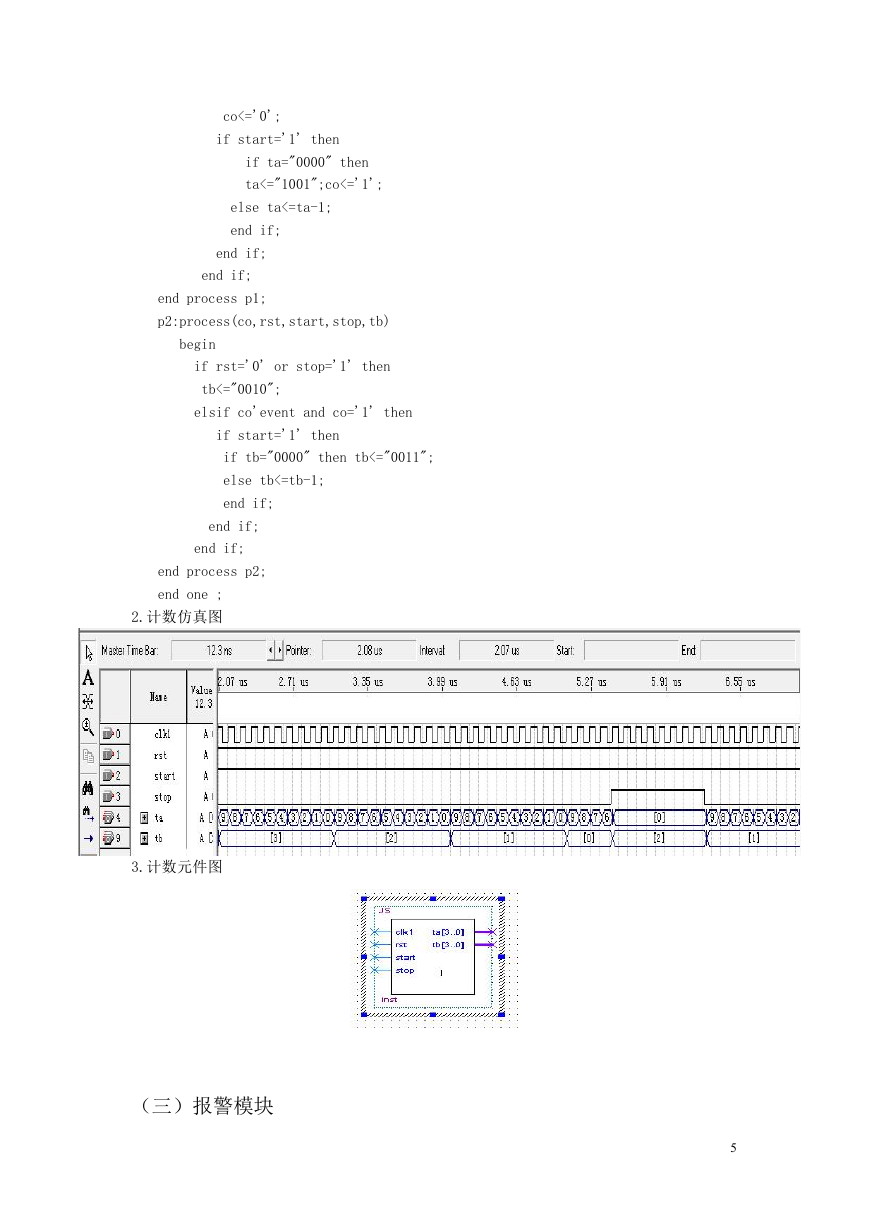

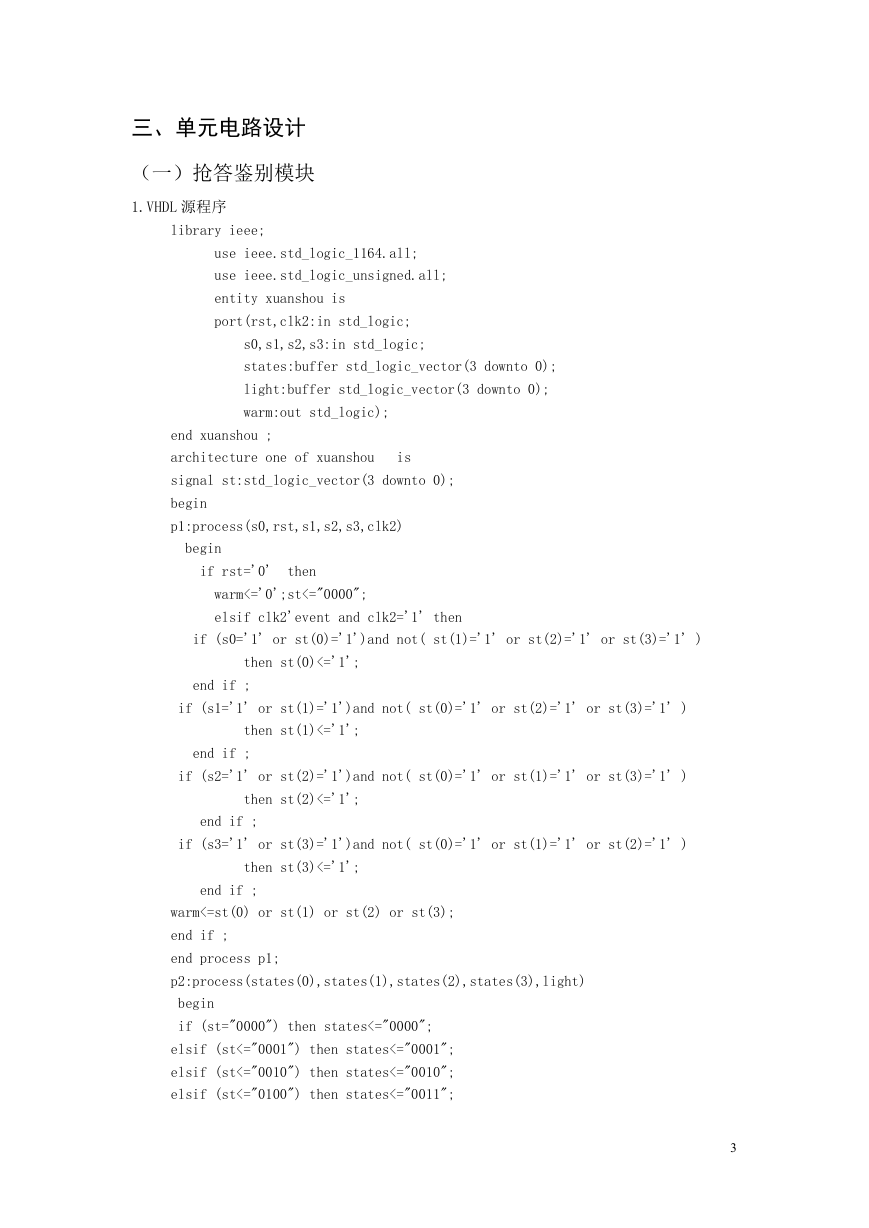

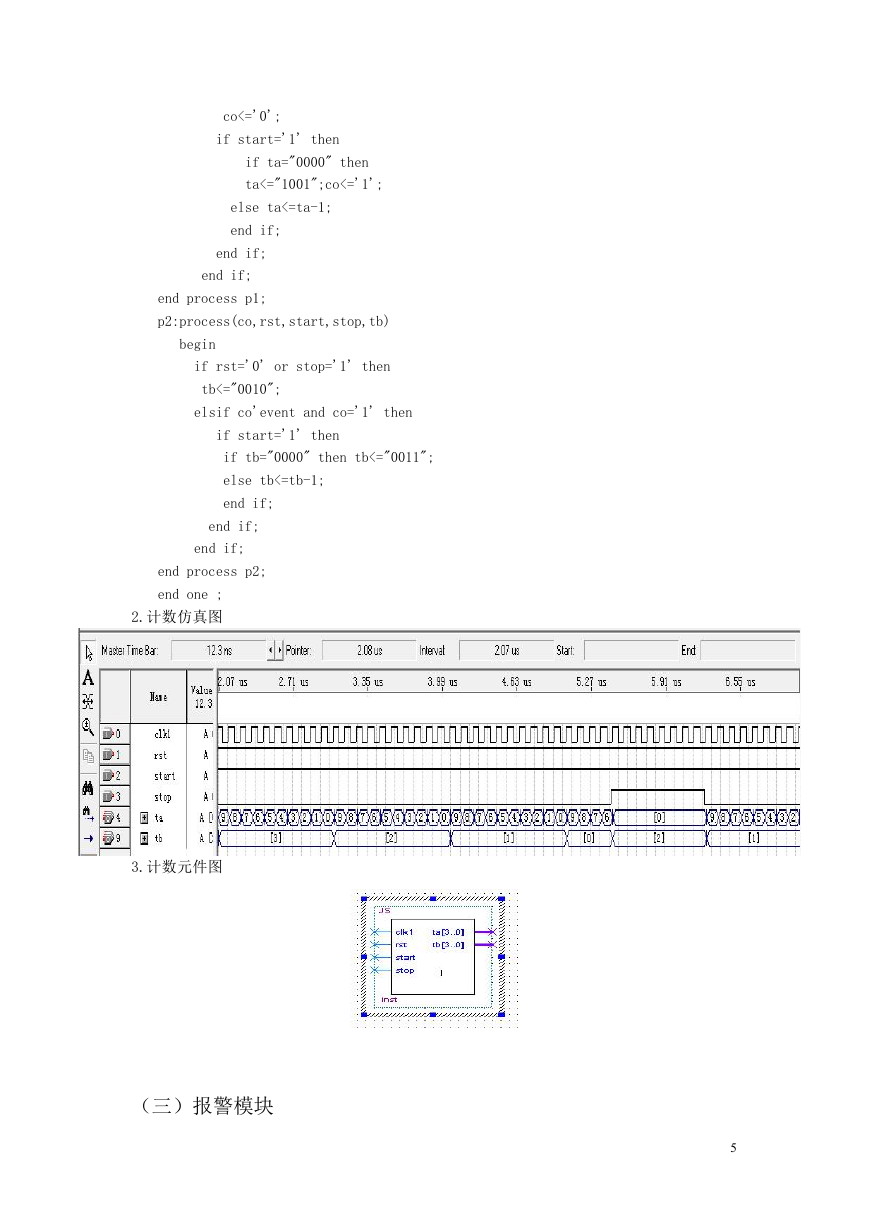

2.计数仿真图

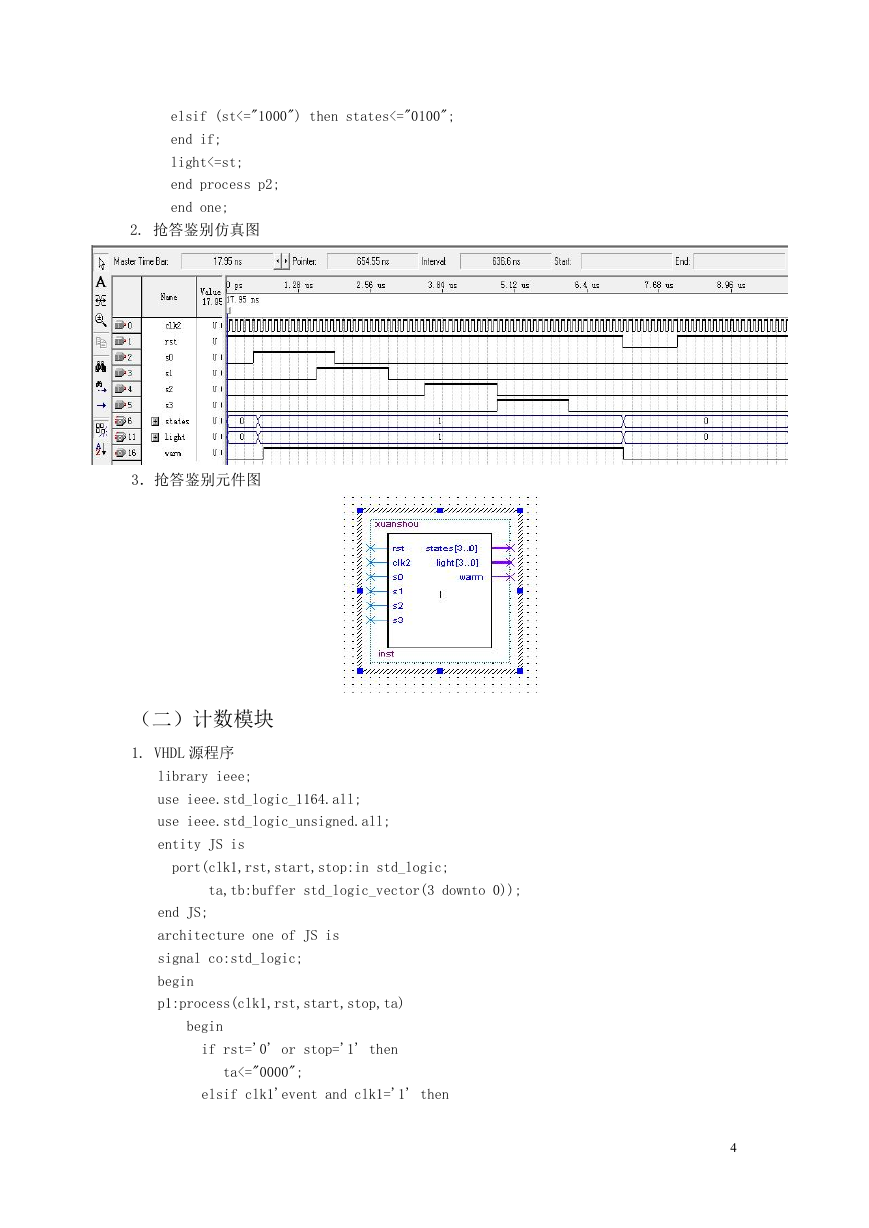

3.计数元件图

(三)报警模块

5

�

1. VHDL 源程序

library

ieee;

use ieee.std_logic_1164.all;

entity shengyin is

port(rst:in std_logic;

warn:in std_logic;

clk:in std_logic;

ta,tb:in integer range 0 to 9;

stop:in std_logic;

alm:out std_logic );

end;

architecture bhv of shengyin is

begin

process(warn,ta,tb,stop,clk)

begin

if rst='0'then

alm<='0';

elsif stop='1'then

alm<='0';

elsif ta=0 and tb=0 then

alm<=clk;

elsif warn='1'then

alm<=clk;

else alm<='0';

end if;

end process;

end;

2.报警仿真图

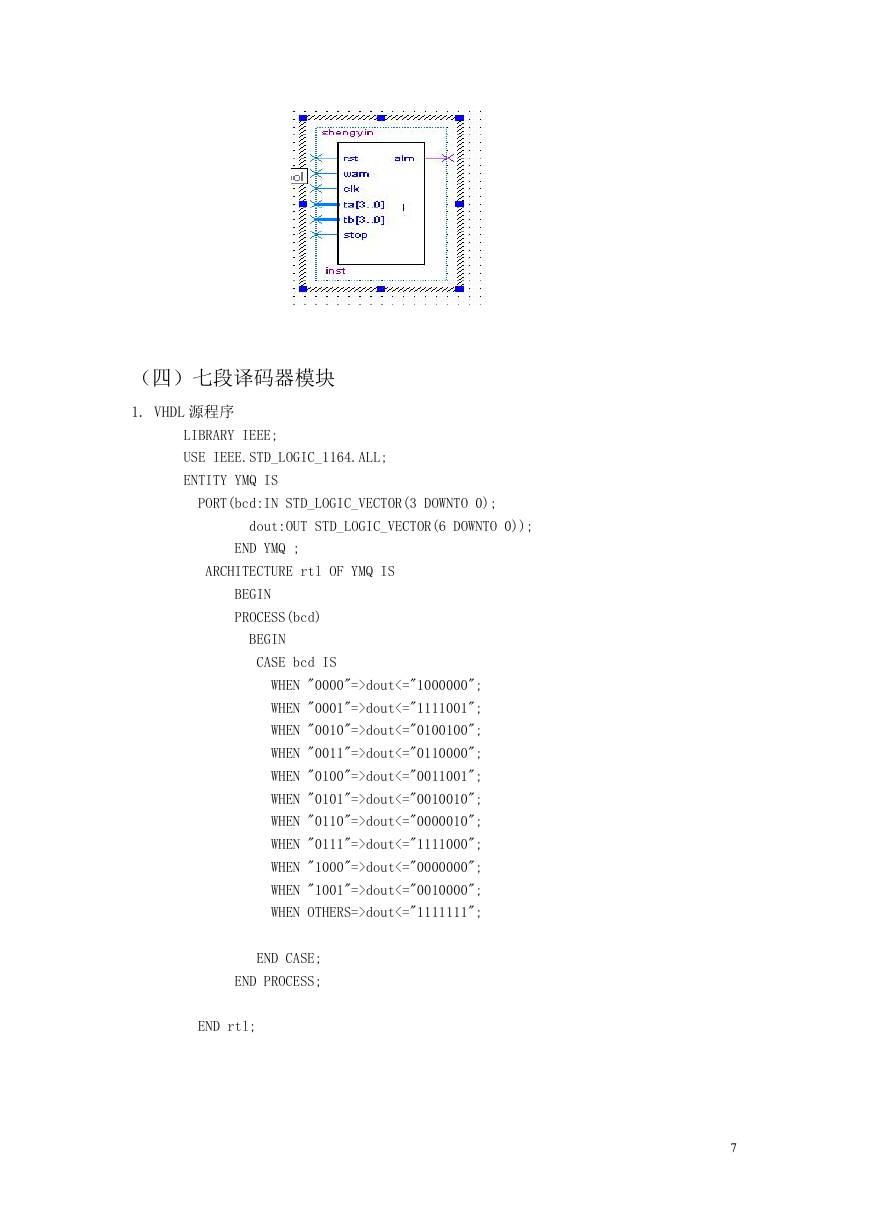

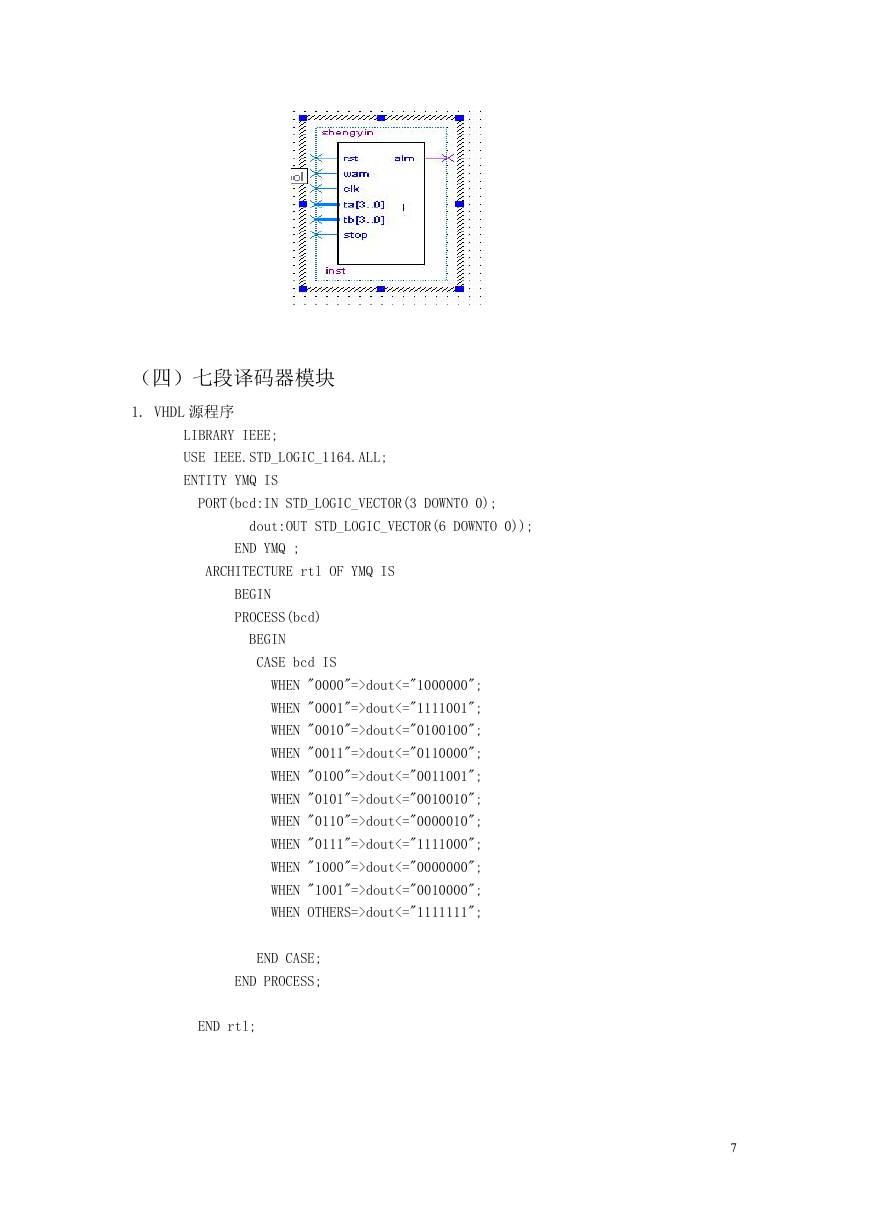

3.报警元件图

6

�

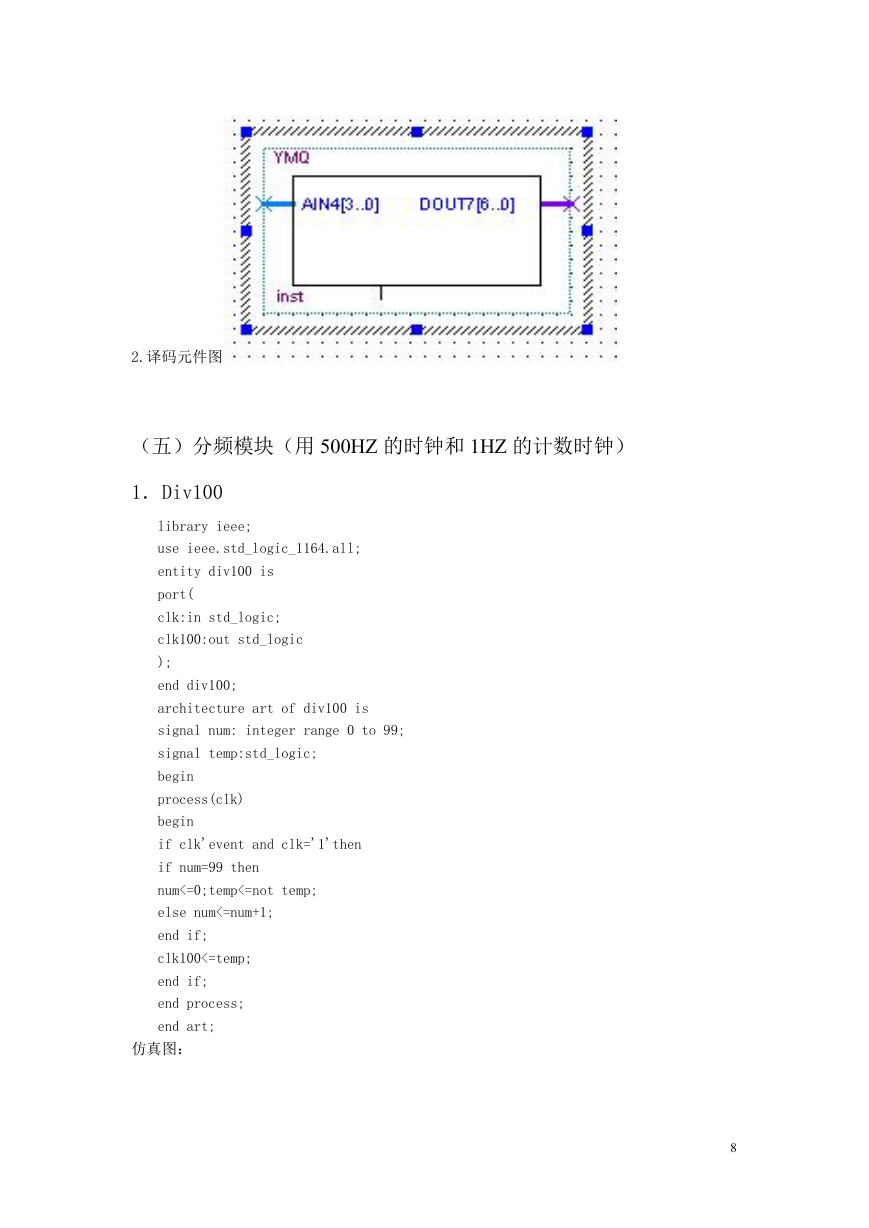

(四)七段译码器模块

1. VHDL 源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY YMQ IS

PORT(bcd:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

dout:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END YMQ ;

ARCHITECTURE rtl OF YMQ IS

BEGIN

PROCESS(bcd)

BEGIN

CASE bcd IS

WHEN "0000"=>dout<="1000000";

WHEN "0001"=>dout<="1111001";

WHEN "0010"=>dout<="0100100";

WHEN "0011"=>dout<="0110000";

WHEN "0100"=>dout<="0011001";

WHEN "0101"=>dout<="0010010";

WHEN "0110"=>dout<="0000010";

WHEN "0111"=>dout<="1111000";

WHEN "1000"=>dout<="0000000";

WHEN "1001"=>dout<="0010000";

WHEN OTHERS=>dout<="1111111";

END CASE;

END PROCESS;

END rtl;

7

�

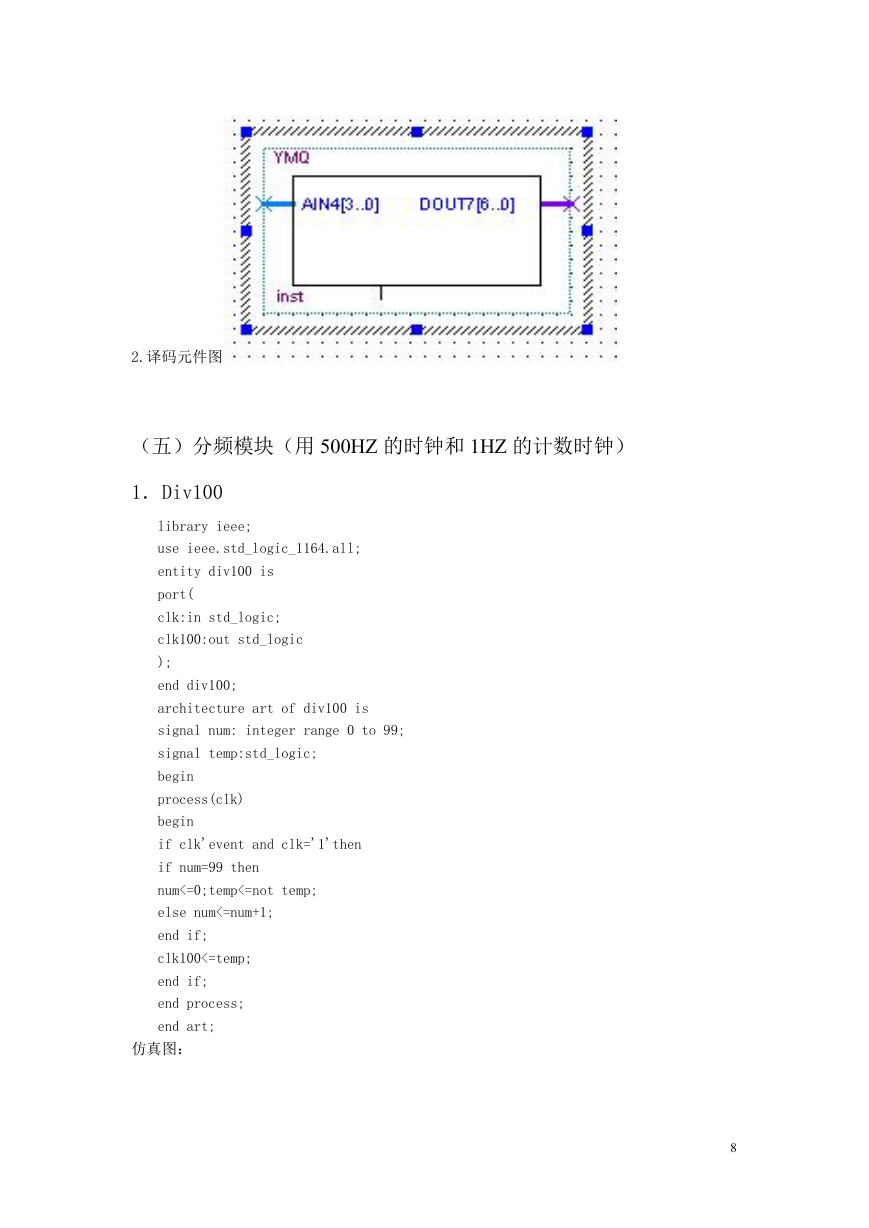

2.译码元件图

(五)分频模块(用 500HZ 的时钟和 1HZ 的计数时钟)

1.Div100

library ieee;

use ieee.std_logic_1164.all;

entity div100 is

port(

clk:in std_logic;

clk100:out std_logic

);

end div100;

architecture art of div100 is

signal num: integer range 0 to 99;

signal temp:std_logic;

begin

process(clk)

begin

if clk'event and clk='1'then

if num=99 then

num<=0;temp<=not temp;

else num<=num+1;

end if;

clk100<=temp;

end if;

end process;

end art;

仿真图:

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc