SPRS294B - TMS320C6713B

Features

Table of Contents

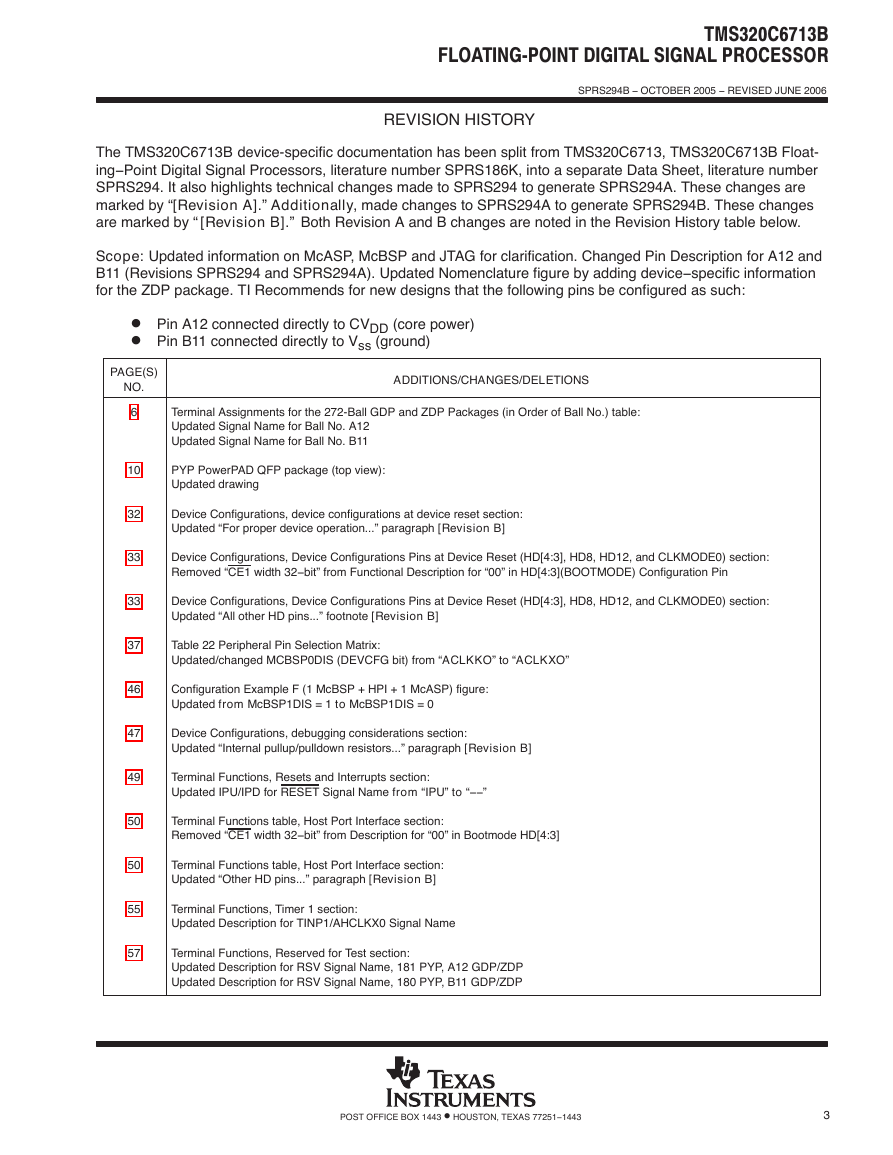

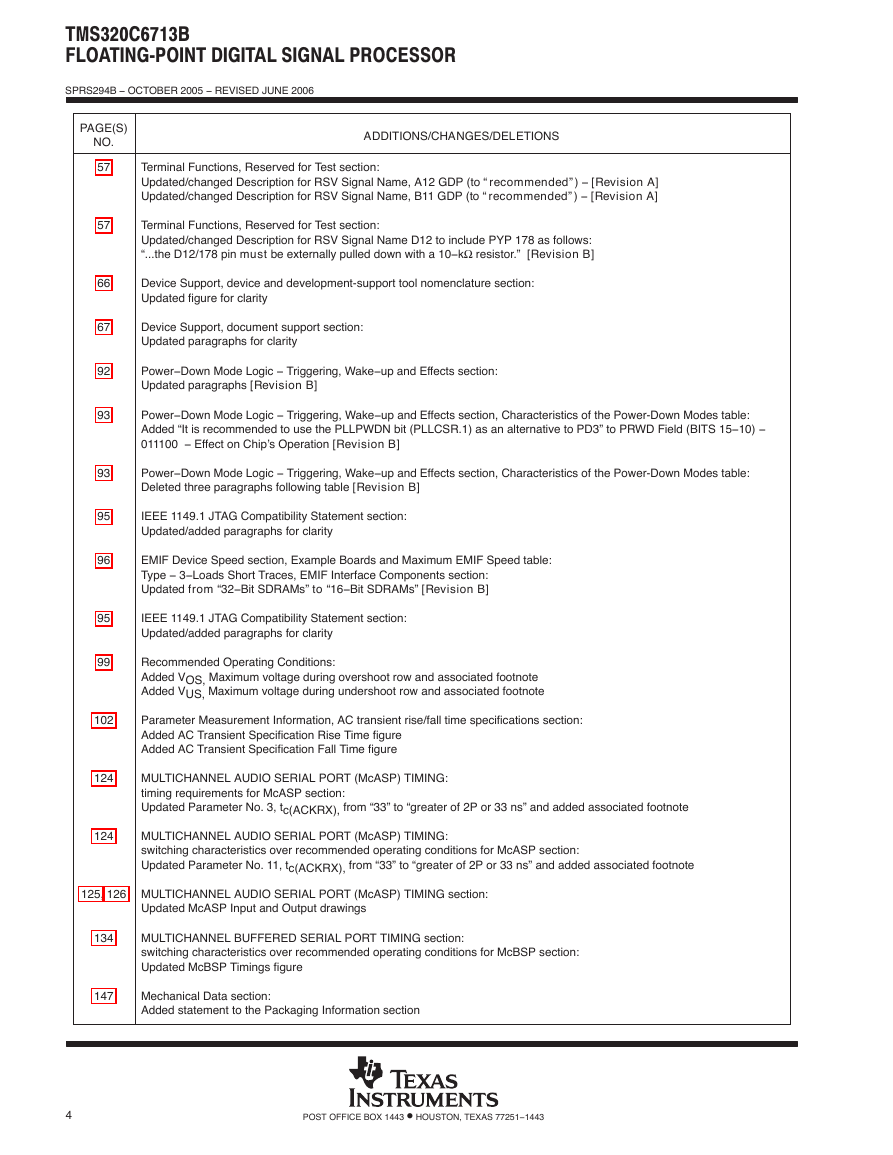

REVISION HISTORY

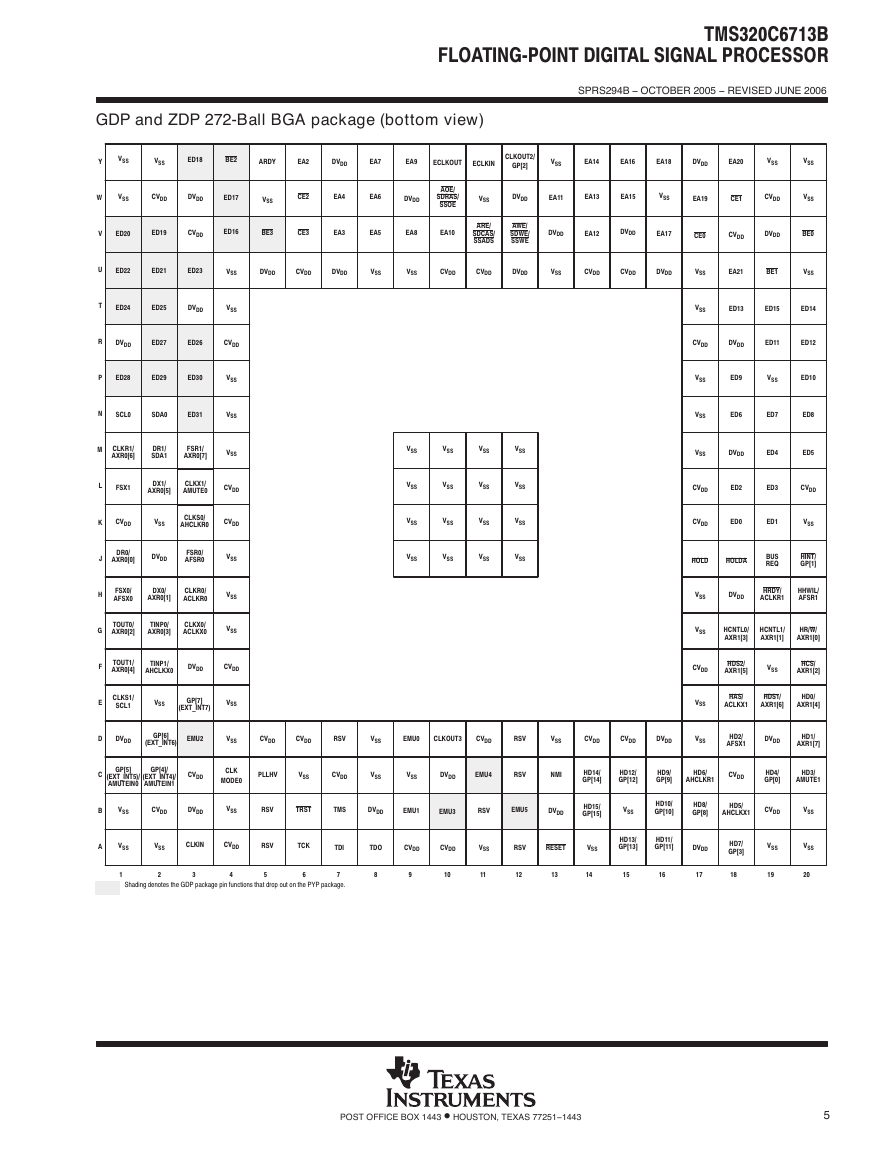

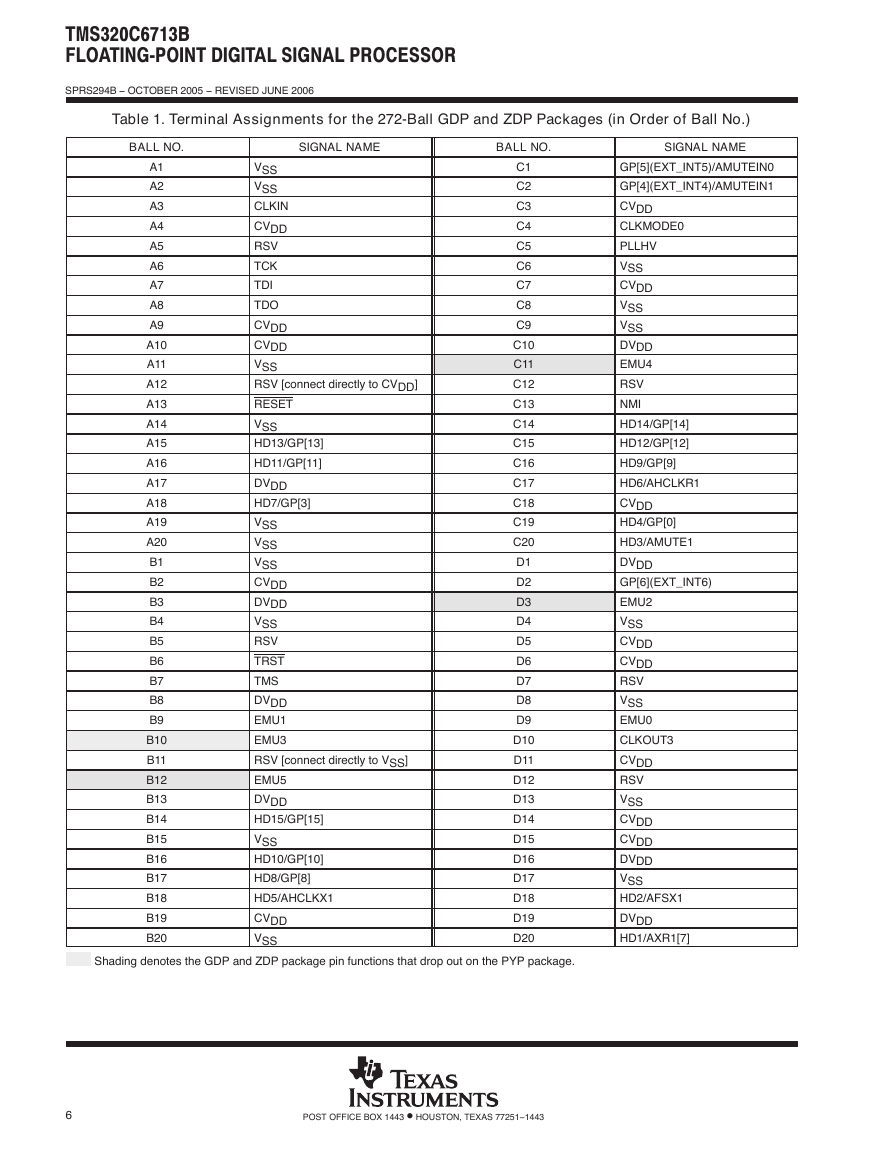

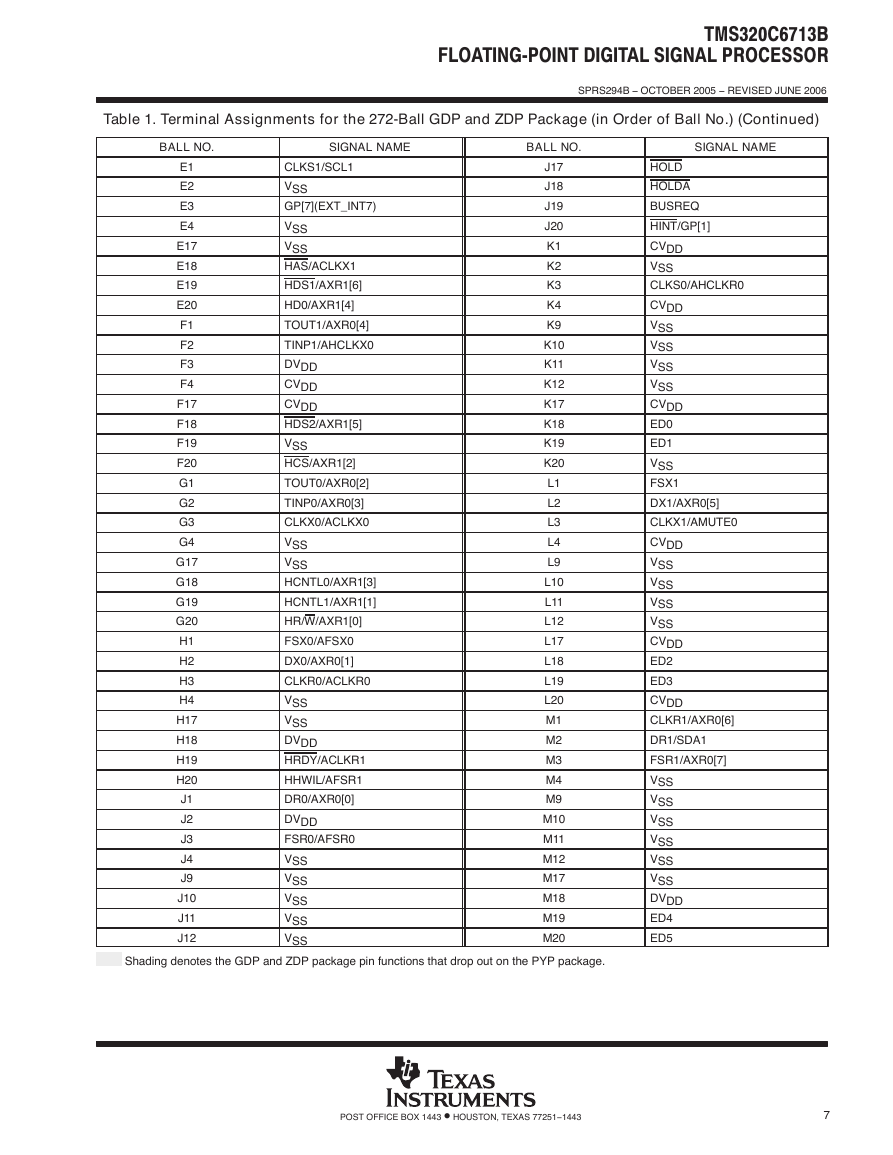

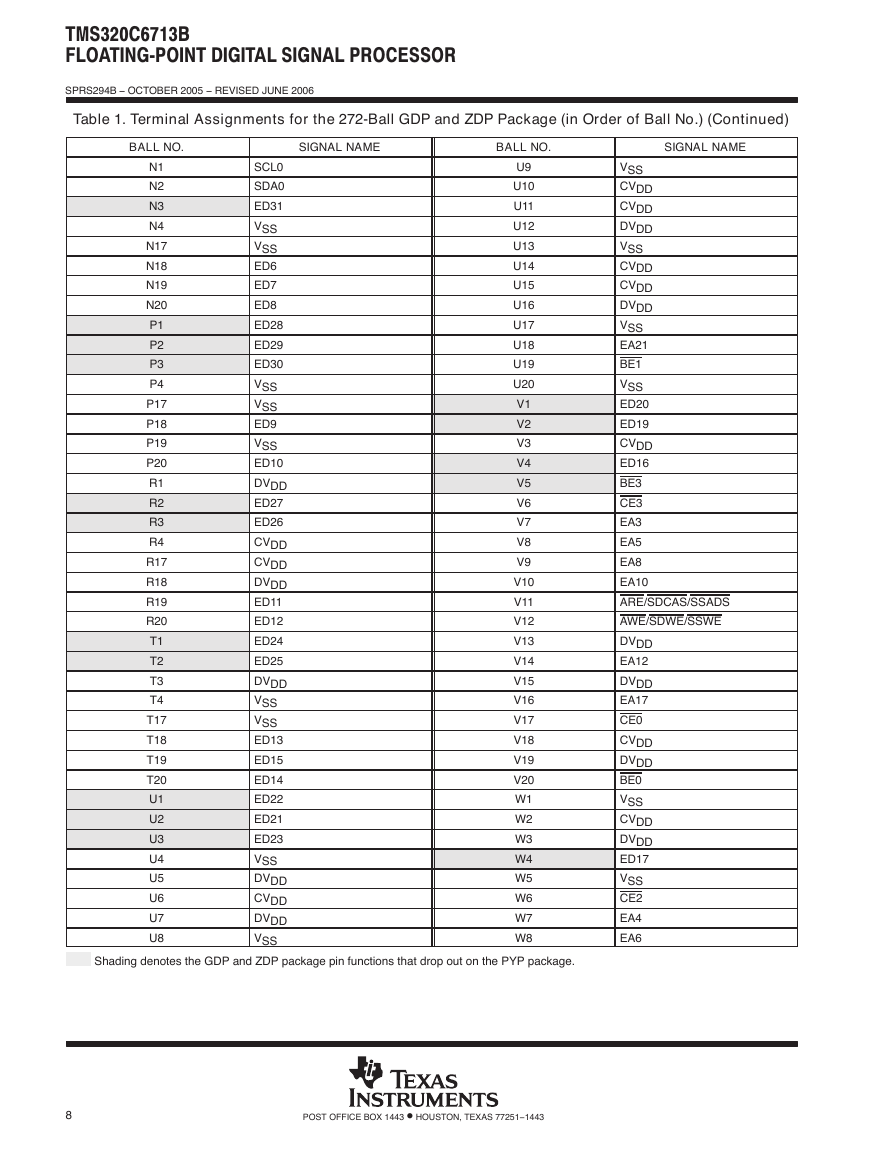

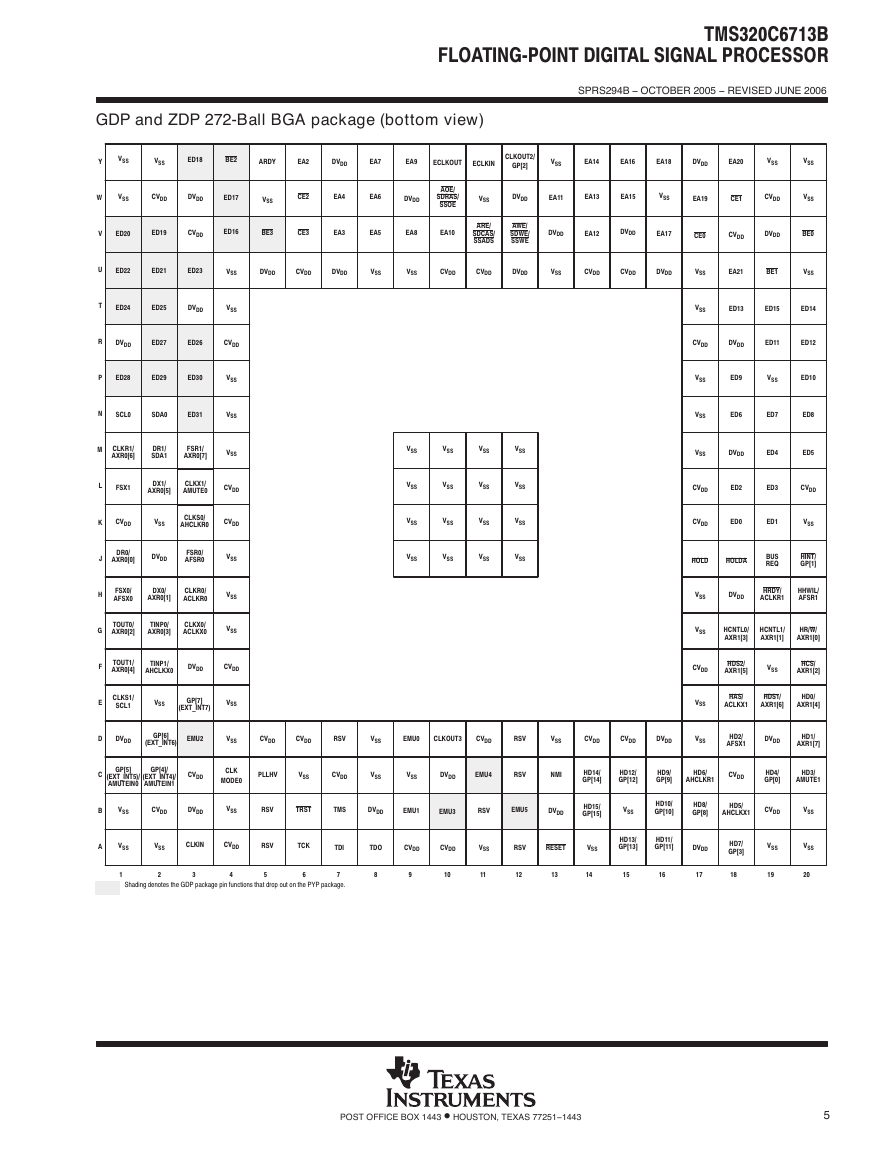

GDP and ZDP 272-Ball BGA package (bottom view)

PYP PowerPAD. QFP package (top view)

description

device characteristics

functional block and CPU (DSP core) diagram

CPU (DSP core) description

memory map summary

L2 memory structure expanded

peripheral register descriptions

signal groups description

DEVICE CONFIGURATIONS

device configurations at device reset

peripheral pin selection at device reset

peripheral selection/device configurations via the DEVCFG control register

multiplexed pins

configuration examples

debugging considerations

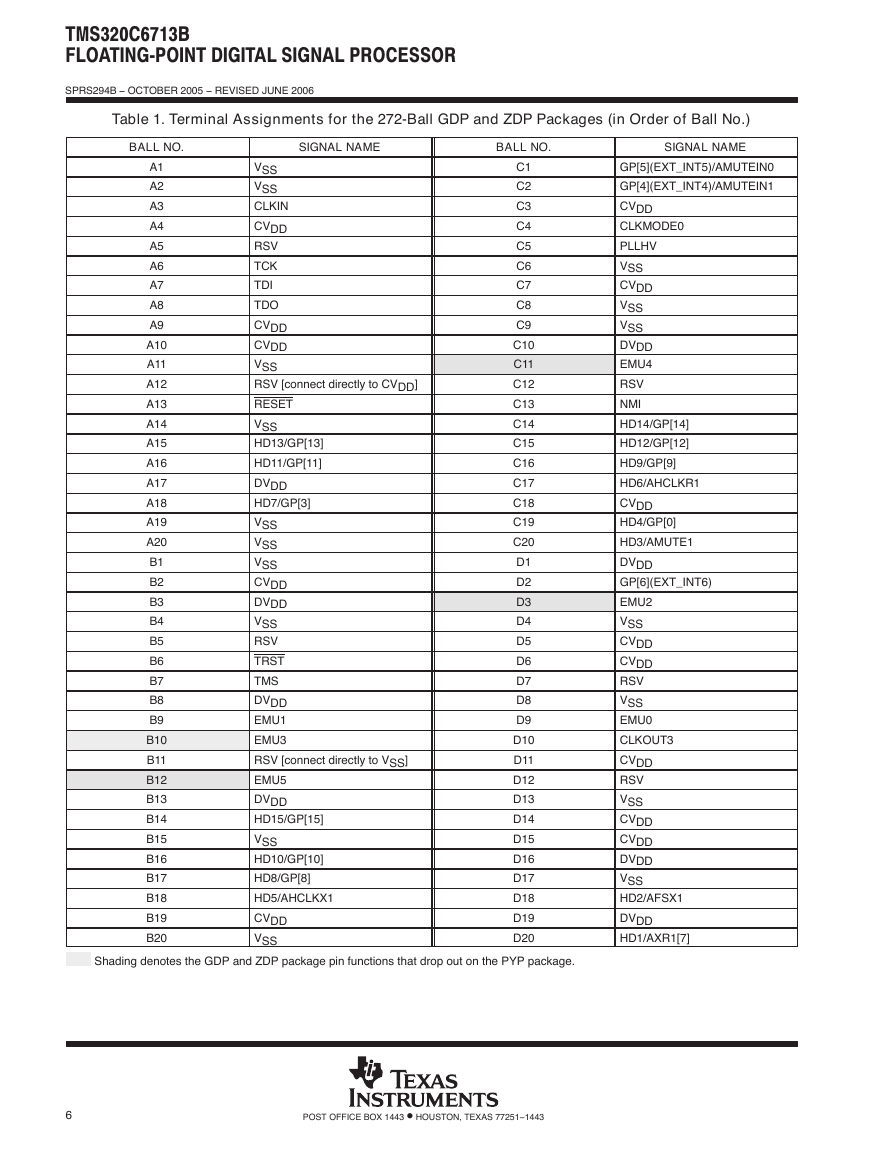

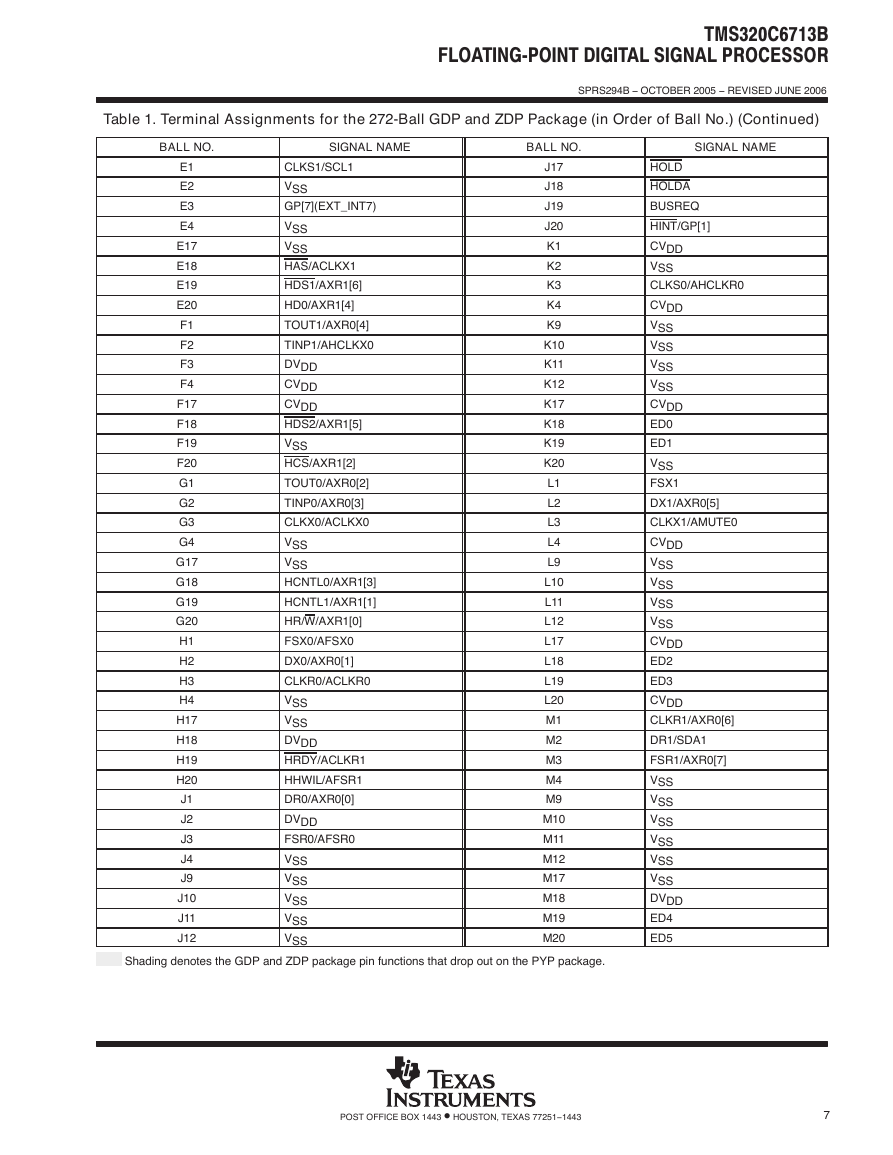

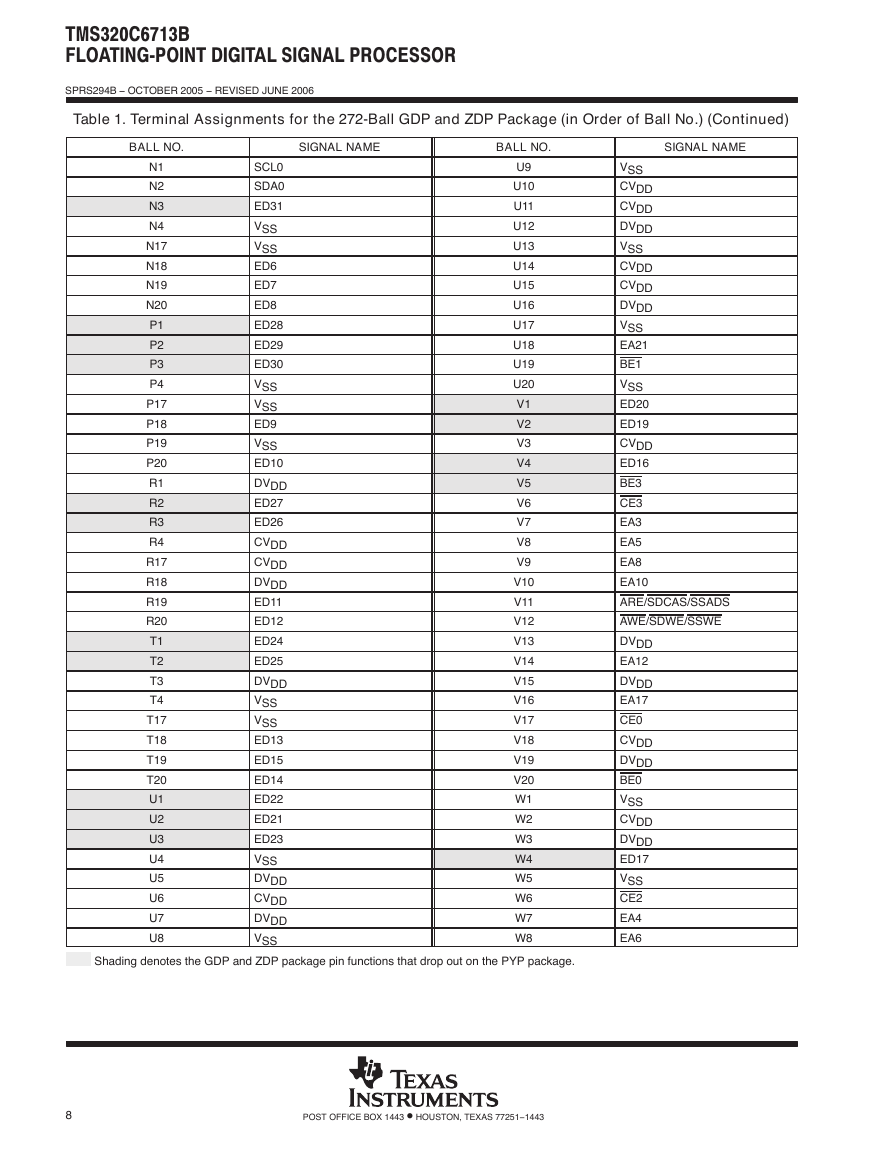

TERMINAL FUNCTIONS

Terminal Functions

development support

Software Development Tools:

Hardware Development Tools:

device support

device and development-support tool nomenclature

documentation support

CPU CSR register description

cache configuration (CCFG) register description

interrupts and interrupt selector

external interrupt sources

EDMA module and EDMA selector

ESEL0 Register (0x01A0 FF00)

ESEL1 Register (0x01A0 FF04)

ESEL3 Register (0x01A0 FF0C)

PLL and PLL controller

multichannel audio serial port (McASP) peripherals

McASP block diagram

multichannel time division multiplexed (TDM) synchronous transfer mode

burst transfer mode

supported bit stream formats for TDM and burst transfer modes

digital audio interface transmitter (DIT) transfer mode (transmitter only)

McASP flexible clock generators

McASP error handling and management

McASP interrupts and EDMA events

I2C

general-purpose input/output (GPIO)

power-down mode logic

triggering, wake-up, and effects

power-supply sequencing

system-level design considerations

power-supply design considerations

power-supply decoupling

IEEE 1149.1 JTAG compatibility statement

EMIF device speed

EMIF big endian mode correctness

bootmode

reset

absolute maximum ratings over operating case temperature range (unless otherwise noted)†

recommended operating conditions†

electrical characteristics over recommended ranges of supply voltage and operating case temperature† ( unless otherwise noted)

PARAMETER MEASUREMENT INFORMATION

signal transition levels

AC transient rise/fall time specifications

timing parameters and board routing analysis

INPUT AND OUTPUT CLOCKS

timing requirements for CLKIN for PYP-200 and GDP/ZDP-225†‡§ (see Figure 31)

timing requirements for CLKIN for PYP-225 and GDP/ZDP-300 †‡§ (see Figure 31)

timing requirements for CLKIN for PYPA-167, GDPA/ZDPA-200 and PYPA-200†‡§ (see Figure 31)

switching characteristics over recommended operating conditions for CLKOUT2†‡ ( see Figure 32)

switching characteristics over recommended operating conditions for CLKOUT3†§

(see Figure 33)

timing requirements for ECLKIN† (see Figure 34)

switching characteristics over recommended operating conditions for ECLKOUT‡§#

(see Figure 35)

ASYNCHRONOUS MEMORY TIMING

timing requirements for asynchronous memory cycles†‡§ (see Figure 36-Figure 37)

switching characteristics over recommended operating conditions for asynchronous memory cyclesद (see Figure 36-Figure 37)

SYNCHRONOUS-BURST MEMORY TIMING

timing requirements for synchronous-burst SRAM cycles† (see Figure 38)

switching characteristics over recommended operating conditions for synchronous-burst SRAM cycles†‡ ( see Figure 38 and Figure 39)

SYNCHRONOUS DRAM TIMING

timing requirements for synchronous DRAM cycles† (see Figure 40)

switching characteristics over recommended operating conditions for synchronous DRAM cycles†‡ ( see Figure 40- Figure 46)

HOLD\/HOLDA\ TIMING

timing requirements for the HOLD\/HOLDA\ cycles† (see Figure 47)

switching characteristics over recommended operating conditions for the HOLD\/HOLDA\ cycles†‡ ( see Figure 47)

BUSREQ TIMING

switching characteristics over recommended operating conditions for the BUSREQ cycles ( see Figure 48)

RESET TIMING

timing requirements for reset†‡ (see Figure 49)

switching characteristics over recommended operating conditions during reset¶ (see Figure 49)

EXTERNAL INTERRUPT TIMING

timing requirements for external interrupts† (see Figure 50)

MULTICHANNEL AUDIO SERIAL PORT (McASP) TIMING

timing requirements for McASP (see Figure 51 and Figure 52)

switching characteristics over recommended operating conditions for McASP‡ (see Figure 51 and Figure 52)

INTER-INTEGRATED CIRCUITS (I2C) TIMING

timing requirements for I2C timings† ( see Figure 53)

switching characteristics for I2C timings† (see Figure 54)

HOST-PORT INTERFACE TIMING

timing requirements for host-port interface cycles†‡ ( see Figure 55, Figure 56, Figure 57, and Figure 58)

switching characteristics over recommended operating conditions during host-port interface cycles†‡ ( see Figure 55, Figure 56, Figure 57, and Figure 58)

MULTICHANNEL BUFFERED SERIAL PORT TIMING

timing requirements for McBSP†‡ (see Figure 59)

switching characteristics over recommended operating conditions for McBSP†‡ (see Figure 59)

timing requirements for FSR when GSYNC = 1 (see Figure 60)

timing requirements for McBSP as SPI master or slave: CLKSTP = 10b, CLKXP = 0†‡ (see Figure 61)

switching characteristics over recommended operating conditions for McBSP as SPI master or slave: CLKSTP = 10b, CLKXP = 0†‡ ( see Figure 61)

timing requirements for McBSP as SPI master or slave: CLKSTP = 11b, CLKXP = 0†‡ (see Figure 62)

switching characteristics over recommended operating conditions for McBSP as SPI master or slave: CLKSTP = 11b, CLKXP = 0†‡ ( see Figure 62)

timing requirements for McBSP as SPI master or slave: CLKSTP = 10b, CLKXP = 1†‡ (see Figure 63)

switching characteristics over recommended operating conditions for McBSP as SPI master or slave: CLKSTP = 10b, CLKXP = 1†‡ ( see Figure 63)

timing requirements for McBSP as SPI master or slave: CLKSTP = 11b, CLKXP = 1†‡ (see Figure 64)

switching characteristics over recommended operating conditions for McBSP as SPI master or slave: CLKSTP = 11b, CLKXP = 1†‡ ( see Figure 64)

TIMER TIMING

timing requirements for timer inputs† (see Figure 65)

switching characteristics over recommended operating conditions for timer outputs† ( see Figure 65)

GENERAL-PURPOSE INPUT/OUTPUT (GPIO) PORT TIMING

timing requirements for GPIO inputs†‡ (see Figure 66)

switching characteristics over recommended operating conditions for GPIO outputs†§

(see Figure 66)

JTAG TEST-PORT TIMING

timing requirements for JTAG test port (see Figure 67)

switching characteristics over recommended operating conditions for JTAG test port ( see Figure 67)

MECHANICAL DATA

thermal resistance characteristics (S-PBGA package) for GDP

thermal resistance characteristics (S-PBGA package) for ZDP

thermal resistance characteristics (S-PQFP-G208 package) for PYP

packaging information

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc