RDA5807M

SINGLE-CHIP BROADCAST FM RADIO TUNER Rev.1.0–May.2011

1 General Description

The RDA5807M series is the newest generation single-chip

broadcast FM stereo radio tuner with fully integrated

synthesizer, IF selectivity, RDS/RBDS and MPX decoder.

The tuner uses the CMOS process, support multi-interface

and require the least external component. All these make it

very suitable for portable devices.

The RDA5807M series has a powerful low-IF digital audio

processor, this make it have optimum sound quality with

varying reception conditions.

The RDA5807M series support frequency range is from

50MHz to 115MHz.

Figure1-1. RDA5807M Top View

1.1 Features

CMOS single-chip fully-integrated FM tuner

Mono/stereo switch

Low power consumption

Total current consumption lower than 20mA at 3.0V

Soft mute

High cut

power supply when under normal situation

Programmable de-emphasis (50/75 s)

Support worldwide frequency band

Receive signal strength indicator (RSSI) and SNR

50 -115 MHz

Bass boost

Support flexible channel spacing mode

Volume control and mute

100KHz, 200KHz, 50KHz and 25KHz

Line-level analog output voltage

Support RDS/RBDS

Digital low-IF tuner

Image-reject down-converter

High performance A/D converter

IF selectivity performed internally

32.768 KHz 12M,24M,13M,26M,19.2M,38.4MHz

Reference clock

Only support 2-wire bus interface

Directly support 32Ω resistance loading

Integrated LDO regulator

Fully integrated digital frequency synthesizer

1.8 to 3.3 V operation voltage

Fully integrated on-chip RF and IF VCO

MSOP-10pins

Fully integrated on-chip loop filter

Autonomous search tuning

Support 32.768KHz crystal oscillator

Digital auto gain control (AGC)

Digital adaptive noise cancellation

1.2

Applications

Cellular handsets

MP3, MP4 players

Portable radios

Copyright © RDA Microelectronics Inc. 2006. All rights are reserved.

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

67891012345RDA5807MLOUTROUTGNDVDDRCLKGNDFMINGNDSCLKSDIO�

RDA Microelectronics, Inc. RDA5807M FM Tuner V1.0

PDAs, Notebook

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

Page 2 of 23

�

RDA Microelectronics, Inc. RDA5807M FM Tuner V1.0

Table of Contents

1 General Description .................................................................................................................................... 1

1.1

1.2

Features ......................................................................................................................................... 1

Applications .................................................................................................................................... 1

Table of Contents ................................................................................................................................................. 3

2

Functional Description................................................................................................................................ 4

2.1

2.2

2.3

2.4

2.5

FM Receiver .................................................................................................................................. 4

Synthesizer .................................................................................................................................... 4

Power Supply ................................................................................................................................ 4

RESET and Control Interface select ............................................................................................. 5

Control Interface ........................................................................................................................... 5

3 Electrical Characteristics ........................................................................................................................... 6

4 Receiver Characteristics ............................................................................................................................. 7

5

Serial Interface ............................................................................................................................................ 8

I2C Interface Timing ...................................................................................................................... 8

5.1

6 Register Definition ...................................................................................................................................... 9

7

Pins Description ......................................................................................................................................... 14

8 Application Diagram ................................................................................................................................. 16

8.1

RDA5807M Common Application : ........................................................................................... 16

8.1.1

Bill of Materials: ......................................................................................................................... 17

9

Physical Dimension ................................................................................................................................... 18

10 PCB Land Pattern ..................................................................................................................................... 19

Change List ........................................................................................................................................................ 22

11 Notes: ....................................................................................................................................................... 22

12 Contact Information ................................................................................................................................. 23

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

Page 3 of 23

�

RDA Microelectronics, Inc. RDA5807M FM Tuner V1.0

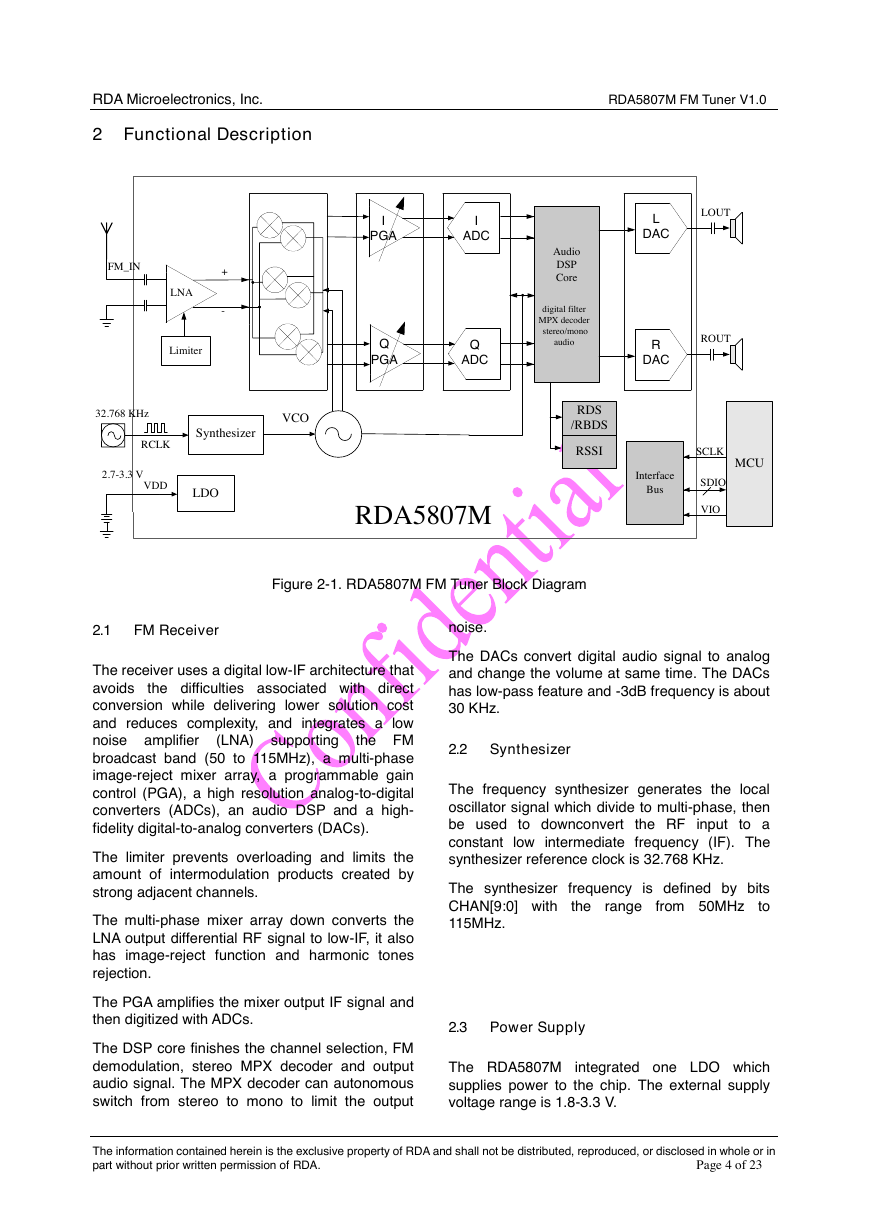

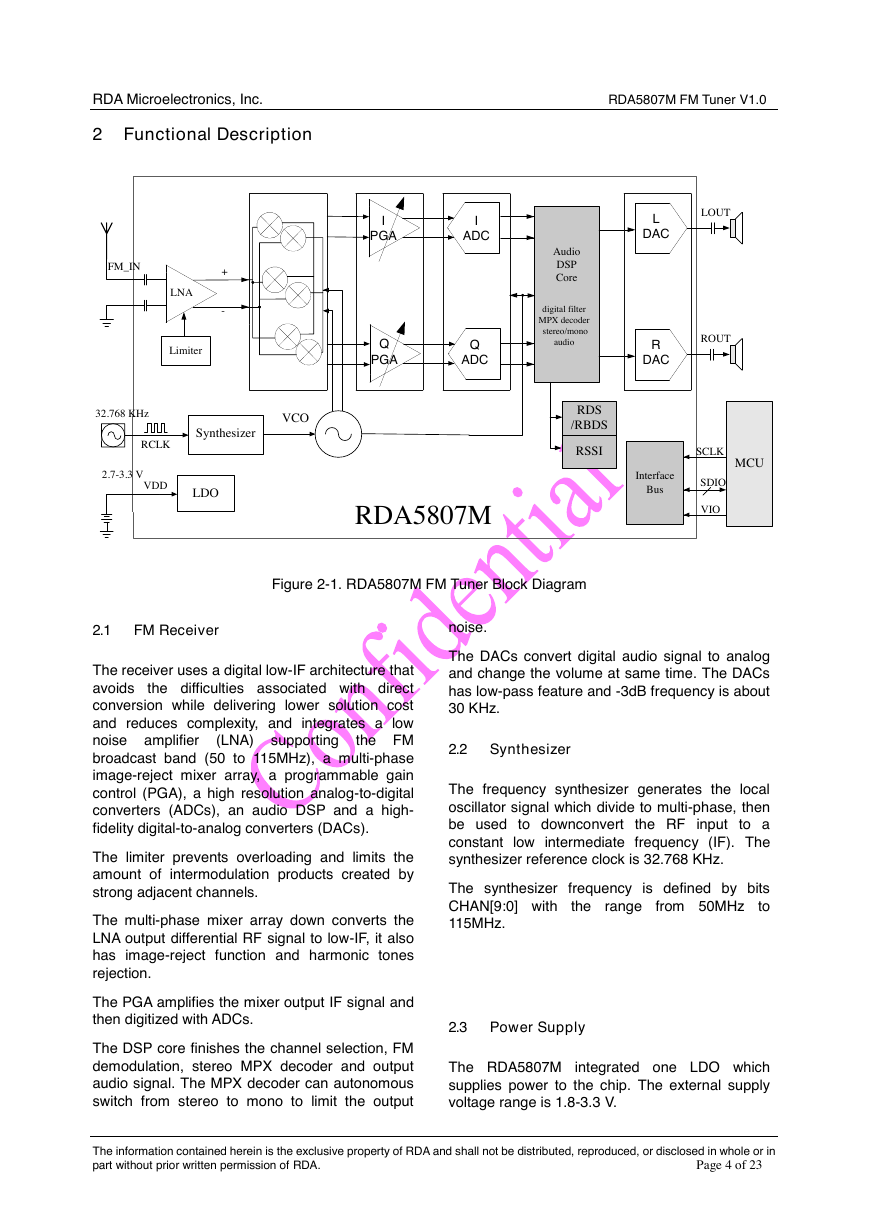

2 Functional Description

Figure 2-1. RDA5807M FM Tuner Block Diagram

2.1

FM Receiver

The receiver uses a digital low-IF architecture that

avoids

the difficulties associated with direct

conversion while delivering lower solution cost

and reduces complexity, and integrates a low

noise amplifier

the FM

broadcast band (50 to 115MHz), a multi-phase

image-reject mixer array, a programmable gain

control (PGA), a high resolution analog-to-digital

converters (ADCs), an audio DSP and a high-

fidelity digital-to-analog converters (DACs).

(LNA) supporting

The limiter prevents overloading and limits the

amount of intermodulation products created by

strong adjacent channels.

The multi-phase mixer array down converts the

LNA output differential RF signal to low-IF, it also

has image-reject function and harmonic tones

rejection.

The PGA amplifies the mixer output IF signal and

then digitized with ADCs.

The DSP core finishes the channel selection, FM

demodulation, stereo MPX decoder and output

audio signal. The MPX decoder can autonomous

switch from stereo to mono to limit the output

noise.

The DACs convert digital audio signal to analog

and change the volume at same time. The DACs

has low-pass feature and -3dB frequency is about

30 KHz.

2.2 Synthesizer

The frequency synthesizer generates the local

oscillator signal which divide to multi-phase, then

be used to downconvert the RF input to a

constant low intermediate frequency (IF). The

synthesizer reference clock is 32.768 KHz.

The synthesizer frequency is defined by bits

CHAN[9:0] with

to

115MHz.

from 50MHz

the range

2.3 Power Supply

The RDA5807M

integrated one LDO which

supplies power to the chip. The external supply

voltage range is 1.8-3.3 V.

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

Page 4 of 23

IADCLDACRDACQADC+-Audio DSP Coredigital filter MPX decoder stereo/monoaudioVCOSynthesizerInterfaceBusRSSIVIOSDIOSCLKMCURDA5807MLOUTROUTFM_INRCLK2.7-3.3 V32.768 KHzVDDLDOLimiterLNAIPGAQPGARDS /RBDS�

RDA Microelectronics, Inc. RDA5807M FM Tuner V1.0

2.4 RESET and Control Interface select

The RDA5807M is RESET itself When VIO is

Power up. And also support soft reset by trigger

02H BIT1 from 0 to 1. T he

only

support I2C control interface bus mode.

RDA5807M

2.5 Control Interface

The RDA5807M only supports

interface.

I2C control

I2C

interface

to

is compliant

I2C Bus

The

Specification 2.1. It includes two pins: SCLK and

SDIO. A I2C interface transfer begins with START

condition, a command byte and data bytes, each

byte has a followed ACK (or NACK) bit, and ends

with STOP condition. The command byte includes

a 7-bit chip address (0010000b) and a R/W bit.

The ACK (or NACK) is always sent out by receiver.

When in write transfer, data bytes is written out

from MCU, and when in read transfer, data bytes

is read out from RDA5807M. There is no visible

register address in I2C interface transfers. The I2C

interface has a fixed start register address (0x02h

for write transfer and 0x0Ah for read transfer), and

an internal incremental address counter. If register

address meets the end of register file, 0x3Ah,

register address will wrap back to 0x00h. For write

transfer, MCU programs registers from register

0x02h high byte, then register 0x02h low byte,

then register 0x03h high byte, till the last register.

RDA5807M always gives out ACK after every byte,

and MCU gives out STOP condition when register

programming is finished. For read transfer, after

command byte from MCU, RDA5807M sends out

register 0x0Ah high byte, then register 0x0Ah low

byte, then register 0x0Bh high byte, till receives

NACK from MCU. MCU gives out ACK for data

bytes besides last data byte. MCU gives out

NACK for last data byte, and then RDA5807M will

return the bus to MCU, and MCU will give out

STOP condition.

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

Page 5 of 23

�

RDA Microelectronics, Inc. RDA5807M FM Tuner V1.0

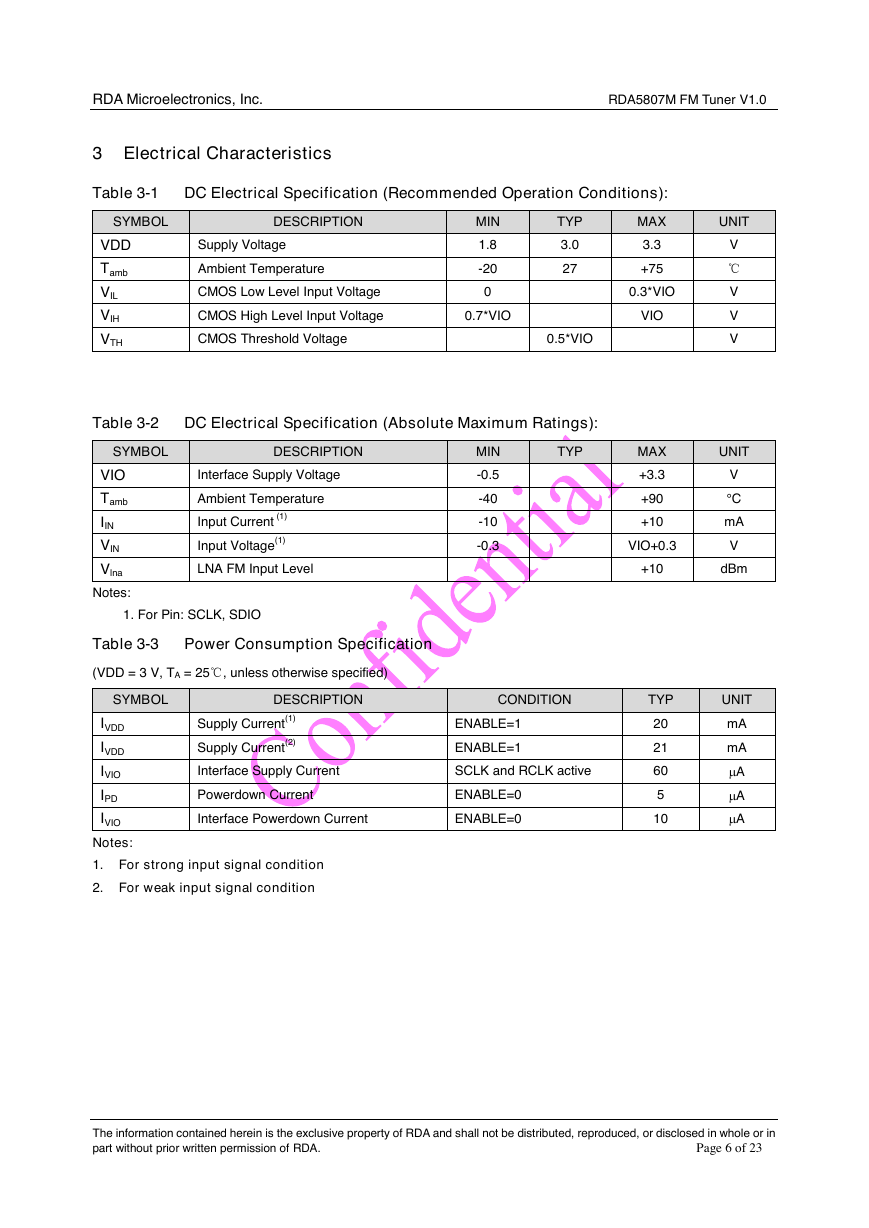

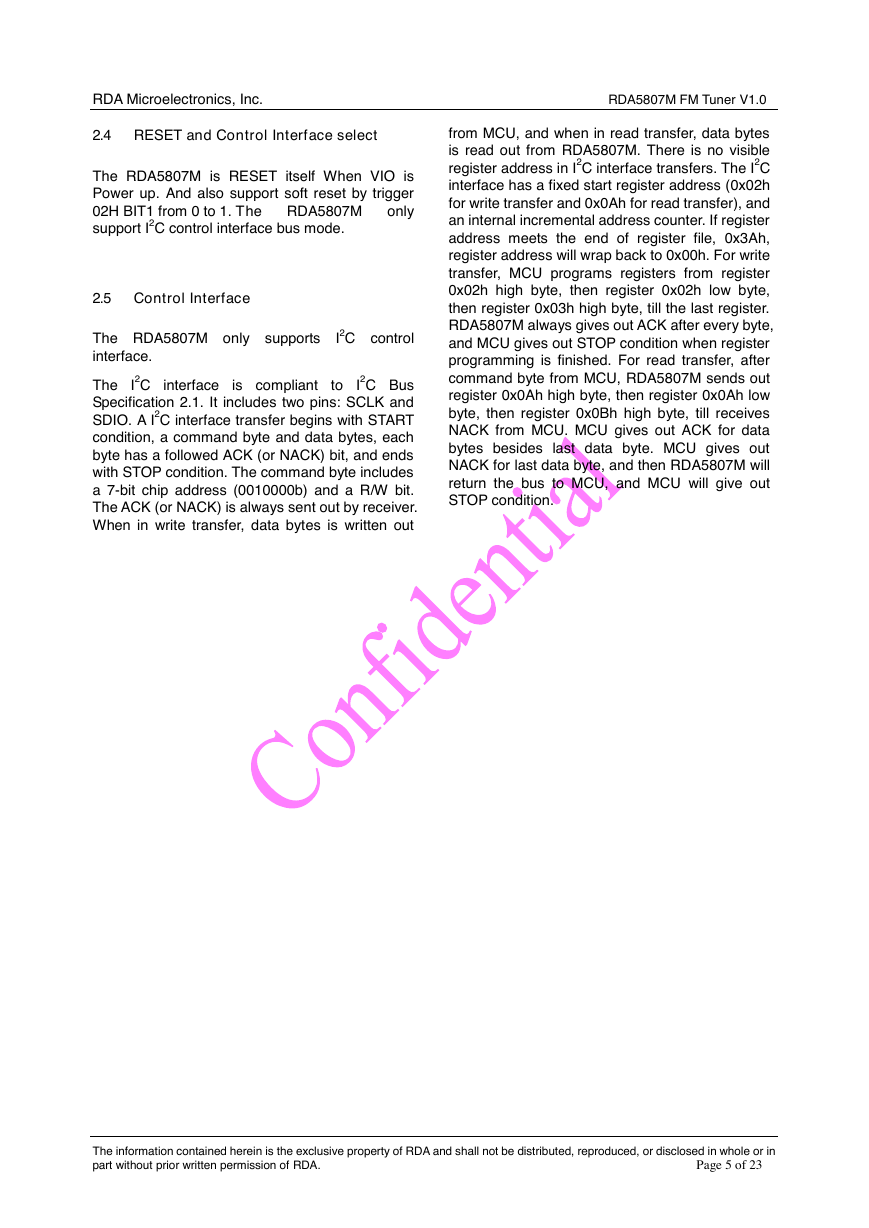

3 Electrical Characteristics

Table 3-1 DC Electrical Specification (Recommended Operation Conditions):

MIN

1.8

-20

0

TYP

3.0

27

MAX

UNIT

3.3

+75

0.3*VIO

VIO

V

℃

V

V

V

CMOS High Level Input Voltage

0.7*VIO

CMOS Threshold Voltage

0.5*VIO

SYMBOL

DESCRIPTION

Supply Voltage

Ambient Temperature

CMOS Low Level Input Voltage

VDD

Tamb

VIL

VIH

VTH

Table 3-2 DC Electrical Specification (Absolute Maximum Ratings):

SYMBOL

DESCRIPTION

VIO

Tamb

IIN

VIN

Vlna

Notes:

Interface Supply Voltage

Ambient Temperature

Input Current (1)

Input Voltage(1)

LNA FM Input Level

1. For Pin: SCLK, SDIO

Table 3-3

Power Consumption Specification

(VDD = 3 V, TA = 25℃, unless otherwise specified)

MIN

-0.5

-40

-10

-0.3

TYP

MAX

+3.3

+90

+10

VIO+0.3

UNIT

V

°C

mA

V

+10

dBm

SYMBOL

DESCRIPTION

CONDITION

TYP

UNIT

IVDD

IVDD

IVIO

IPD

IVIO

Notes:

Supply Current(1)

Supply Current(2)

ENABLE=1

ENABLE=1

Interface Supply Current

SCLK and RCLK active

Powerdown Current

Interface Powerdown Current

ENABLE=0

ENABLE=0

20

21

60

5

10

mA

mA

A

A

A

1. For strong input signal condition

2. For weak input signal condition

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

Page 6 of 23

�

RDA Microelectronics, Inc. RDA5807M FM Tuner V1.0

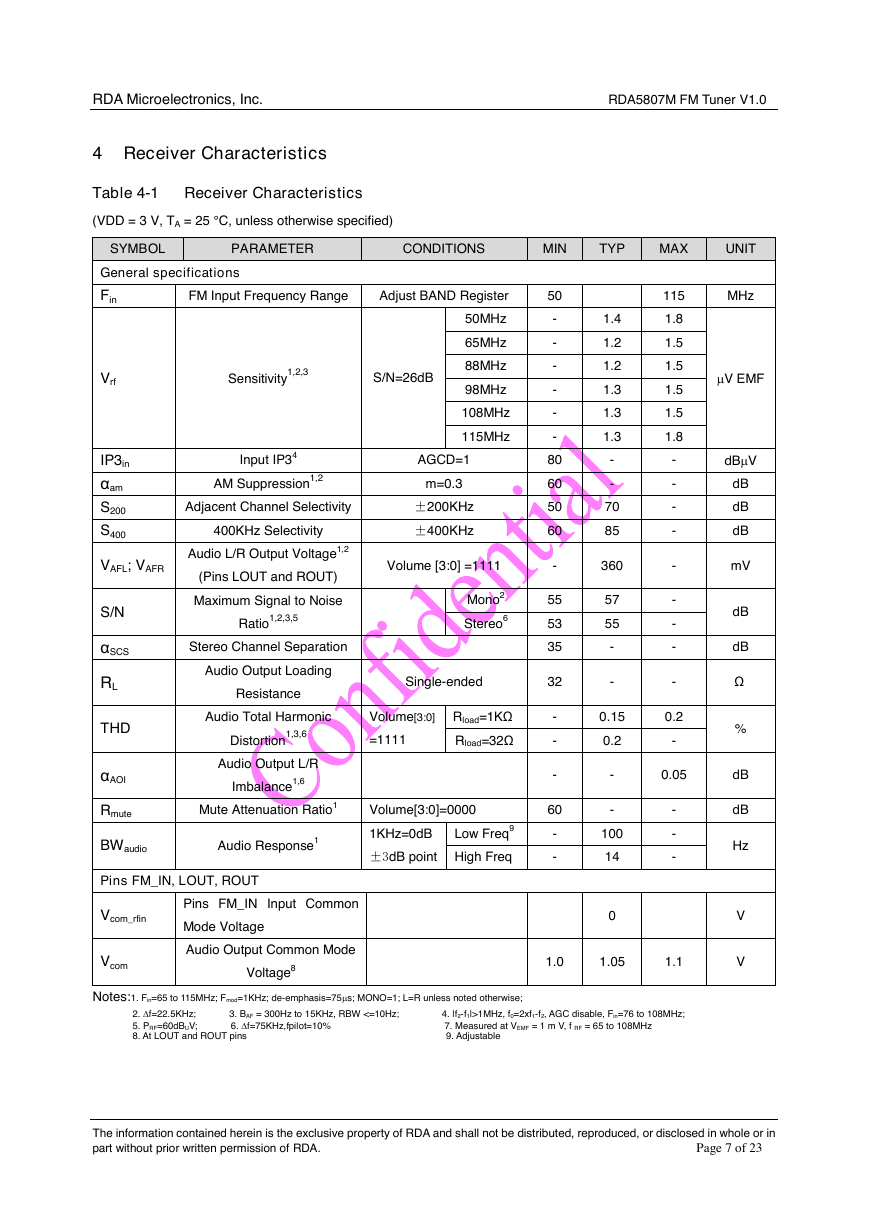

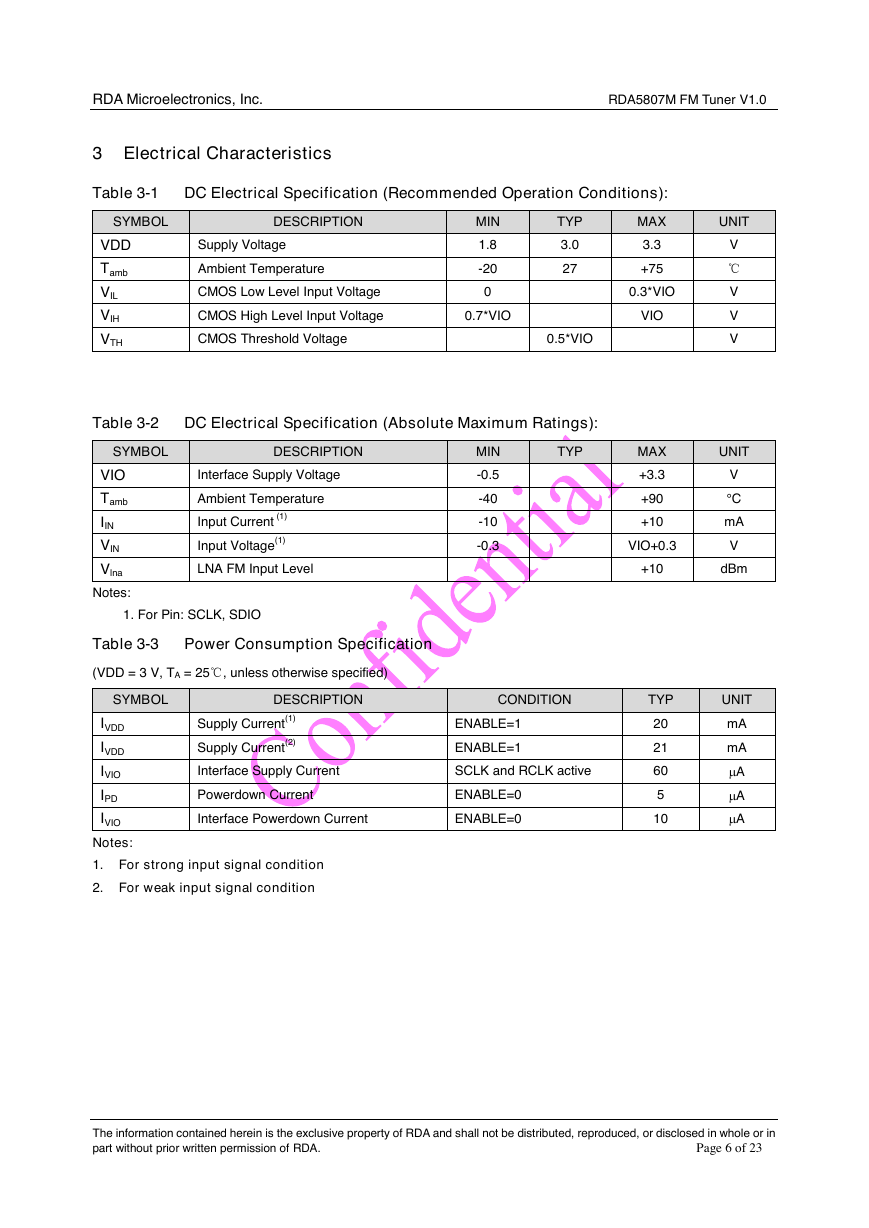

4 Receiver Characteristics

Table 4-1 Receiver Characteristics

(VDD = 3 V, TA = 25 °C, unless otherwise specified)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNIT

General specifications

FM Input Frequency Range

Adjust BAND Register

50

115

MHz

Fin

Vrf

IP3in

αam

S200

S400

VAFL; VAFR

S/N

αSCS

RL

THD

αAOI

Rmute

Sensitivity

1,2,3

S/N=26dB

50MHz

65MHz

88MHz

98MHz

108MHz

115MHz

Input IP34

AM Suppression

1,2

Adjacent Channel Selectivity

400KHz Selectivity

Audio L/R Output Voltage1,2

(Pins LOUT and ROUT)

Maximum Signal to Noise

Ratio

1,2,3,5

AGCD=1

m=0.3

±200KHz

±400KHz

Mono2

Stereo6

Stereo Channel Separation

Audio Output Loading

Resistance

Single-ended

Audio Total Harmonic

Volume[3:0]

Rload=1KΩ

Distortion

1,3,6

Audio Output L/R

Imbalance1,6

=1111

Rload=32Ω

Mute Attenuation Ratio1

Volume[3:0]=0000

60

BWaudio

Audio Response1

Pins FM_IN, LOUT, ROUT

Vcom_rfin

Vcom

Pins FM_IN Input Common

Mode Voltage

Audio Output Common Mode

Voltage8

1KHz=0dB

Low Freq9

±3dB point

High Freq

Volume [3:0] =1111

-

360

1.4

1.2

1.2

1.3

1.3

1.3

-

-

70

85

57

55

-

-

0.15

0.2

-

-

100

14

0

1.8

1.5

1.5

1.5

1.5

1.8

-

-

-

-

-

-

-

-

-

0.2

-

0.05

-

-

-

-

-

-

-

-

-

80

60

50

60

55

53

35

32

-

-

-

-

-

1.0

1.05

1.1

V EMF

dBV

dB

dB

dB

mV

dB

dB

Ω

%

dB

dB

Hz

V

V

Notes:1. Fin=65 to 115MHz; Fmod=1KHz; de-emphasis=75s; MONO=1; L=R unless noted otherwise;

2. f=22.5KHz; 3. BAF = 300Hz to 15KHz, RBW <=10Hz; 4. |f2-f1|>1MHz, f0=2xf1-f2, AGC disable, Fin=76 to 108MHz;

5. PRF=60dBUV; 6. f=75KHz,fpilot=10% 7. Measured at VEMF = 1 m V, f RF = 65 to 108MHz

8. At LOUT and ROUT pins 9. Adjustable

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

Page 7 of 23

�

RDA Microelectronics, Inc. RDA5807M FM Tuner V1.0

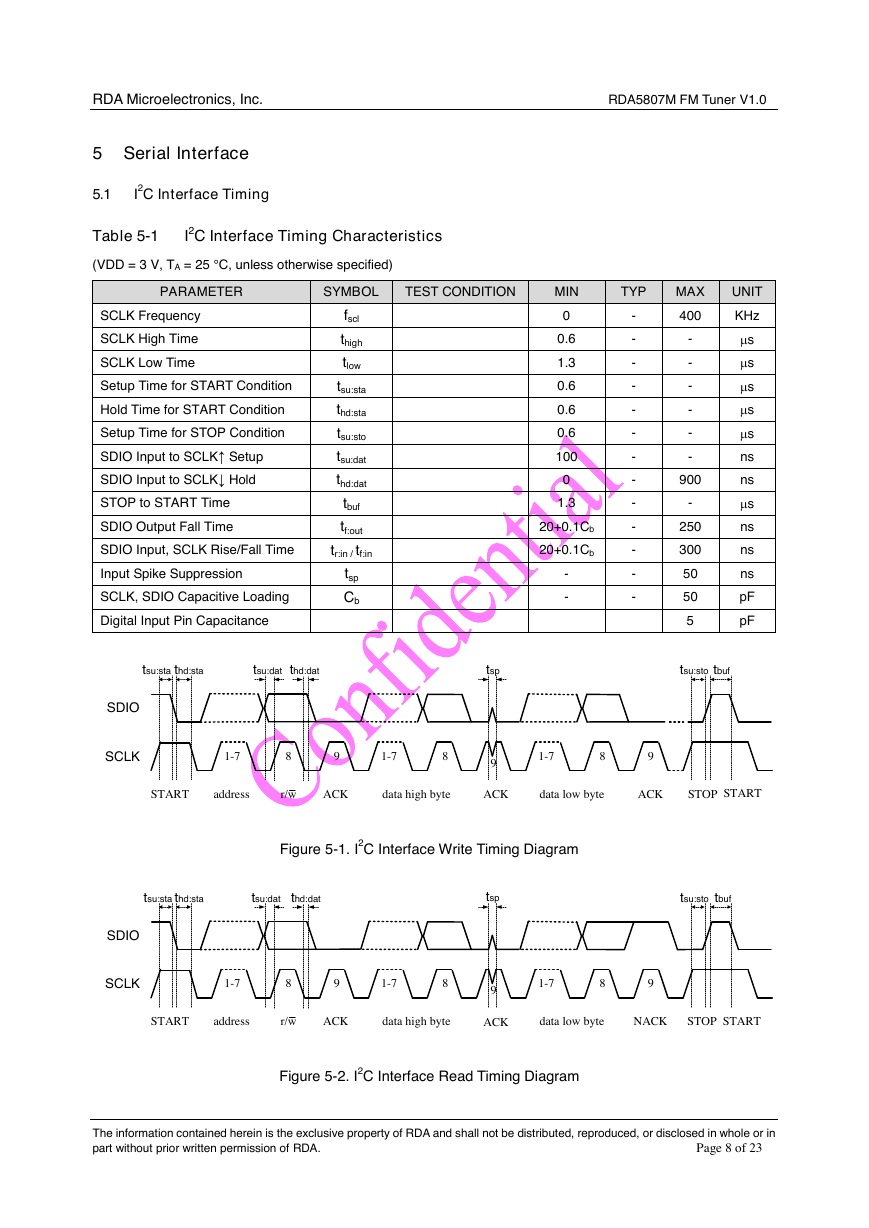

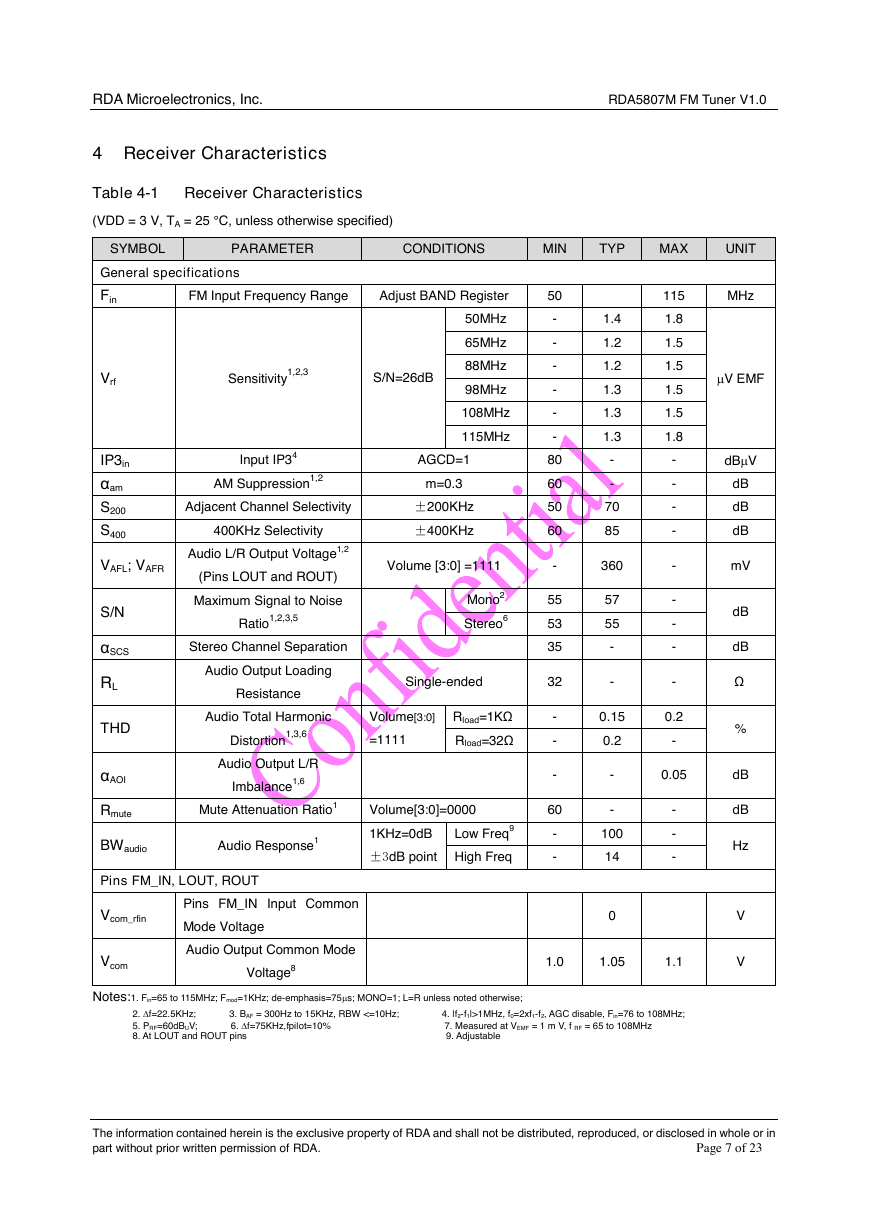

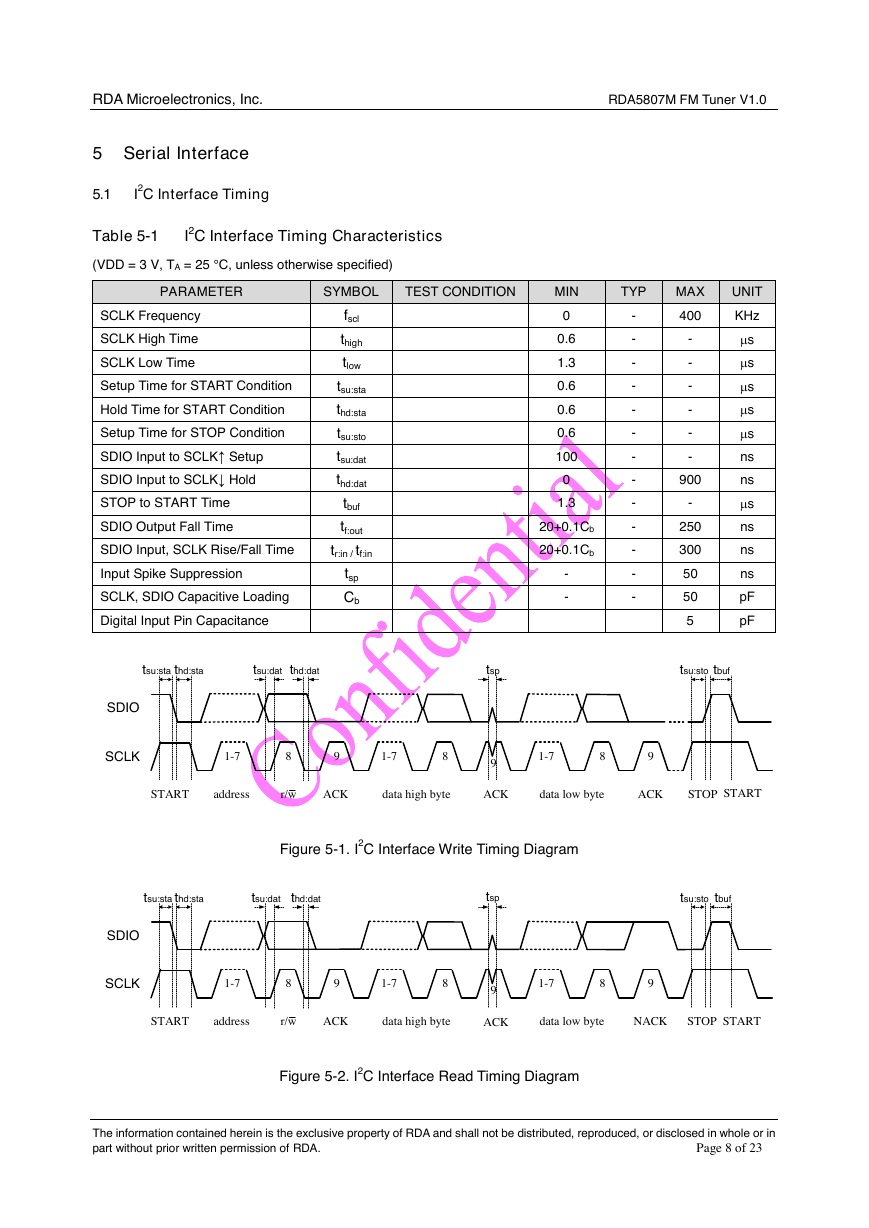

5 Serial Interface

5.1

I2C Interface Timing

Table 5-1

I2C Interface Timing Characteristics

(VDD = 3 V, TA = 25 °C, unless otherwise specified)

PARAMETER

SYMBOL

TEST CONDITION

MIN

TYP

MAX

UNIT

SCLK Frequency

SCLK High Time

SCLK Low Time

Setup Time for START Condition

Hold Time for START Condition

Setup Time for STOP Condition

SDIO Input to SCLK↑ Setup

SDIO Input to SCLK↓ Hold

STOP to START Time

SDIO Output Fall Time

fscl

thigh

tlow

tsu:sta

thd:sta

tsu:sto

tsu:dat

thd:dat

tbuf

tf:out

SDIO Input, SCLK Rise/Fall Time

tr:in / tf:in

Input Spike Suppression

SCLK, SDIO Capacitive Loading

Digital Input Pin Capacitance

tsp

Cb

0

0.6

1.3

0.6

0.6

0.6

100

0

1.3

20+0.1Cb

20+0.1Cb

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

400

KHz

-

-

-

-

-

-

900

-

250

300

50

50

5

s

s

s

s

s

ns

ns

s

ns

ns

ns

pF

pF

Figure 5-1. I2C Interface Write Timing Diagram

Figure 5-2. I2C Interface Read Timing Diagram

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

Page 8 of 23

SCLKSDIO1-7891-7891-789STARTACKdata high byteACKr/waddressdata low byteACKSTOPtsu:stathd:statspSTARTtsu:stotbuftsu:datthd:datSCLKSDIO1-7891-7891-789STARTACKdata high byteACKr/waddressdata low byteNACKSTOPtspSTARTtbuftsu:stathd:statsu:datthd:dattsu:sto�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc