中国科技论文在线

http://www.paper.edu.cn

基于 FPGA 的 A/D 转换采集控制模块设计

1

黄容兰

,万德焕

2

1. 桂林电子科技大学电子工程学院,广西桂林 (541001)

2.桂林空军学院,广西桂林 (541003)

摘 要:本文采用 FPGA 器件 EP1C3T144C8N 处理器,对 A/D 转换芯片 AD7714 进行采样

控制。整个设计在 QuartusⅡ平台下进行软件编程,采用 Verilog 语言描述,实现正确的

AD7714 转换的工作时序控制过程,并将采样的数据存储起来进行处理。本设计可用于微弱信

号采集和实时监控方面,仿真结果显示该模块工作性能稳定、可靠性高、使用方便。

关键词:FPGA;Verilog;A/D 转换;采样控制

中图分类号:TN

1.引言

对于微弱信号的采集和处理,多数是以单片机或 CPU 为控制核心,虽然编程简单,控制

灵活,但缺点是速度慢,控制周期长。单片机的速度极大地限制了 A/D 高速性能的利用。而

FPGA 的时钟频率可高达 100MHz 以上【1】。本设计以高集成度的芯片为核心,进行数据采集

控制、数据时序控制、数据存储等。具有开发周期短、灵活性强、通用能力好、易于开发、

扩展等优点【2】。既降低了设计难度,又加快了产品的开发周期。

2.系统设计

本设计采用 FPGA 芯片 EP1C3T144C8N 来对 AD7714 进行采样控制,并对数据进行存储,

然后进行处理。

2.1 AD7714 芯片介绍

AD7714 是 AD 公司生产的 16/24 位可编程串行模数转换器,能直接从传感器接收低电

平信号并输出串行数字。它具有低噪声(140nV)、低功耗和±0.0015%的精度,片内含可编

程低通滤波寄存器和可读写系统校准寄存器等 8 个可编程的片内寄存器等特点。AD7714 对

于微控制器非常理想,主要应用于低频小信号的测量。

FPGA 对 AD7714 的控制,主要通过对它的片内 8 个寄存器进行设置,如表 1 所示。

表 1 AD7714 内部功能结构表

寄存器位数

8 位

8 位

8 位

8 位

8 位

16 位或者 24 位

24 位

24 位

寄存器

通信寄存器

模式寄存器

高位滤波寄存器

低位滤波寄存器

测试寄存器

数据寄存器

0 刻度校准寄存器

全刻度校准寄存器

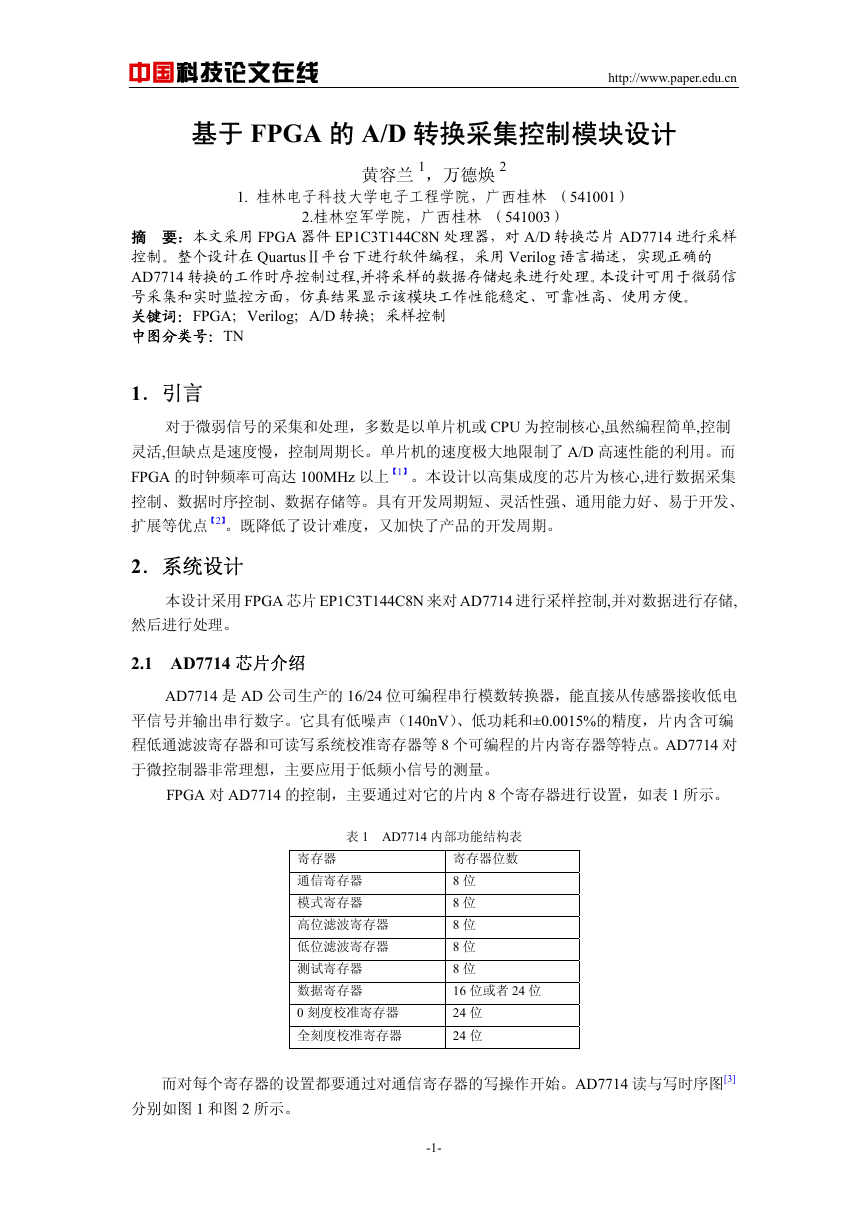

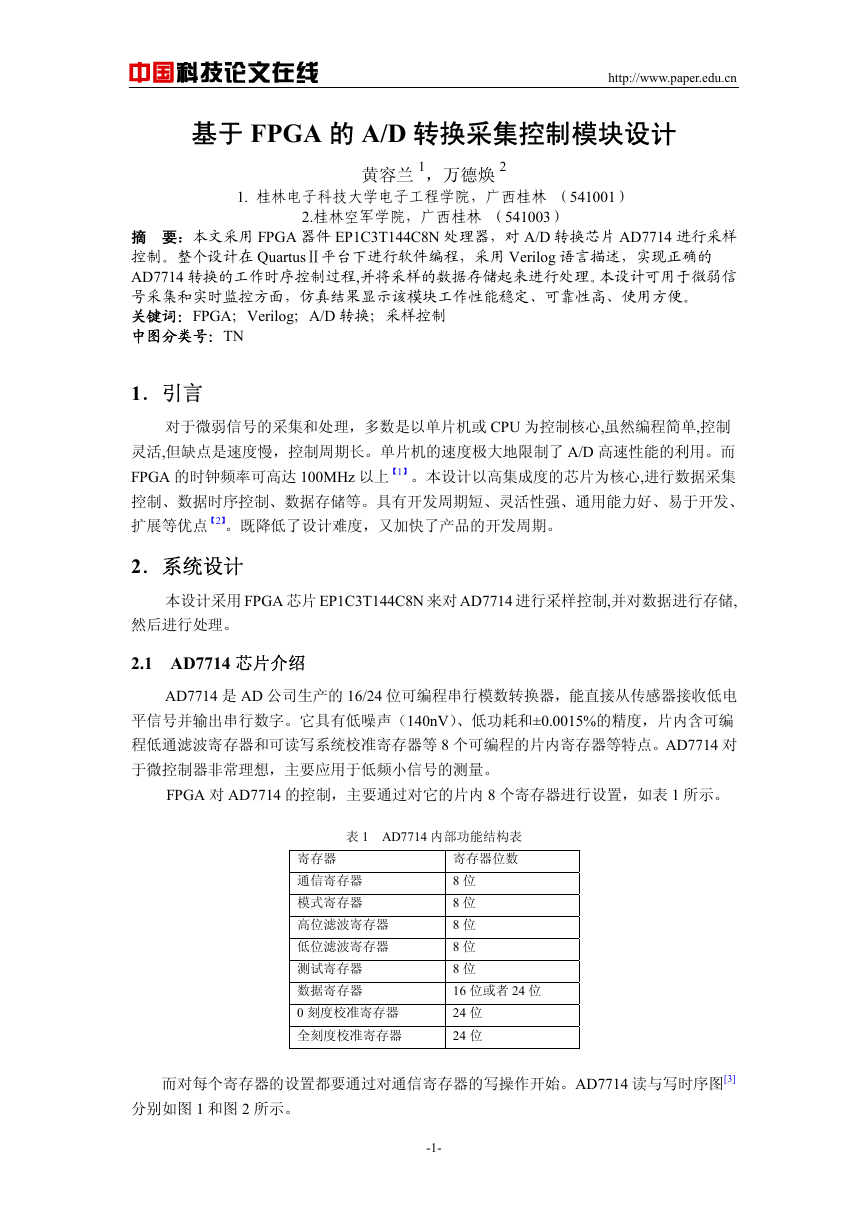

而对每个寄存器的设置都要通过对通信寄存器的写操作开始。AD7714 读与写时序图[3]

分别如图 1 和图 2 所示。

-1-

�

中国科技论文在线

http://www.paper.edu.cn

图 1 AD7714 写时序图 图 2 AD7714 读时序图

从写时序图可知,往芯片 AD7714 的寄存器中写数据时,片选信号CS 必须为低;当CS

为低时,在时钟信号 sclk 上升沿的作用下向 AD7714 中写一位数据。而在读时序图中可以看

到,只有数据在 AD7714 中转换好、且满足片选信号CS 为低电平时,在时钟信号 sclk 下降

沿的作用下从芯片 AD7714 的数据寄存器中读一位数据。当读完最后一位数据后,DRDY 位

自动跳变为高电平。

2.2 系统设计原理

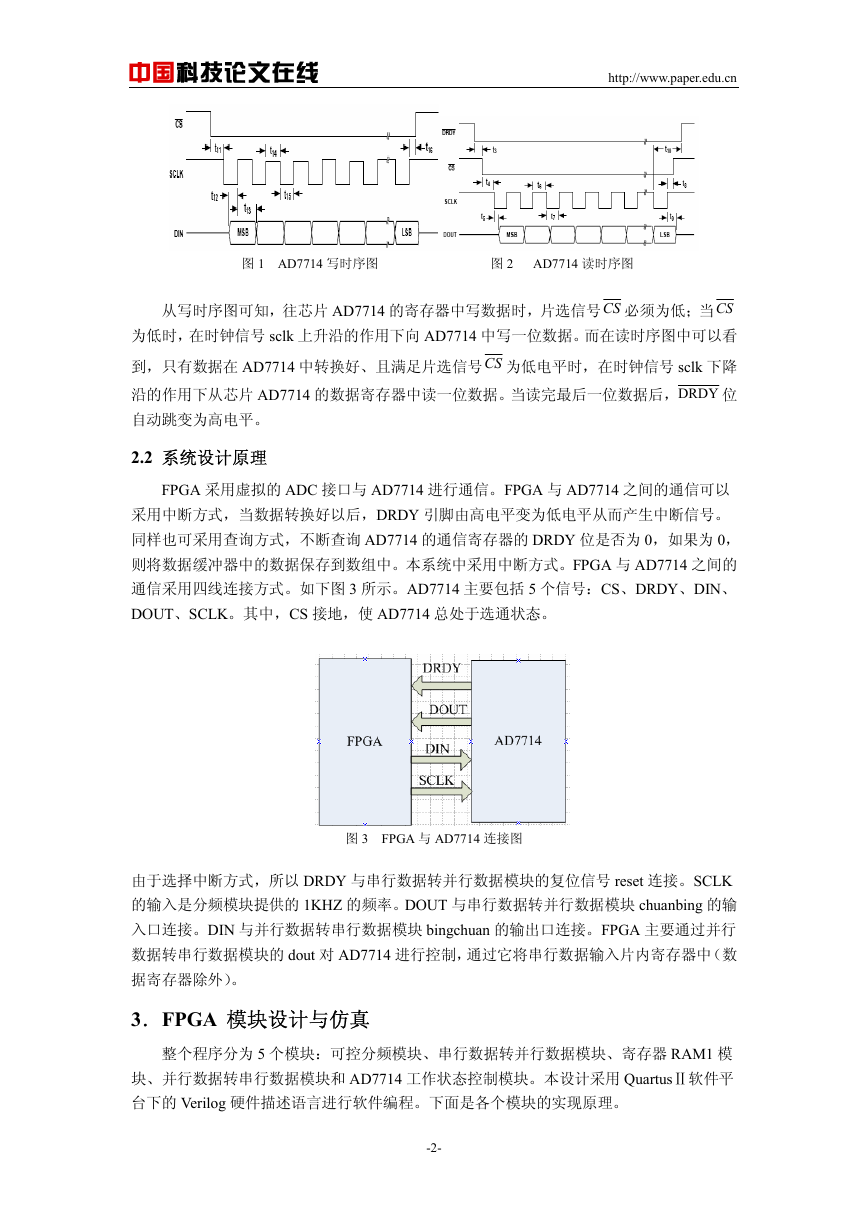

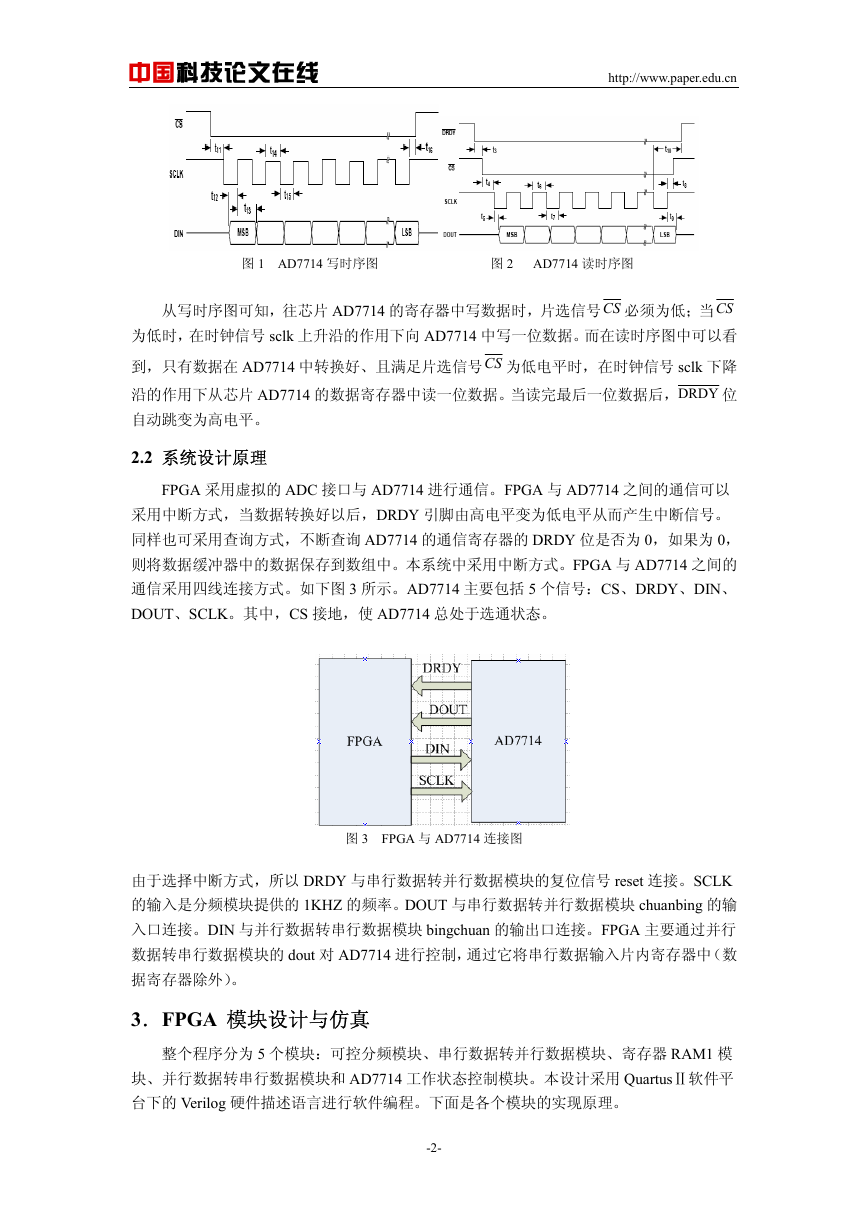

FPGA 采用虚拟的 ADC 接口与 AD7714 进行通信。FPGA 与 AD7714 之间的通信可以

采用中断方式,当数据转换好以后,DRDY 引脚由高电平变为低电平从而产生中断信号。

同样也可采用查询方式,不断查询 AD7714 的通信寄存器的 DRDY 位是否为 0,如果为 0,

则将数据缓冲器中的数据保存到数组中。本系统中采用中断方式。FPGA 与 AD7714 之间的

通信采用四线连接方式。如下图 3 所示。AD7714 主要包括 5 个信号:CS、DRDY、DIN、

DOUT、SCLK。其中,CS 接地,使 AD7714 总处于选通状态。

图 3 FPGA 与 AD7714 连接图

由于选择中断方式,所以 DRDY 与串行数据转并行数据模块的复位信号 reset 连接。SCLK

的输入是分频模块提供的 1KHZ 的频率。DOUT 与串行数据转并行数据模块 chuanbing 的输

入口连接。DIN 与并行数据转串行数据模块 bingchuan 的输出口连接。FPGA 主要通过并行

数据转串行数据模块的 dout 对 AD7714 进行控制,通过它将串行数据输入片内寄存器中(数

据寄存器除外)。

3.FPGA 模块设计与仿真

整个程序分为 5 个模块:可控分频模块、串行数据转并行数据模块、寄存器 RAM1 模

块、并行数据转串行数据模块和 AD7714 工作状态控制模块。本设计采用 QuartusⅡ软件平

台下的 Verilog 硬件描述语言进行软件编程。下面是各个模块的实现原理。

-2-

�

中国科技论文在线

http://www.paper.edu.cn

本设计时钟采用 20MHz 有源晶振,当输入到 EP1C3T144C8N 后,经过编程分频成 1KHz、

100KHZ 和 100HZ 后分别提供给串行数据转并行数据模块 chuanbing 和并行数据转串行数据

模块 bingchuan、寄存器模块 RAM1 和控制模块 control。由于 AD7714 的数据传输是串行数

据传输,所以控制模块 control 的时钟要比串行数据转并行数据模块 chuanbing 和并行数据转

串行数据模块 bingchuan 的时钟慢 10 倍以上,以此保证全部数据传输完毕。

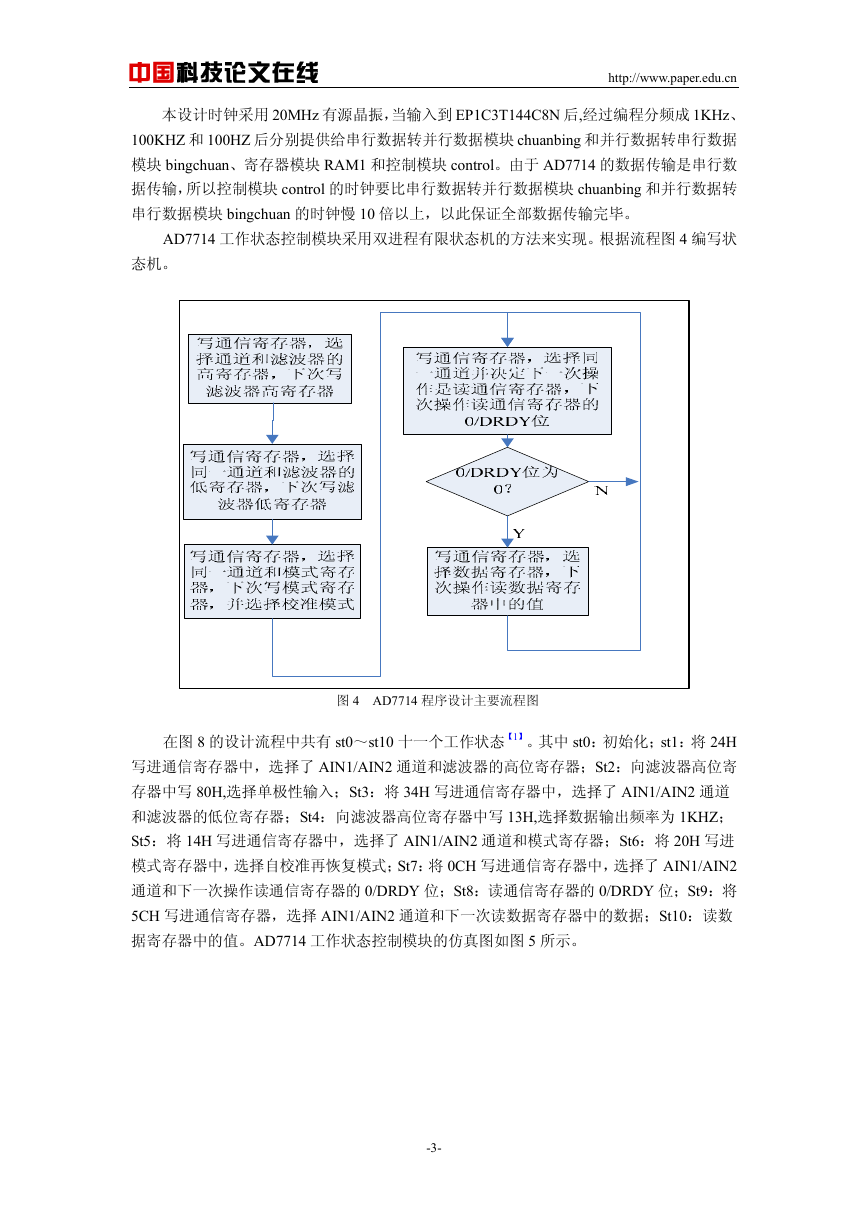

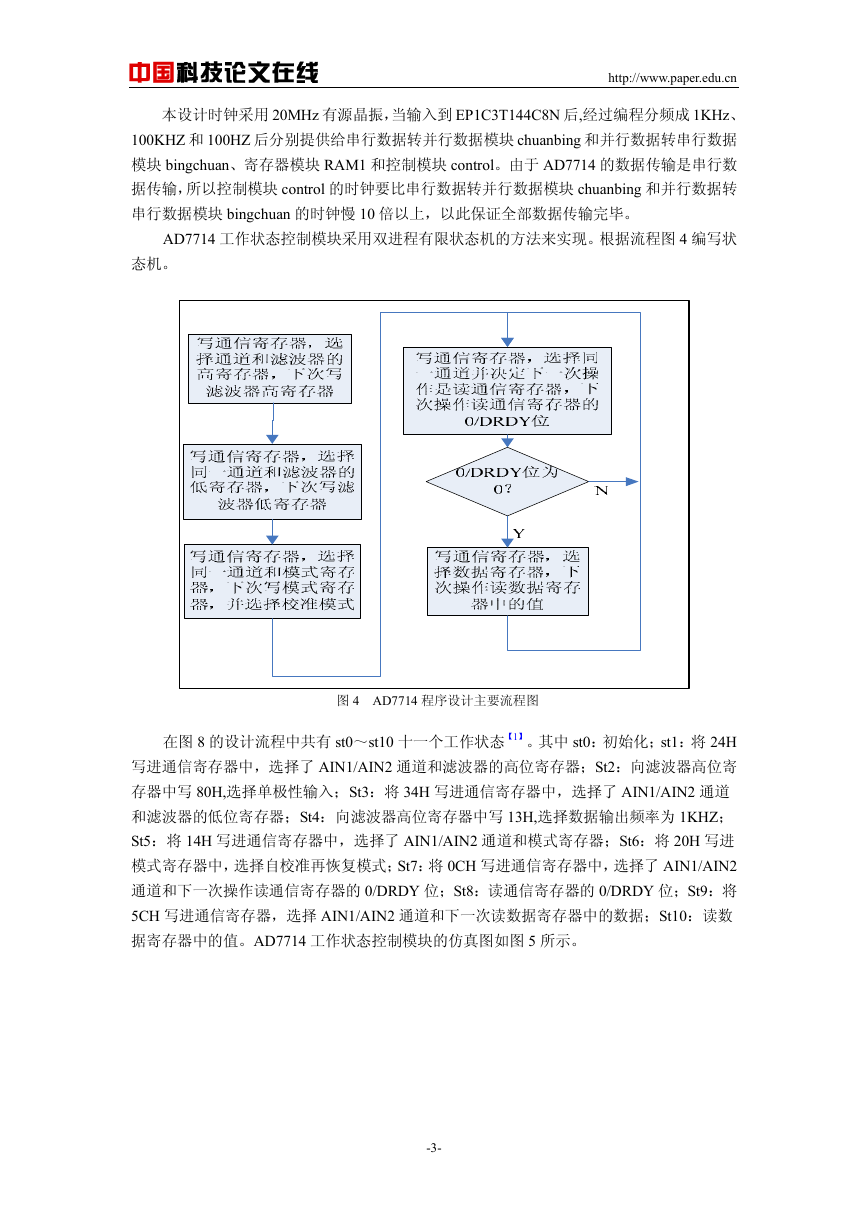

AD7714 工作状态控制模块采用双进程有限状态机的方法来实现。根据流程图 4 编写状

态机。

图 4 AD7714 程序设计主要流程图

在图 8 的设计流程中共有 st0~st10 十一个工作状态【1】。其中 st0:初始化;st1:将 24H

写进通信寄存器中,选择了 AIN1/AIN2 通道和滤波器的高位寄存器;St2:向滤波器高位寄

存器中写 80H,选择单极性输入;St3:将 34H 写进通信寄存器中,选择了 AIN1/AIN2 通道

和滤波器的低位寄存器;St4:向滤波器高位寄存器中写 13H,选择数据输出频率为 1KHZ;

St5:将 14H 写进通信寄存器中,选择了 AIN1/AIN2 通道和模式寄存器;St6:将 20H 写进

模式寄存器中,选择自校准再恢复模式;St7:将 0CH 写进通信寄存器中,选择了 AIN1/AIN2

通道和下一次操作读通信寄存器的 0/DRDY 位;St8:读通信寄存器的 0/DRDY 位;St9:将

5CH 写进通信寄存器,选择 AIN1/AIN2 通道和下一次读数据寄存器中的数据;St10:读数

据寄存器中的值。AD7714 工作状态控制模块的仿真图如图 5 所示。

-3-

�

中国科技论文在线

http://www.paper.edu.cn

图 5 控制模块的仿真图

从 AD7714 传输出来的数据是串行的数据,为了便于数据的存储和处理,有必要将串

行的数据流转化为并行的。从 AD7714 传出来的数据是 16 位的,所以开辟一个深度位 16 的

RAM1 来暂时存储数据。从串行数据到并行数据的转换如仿真图 6 所示。

图 6 串行数据转并行数据的仿真图

为了方便,在 FPGA 上定义的数据都是并行的数据,为了往 AD7714 的寄存器中写数据,

必须要将并行的数据转换为串行的数据。并行数据转串行数据的仿真图如图 7 所示。

图 7 并行数据转串行数据仿真图

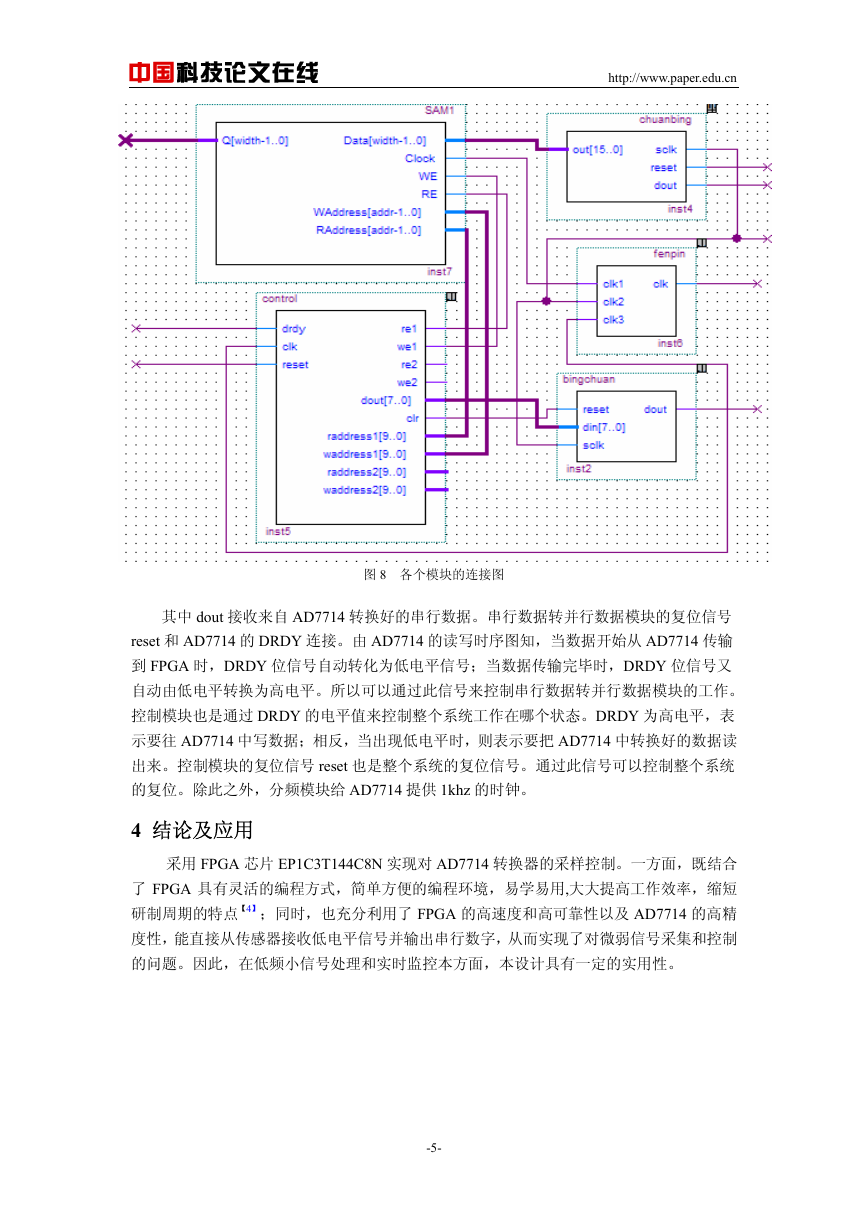

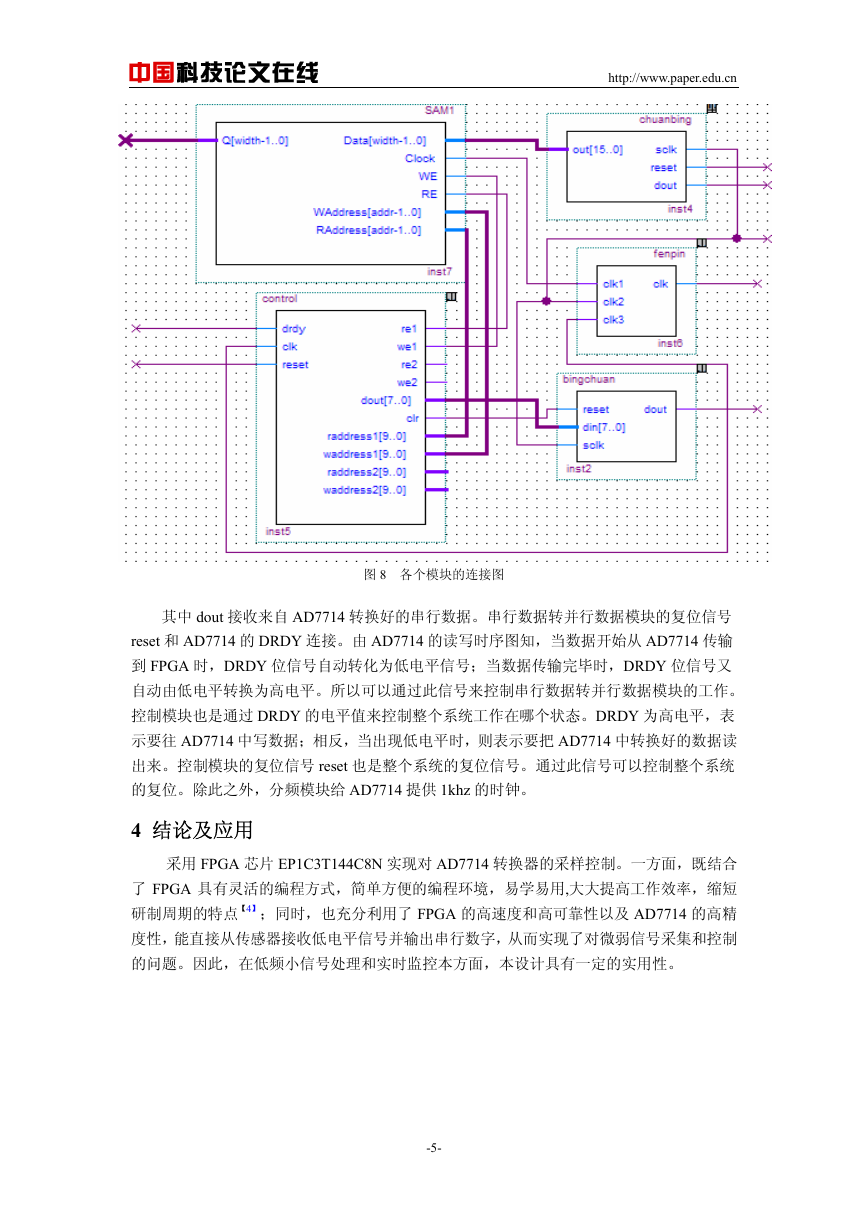

下图 8 是各个模块的连接图。

-4-

�

中国科技论文在线

http://www.paper.edu.cn

图 8 各个模块的连接图

其中 dout 接收来自 AD7714 转换好的串行数据。串行数据转并行数据模块的复位信号

reset 和 AD7714 的 DRDY 连接。由 AD7714 的读写时序图知,当数据开始从 AD7714 传输

到 FPGA 时,DRDY 位信号自动转化为低电平信号;当数据传输完毕时,DRDY 位信号又

自动由低电平转换为高电平。所以可以通过此信号来控制串行数据转并行数据模块的工作。

控制模块也是通过 DRDY 的电平值来控制整个系统工作在哪个状态。DRDY 为高电平,表

示要往 AD7714 中写数据;相反,当出现低电平时,则表示要把 AD7714 中转换好的数据读

出来。控制模块的复位信号 reset 也是整个系统的复位信号。通过此信号可以控制整个系统

的复位。除此之外,分频模块给 AD7714 提供 1khz 的时钟。

4 结论及应用

采用 FPGA 芯片 EP1C3T144C8N 实现对 AD7714 转换器的采样控制。一方面,既结合

了 FPGA 具有灵活的编程方式,简单方便的编程环境,易学易用,大大提高工作效率,缩短

研制周期的特点【4】;同时,也充分利用了 FPGA 的高速度和高可靠性以及 AD7714 的高精

度性,能直接从传感器接收低电平信号并输出串行数字,从而实现了对微弱信号采集和控制

的问题。因此,在低频小信号处理和实时监控本方面,本设计具有一定的实用性。

-5-

�

中国科技论文在线

http://www.paper.edu.cn

参考文献

[1]户国强, 房建东, 郭春兰. 基于 FPGA 的 A/D 转换采样控制模块的设计. 2008

[2]夏宇闻. Verilog 数字系统设计教程.

[3]付晓丹. 海水中叶绿素 a 含量监测系统的研究. 2007.7

[4]韦存刚, 金星. 基于 FPGA 的多路数据采集和控制模块设计. 2008.

A Design of the A/D Convertion Sampling Control Module

Based on FPGA

Huang Ronglan1, Wan Dehuan2

1. School of Electronic Engineering ,Guilin University of Electronic Technology, Guilin,

2. Guilin Air Force Academy, Guilin, Guangxi (541003)

2. Guangxi (541001)

Abstract

Ⅱ

platform

By using FPGA device EP1C3T144C8N as the controller of A/D converter AD7714 in this paper .The

whole design is under the Quartus

,described in the Verilog,to realize the correct sequence

controlling process of AD7714 converter and storage the sampling data to processe..It can be widely

used in feebleness data sampling and the real-time supervisory control aspect. The practice shows that

the module has the advantages of stable performance,high reliability and convenient usage.

Keywords: FPGA,Verilog,A/D convertion,sampling control

-6-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc