中国科技论文在线

http://www.paper.edu.cn

基于 Verilog HDL 的有限状态机研究

张殿文,张晓冰,颜颐欣**

(哈尔滨理工大学测控技术与通信工程学院,哈尔滨 150080)

5 摘要:Verilog HDL(硬件描述语言)既可以适于可综合的电路设计,也可胜任电路与系统

的仿真,能在多个层次上对所设计的系统加以描述。有限状态机是数字系统中的重要组成部

分,本文首先研究运用 Verilog HDL 设计有限状态机时可以采用的不同的状态编码方式和风

格。其次,介绍了有限状态机综合时要注意的一般原则。最后,以自动转换量程频率计控制

器状态机 为例,分别用 Synplify Pro 和 QuartusII 对设计进行了综合和仿真验证。

关键词:Verilog HDL;有限状态机;状态编码;综合

中图分类号:TN98

10

Finite State Machine Verilog HDL-based research

15

20

25

ZHANG Dianwen, ZHANG Xiaobing, YAN Yixin

(School of Measurement and Communication Engineering,Harbin University of Science and

Technology,Harbin 150080)

Abstract: Verilog HDL (hardware description language) not only can be suitable for integrated

circuit design but also can serve in the circuit and system simulation, it also can descibed at

multiple levels of the designed system . Finite state machine(FSM) is an important part of a digital

system. This paper first study of the use of Verilog HDL design finite state machine can be used in

a different state encoding and style. Second, the introduction of the synthesis finite state machine

to the attention of the general principles. Finally, automatic conversion range frequency counter

controller state machine as a FSM design example. The synthesis and simulation of the design are

implemented separately through Synplify Pro and QuartusII .

Key words: Verilog HDL; FSM ;State Encoding;Synthesis

0 引言

有限状态机(Finite State Machine,FSM)是时序电路设计中经常采用的一种方式,尤其

30

适于设计数字系统的控制模块,在一些需要控制高速器件的场合,用状态机进行设计是解决

问题的一种很好的实现方案,具有速度快,结构简单,可靠性高等优点。状态机可以认为是

组合逻辑和寄存器逻辑的特殊组合,它一般包括两个部分:组合逻辑部分和寄存器逻辑部分。

寄存器用于存储状态,组合电路用于状态译码和产生输出信号。[1]状态机的下一个状态及输

出,不仅与输入信号有关,而且还与寄存器当前所处的状态有关。状态机可以分为两类:米

35

里型(Mealy)和摩尔型(Moore)。Moore 型是指输出只与当前状态有关,而 Mealy 型的

输出不只与当前状态有关,还与输入信号有关。用 Verilog HDL 的 case、if-else 等语句能很

好地描述基于状态机的设计。有限状态机的综合就是从采用由 Verilog HDL 描述的寄存器传

输级电路模型构造出门级网表的过程。

1 状态编码

40

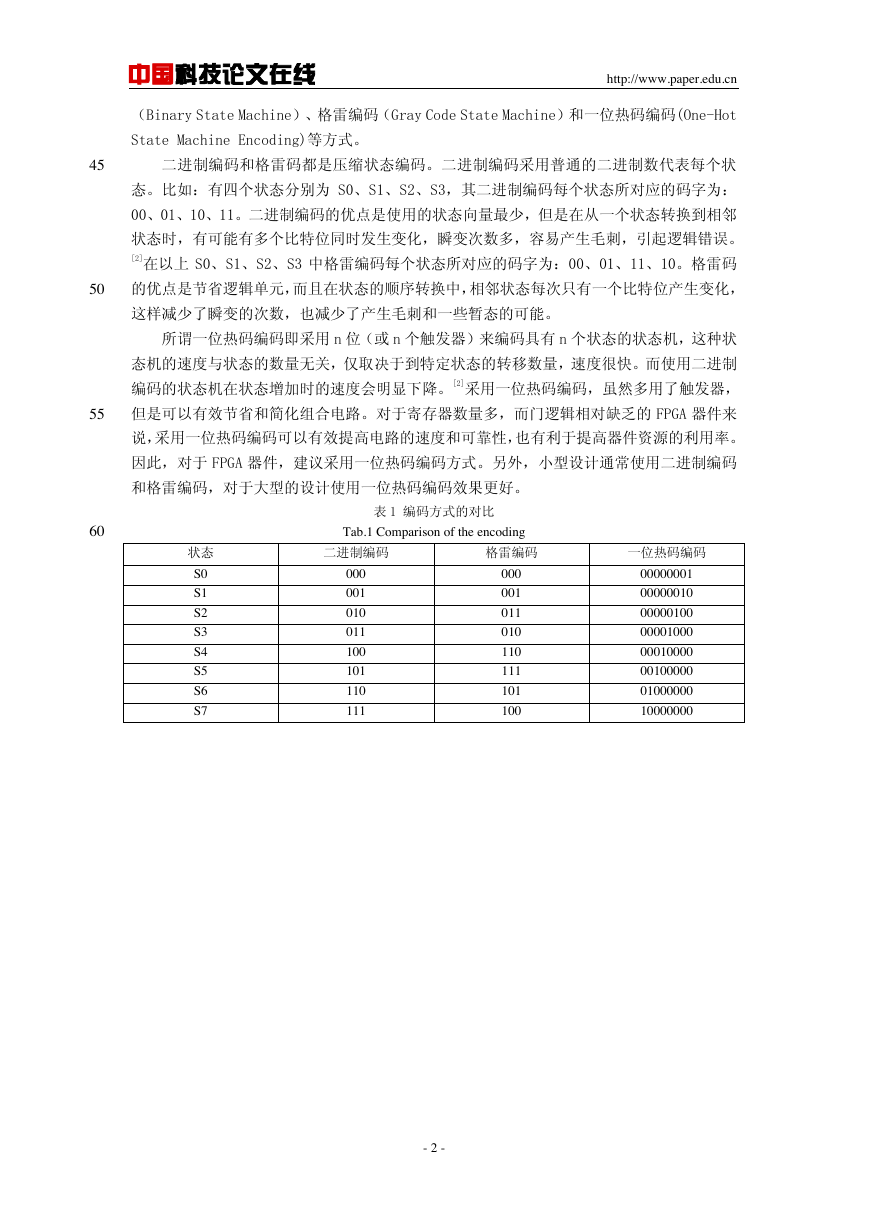

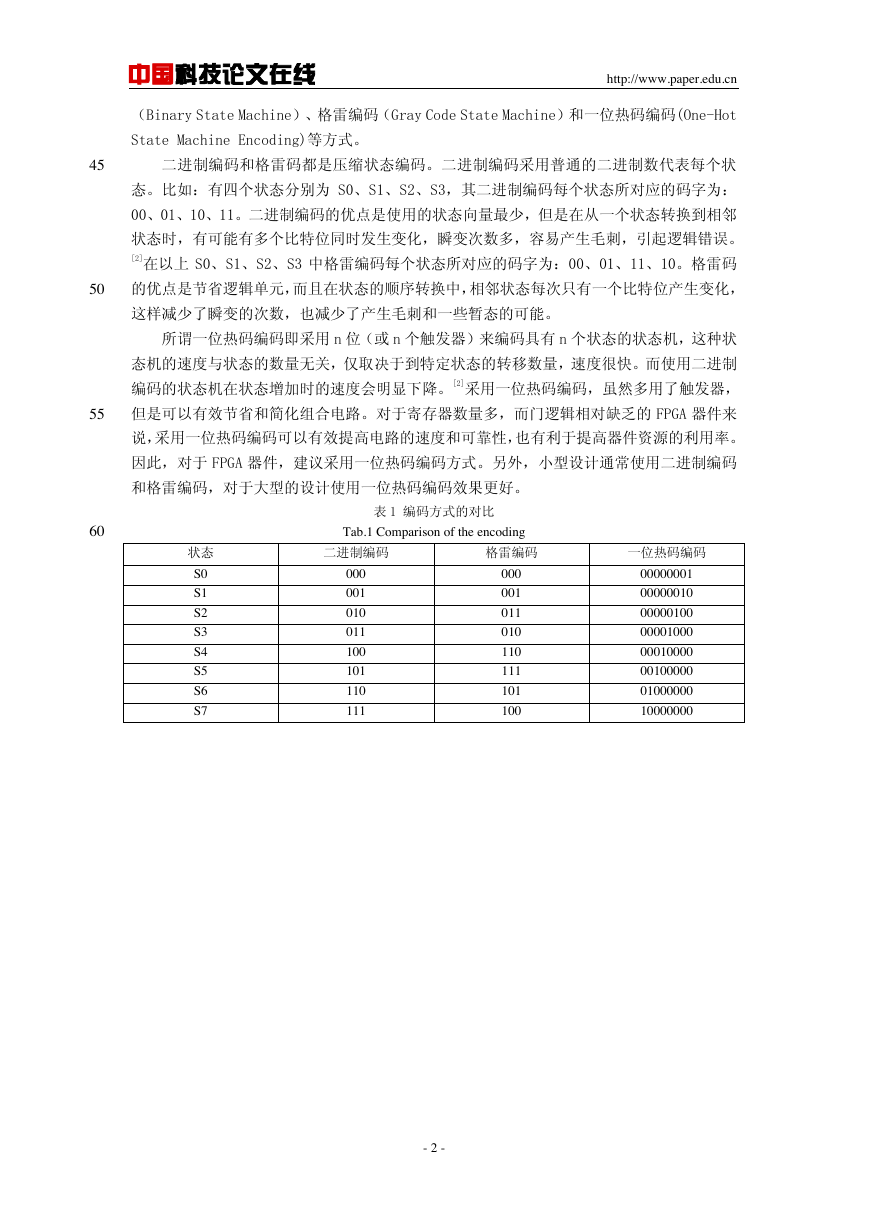

状态编码是设计状态机十分重要的部分,状态编码又称状态分配,不同的状态机编码类

型和描述风格对状态机的影响是不同的,状态编码方案选取得当,设计的电路就可以简单;

反之,电路就会占用过多的逻辑资源造成电路复杂。如表 1 所示状态编码主要有二进制编码

作者简介:张殿文(1986-),男,硕士,测控计量技术及仪器

通信联系人:张晓冰(1962-),女,教授,电气测量技术及仪器,工业自动化仪表. E-mail: Zhxiaobing@163.com

- 1 -

�

中国科技论文在线

http://www.paper.edu.cn

(Binary State Machine)、格雷编码(Gray Code State Machine)和一位热码编码(One-Hot

State Machine Encoding)等方式。

45

二进制编码和格雷码都是压缩状态编码。二进制编码采用普通的二进制数代表每个状

态。比如:有四个状态分别为 S0、S1、S2、S3,其二进制编码每个状态所对应的码字为:

00、01、10、11。二进制编码的优点是使用的状态向量最少,但是在从一个状态转换到相邻

状态时,有可能有多个比特位同时发生变化,瞬变次数多,容易产生毛刺,引起逻辑错误。

[2]在以上 S0、S1、S2、S3 中格雷编码每个状态所对应的码字为:00、01、11、10。格雷码

50

的优点是节省逻辑单元,而且在状态的顺序转换中,相邻状态每次只有一个比特位产生变化,

这样减少了瞬变的次数,也减少了产生毛刺和一些暂态的可能。

所谓一位热码编码即采用 n 位(或 n 个触发器)来编码具有 n 个状态的状态机,这种状

态机的速度与状态的数量无关,仅取决于到特定状态的转移数量,速度很快。而使用二进制

编码的状态机在状态增加时的速度会明显下降。[2]采用一位热码编码,虽然多用了触发器,

55

但是可以有效节省和简化组合电路。对于寄存器数量多,而门逻辑相对缺乏的 FPGA 器件来

说,采用一位热码编码可以有效提高电路的速度和可靠性,也有利于提高器件资源的利用率。

因此,对于 FPGA 器件,建议采用一位热码编码方式。另外,小型设计通常使用二进制编码

和格雷编码,对于大型的设计使用一位热码编码效果更好。

60

表 1 编码方式的对比

Tab.1 Comparison of the encoding

状态

二进制编码

格雷编码

一位热码编码

S0

S1

S2

S3

S4

S5

S6

S7

000

001

010

011

100

101

110

111

000

001

011

010

110

111

101

100

00000001

00000010

00000100

00001000

00010000

00100000

01000000

10000000

- 2 -

�

中国科技论文在线

http://www.paper.edu.cn

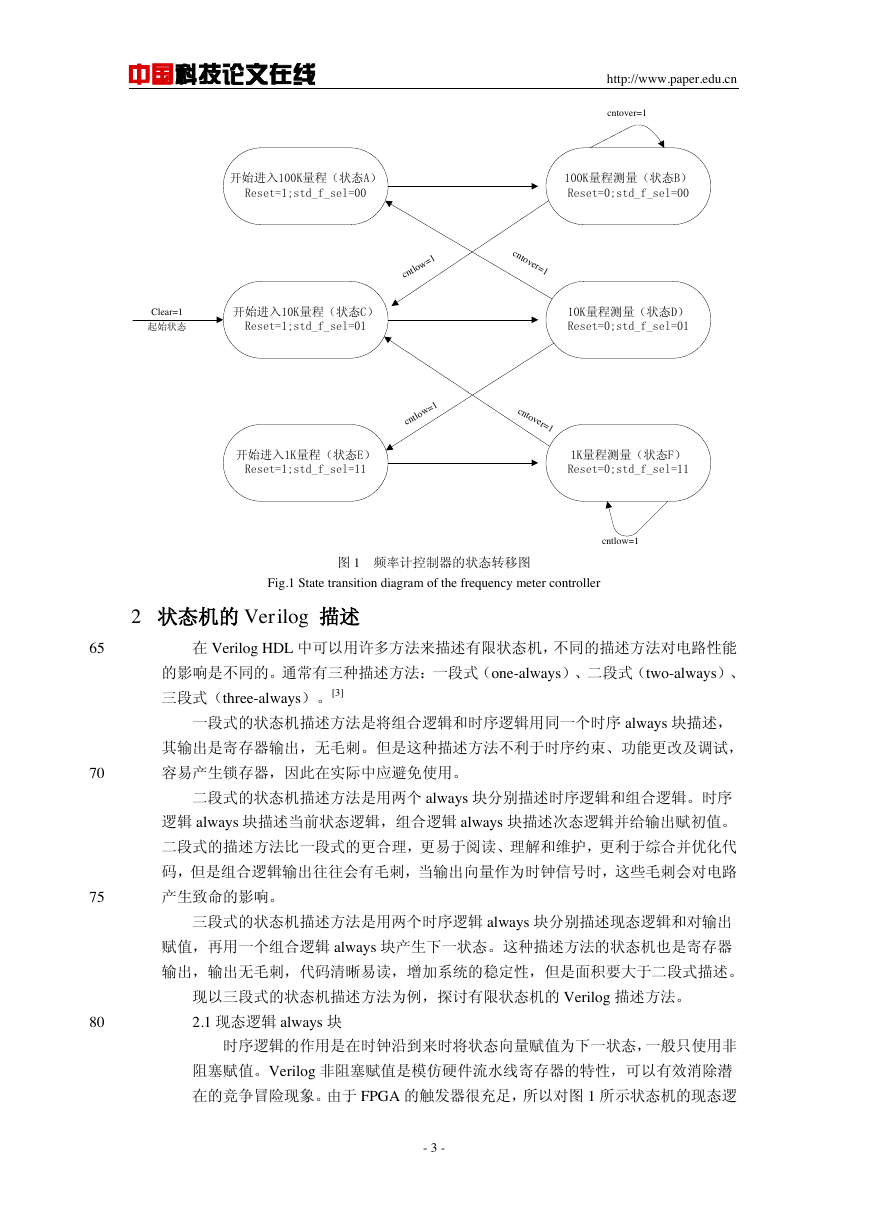

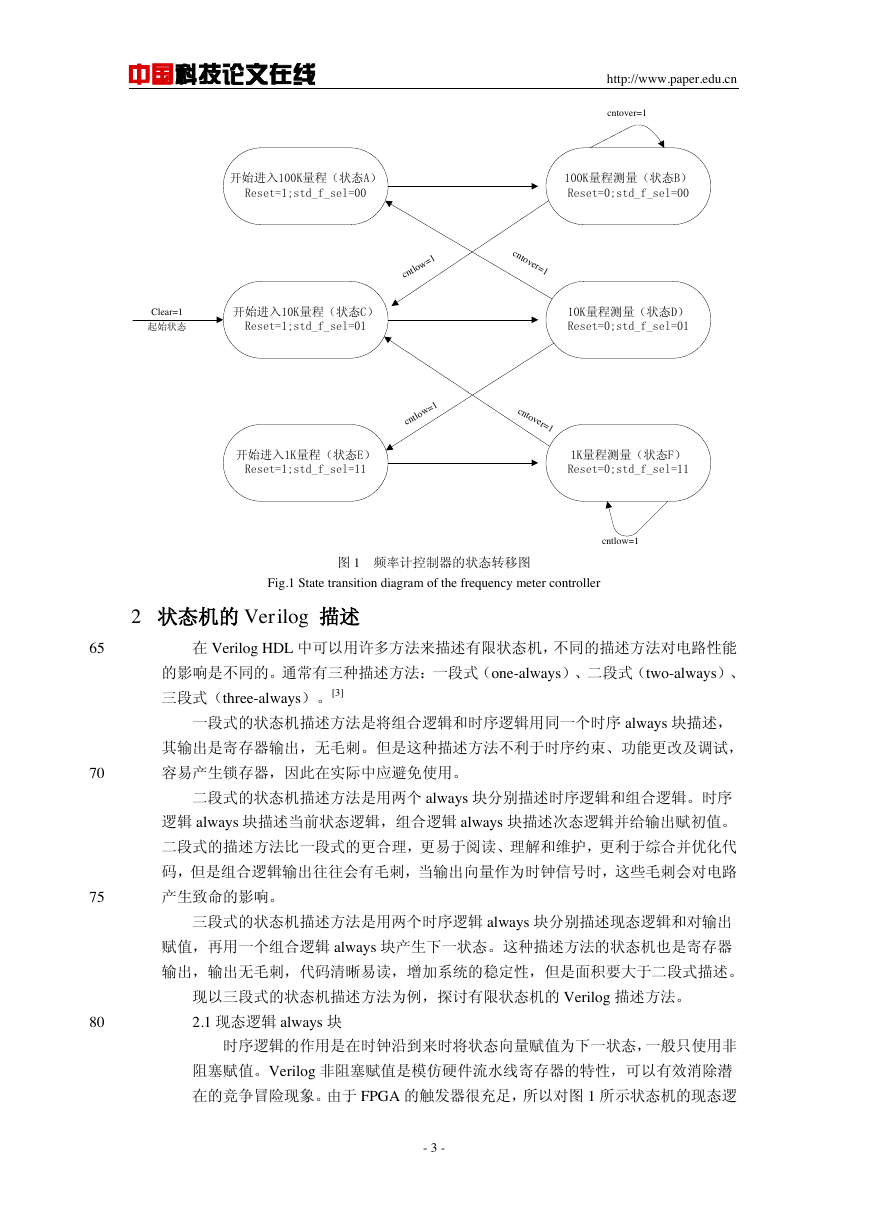

图 1 频率计控制器的状态转移图

Fig.1 State transition diagram of the frequency meter controller

2 状态机的 Verilog 描述

65

在 Verilog HDL 中可以用许多方法来描述有限状态机,不同的描述方法对电路性能

的影响是不同的。通常有三种描述方法:一段式(one-always)、二段式(two-always)、

三段式(three-always)。[3]

一段式的状态机描述方法是将组合逻辑和时序逻辑用同一个时序 always 块描述,

其输出是寄存器输出,无毛刺。但是这种描述方法不利于时序约束、功能更改及调试,

70

容易产生锁存器,因此在实际中应避免使用。

二段式的状态机描述方法是用两个 always 块分别描述时序逻辑和组合逻辑。时序

逻辑 always 块描述当前状态逻辑,组合逻辑 always 块描述次态逻辑并给输出赋初值。

二段式的描述方法比一段式的更合理,更易于阅读、理解和维护,更利于综合并优化代

码,但是组合逻辑输出往往会有毛刺,当输出向量作为时钟信号时,这些毛刺会对电路

75

产生致命的影响。

三段式的状态机描述方法是用两个时序逻辑 always 块分别描述现态逻辑和对输出

赋值,再用一个组合逻辑 always 块产生下一状态。这种描述方法的状态机也是寄存器

输出,输出无毛刺,代码清晰易读,增加系统的稳定性,但是面积要大于二段式描述。

现以三段式的状态机描述方法为例,探讨有限状态机的 Verilog 描述方法。

80

2.1 现态逻辑 always 块

时序逻辑的作用是在时钟沿到来时将状态向量赋值为下一状态,一般只使用非

阻塞赋值。Verilog 非阻塞赋值是模仿硬件流水线寄存器的特性,可以有效消除潜

在的竞争冒险现象。由于 FPGA 的触发器很充足,所以对图 1 所示状态机的现态逻

- 3 -

开始进入100K量程(状态A)Reset=1;std_f_sel=00100K量程测量(状态B)Reset=0;std_f_sel=00开始进入10K量程(状态C)Reset=1;std_f_sel=0110K量程测量(状态D)Reset=0;std_f_sel=01开始进入1K量程(状态E)Reset=1;std_f_sel=111K量程测量(状态F)Reset=0;std_f_sel=11Clear=1起始状态cntlow=1cntlow=1cntover=1cntover=1cntover=1cntlow=1�

中国科技论文在线

http://www.paper.edu.cn

辑模块采用一位热码编码进行描述:

85

Parameter

start_f100k=6'b000001, //状态 A

f100k_cnt=6'b000010,

start_f10k=6'b000100,

f10k_cnt=6'b001000,

start_f1k=6'b010000,

f1k_cnt=6'b100000;

//状态 B

//状态 C

//状态 D

//状态 E

//状态 F

always @(posedge clk or posedge clear)

begin

if(clear)

present<=start_f10k;//start_f10k 为起始状态

else

present<=next;

end

90

95

2.2 输出赋值 always 块

输出赋值 always 块属于时序逻辑模块,为便于综合要采用非阻塞赋值,以下

100

是对图 1 状态机的输出逻辑模块采用一位热码编码的描述:

always @(present or

cntover or

cntlow)

105

110

115

120

125

begin

case(present)

start_f100k: next<=f100k_cnt;

f100k_cnt:

begin

if(cntlow)

next<=start_f10k;

else

next<=f100k_cnt;

end

start_f10k:

next<=f10k_cnt;

f10k_cnt:

begin

if(cntlow)

next<=start_f1k;

else

if(cntover)

next<=start_f100k;

else

next<=f10k_cnt;

end

start_f1k: next<=f1k_cnt;

f1k_cnt:

begin

if(cntover)

next<=start_f10k;

else

- 4 -

�

中国科技论文在线

http://www.paper.edu.cn

130

next<=f1k_cnt;

end

default: next<=start_f10k;

endcase

end

2.3 组合逻辑 always 块

135

组合逻辑模块使用 case 语句或 if/else 语句指定下一状态和输出。这个 always

块是由包含状态寄存器现态值和所有输入的敏感信号触发的。以下是对图 1 状态机

的组合逻辑 always 块采用一位热码编码的描述:

always @

(present)

140

145

begin

case(present)

start_f100k: begin

reset=1;

std_f_sel=2'b00;

end

f100k_cnt:

start_f10k:

begin

begin

reset=0;

reset=1;

std_f_sel=2'b00;

std_f_sel=2'b01;

end

end

f10k_cnt:

start_f1k:

f1k_cnt:

default:

endcase

begin

begin

begin

begin

reset=0;

reset=1;

reset=0;

reset=1;

std_f_sel=2'b01;

std_f_sel=2'b11;

std_f_sel=2'b11;

std_f_sel=2'b01;

end

end

end

end

end

150

3 状态机综合的一般原则

在硬件描述语言中,虽然有许多基于仿真的语句符合语法规则,但是不能映射到硬

件逻辑电路单元,如果要实现硬件设计,必须写出可以综合的程序。通常,综合的一般

原则为:

1)综合之前一定要进行仿真,仿真会暴露逻辑错误。如果不做仿真,没有发

155

现的逻辑错误会进入综合器,是综合的结果产生同样的逻辑错误。[4]

2)每一次布线之后都要进行仿真,在器件编程或流片之前一定要进行最后的

仿真。

160

3)用 Verilog HDL 描述的异步状态机是不能综合的,应该避免用综合器来仿

真,必须设计异步状态机时,建议用电路图输入的方法。[5]

4)如果要为电平敏感的锁存器建模,使用连续赋值语句是最简单的方法。

5)状态机应该有一个异步和同步复位端,以便在通电时将硬件电路复位到有

效状态。建议使用异步复位以使硬件简化。[5]

时序逻辑电路建模时,用非阻塞赋值。用 always 块写组合逻辑时,采用阻塞赋值。不要在

多个 always 块中为同一个变量赋值。

165

4 设计举例

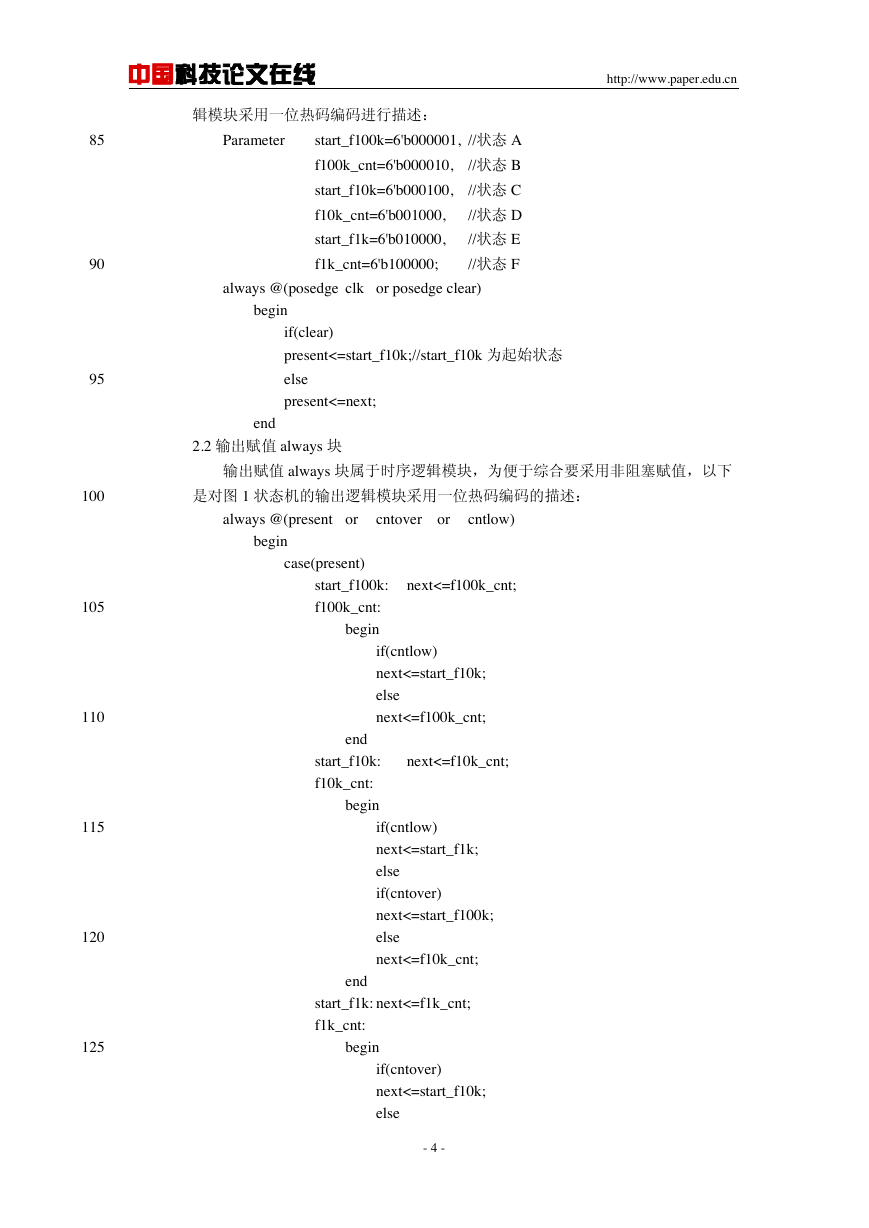

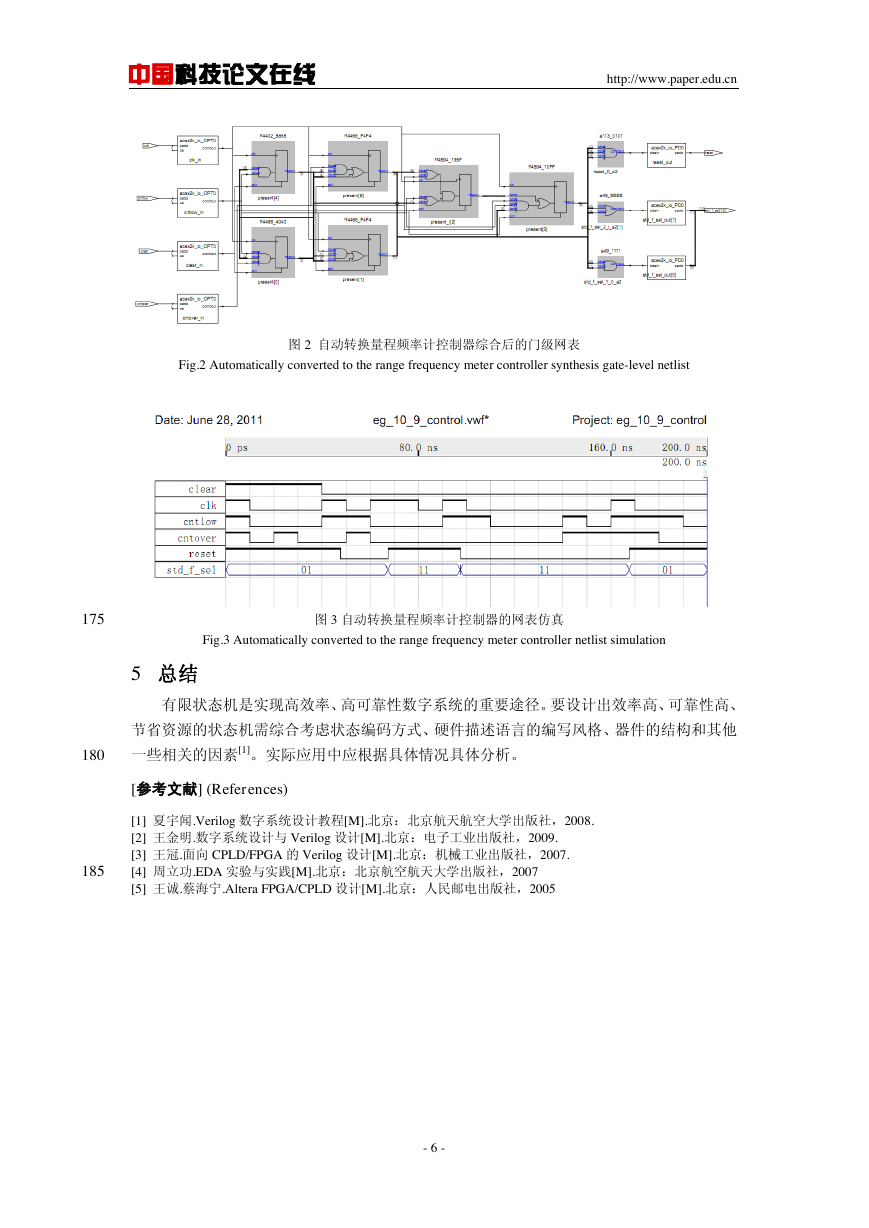

设计一个自动转换量程频率计控制器状态机,设 clear=1 为起始状态,当下一个时

钟周期到来时判断频率的频率范围,cntover=1 代表超量程,cntlow=1 代表欠量程。其

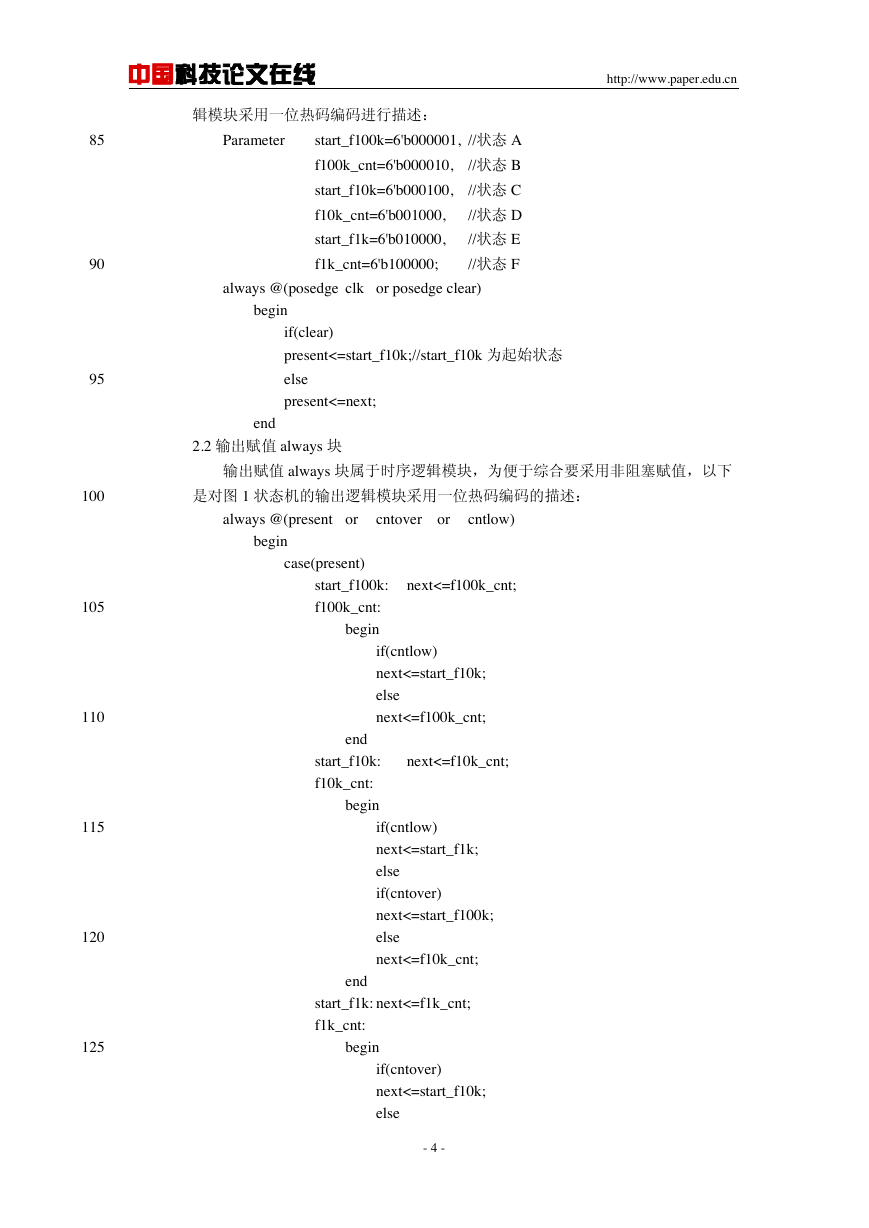

状态转移图见图 1.采用一位热码编码和三段式描述方法设计的状态机综合后的门级网

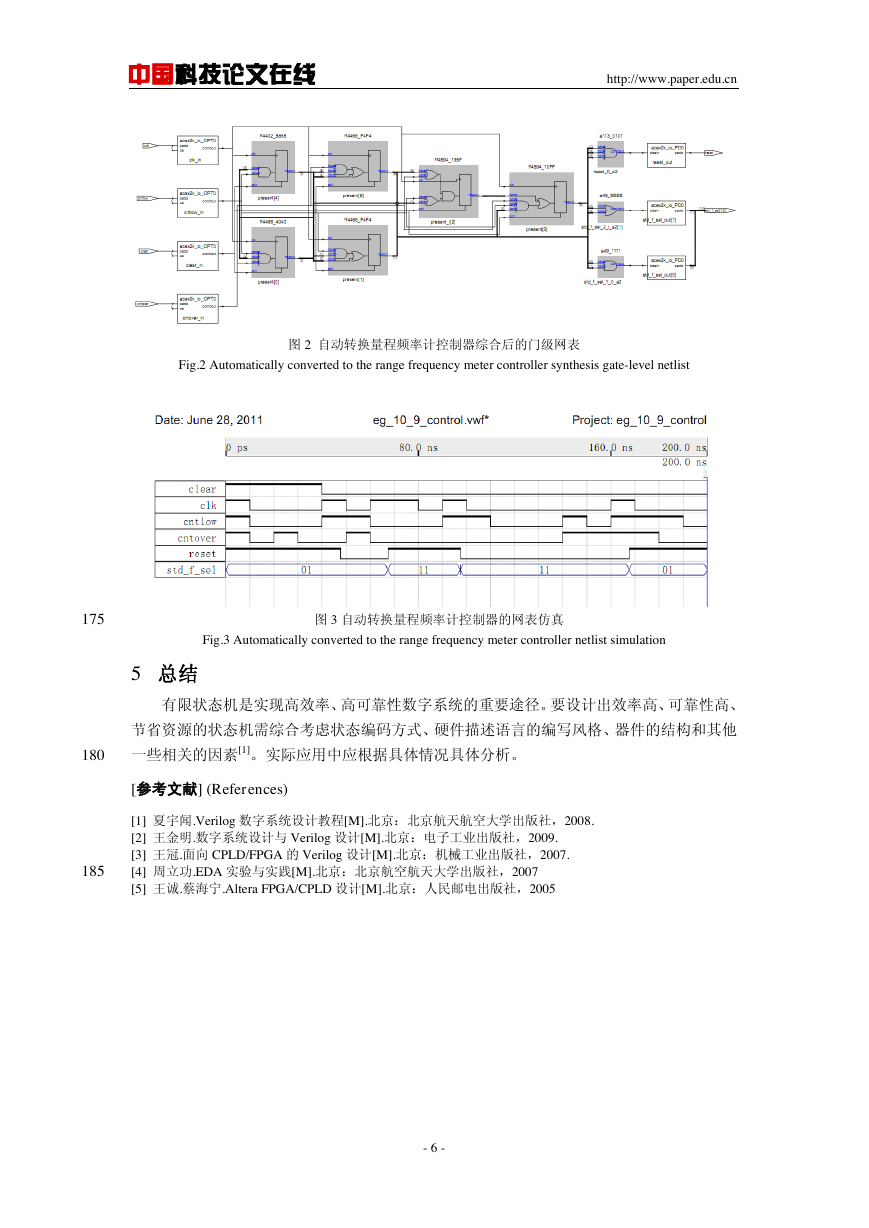

表见图 2(综合工具为 Synplify Pro9.6)。综合后的门级网表的仿真波形(Quartus II 7.0)

170

见图 3。

- 5 -

�

中国科技论文在线

http://www.paper.edu.cn

图 2 自动转换量程频率计控制器综合后的门级网表

Fig.2 Automatically converted to the range frequency meter controller synthesis gate-level netlist

175

图 3 自动转换量程频率计控制器的网表仿真

Fig.3 Automatically converted to the range frequency meter controller netlist simulation

5 总结

有限状态机是实现高效率、高可靠性数字系统的重要途径。要设计出效率高、可靠性高、

节省资源的状态机需综合考虑状态编码方式、硬件描述语言的编写风格、器件的结构和其他

一些相关的因素[1]。实际应用中应根据具体情况具体分析。

180

[参考文献] (References)

[1] 夏宇闻.Verilog 数字系统设计教程[M].北京:北京航天航空大学出版社,2008.

[2] 王金明.数字系统设计与 Verilog 设计[M].北京:电子工业出版社,2009.

[3] 王冠.面向 CPLD/FPGA 的 Verilog 设计[M].北京:机械工业出版社,2007.

[4] 周立功.EDA 实验与实践[M].北京:北京航空航天大学出版社,2007

[5] 王诚.蔡海宁.Altera FPGA/CPLD 设计[M].北京:人民邮电出版社,2005

185

- 6 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc