8.3 异步通信接口

IBM—PC 机系统可配有同步和异步通信接口,一般系统只配置了异步通信接口,系统

提供有两个通信端口:COM1 和 COM2。PC 机异步通信适配器提供 RS-232C 标准的 EIA 电

压接口和 20mA 电流环接口两种操作方式,适用于微机与微机、微机与 MODEM 或外设之

间进行异步通信,应用非常广泛。异步通信适配器硬件核心部分是可编程 INS 8250 芯片,

是本节讨论的重点。最后,用 PC 机相互之间通信的例子来说明适配器的编程应用。

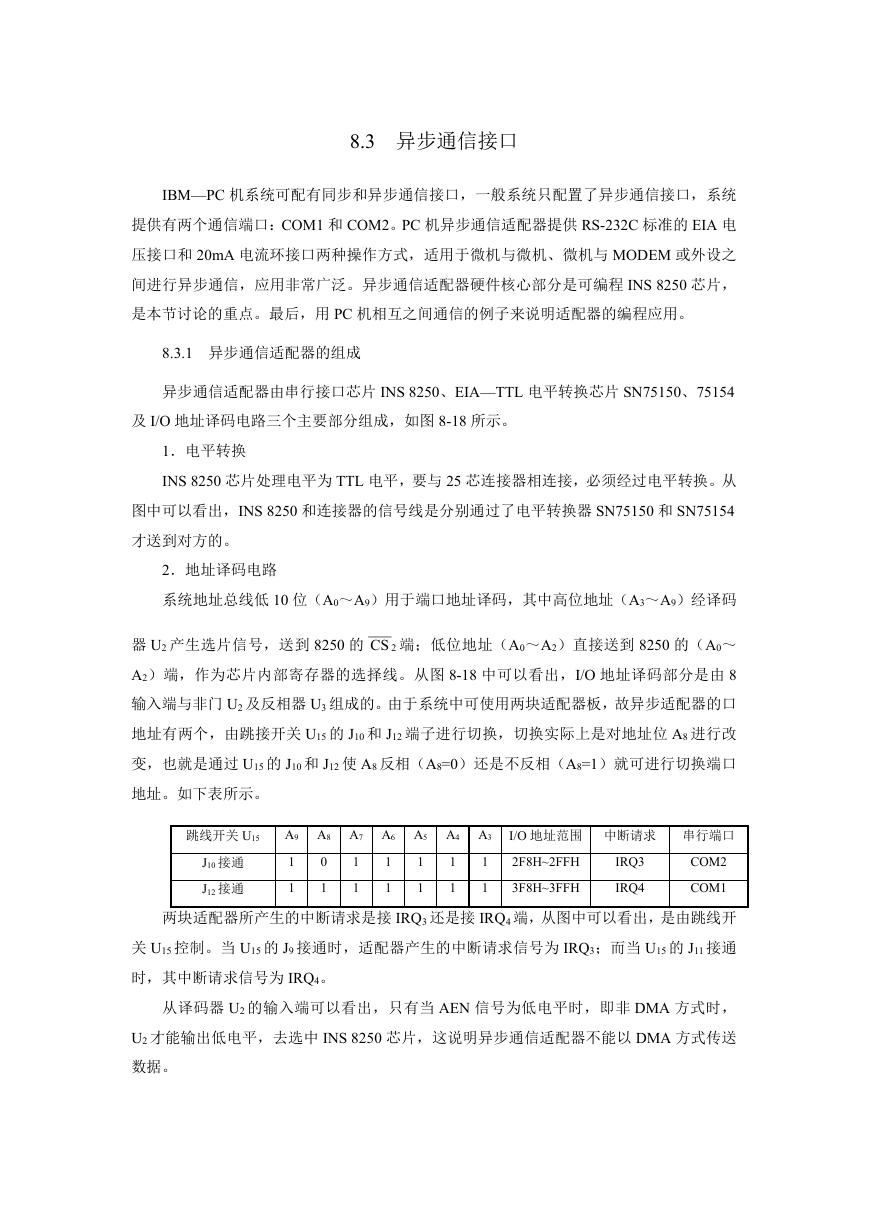

8.3.1 异步通信适配器的组成

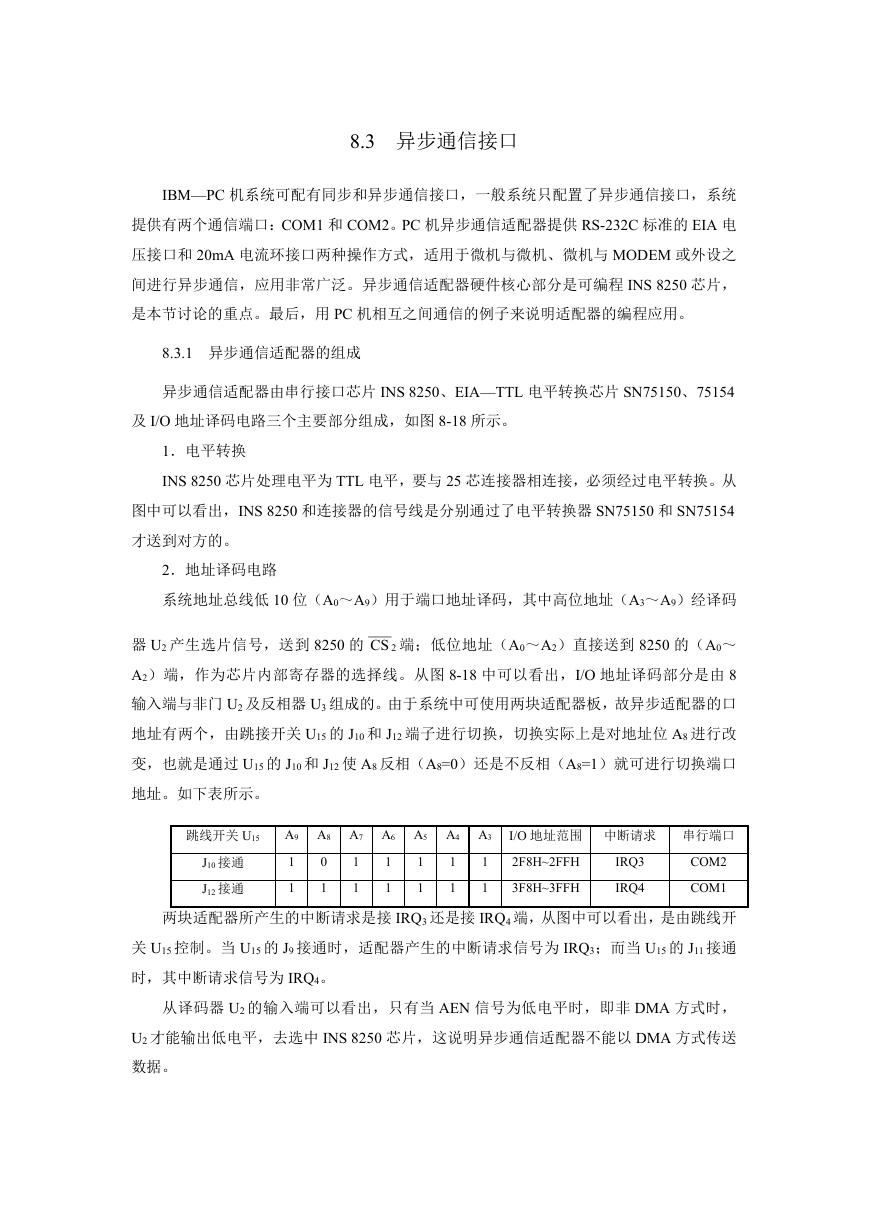

异步通信适配器由串行接口芯片 INS 8250、EIA—TTL 电平转换芯片 SN75150、75154

及 I/O 地址译码电路三个主要部分组成,如图 8-18 所示。

1.电平转换

INS 8250 芯片处理电平为 TTL 电平,要与 25 芯连接器相连接,必须经过电平转换。从

图中可以看出,INS 8250 和连接器的信号线是分别通过了电平转换器 SN75150 和 SN75154

才送到对方的。

2.地址译码电路

系统地址总线低 10 位(A0~A9)用于端口地址译码,其中高位地址(A3~A9)经译码

___

CS 2 端;低位地址(A0~A2)直接送到 8250 的(A0~

器 U2 产生选片信号,送到 8250 的

A2)端,作为芯片内部寄存器的选择线。从图 8-18 中可以看出,I/O 地址译码部分是由 8

输入端与非门 U2 及反相器 U3 组成的。由于系统中可使用两块适配器板,故异步适配器的口

地址有两个,由跳接开关 U15 的 J10 和 J12 端子进行切换,切换实际上是对地址位 A8 进行改

变,也就是通过 U15 的 J10 和 J12 使 A8 反相(A8=0)还是不反相(A8=1)就可进行切换端口

地址。如下表所示。

跳线开关 U15

A9 A8 A7 A6 A5 A4 A3

J10 接通

J12 接通

1

1

0

1

1

1

1

1

1

1

1

1

1

1

I/O 地址范围 中断请求

2F8H~2FFH

IRQ3

3F8H~3FFH

IRQ4

串行端口

COM2

COM1

两块适配器所产生的中断请求是接 IRQ3 还是接 IRQ4 端,从图中可以看出,是由跳线开

关 U15 控制。当 U15 的 J9 接通时,适配器产生的中断请求信号为 IRQ3;而当 U15 的 J11 接通

时,其中断请求信号为 IRQ4。

从译码器 U2 的输入端可以看出,只有当 AEN 信号为低电平时,即非 DMA 方式时,

U2 才能输出低电平,去选中 INS 8250 芯片,这说明异步通信适配器不能以 DMA 方式传送

数据。

�

8.3.2

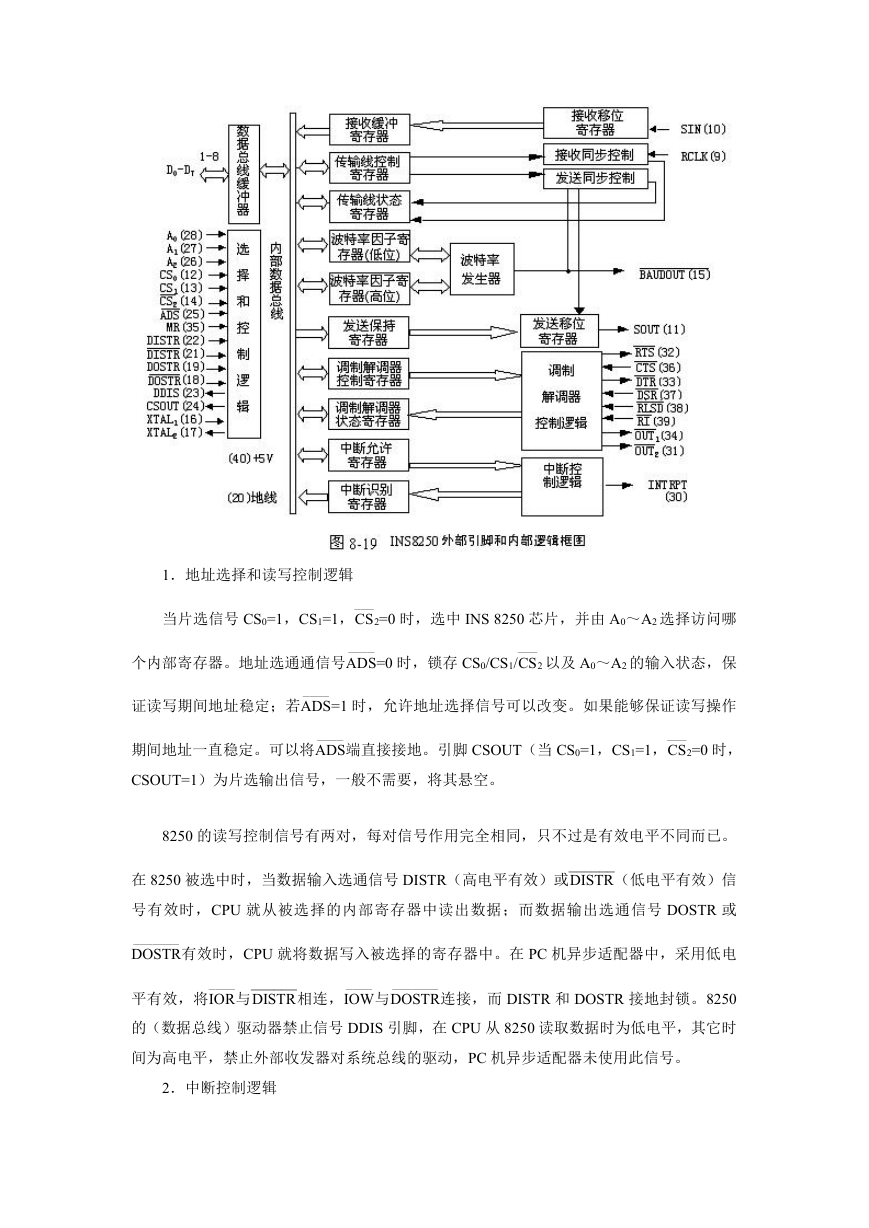

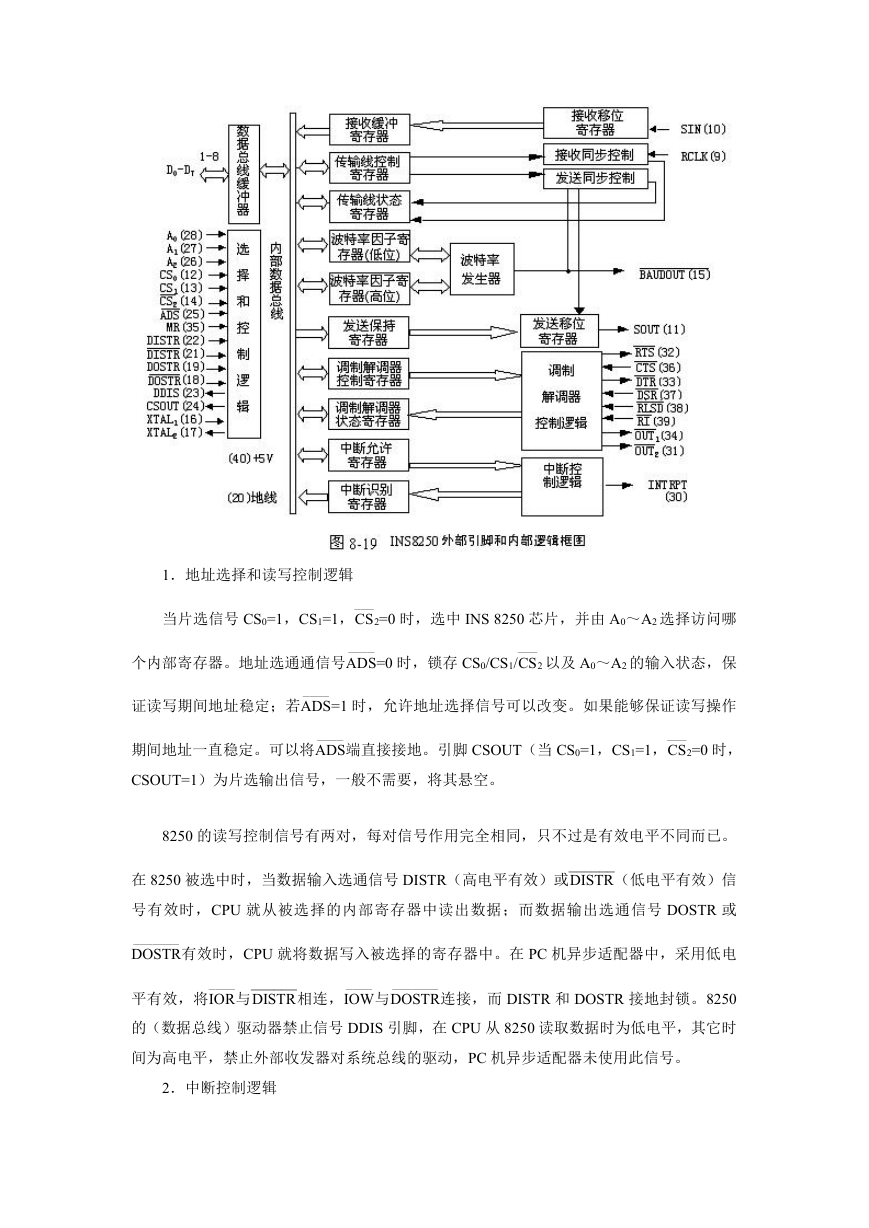

INS 8250 的结构和外部特性

INS 8250 是通用异步收发器 UART,适合用作异步通信接口电路。INS 8250 的外部引

脚及内部结构如图 8-19 所示。

INS 8250 的引脚信号线基本上可分为两大类:与 CPU 系统总线相连的信号和与通信设

备 MODEM 连接的信号。除 8 根并行数据线 D0~D7 外,还有如下信号:

�

1.地址选择和读写控制逻辑

当片选信号 CS0=1,CS1=1,

___

CS2=0 时,选中 INS 8250 芯片,并由 A0~A2 选择访问哪

个内部寄存器。地址选通通信号

____

ADS=0 时,锁存 CS0/CS1/

___

CS2 以及 A0~A2 的输入状态,保

证读写期间地址稳定;若

____

ADS=1 时,允许地址选择信号可以改变。如果能够保证读写操作

期间地址一直稳定。可以将

____

ADS端直接接地。引脚 CSOUT(当 CS0=1,CS1=1,

___

CS2=0 时,

CSOUT=1)为片选输出信号,一般不需要,将其悬空。

8250 的读写控制信号有两对,每对信号作用完全相同,只不过是有效电平不同而已。

______

在 8250 被选中时,当数据输入选通信号 DISTR(高电平有效)或

DISTR(低电平有效)信

号有效时,CPU 就从被选择的内部寄存器中读出数据;而数据输出选通信号 DOSTR 或

_______

DOSTR有效时,CPU 就将数据写入被选择的寄存器中。在 PC 机异步适配器中,采用低电

平有效,将

______

DISTR相连,

____

IOR与

_______

DOSTR连接,而 DISTR 和 DOSTR 接地封锁。8250

的(数据总线)驱动器禁止信号 DDIS 引脚,在 CPU 从 8250 读取数据时为低电平,其它时

间为高电平,禁止外部收发器对系统总线的驱动,PC 机异步适配器未使用此信号。

____

IOW与

2.中断控制逻辑

�

INS 8250 具有中断控制和中断优先权判断能力,在串行通信过程中,如果接收数据准

备好、发送保持寄存器空或通信出错以及允许中断时,中断请求引脚 INTRPT 就变成高电平,

产生中断请求(IRQ3 或 IRQ4),输出 1(OUT1)和输出 2(OUT2)两个输出引脚用来控制

INTRPT 的输出。在 PC 机异步适配器中,使用 OUT2 来控制中断请求信号 INTRPT 的输出。

3.时钟信号及复位控制

外部晶体振荡电路产生的 1.8432MHz 信号送到 8250 的 XTAL1 端,作为 8250 的基准工

作时钟。XTAL2 引脚是基准时钟信号的输出端,可用作其他功能的定时控制。外部输入的

__________

BAUDOUT引

基准时钟,经 8250 内部波特率发生器(分频器)分频后产生发送时钟,并经

脚输出。8250 的接收时钟引脚 RCLK 可接收由外部提供的接收时钟信号。而在 PC 机异步

适配器中,将 RCLK 引脚和

___________

BAUDOUT引脚直接相连,即将 8250 芯片内部的发送时钟作为

接收时钟。

在系统复位时,8250 的主复位端 MR 接系统 RESET 信号,将 8250 复位。

4.通信设备之间的信号

有 8 个信号,其中 6 个控制信号

______

RLSD和

SOUT/SIN。它们的功能与定义和 RS—232C 标准相同,不再讨论。

____

CTS、

___

RI ,2 个串行数据信号

____

RTS、

____

DTR、

____

DSR、

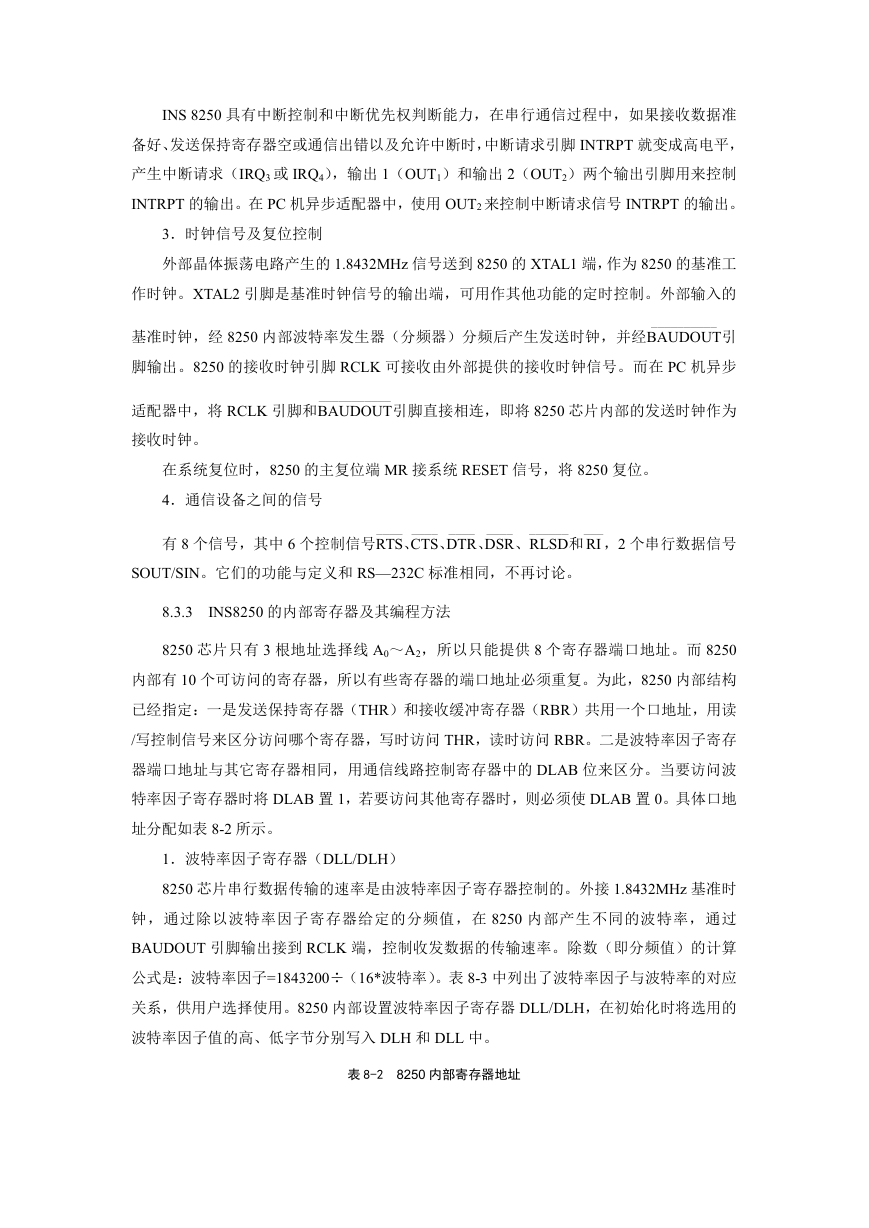

8.3.3

INS8250 的内部寄存器及其编程方法

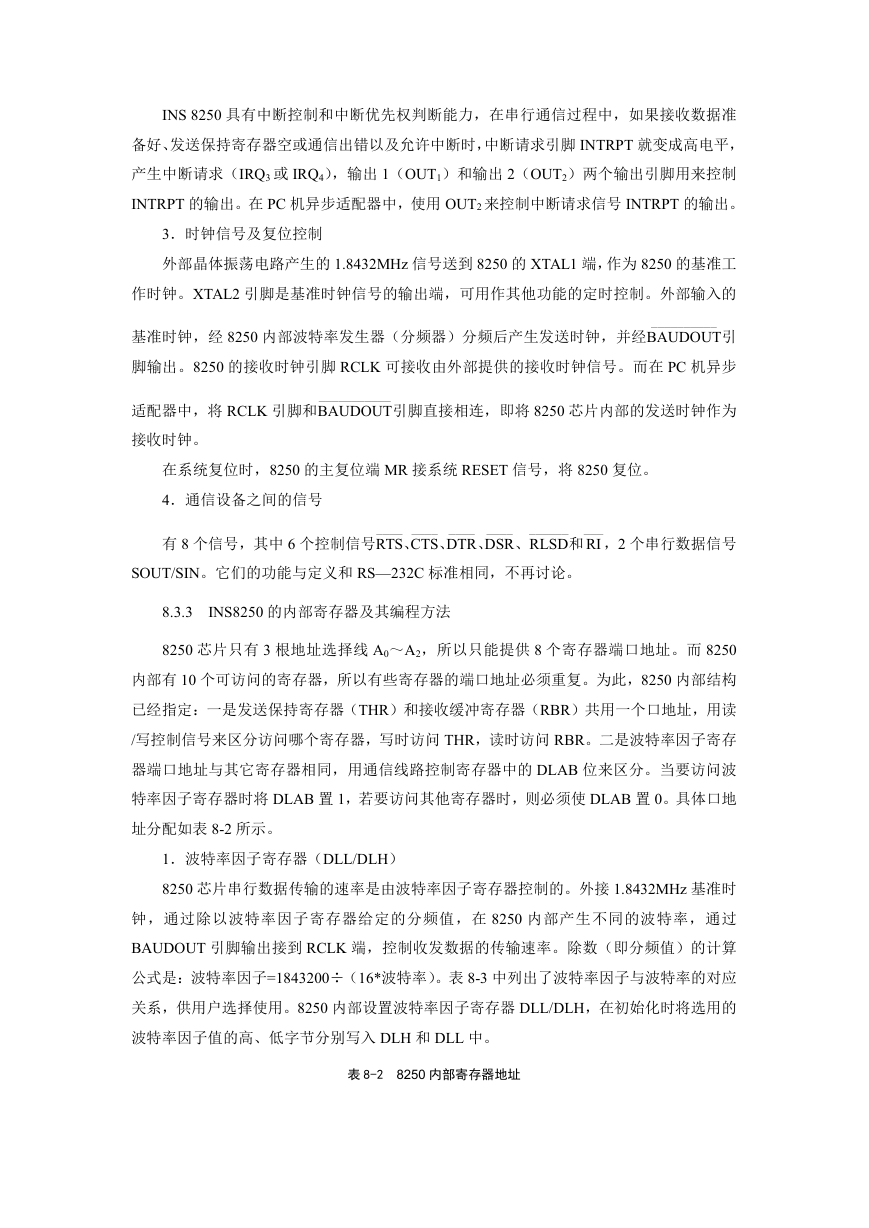

8250 芯片只有 3 根地址选择线 A0~A2,所以只能提供 8 个寄存器端口地址。而 8250

内部有 10 个可访问的寄存器,所以有些寄存器的端口地址必须重复。为此,8250 内部结构

已经指定:一是发送保持寄存器(THR)和接收缓冲寄存器(RBR)共用一个口地址,用读

/写控制信号来区分访问哪个寄存器,写时访问 THR,读时访问 RBR。二是波特率因子寄存

器端口地址与其它寄存器相同,用通信线路控制寄存器中的 DLAB 位来区分。当要访问波

特率因子寄存器时将 DLAB 置 1,若要访问其他寄存器时,则必须使 DLAB 置 0。具体口地

址分配如表 8-2 所示。

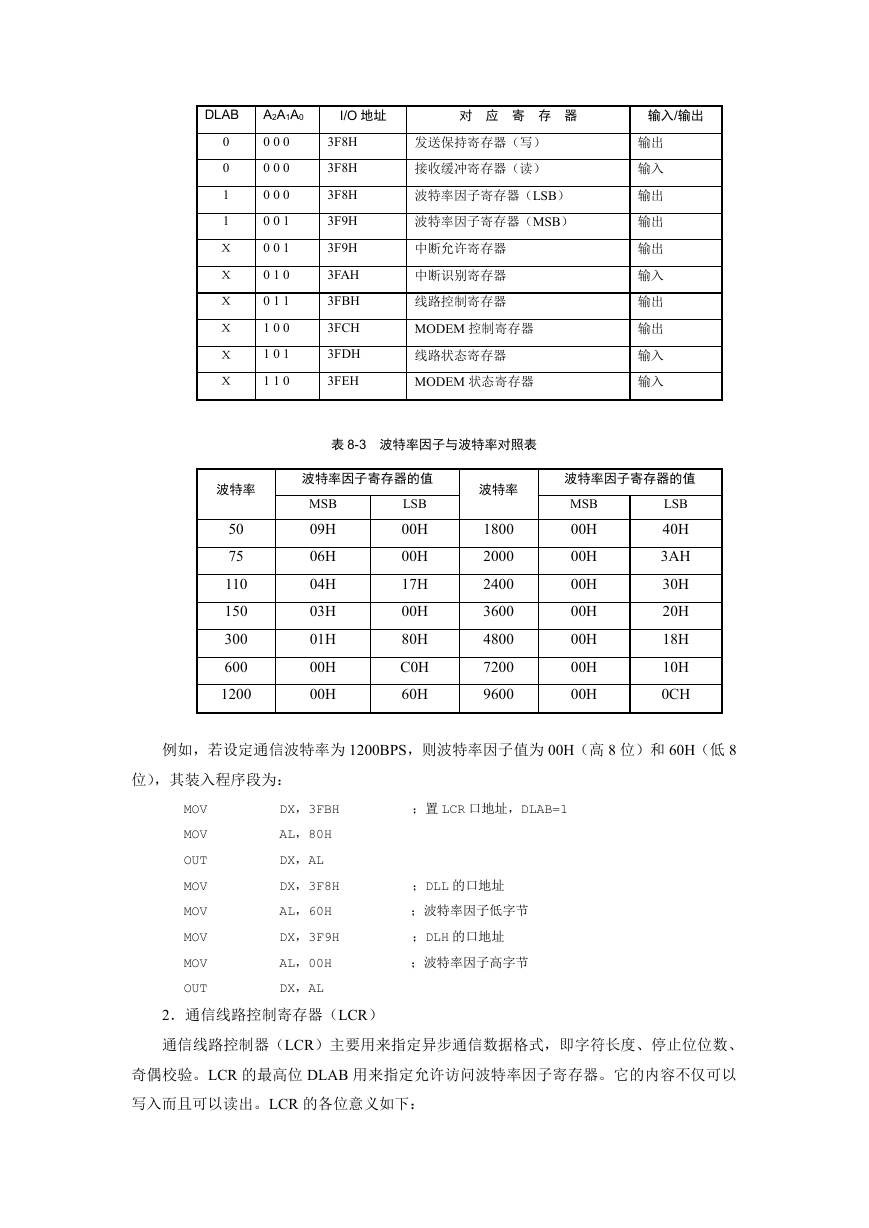

1.波特率因子寄存器(DLL/DLH)

8250 芯片串行数据传输的速率是由波特率因子寄存器控制的。外接 1.8432MHz 基准时

钟,通过除以波特率因子寄存器给定的分频值,在 8250 内部产生不同的波特率,通过

BAUDOUT 引脚输出接到 RCLK 端,控制收发数据的传输速率。除数(即分频值)的计算

公式是:波特率因子=1843200÷(16*波特率)。表 8-3 中列出了波特率因子与波特率的对应

关系,供用户选择使用。8250 内部设置波特率因子寄存器 DLL/DLH,在初始化时将选用的

波特率因子值的高、低字节分别写入 DLH 和 DLL 中。

表 8-2 8250 内部寄存器地址

�

DLAB

0

0

1

1

Х

Х

Х

Х

Х

Х

A2A1A0

0 0 0

0 0 0

0 0 0

0 0 1

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

I/O 地址

对 应 寄 存 器

输入/输出

3F8H

3F8H

3F8H

3F9H

3F9H

3FAH

3FBH

3FCH

3FDH

3FEH

发送保持寄存器(写)

接收缓冲寄存器(读)

波特率因子寄存器(LSB)

波特率因子寄存器(MSB)

中断允许寄存器

中断识别寄存器

线路控制寄存器

MODEM 控制寄存器

线路状态寄存器

MODEM 状态寄存器

输出

输入

输出

输出

输出

输入

输出

输出

输入

输入

表 8-3 波特率因子与波特率对照表

波特率因子寄存器的值

MSB

09H

06H

04H

03H

01H

00H

00H

LSB

00H

00H

17H

00H

80H

C0H

60H

波特率

1800

2000

2400

3600

4800

7200

9600

波特率因子寄存器的值

MSB

00H

00H

00H

00H

00H

00H

00H

LSB

40H

3AH

30H

20H

18H

10H

0CH

波特率

50

75

110

150

300

600

1200

例如,若设定通信波特率为 1200BPS,则波特率因子值为 00H(高 8 位)和 60H(低 8

位),其装入程序段为:

MOV

MOV

OUT

MOV

MOV

MOV

MOV

OUT

DX,3FBH

AL,80H

DX,AL

DX,3F8H

AL,60H

DX,3F9H

AL,00H

DX,AL

;置 LCR 口地址,DLAB=1

;DLL 的口地址

;波特率因子低字节

;DLH 的口地址

;波特率因子高字节

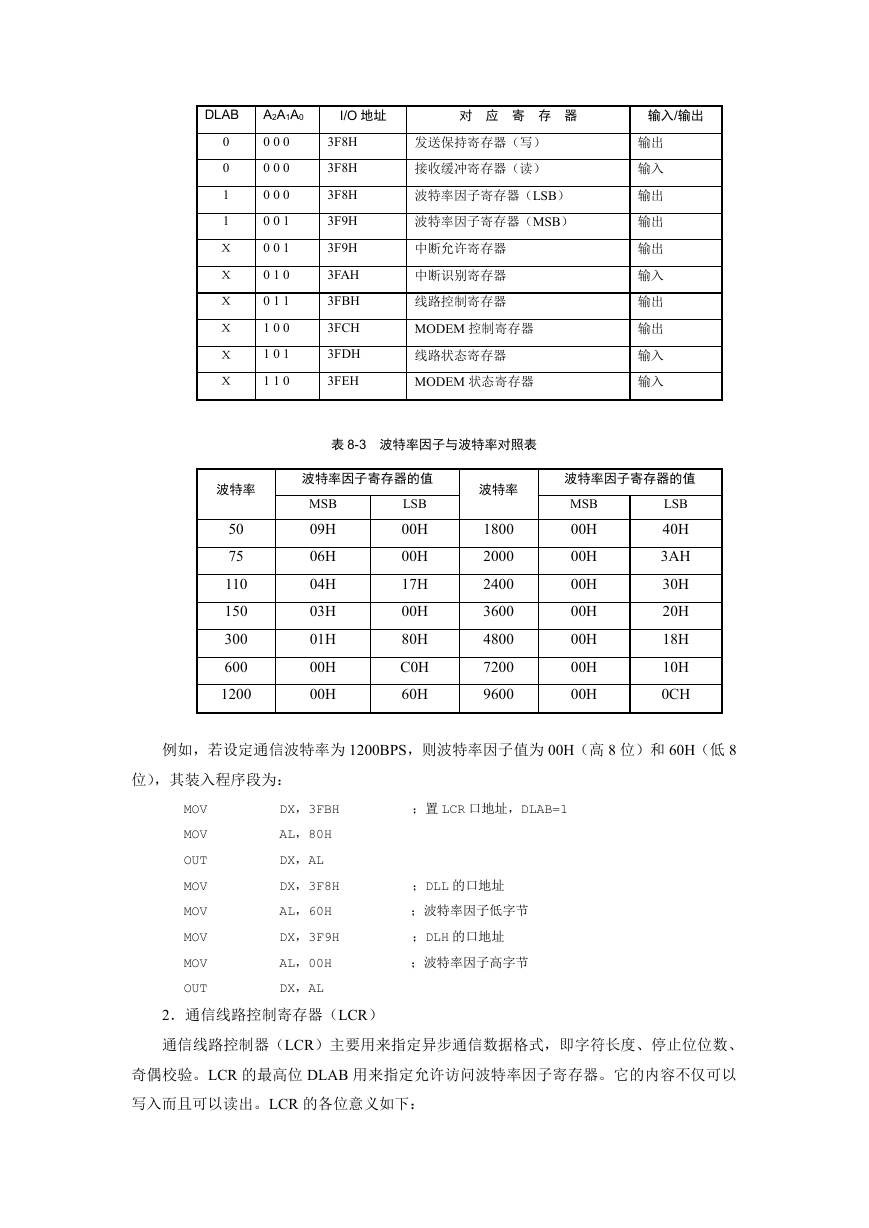

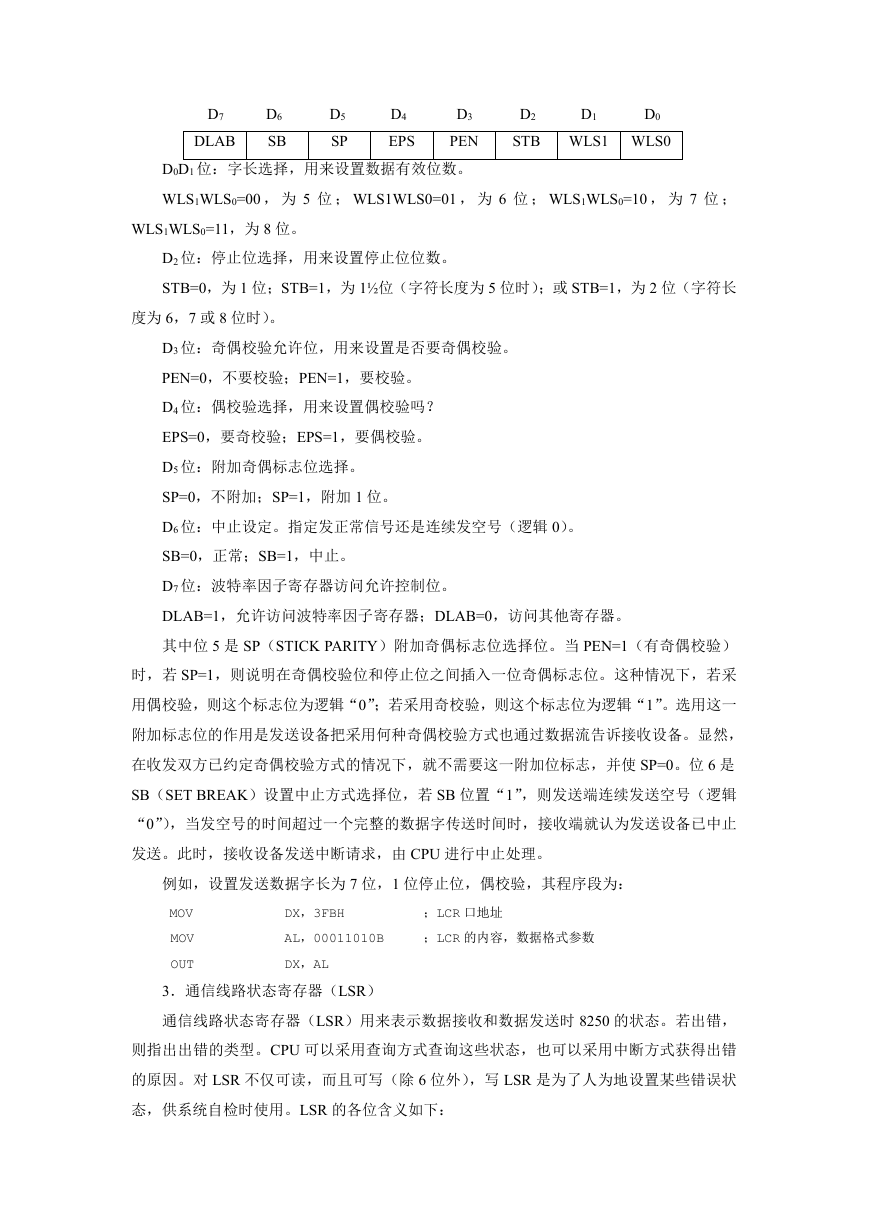

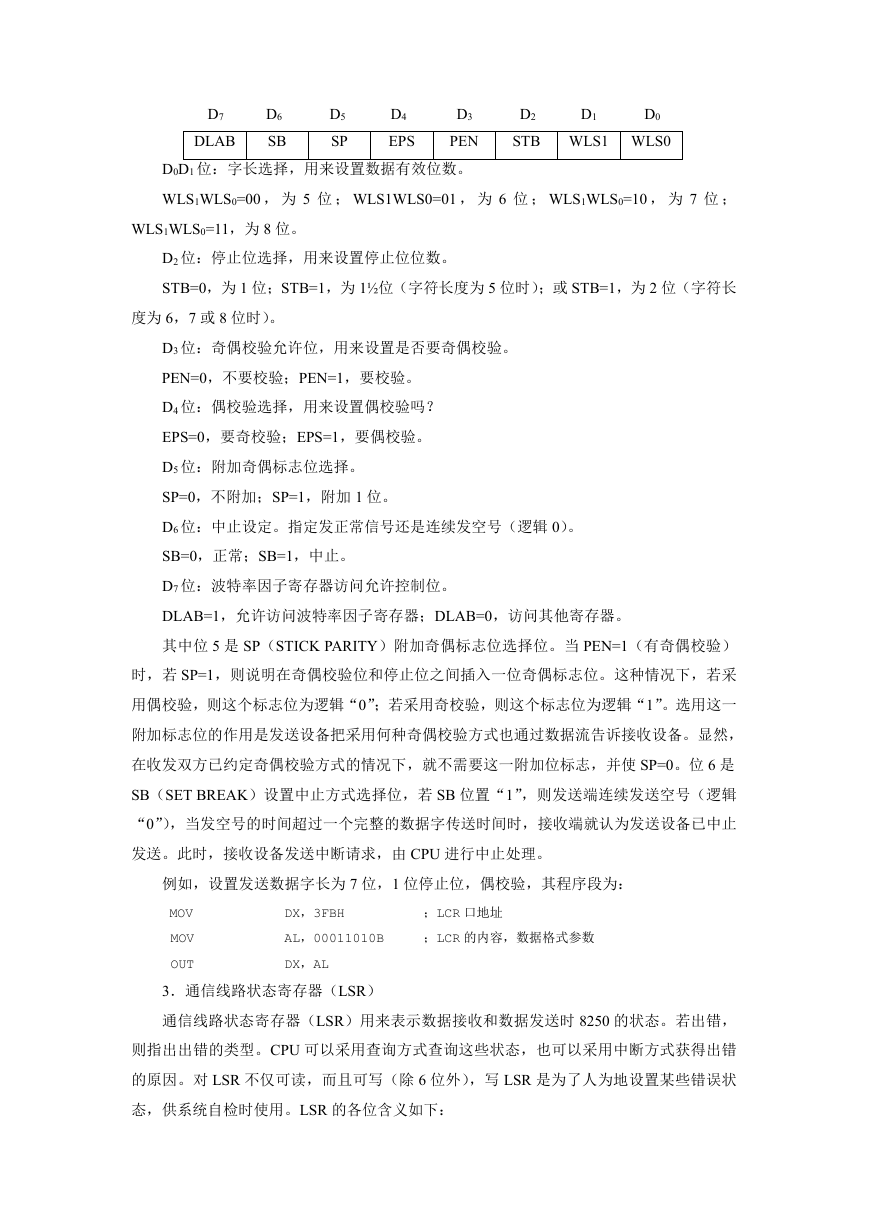

2.通信线路控制寄存器(LCR)

通信线路控制器(LCR)主要用来指定异步通信数据格式,即字符长度、停止位位数、

奇偶校验。LCR 的最高位 DLAB 用来指定允许访问波特率因子寄存器。它的内容不仅可以

写入而且可以读出。LCR 的各位意义如下:

�

D6

SB

D5

SP

D7

DLAB

D3

PEN

D0D1 位:字长选择,用来设置数据有效位数。

WLS1WLS0=00 , 为 5 位 ; WLS1WLS0=01 , 为 6 位 ; WLS1WLS0=10 , 为 7 位 ;

D2

STB WLS1 WLS0

D4

EPS

D1

D0

WLS1WLS0=11,为 8 位。

D2 位:停止位选择,用来设置停止位位数。

STB=0,为 1 位;STB=1,为 1½位(字符长度为 5 位时);或 STB=1,为 2 位(字符长

度为 6,7 或 8 位时)。

D3 位:奇偶校验允许位,用来设置是否要奇偶校验。

PEN=0,不要校验;PEN=1,要校验。

D4 位:偶校验选择,用来设置偶校验吗?

EPS=0,要奇校验;EPS=1,要偶校验。

D5 位:附加奇偶标志位选择。

SP=0,不附加;SP=1,附加 1 位。

D6 位:中止设定。指定发正常信号还是连续发空号(逻辑 0)。

SB=0,正常;SB=1,中止。

D7 位:波特率因子寄存器访问允许控制位。

DLAB=1,允许访问波特率因子寄存器;DLAB=0,访问其他寄存器。

其中位 5 是 SP(STICK PARITY)附加奇偶标志位选择位。当 PEN=1(有奇偶校验)

时,若 SP=1,则说明在奇偶校验位和停止位之间插入一位奇偶标志位。这种情况下,若采

用偶校验,则这个标志位为逻辑“0”;若采用奇校验,则这个标志位为逻辑“1”。选用这一

附加标志位的作用是发送设备把采用何种奇偶校验方式也通过数据流告诉接收设备。显然,

在收发双方已约定奇偶校验方式的情况下,就不需要这一附加位标志,并使 SP=0。位 6 是

SB(SET BREAK)设置中止方式选择位,若 SB 位置“1”,则发送端连续发送空号(逻辑

“0”),当发空号的时间超过一个完整的数据字传送时间时,接收端就认为发送设备已中止

发送。此时,接收设备发送中断请求,由 CPU 进行中止处理。

DX,3FBH

AL,00011010B

DX,AL

;LCR 口地址

;LCR 的内容,数据格式参数

例如,设置发送数据字长为 7 位,1 位停止位,偶校验,其程序段为:

MOV

MOV

OUT

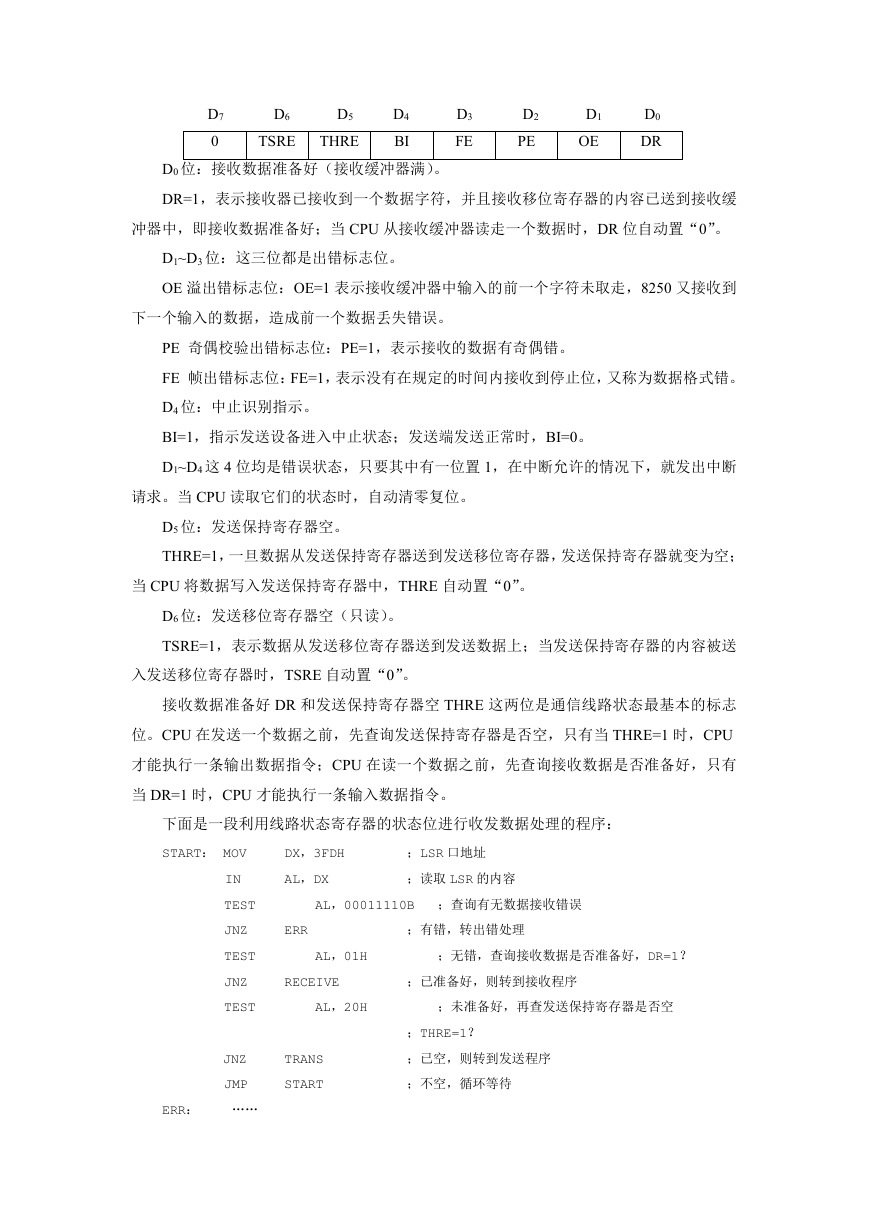

3.通信线路状态寄存器(LSR)

通信线路状态寄存器(LSR)用来表示数据接收和数据发送时 8250 的状态。若出错,

则指出出错的类型。CPU 可以采用查询方式查询这些状态,也可以采用中断方式获得出错

的原因。对 LSR 不仅可读,而且可写(除 6 位外),写 LSR 是为了人为地设置某些错误状

态,供系统自检时使用。LSR 的各位含义如下:

�

D7

0

D6

TSRE

D5

THRE

D4

BI

D3

FE

D2

PE

D1

OE

D0

DR

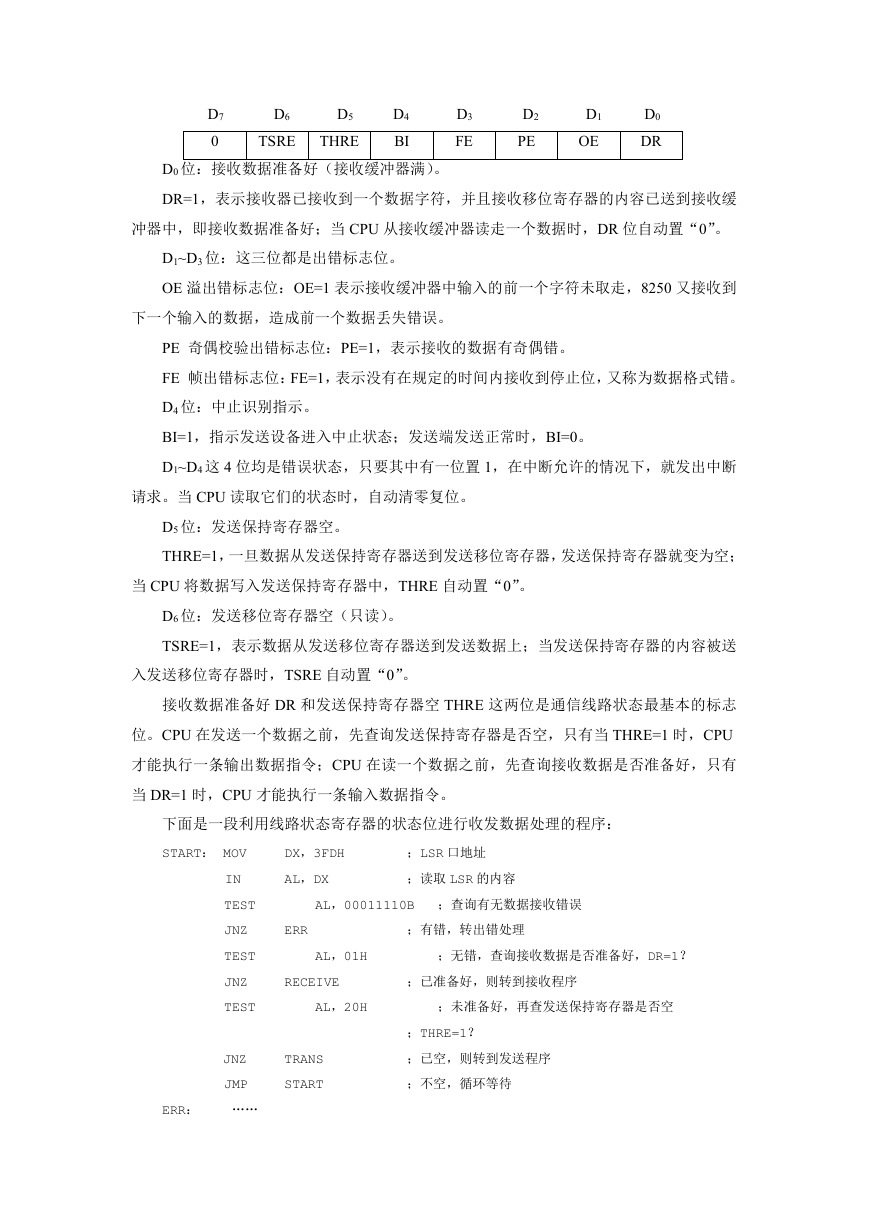

D0 位:接收数据准备好(接收缓冲器满)。

DR=1,表示接收器已接收到一个数据字符,并且接收移位寄存器的内容已送到接收缓

冲器中,即接收数据准备好;当 CPU 从接收缓冲器读走一个数据时,DR 位自动置“0”。

D1~D3 位:这三位都是出错标志位。

OE 溢出错标志位:OE=1 表示接收缓冲器中输入的前一个字符未取走,8250 又接收到

下一个输入的数据,造成前一个数据丢失错误。

PE 奇偶校验出错标志位:PE=1,表示接收的数据有奇偶错。

FE 帧出错标志位:FE=1,表示没有在规定的时间内接收到停止位,又称为数据格式错。

D4 位:中止识别指示。

BI=1,指示发送设备进入中止状态;发送端发送正常时,BI=0。

D1~D4 这 4 位均是错误状态,只要其中有一位置 1,在中断允许的情况下,就发出中断

请求。当 CPU 读取它们的状态时,自动清零复位。

D5 位:发送保持寄存器空。

THRE=1,一旦数据从发送保持寄存器送到发送移位寄存器,发送保持寄存器就变为空;

当 CPU 将数据写入发送保持寄存器中,THRE 自动置“0”。

D6 位:发送移位寄存器空(只读)。

TSRE=1,表示数据从发送移位寄存器送到发送数据上;当发送保持寄存器的内容被送

入发送移位寄存器时,TSRE 自动置“0”。

接收数据准备好 DR 和发送保持寄存器空 THRE 这两位是通信线路状态最基本的标志

位。CPU 在发送一个数据之前,先查询发送保持寄存器是否空,只有当 THRE=1 时,CPU

才能执行一条输出数据指令;CPU 在读一个数据之前,先查询接收数据是否准备好,只有

当 DR=1 时,CPU 才能执行一条输入数据指令。

下面是一段利用线路状态寄存器的状态位进行收发数据处理的程序:

START: MOV

IN

TEST

JNZ

TEST

JNZ

TEST

DX,3FDH

AL,DX

;LSR 口地址

;读取 LSR 的内容

AL,00011110B ;查询有无数据接收错误

ERR

;有错,转出错处理

AL,01H

;无错,查询接收数据是否准备好,DR=1?

RECEIVE

AL,20H

;已准备好,则转到接收程序

;未准备好,再查发送保持寄存器是否空

JNZ

JMP

……

TRANS

START

ERR:

;THRE=1?

;已空,则转到发送程序

;不空,循环等待

�

TRANS : ……

RECEIVE: ……

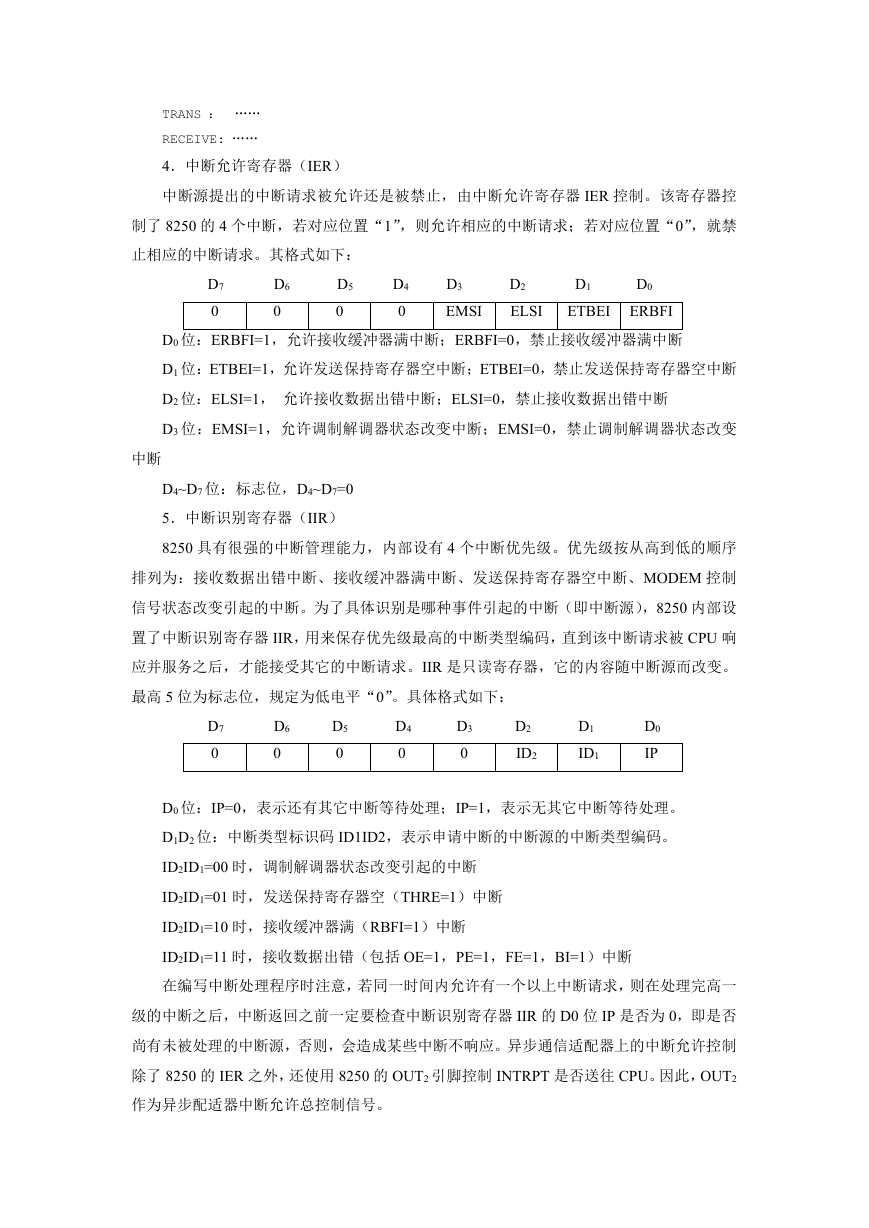

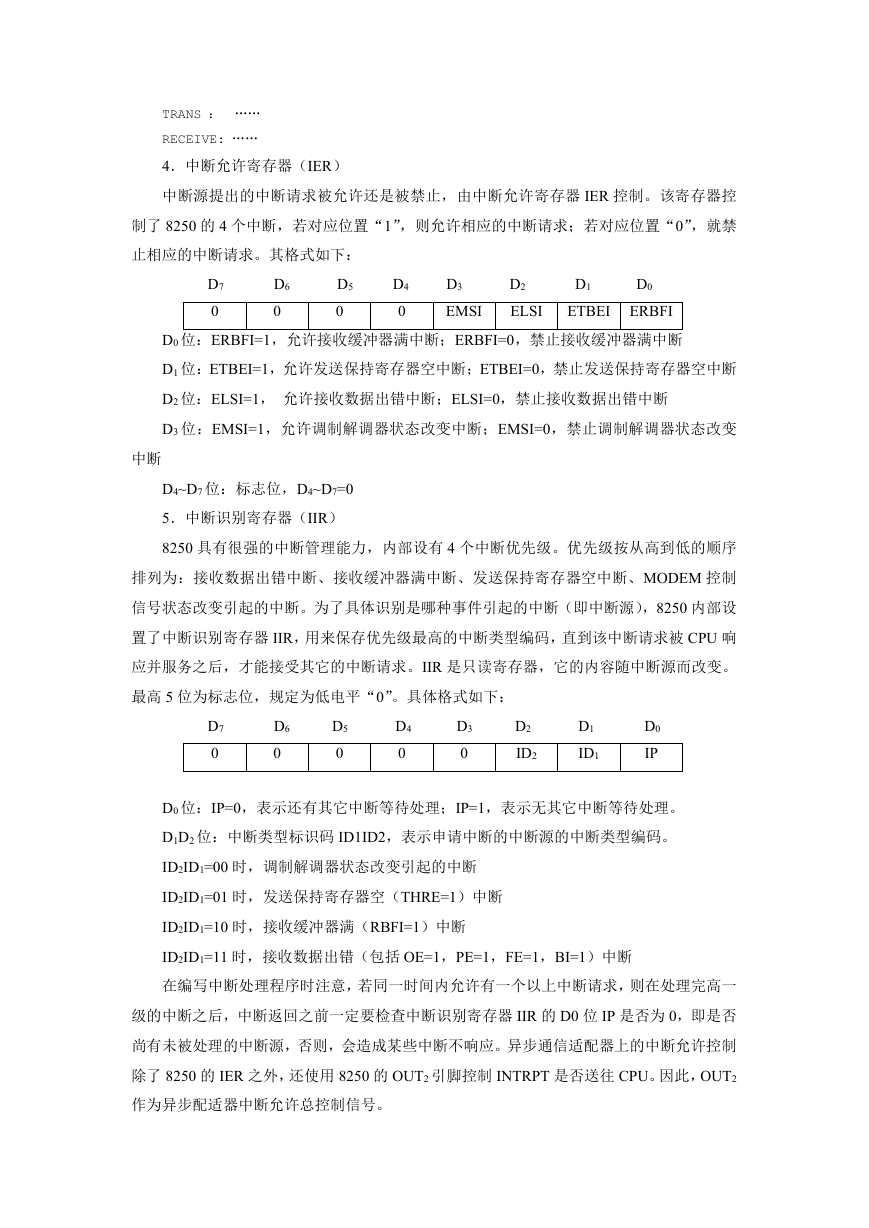

4.中断允许寄存器(IER)

中断源提出的中断请求被允许还是被禁止,由中断允许寄存器 IER 控制。该寄存器控

制了 8250 的 4 个中断,若对应位置“1”,则允许相应的中断请求;若对应位置“0”,就禁

止相应的中断请求。其格式如下:

D7

0

D4

0

D3

EMSI

D2

ELSI

D6

0

D5

0

D0

ERBFI

D0 位:ERBFI=1,允许接收缓冲器满中断;ERBFI=0,禁止接收缓冲器满中断

D1 位:ETBEI=1,允许发送保持寄存器空中断;ETBEI=0,禁止发送保持寄存器空中断

D2 位:ELSI=1, 允许接收数据出错中断;ELSI=0,禁止接收数据出错中断

D3 位:EMSI=1,允许调制解调器状态改变中断;EMSI=0,禁止调制解调器状态改变

D1

ETBEI

中断

D4~D7 位:标志位,D4~D7=0

5.中断识别寄存器(IIR)

8250 具有很强的中断管理能力,内部设有 4 个中断优先级。优先级按从高到低的顺序

排列为:接收数据出错中断、接收缓冲器满中断、发送保持寄存器空中断、MODEM 控制

信号状态改变引起的中断。为了具体识别是哪种事件引起的中断(即中断源),8250 内部设

置了中断识别寄存器 IIR,用来保存优先级最高的中断类型编码,直到该中断请求被 CPU 响

应并服务之后,才能接受其它的中断请求。IIR 是只读寄存器,它的内容随中断源而改变。

最高 5 位为标志位,规定为低电平“0”。具体格式如下:

D7

0

D6

0

D5

0

D4

0

D3

0

D2

ID2

D1

ID1

D0

IP

D0 位:IP=0,表示还有其它中断等待处理;IP=1,表示无其它中断等待处理。

D1D2 位:中断类型标识码 ID1ID2,表示申请中断的中断源的中断类型编码。

ID2ID1=00 时,调制解调器状态改变引起的中断

ID2ID1=01 时,发送保持寄存器空(THRE=1)中断

ID2ID1=10 时,接收缓冲器满(RBFI=1)中断

ID2ID1=11 时,接收数据出错(包括 OE=1,PE=1,FE=1,BI=1)中断

在编写中断处理程序时注意,若同一时间内允许有一个以上中断请求,则在处理完高一

级的中断之后,中断返回之前一定要检查中断识别寄存器 IIR 的 D0 位 IP 是否为 0,即是否

尚有未被处理的中断源,否则,会造成某些中断不响应。异步通信适配器上的中断允许控制

除了 8250 的 IER 之外,还使用 8250 的 OUT2 引脚控制 INTRPT 是否送往 CPU。因此,OUT2

作为异步配适器中断允许总控制信号。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc