利用利用EDA技术和技术和VHDL语言的智能密码锁设计

语言的智能密码锁设计

A Digital PasswordLock Designed by VHDL

Abstract:This paper introduces a new type digital pasword lock is designed with EDA technology and VHDL language. This

new digital password lock has beter application prospect , becauseof smal volume , lowpower , lowprice , securityand easy

maintenanceand upgrade.

Keywords:Digital pasword lock EDA VHDL MAX+ PLUSⅡ

摘 要:本文介绍一种利用EDA技术和VHDL语言 ,在MAX+PLUSⅡ环境下,设计了一种新型的智能密码锁。它体积小、功耗

低、价格便宜、安全可靠,维护和升级都十分方便,具有较好的应用前景。

关键词:数字密码锁 EDA VHDL MAX+ PLUSⅡ

随着社会物质财富的日益增长,安全防盗已成为全社会问题。人们对锁的要求越来越高,既要安全可靠地防盗,又要使用方便。

弹子锁由于结构上的局限已难以满足当前社会管理和防盗要求,特别是在人员经常变动的公共场所,如办公室、宾馆等地方。

电子密码锁由于其自身的优势,越来越受到人们的青睐 ,但是目前使用的电子密码锁大部分是基于单片机用分离元件实现的,

其成本较高且可靠性得不保证。本文采用先进的EDA 技术,利用 MAX +PLUXⅡ工作平台和 VHDL 语言,设计了一种新型的智

能密码锁。该密码锁具有密码预置和误码报警等功能,用一片 FPGA 芯片实现,从而大大简化了系统结构,降低了成本,提高

了系统的保密性和可靠性。采用这种器件开发的数字系统,其升级与改进极其方便。

1、 智能密码锁的设计要求

该密码锁的密码由六位十进制数字组成,初始设定“000000”。可由用户任意设置密码,密码输入正确时开锁,连续三次输入错

误密码时系统报警。

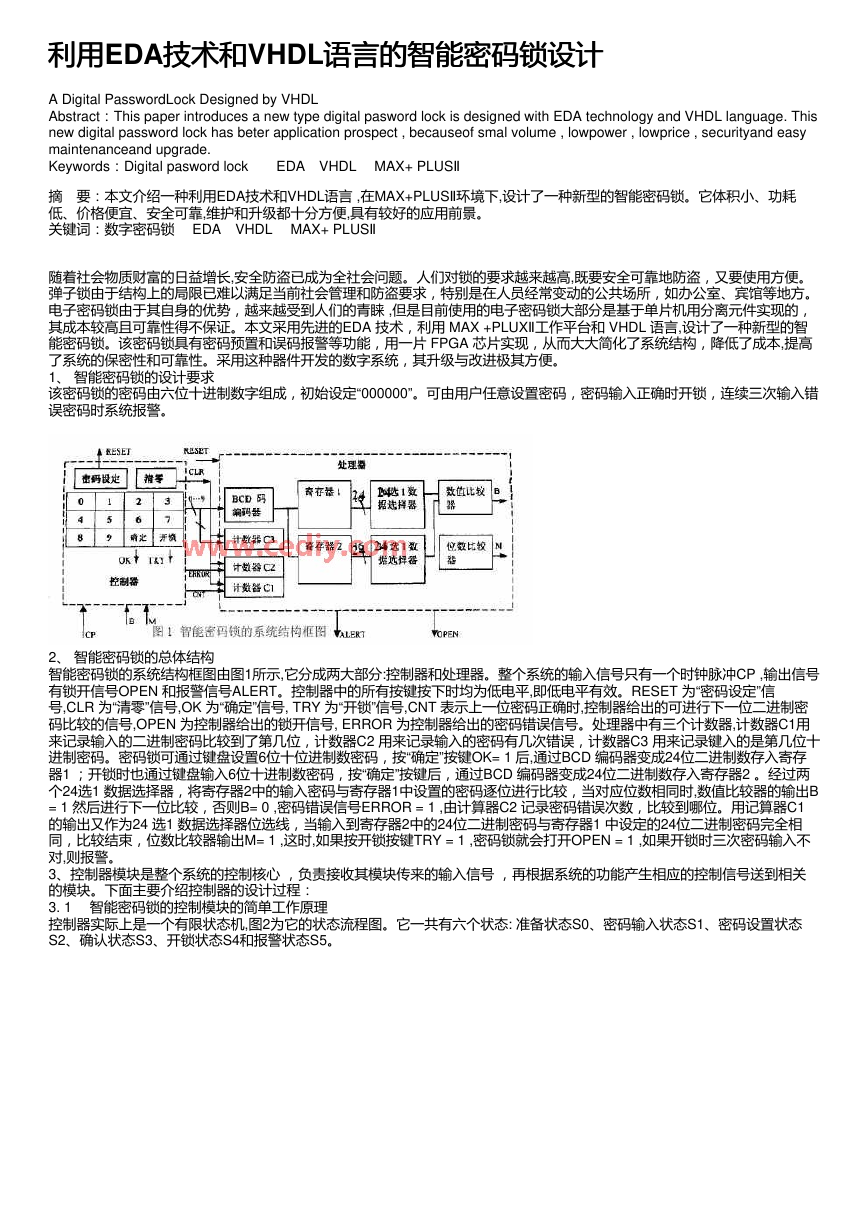

2、 智能密码锁的总体结构

智能密码锁的系统结构框图由图1所示,它分成两大部分:控制器和处理器。整个系统的输入信号只有一个时钟脉冲CP ,输出信号

有锁开信号OPEN 和报警信号ALERT。控制器中的所有按键按下时均为低电平,即低电平有效。RESET 为“密码设定”信

号,CLR 为“清零”信号,OK 为“确定”信号, TRY 为“开锁”信号,CNT 表示上一位密码正确时,控制器给出的可进行下一位二进制密

码比较的信号,OPEN 为控制器给出的锁开信号, ERROR 为控制器给出的密码错误信号。处理器中有三个计数器,计数器C1用

来记录输入的二进制密码比较到了第几位,计数器C2 用来记录输入的密码有几次错误,计数器C3 用来记录键入的是第几位十

进制密码。密码锁可通过键盘设置6位十位进制数密码,按“确定”按键OK= 1 后,通过BCD 编码器变成24位二进制数存入寄存

器1 ;开锁时也通过键盘输入6位十进制数密码,按“确定”按键后,通过BCD 编码器变成24位二进制数存入寄存器2 。经过两

个24选1 数据选择器,将寄存器2中的输入密码与寄存器1中设置的密码逐位进行比较,当对应位数相同时,数值比较器的输出B

= 1 然后进行下一位比较,否则B= 0 ,密码错误信号ERROR = 1 ,由计算器C2 记录密码错误次数,比较到哪位。用记算器C1

的输出又作为24 选1 数据选择器位选线,当输入到寄存器2中的24位二进制密码与寄存器1 中设定的24位二进制密码完全相

同,比较结束,位数比较器输出M= 1 ,这时,如果按开锁按键TRY = 1 ,密码锁就会打开OPEN = 1 ,如果开锁时三次密码输入不

对,则报警。

3、控制器模块是整个系统的控制核心 ,负责接收其模块传来的输入信号 ,再根据系统的功能产生相应的控制信号送到相关

的模块。下面主要介绍控制器的设计过程:

3. 1 智能密码锁的控制模块的简单工作原理

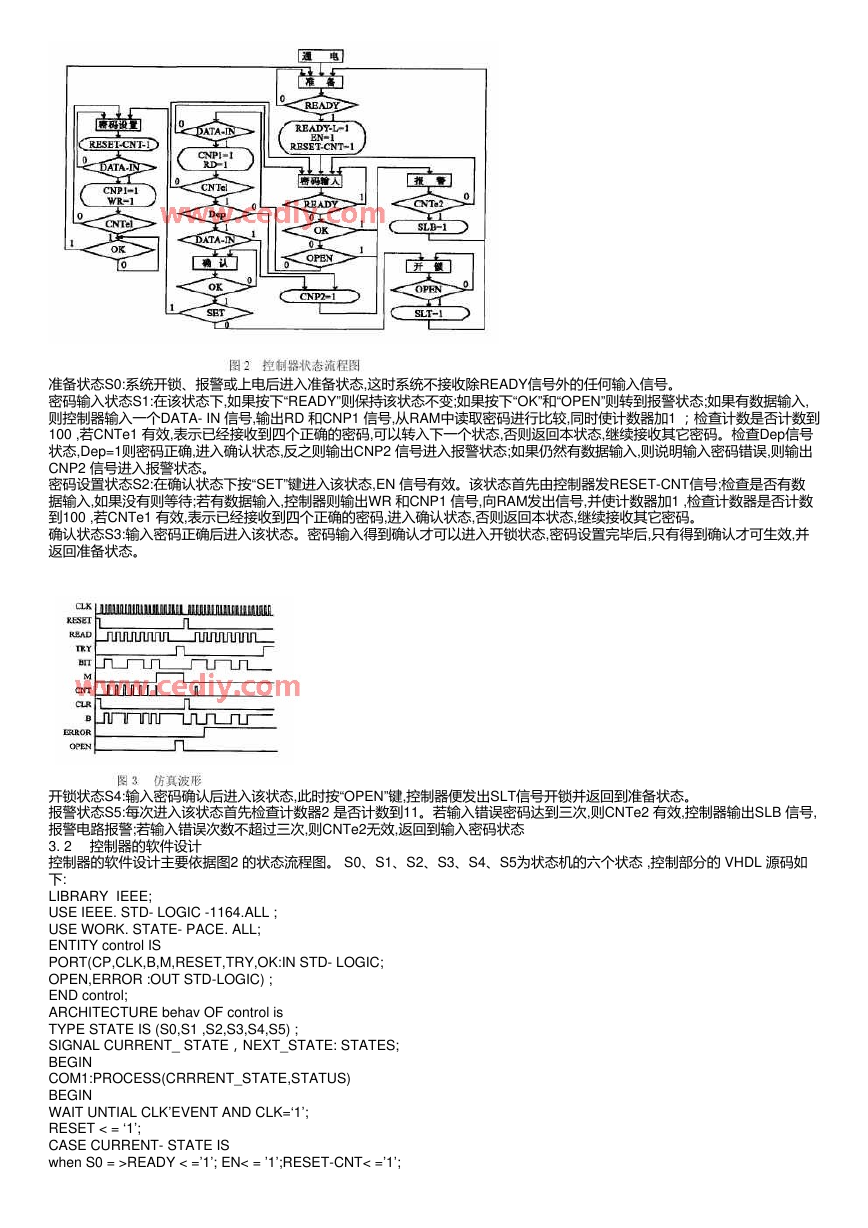

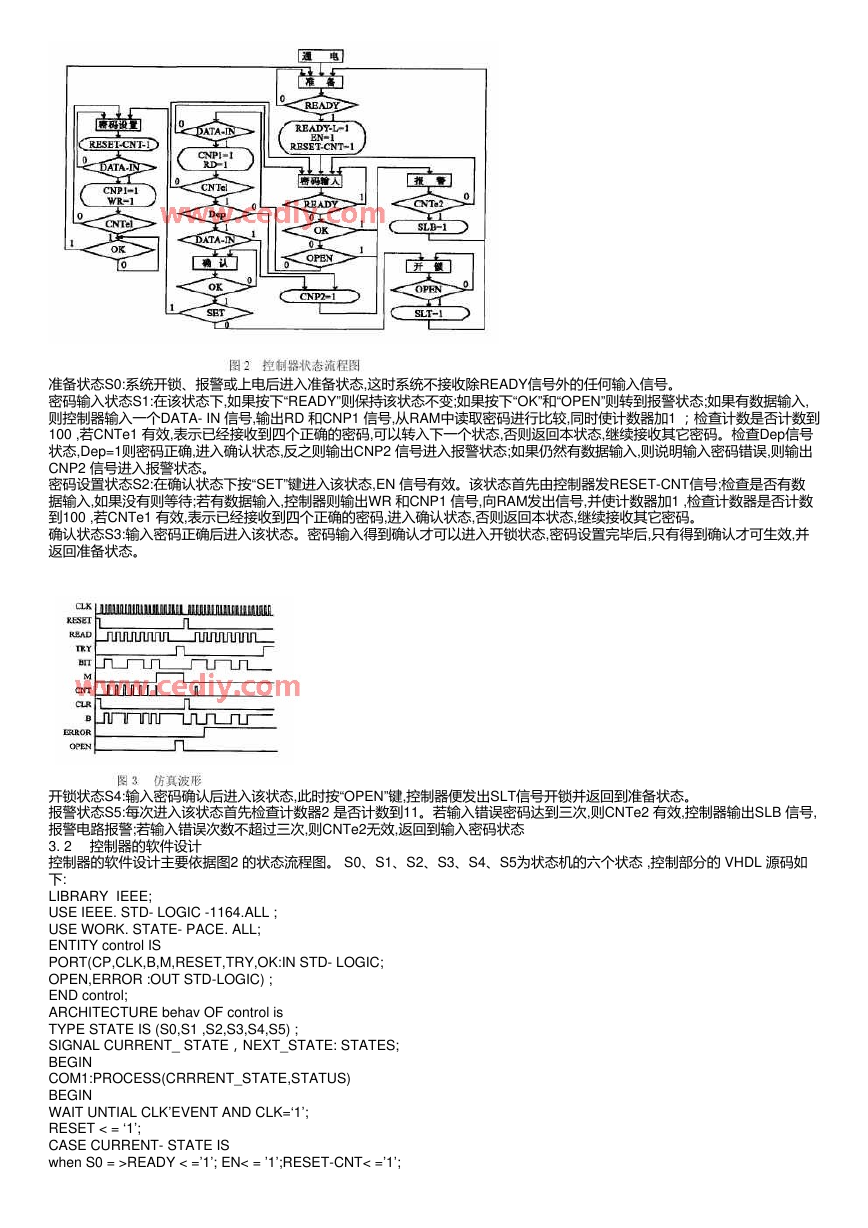

控制器实际上是一个有限状态机,图2为它的状态流程图。它一共有六个状态: 准备状态S0、密码输入状态S1、密码设置状态

S2、确认状态S3、开锁状态S4和报警状态S5。

�

准备状态S0:系统开锁、报警或上电后进入准备状态,这时系统不接收除READY信号外的任何输入信号。

密码输入状态S1:在该状态下,如果按下“READY”则保持该状态不变;如果按下“OK”和“OPEN”则转到报警状态;如果有数据输入,

则控制器输入一个DATA- IN 信号,输出RD 和CNP1 信号,从RAM中读取密码进行比较,同时使计数器加1 ;检查计数是否计数到

100 ,若CNTe1 有效,表示已经接收到四个正确的密码,可以转入下一个状态,否则返回本状态,继续接收其它密码。检查Dep信号

状态,Dep=1则密码正确,进入确认状态,反之则输出CNP2 信号进入报警状态;如果仍然有数据输入,则说明输入密码错误,则输出

CNP2 信号进入报警状态。

密码设置状态S2:在确认状态下按“SET”键进入该状态,EN 信号有效。该状态首先由控制器发RESET-CNT信号;检查是否有数

据输入,如果没有则等待;若有数据输入,控制器则输出WR 和CNP1 信号,向RAM发出信号,并使计数器加1 ,检查计数器是否计数

到100 ,若CNTe1 有效,表示已经接收到四个正确的密码,进入确认状态,否则返回本状态,继续接收其它密码。

确认状态S3:输入密码正确后进入该状态。密码输入得到确认才可以进入开锁状态,密码设置完毕后,只有得到确认才可生效,并

返回准备状态。

开锁状态S4:输入密码确认后进入该状态,此时按“OPEN”键,控制器便发出SLT信号开锁并返回到准备状态。

报警状态S5:每次进入该状态首先检查计数器2 是否计数到11。若输入错误密码达到三次,则CNTe2 有效,控制器输出SLB 信号,

报警电路报警;若输入错误次数不超过三次,则CNTe2无效,返回到输入密码状态

3. 2 控制器的软件设计

控制器的软件设计主要依据图2 的状态流程图。 S0、S1、S2、S3、S4、S5为状态机的六个状态 ,控制部分的 VHDL 源码如

下:

LIBRARY IEEE;

USE IEEE. STD- LOGIC -1164.ALL ;

USE WORK. STATE- PACE. ALL;

ENTITY control IS

PORT(CP,CLK,B,M,RESET,TRY,OK:IN STD- LOGIC;

OPEN,ERROR :OUT STD-LOGIC) ;

END control;

ARCHITECTURE behav OF control is

TYPE STATE IS (S0,S1 ,S2,S3,S4,S5) ;

SIGNAL CURRENT_ STATE,NEXT_STATE: STATES;

BEGIN

COM1:PROCESS(CRRRENT_STATE,STATUS)

BEGIN

WAIT UNTIAL CLK’EVENT AND CLK=‘1’;

RESET < = ‘1’;

CASE CURRENT- STATE IS

when S0 = >READY < =’1’; EN< = ’1’;RESET-CNT< =’1’;

�

if(READY = ‘0’) then curent- state < = S0;

else

curent- state < =S1;

…

因源程序较长, 故程序略

…

END IF;

END CASE;

END PROCESS;

END behav;

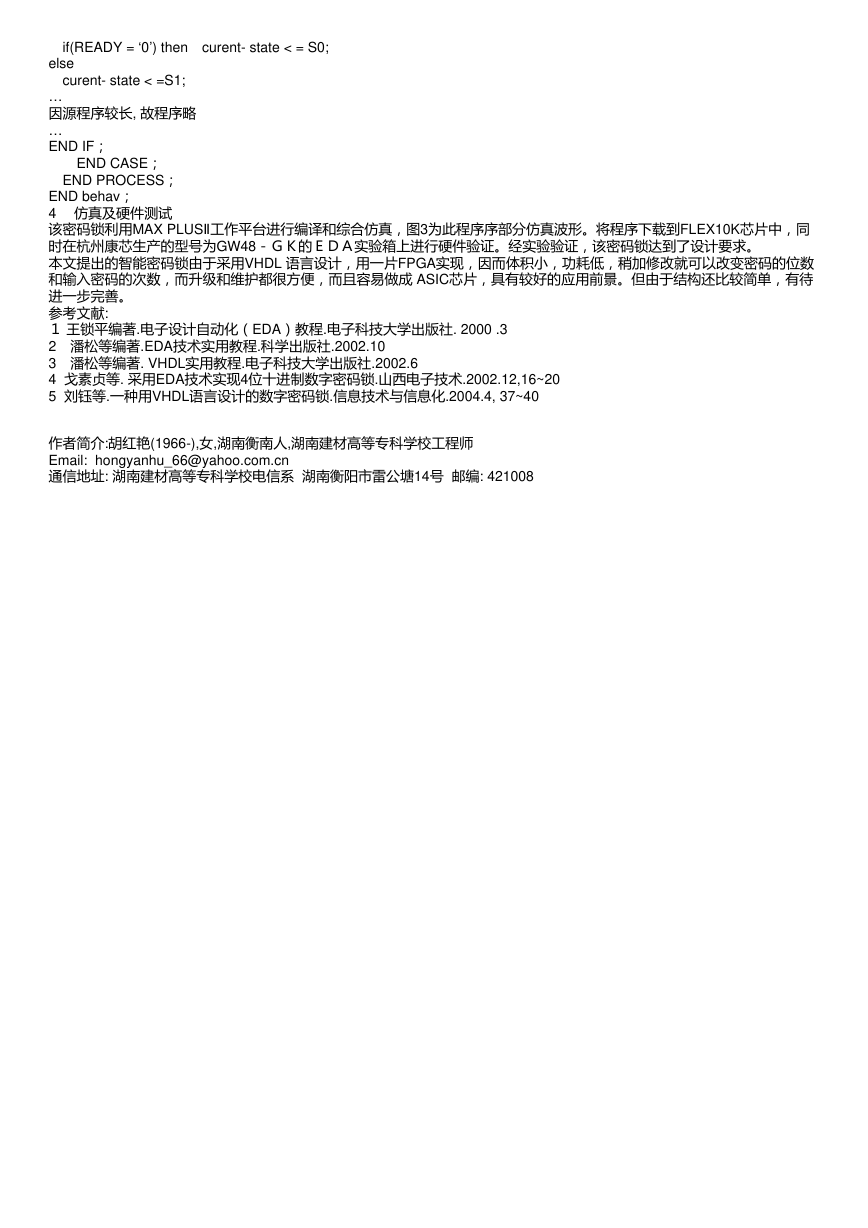

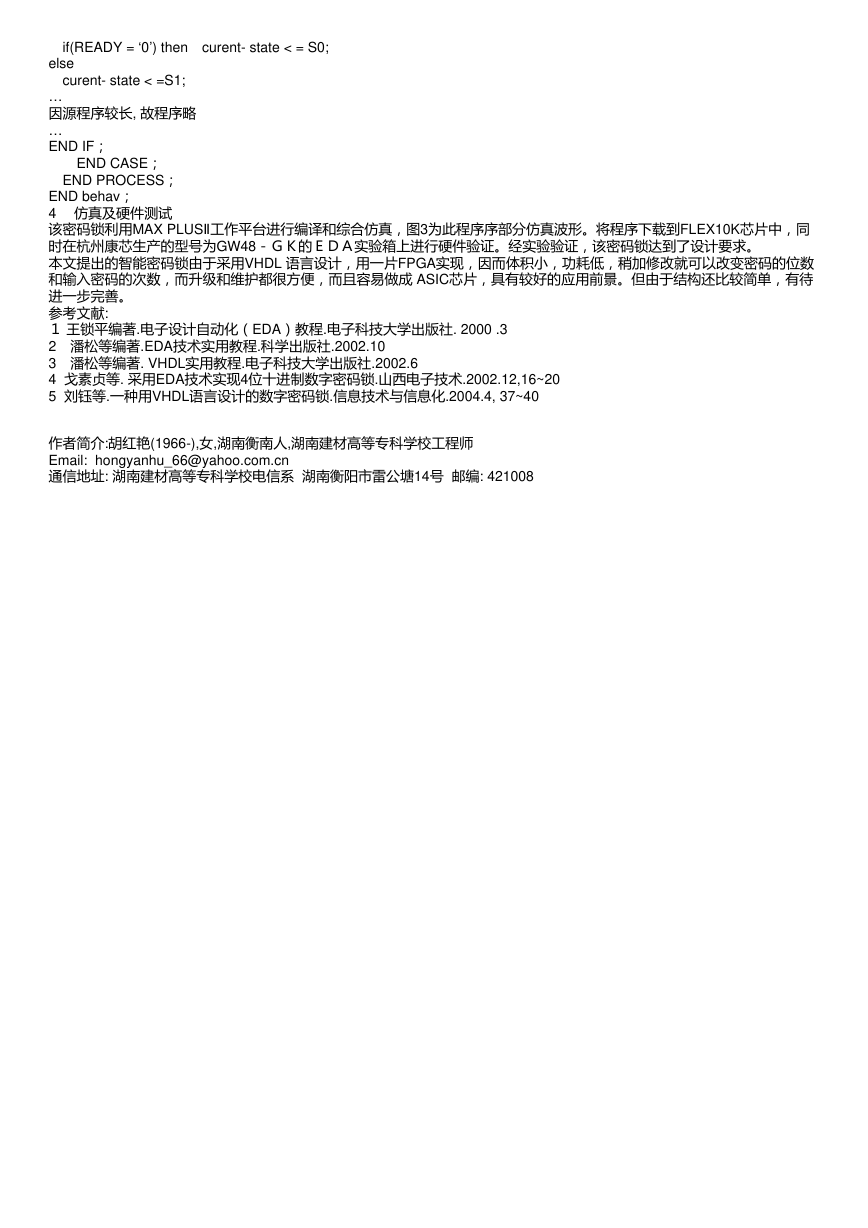

4 仿真及硬件测试

该密码锁利用MAX PLUSⅡ工作平台进行编译和综合仿真,图3为此程序序部分仿真波形。将程序下载到FLEX10K芯片中,同

时在杭州康芯生产的型号为GW48-GK的EDA实验箱上进行硬件验证。经实验验证,该密码锁达到了设计要求。

本文提出的智能密码锁由于采用VHDL 语言设计,用一片FPGA实现,因而体积小,功耗低,稍加修改就可以改变密码的位数

和输入密码的次数,而升级和维护都很方便,而且容易做成 ASIC芯片,具有较好的应用前景。但由于结构还比较简单,有待

进一步完善。

参考文献:

1 王锁平编著.电子设计自动化(EDA)教程.电子科技大学出版社. 2000 .3

2 潘松等编著.EDA技术实用教程.科学出版社.2002.10

3 潘松等编著. VHDL实用教程.电子科技大学出版社.2002.6

4 戈素贞等. 采用EDA技术实现4位十进制数字密码锁.山西电子技术.2002.12,16~20

5 刘钰等.一种用VHDL语言设计的数字密码锁.信息技术与信息化.2004.4, 37~40

作者简介:胡红艳(1966-),女,湖南衡南人,湖南建材高等专科学校工程师

Email: hongyanhu_66@yahoo.com.cn

通信地址: 湖南建材高等专科学校电信系 湖南衡阳市雷公塘14号 邮编: 421008

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc