Common Flash Memory Interface

Publication 100

Vendor & Device

ID Code Assignments

Publication Date: May 30, 1997

Volume Number 97.1

Intel Corporation

1900 Prairie City Rd, Folsom CA 95630-9598

�

Common Flash Memory Interface

CFI PUBLICATION 100

Publication Date: May 30, 1997

Edition Date Published

1.00

1.10

07/25/96

05/30/97

Revision Record

Revised Contents

First Draft Release

Addition of Mitsubishi Vendor Codes and clerical

corrections

Intel CFI Program Office

c/o Alan Hanson

Intel Corporation

1900 Prairie City Road, Mailstop FM3-123

Folsom, Ca. 95630-9598

Notice

Information in this document is provided in connection with Intel products. No license, express or

implied, by estoppel or otherwise, to any intellectual property rights is granted by this document.

Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no

liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of

Intel products including liability or warranties relating to fitness for a particular purpose,

merchantability, or infringement of any patent, copyright or other intellectual property right. Intel

products are not intended for use in medical, life saving, or life sustaining applications. Intel may

make changes to specifications and product descriptions at any time, without notice.

CFI Publication 100

Page 1

Publication Date: May 30, 1997

Volume Number

�

Table of Contents

Overview

A. Purpose

B. Scope

Section 1. Vendor Command Set & Control Interface ID Code Assignments

Section 2. Device Interface Code Assignments

Appendix

Appendix A. CFI Structure Examples

Publication Date: May 30, 1997

Volume Number

CFI Publication 100

Page 2

�

Overview

A. Purpose

The CFI Publication 100 is a companion document to the Common Flash Interface (CFI) specification,

which outlines device and host system software interrogation handshake. CFI Publication 100

documents ID Code assignments for: 1) the Vendor-specific Command Set and Control Interfaces

and 2) the Device Interfaces. It is published as needed when additions are made to either of these lists

of codes.

B. Scope

The Vendor Command Set and Control Interface ID codes listed in CFI Publication 100 are assigned

to each unique manufacturers’ interfaces upon request to the CFI Program Office. Any number of

different interfaces may be thus identified by a single vendor or association of vendors. It is up to

those manufacturers to provide the detailed specifications for each identified interface. Similarly,

new device interface codes will be assigned as needed as new devices employing the Common Flash

Interface Query scheme are identified. CFI Publication 100 also provides examples of Query data

output for pre-CFI devices as provided by participating vendors; these represent the appropriate data

for the specifications and geometry of these devices as they would appear in the Query structure if the

Query mode were available for them.

CFI Publication 100

Page 3

Publication Date: May 30, 1997

Volume Number

�

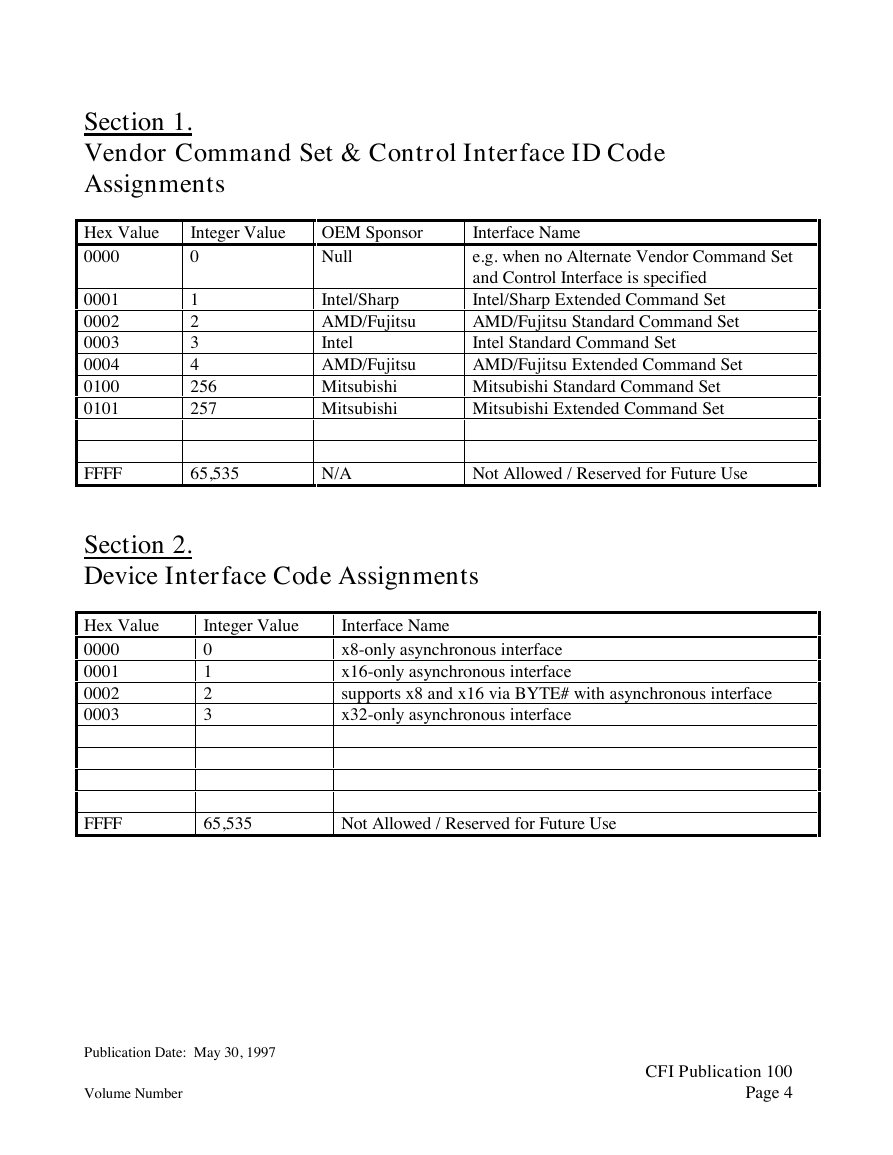

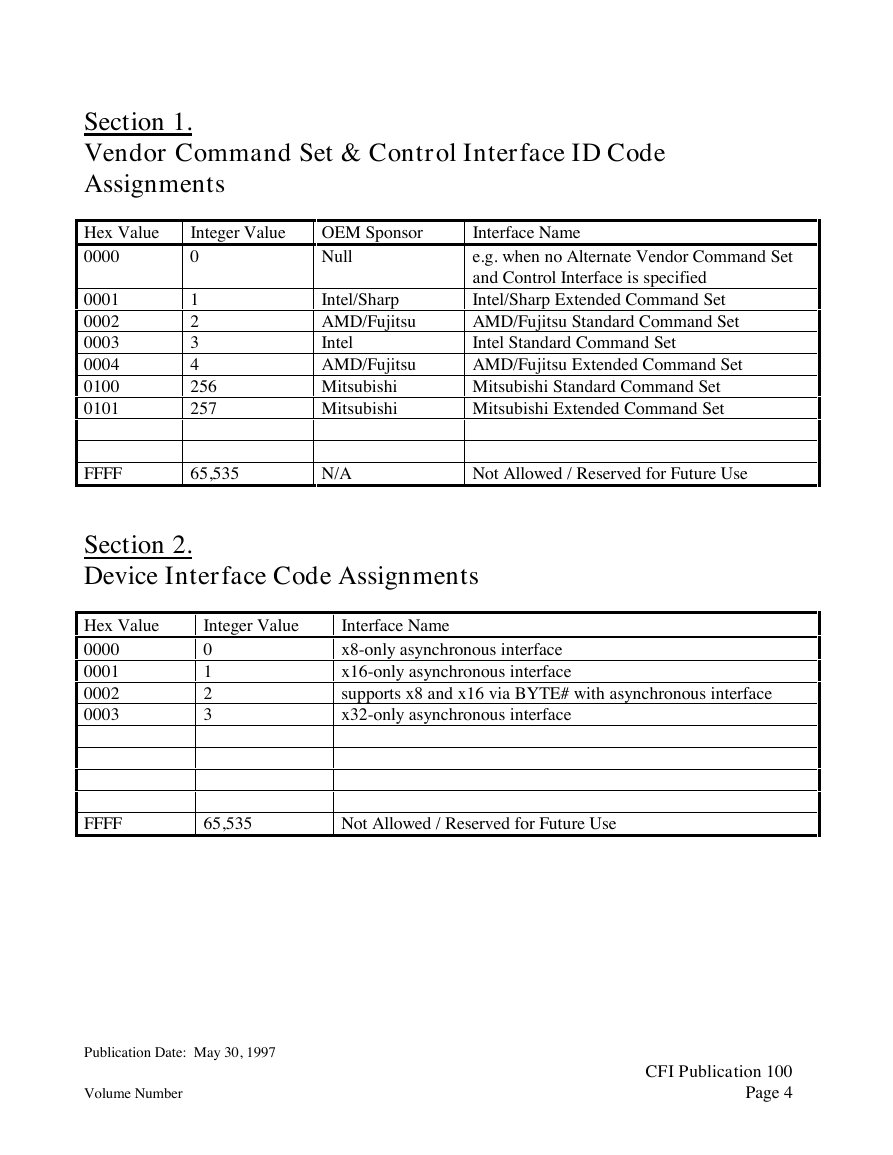

Section 1.

Vendor Command Set & Control Interface ID Code

Assignments

Hex Value

0000

Integer Value

0

OEM Sponsor

Null

0001

0002

0003

0004

0100

0101

1

2

3

4

256

257

Intel/Sharp

AMD/Fujitsu

Intel

AMD/Fujitsu

Mitsubishi

Mitsubishi

Interface Name

e.g. when no Alternate Vendor Command Set

and Control Interface is specified

Intel/Sharp Extended Command Set

AMD/Fujitsu Standard Command Set

Intel Standard Command Set

AMD/Fujitsu Extended Command Set

Mitsubishi Standard Command Set

Mitsubishi Extended Command Set

FFFF

65,535

N/A

Not Allowed / Reserved for Future Use

Section 2.

Device Interface Code Assignments

Hex Value

0000

0001

0002

0003

Integer Value

0

1

2

3

Interface Name

x8-only asynchronous interface

x16-only asynchronous interface

supports x8 and x16 via BYTE# with asynchronous interface

x32-only asynchronous interface

FFFF

65,535

Not Allowed / Reserved for Future Use

Publication Date: May 30, 1997

Volume Number

CFI Publication 100

Page 4

�

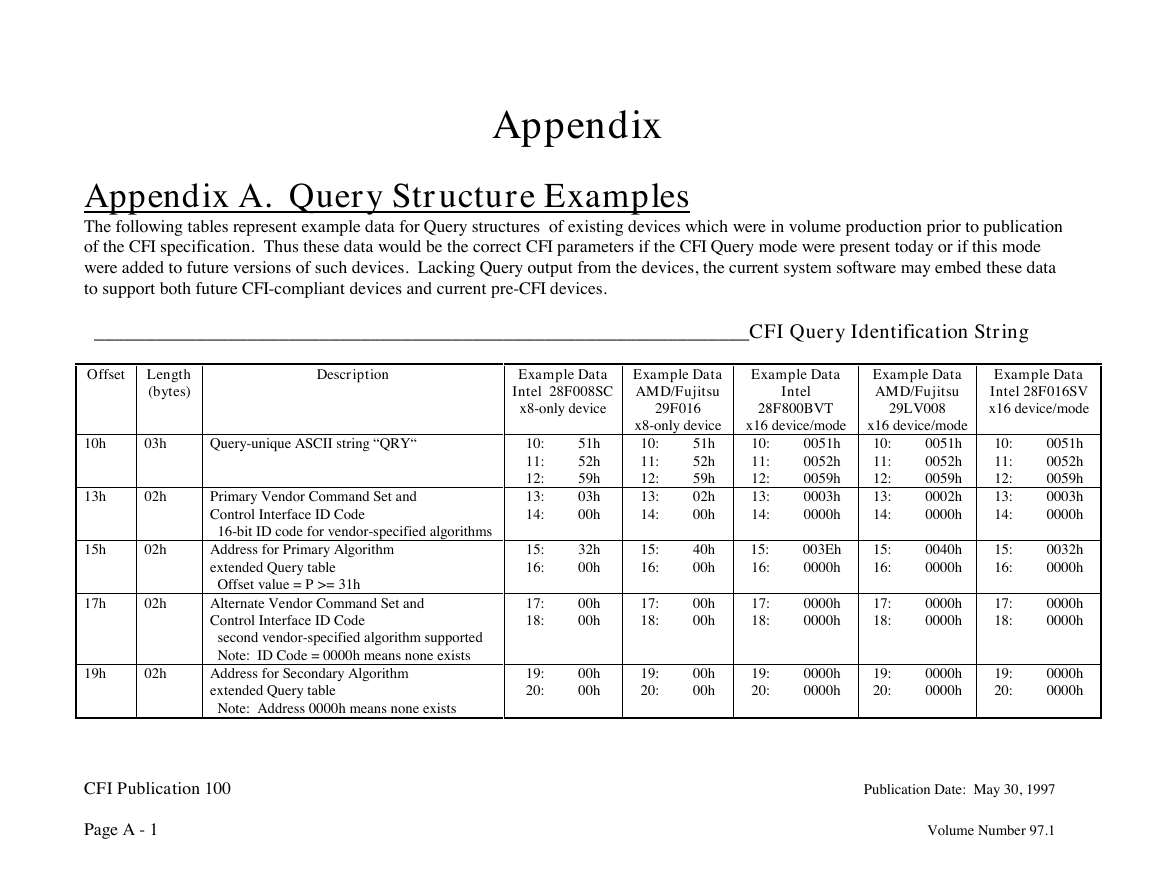

Appendix

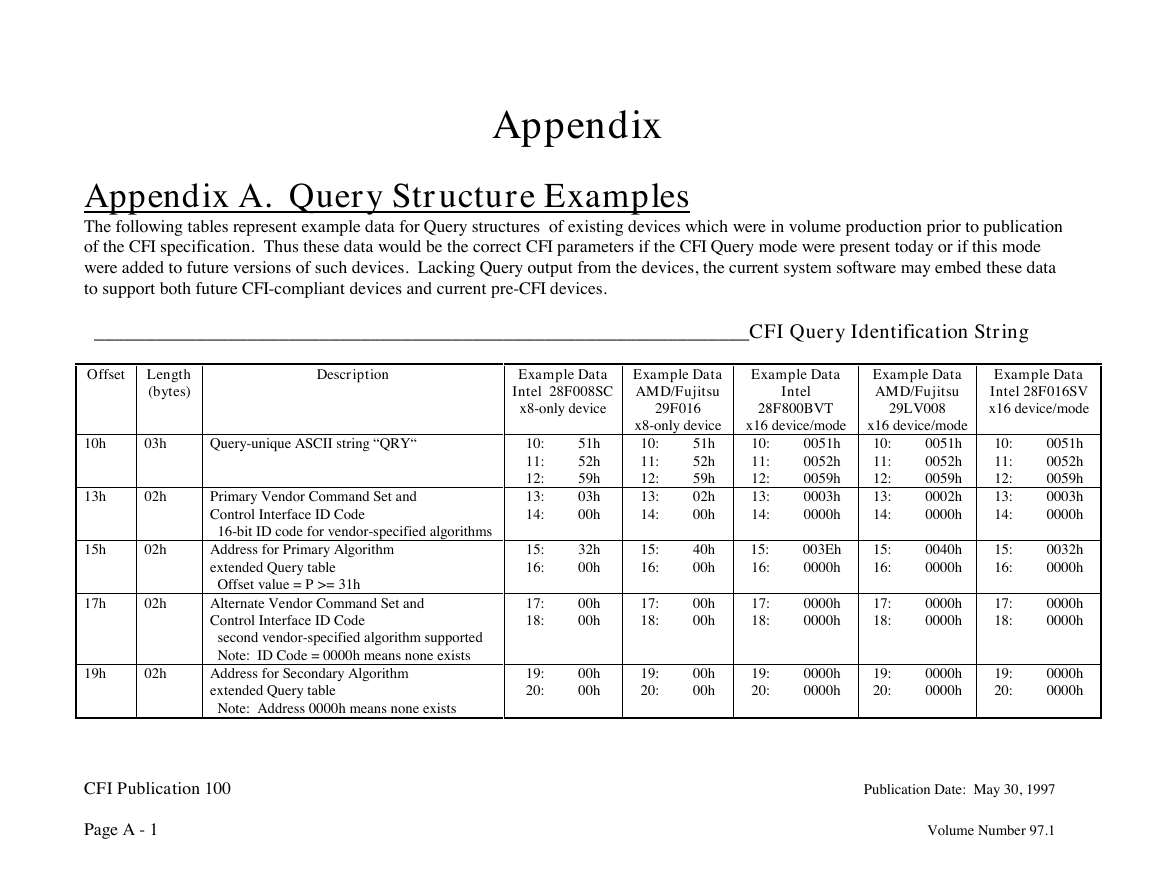

Appendix A. Query Structure Examples

The following tables represent example data for Query structures of existing devices which were in volume production prior to publication

of the CFI specification. Thus these data would be the correct CFI parameters if the CFI Query mode were present today or if this mode

were added to future versions of such devices. Lacking Query output from the devices, the current system software may embed these data

to support both future CFI-compliant devices and current pre-CFI devices.

________________________________________________________________CFI Query Identification String

Offset

Length

(bytes)

Description

10h

03h

Query-unique ASCII string “QRY“

13h

02h

15h

02h

17h

02h

19h

02h

Primary Vendor Command Set and

Control Interface ID Code

16-bit ID code for vendor-specified algorithms

Address for Primary Algorithm

extended Query table

Offset value = P >= 31h

Alternate Vendor Command Set and

Control Interface ID Code

second vendor-specified algorithm supported

Note: ID Code = 0000h means none exists

Address for Secondary Algorithm

extended Query table

Note: Address 0000h means none exists

Example Data

Intel 28F008SC

x8-only device

10:

11:

12:

13:

14:

15:

16:

17:

18:

19:

20:

51h

52h

59h

03h

00h

32h

00h

00h

00h

00h

00h

Example Data

AMD/Fujitsu

29F016

x8-only device

10:

51h

52h

11:

59h

12:

02h

13:

14:

00h

Example Data

Intel

28F800BVT

x16 device/mode

10:

0051h

0052h

11:

0059h

12:

0003h

13:

14:

0000h

Example Data

AMD/Fujitsu

29LV008

x16 device/mode

10:

0051h

0052h

11:

0059h

12:

0002h

13:

14:

0000h

15:

16:

17:

18:

19:

20:

40h

00h

00h

00h

00h

00h

15:

16:

17:

18:

19:

20:

003Eh

0000h

0000h

0000h

0000h

0000h

15:

16:

17:

18:

19:

20:

0040h

0000h

0000h

0000h

0000h

0000h

Example Data

Intel 28F016SV

x16 device/mode

10:

11:

12:

13:

14:

15:

16:

17:

18:

19:

20:

0051h

0052h

0059h

0003h

0000h

0032h

0000h

0000h

0000h

0000h

0000h

CFI Publication 100

Page A - 1

Publication Date: May 30, 1997

Volume Number 97.1

�

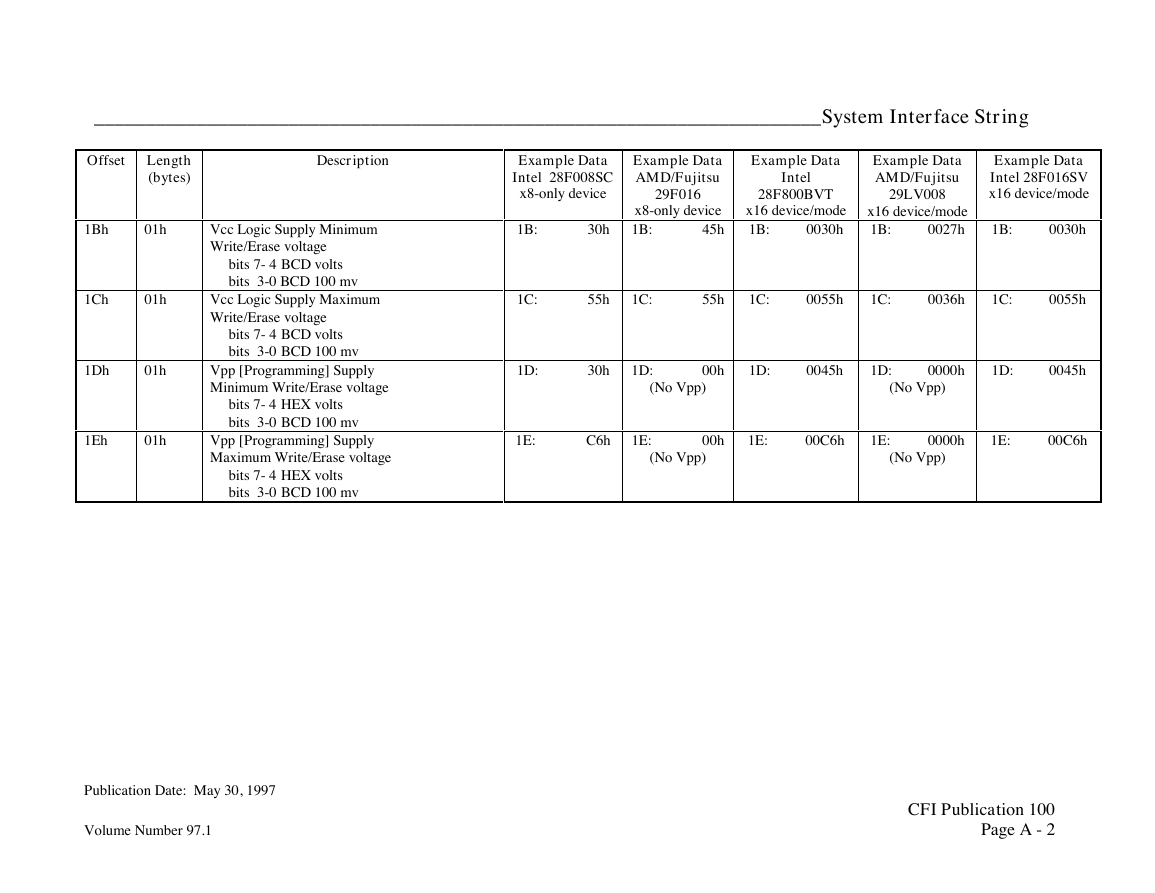

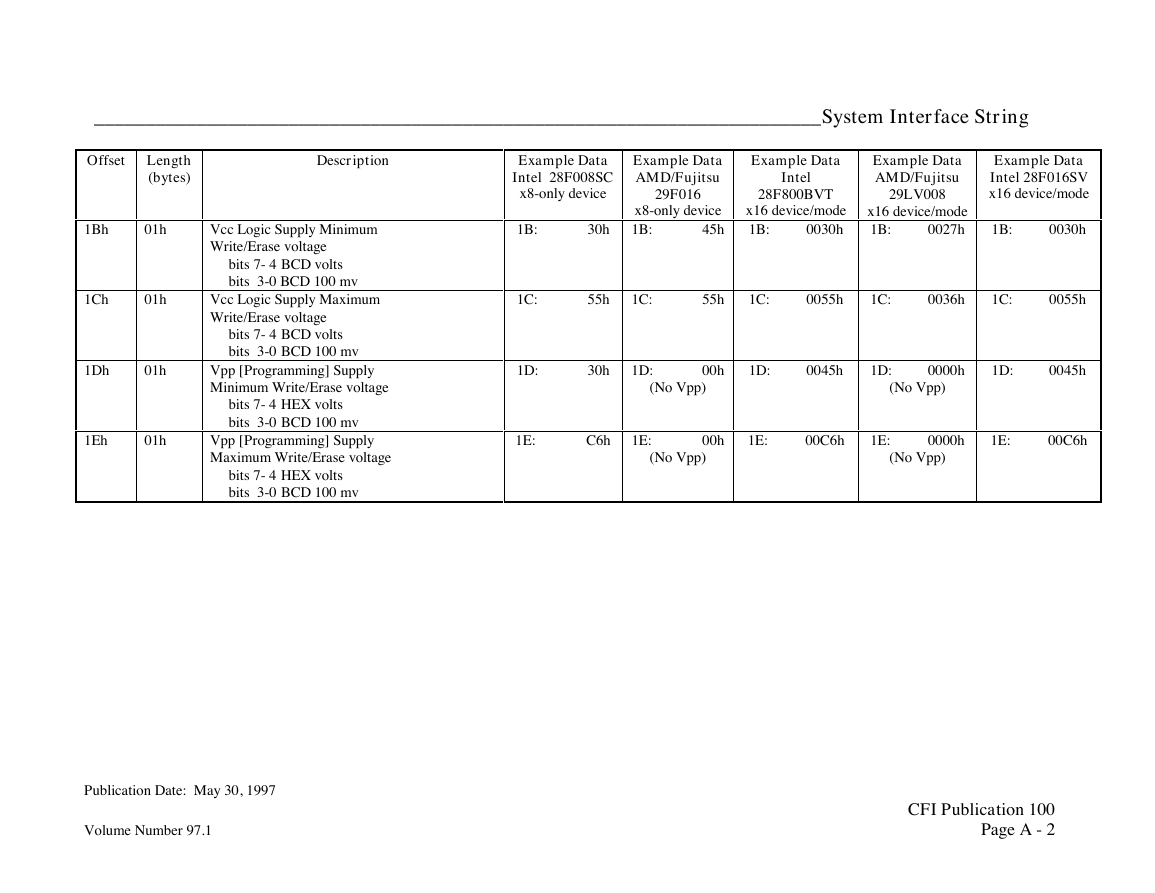

_______________________________________________________________________System Interface String

Offset

Length

(bytes)

1Bh

01h

1Ch

01h

1Dh

01h

1Eh

01h

Description

Vcc Logic Supply Minimum

Write/Erase voltage

bits 7- 4 BCD volts

bits 3-0 BCD 100 mv

Vcc Logic Supply Maximum

Write/Erase voltage

bits 7- 4 BCD volts

bits 3-0 BCD 100 mv

Vpp [Programming] Supply

Minimum Write/Erase voltage

bits 7- 4 HEX volts

bits 3-0 BCD 100 mv

Vpp [Programming] Supply

Maximum Write/Erase voltage

bits 7- 4 HEX volts

bits 3-0 BCD 100 mv

Example Data

Intel 28F008SC

x8-only device

1B:

30h

Example Data

AMD/Fujitsu

29F016

x8-only device

45h

1B:

Example Data

Intel

28F800BVT

x16 device/mode

0030h

1B:

Example Data

AMD/Fujitsu

29LV008

x16 device/mode

0027h

1B:

Example Data

Intel 28F016SV

x16 device/mode

1B:

0030h

1C:

55h

1C:

55h

1C:

0055h

1C:

0036h

1C:

0055h

1D:

30h

1D:

00h

1D:

0045h

1D:

0000h

1D:

0045h

(No Vpp)

(No Vpp)

1E:

C6h

1E:

00h

1E:

00C6h

1E:

0000h

1E:

00C6h

(No Vpp)

(No Vpp)

Publication Date: May 30, 1997

Volume Number 97.1

CFI Publication 100

Page A - 2

�

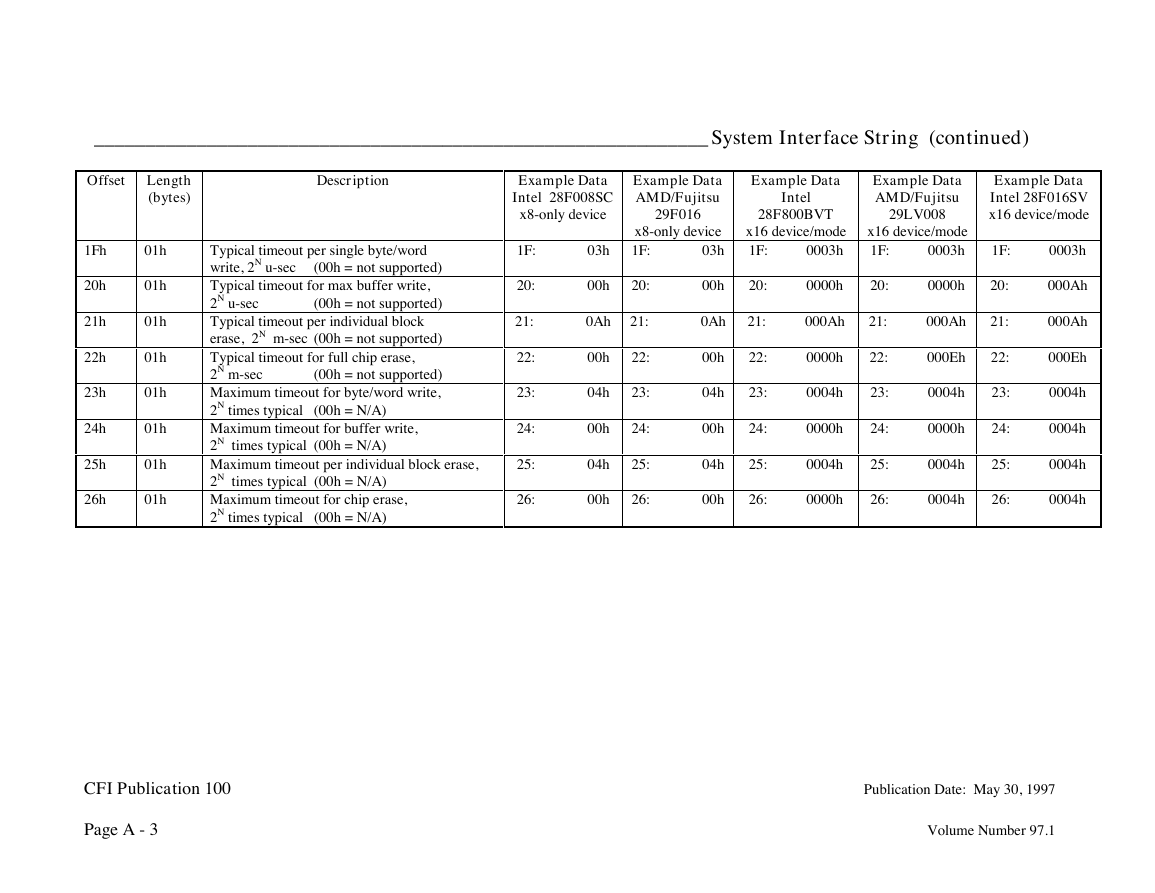

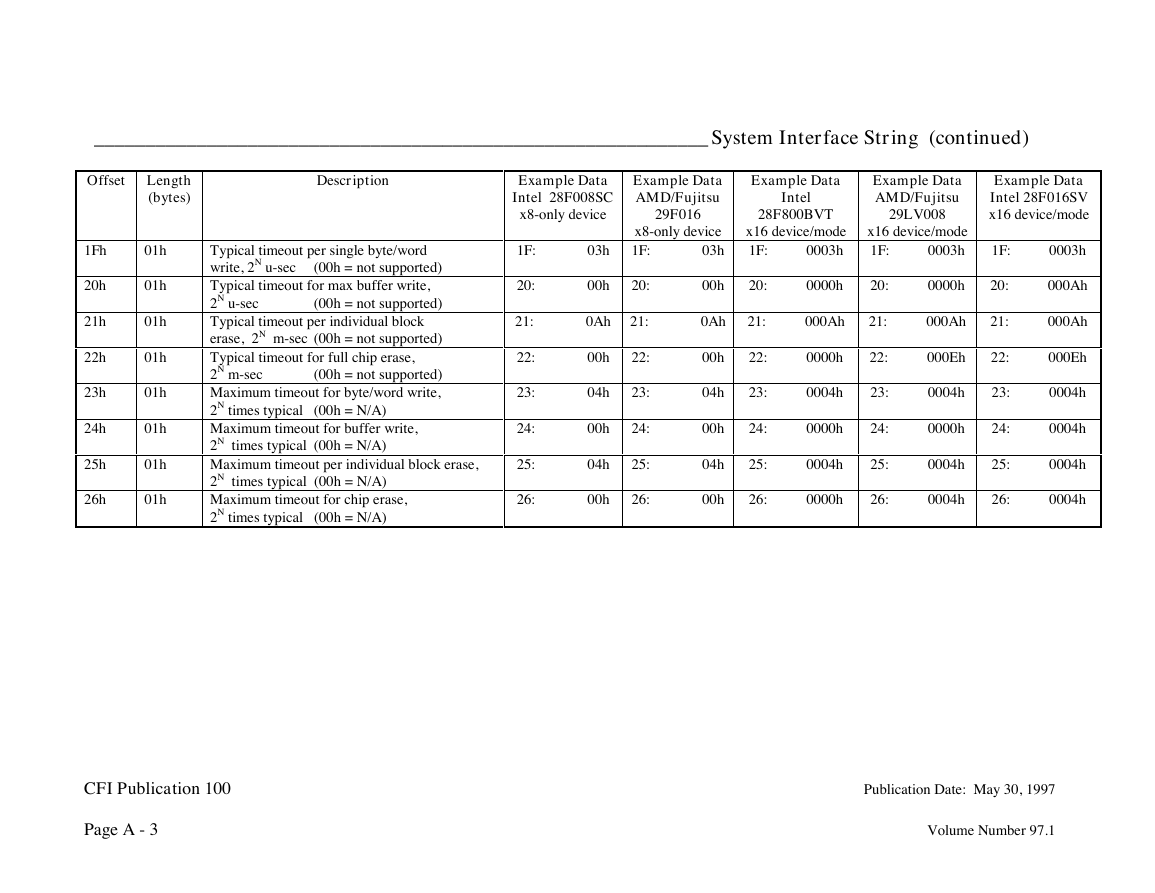

____________________________________________________________ System Interface String (continued)

Example Data

AMD/Fujitsu

29F016

x8-only device

1F:

03h

Example Data

Intel

28F800BVT

x16 device/mode

1F:

0003h

Example Data

AMD/Fujitsu

29LV008

x16 device/mode

1F:

0003h

03h

00h

20:

00h

20:

0000h

20:

0000h

0Ah

21:

0Ah

21:

000Ah

21:

000Ah

Example Data

Intel 28F016SV

x16 device/mode

1F:

20:

21:

0003h

000Ah

000Ah

Offset

Length

(bytes)

Description

Example Data

Intel 28F008SC

x8-only device

1Fh

20h

21h

22h

23h

24h

25h

26h

01h

01h

01h

01h

01h

01h

01h

01h

(00h = not supported)

(00h = not supported)

Typical timeout per single byte/word

write, 2N u-sec

Typical timeout for max buffer write,

2N u-sec

Typical timeout per individual block

erase, 2N m-sec (00h = not supported)

Typical timeout for full chip erase,

2N m-sec

(00h = not supported)

Maximum timeout for byte/word write,

2N times typical

Maximum timeout for buffer write,

2N times typical (00h = N/A)

Maximum timeout per individual block erase,

2N times typical (00h = N/A)

Maximum timeout for chip erase,

2N times typical (00h = N/A)

(00h = N/A)

1F:

20:

21:

22:

23:

24:

25:

26:

00h

22:

04h

23:

00h

24:

04h

25:

00h

26:

00h

04h

00h

04h

00h

22:

23:

24:

25:

26:

0000h

22:

000Eh

22:

000Eh

0004h

0000h

0004h

0000h

23:

24:

25:

26:

0004h

0000h

0004h

0004h

23:

24:

25:

26:

0004h

0004h

0004h

0004h

CFI Publication 100

Page A - 3

Publication Date: May 30, 1997

Volume Number 97.1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc