Altium Designer 中进行信号完整性分析教程

By kms 2012

在高速数字系统中,由于脉冲上升/下降时间通常在 10 到几百 p 秒,当受到诸如

内连、传输时延和电源噪声等因素的影响,从而造成脉冲信号失真的现象;

在自然界中,存在着各种各样频率的微波和电磁干扰源,可能由于很小的差异导

致高速系统设计的失败; 在电子产品向高密和高速电路设计方向发展的今天,

解决一系列信号完整性的问题,成为当前每一个电子设计者所必须面对的问题。

业界通常会采用在 PCB 制板前 期,通过信号完整性分析工具尽可能将设计风险

降到最低,从而也大大促进了 EDA 设计工具的发展……

信号完整性(Signal Integrity,简称 SI)问题是指高速数字电路中,脉冲形

状畸变而引发的信号失真问题,通常由传输线不阻抗匹配产生的问题。而影响阻

抗匹配的因素包 括信号源的架构、输出阻抗(output impedance)、走线的特性

阻抗、负载端的特性、走线的拓朴(topology)架构等。解决的方式可以采用端接

(termination)与调整 走线拓朴的策略。

信号完整性问题通常不是由某个单一 因素导致的,而是板级设计中多种因素共

同作用的结果。信号完整性问题主要表现形式包括信号反射、信号振铃、地弹、

串扰等;

1,Altium Designer 信号完整性分析(机理、模型、功能)

在 Altium Designer 设计环境下,您既可以在原理图又可以在 PCB 编辑器内实现

信号完整性分析,并且能以波形的方式在图形界面下给出反射和串扰的分析结果。

Altium Designer 的信号完整性分析采用 IC 器件的 IBIS 模型,通过对版图内信

号线路的阻抗计算,得到信号响应和失真等仿真数据来检查设计信号的可靠性。

Altium Designer 的信号完整性分析工具可以支持包括差分对信号在内的高速电

路信号完整性分析功能。

Altium Designer 仿真参数通过一个简单直观的对话框进行配置,通过使用集成

的波形观察仪,实现图形显示仿真结果,而且波形观察仪可以同时显示多个仿真

数据图像。并且可以直接在标绘的波形上进行测量,输出结果数据还可供进一步

分析之用。

Altium Designer 提供的集成器件库包含了大量的的器件 IBIS 模型,用户可以

对器件添加器件的 IBIS 模型,也可以从外部导入与器件相关联的 IBIS 模型,选

择从器件厂商那里得到的 IBIS 模型。

Altium Designer 的 SI 功能包含了布线前(即原理图设计阶段)及布线后(PCB

版图设计阶段)两部分 SI 分析功能;采用成熟的传输线计算方法,以及 I/O 缓

冲宏模型进行仿真。基于快速反射和串扰模型,信号完整性分析器使用完全可靠

的算法,从而能够产生出准确的仿真结果。布线前的阻抗特征计算和信号反射的

信 号完整性分析,用户可以在原理图环境下运行 SI 仿真功能,对电路潜在的信

号完整性问题进行分析,如阻抗不匹配等因素。

更全面的信号完整性分析是在布线后 PCB 版图上完成的,它不仅能对传输线阻抗、

信号反射和信号间串扰等多种设计中存在的信号完整性问题以图形的方式进行

�

分 析,而且还能利用规则检查发现信号完整性问题,同时,Altium Designer

还提供一些有效的终端选项,来帮助您选择最好的解决方案。

2,分析设置需求

在 PCB 编辑环境下进行信号完整性分析。

为了得到精确的结果,在运行信号完整性分析之前需要完成以下步骤:

1、电路中需要至少一块集成电路,因为集成电路的管脚可以作为激励源

输出到被分析的网络上。像电阻、电容、电感等被动元件,如果没有源的

驱动,是无法给出仿真结果的。

2、针对每个元件的信号完整性模型必须正确。

3、在规则中必须设定电源网络和地网络,具体操作见本文。

4、设定激励源。

5、用于 PCB 的层堆栈必须设置正确,电源平面必须连续,分割电源平面

将无法得到正确分析结果,另外,要正确设置所有层的厚度。

3,操作流程

a .布线前(即原理图设计阶段)SI 分析概述

用户如需对项目原理图设计进行 SI 仿真分析, Altium Designer 要求必须建立

一个工程项目名称。在原理图 SI 分析中,系统将采用在 SI Setup Option 对话

框设置的传输线平均线长和特征阻抗值;仿真器也将直接采用规则设置中信号完

整性规则约束,如激励源和供电网络等,同时,允许用户直接在原 理图编辑环

境下放置 PCB Layout 图标,直接对原理图内网络定义规则约束。

当建立了必要的仿真模型后,在原理图编辑环境的菜单中选择 Tools -> Signal

Integrity 命令,运行仿真。

b .布线后(即 PCB 版图设计阶段)SI 分析概述

用户如需对项目 PCB 版图设计进行 SI 仿真分析, Altium Designer 要求必须在

项目工程中建立相关的原理图设计。此时,当用户在任何一个原理图文档下运行

SI 分析功能将与 PCB 版图设计下允许 SI 分析功能得到相同的结果。

当建立了必要的仿真模型后,在 PCB 编辑环境的菜单中选择 Tools -> Signal

Integrity 命令,运行仿真。

4,操作实例:

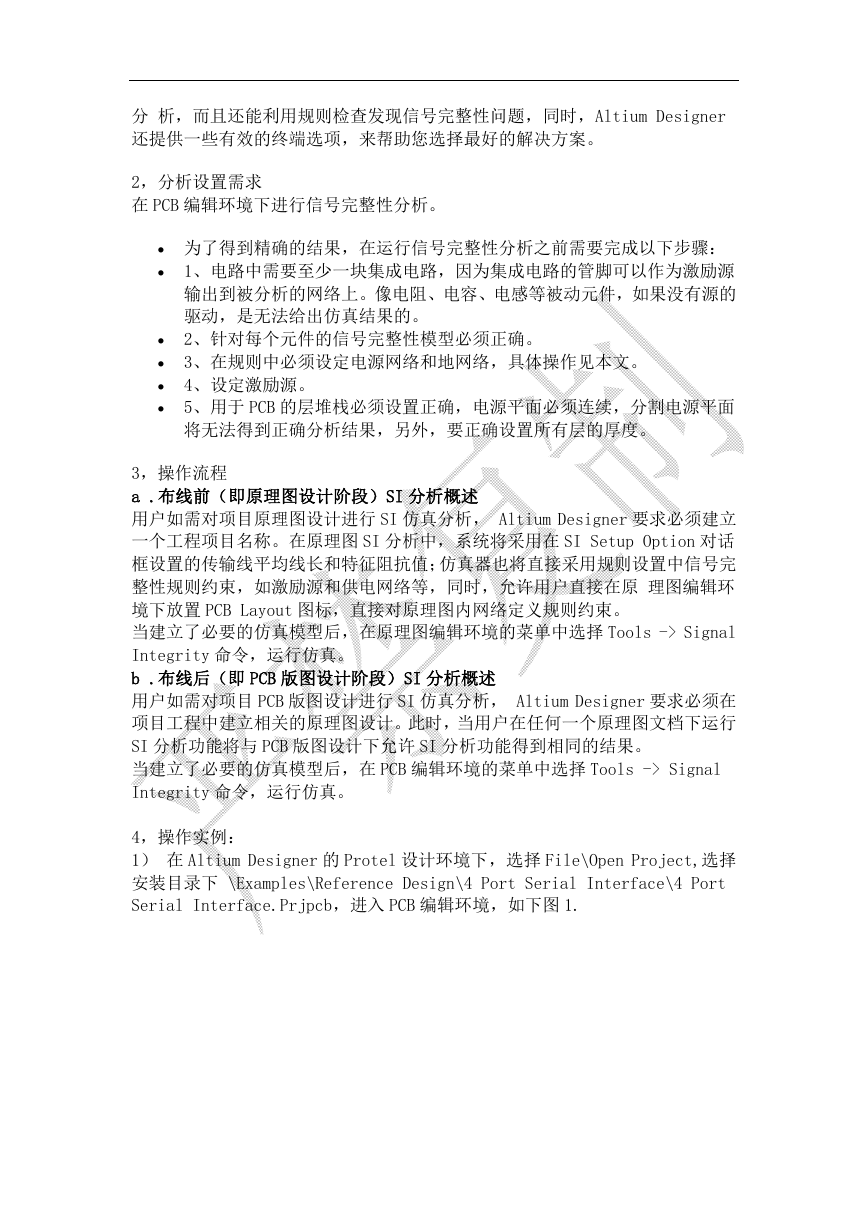

1) 在 Altium Designer 的 Protel 设计环境下,选择 File\Open Project,选择

安装目录下 \Examples\Reference Design\4 Port Serial Interface\4 Port

Serial Interface.Prjpcb,进入 PCB 编辑环境,如下图 1.

�

图 1 在 PCB 文件中进行 SI 分析

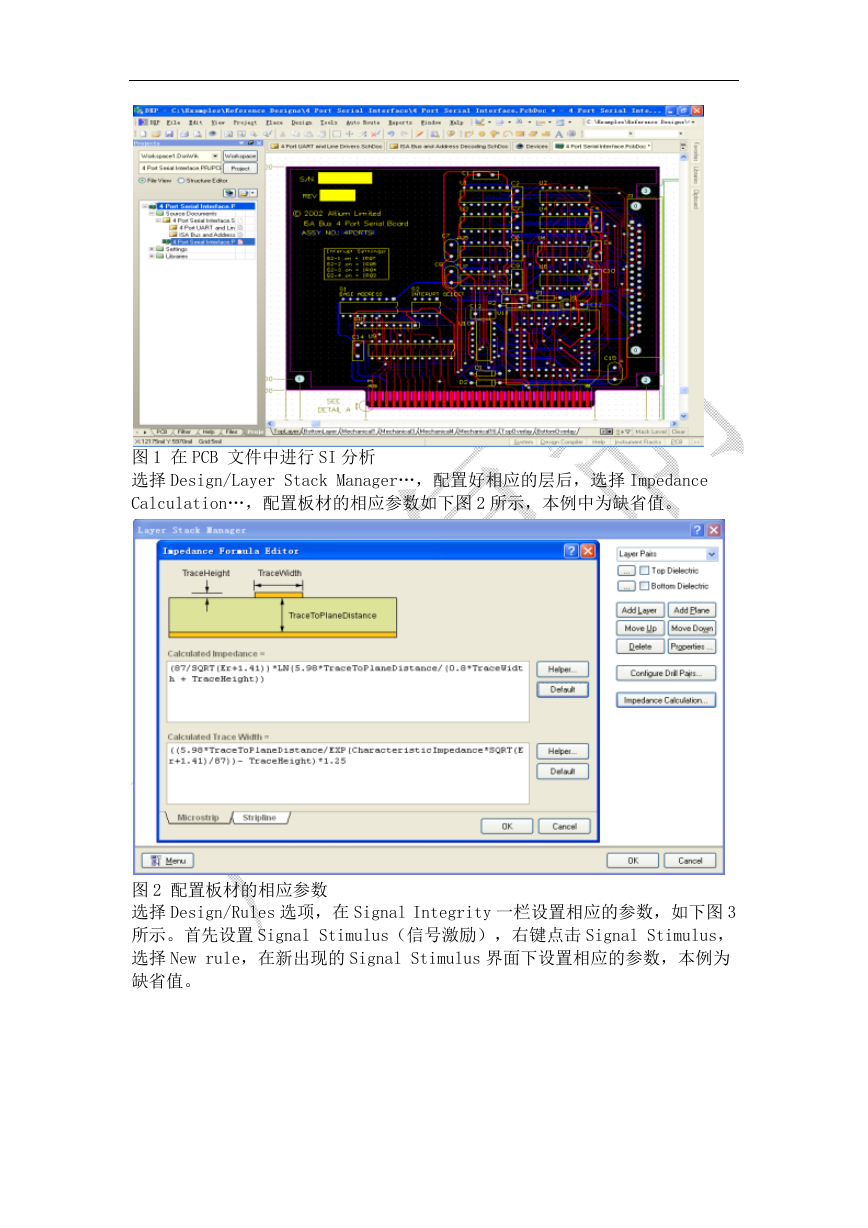

选择 Design/Layer Stack Manager…,配置好相应的层后,选择 Impedance

Calculation…,配置板材的相应参数如下图 2 所示,本例中为缺省值。

图 2 配置板材的相应参数

选择 Design/Rules 选项,在 Signal Integrity 一栏设置相应的参数,如下图 3

所示。首先设置 Signal Stimulus(信号激励),右键点击 Signal Stimulus,

选择 New rule,在新出现的 Signal Stimulus 界面下设置相应的参数,本例为

缺省值。

�

图 3 设置信号激励*

接下来设置电源和地网络,右键点击 Supply Net,选择 New Rule,在新出现的

Supplynets 界面下,将 GND 网络的 Voltage 设置为 0 如图 4 所示,按相同方法

再添加 Rule,将 VCC 网络的 Voltage 设置为 5。其余的参数按实际需要进行设

置。最后点击 OK 推出。

图 4 设置电源和地网络*

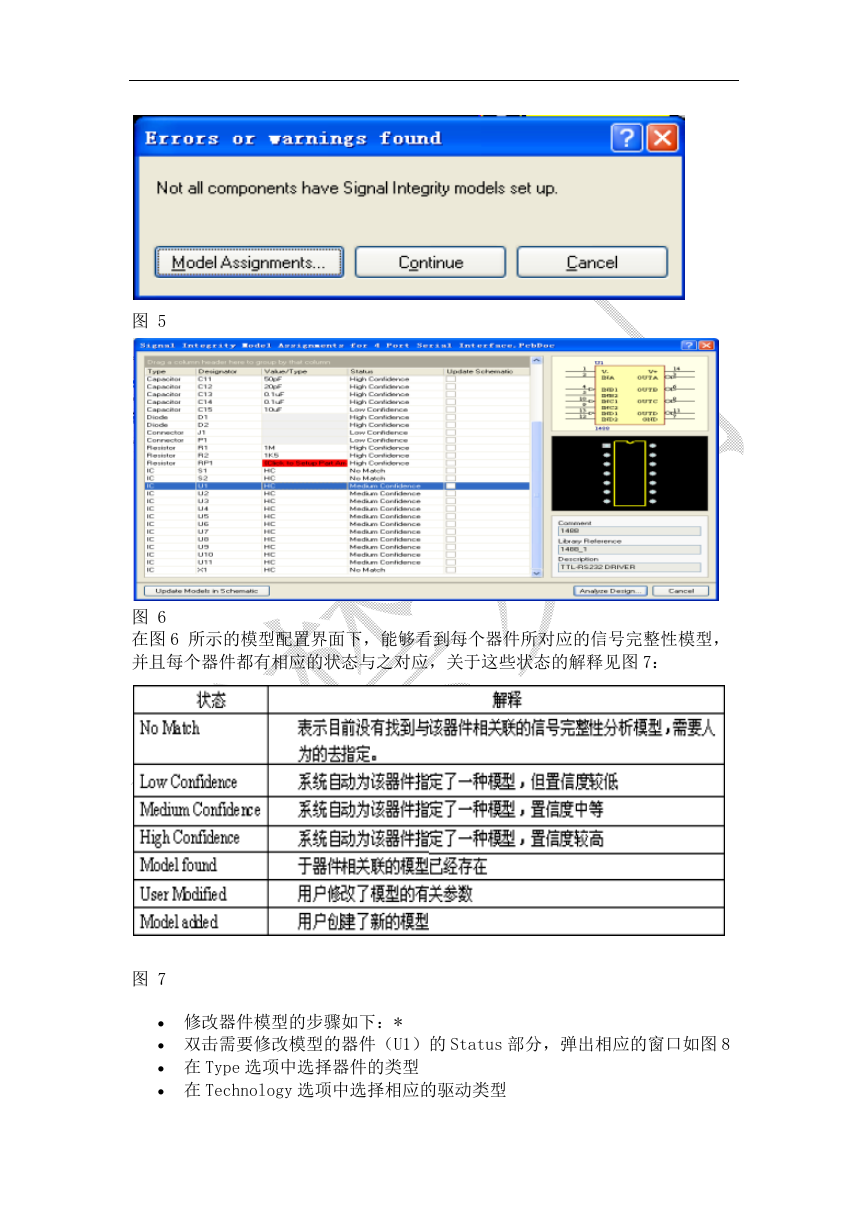

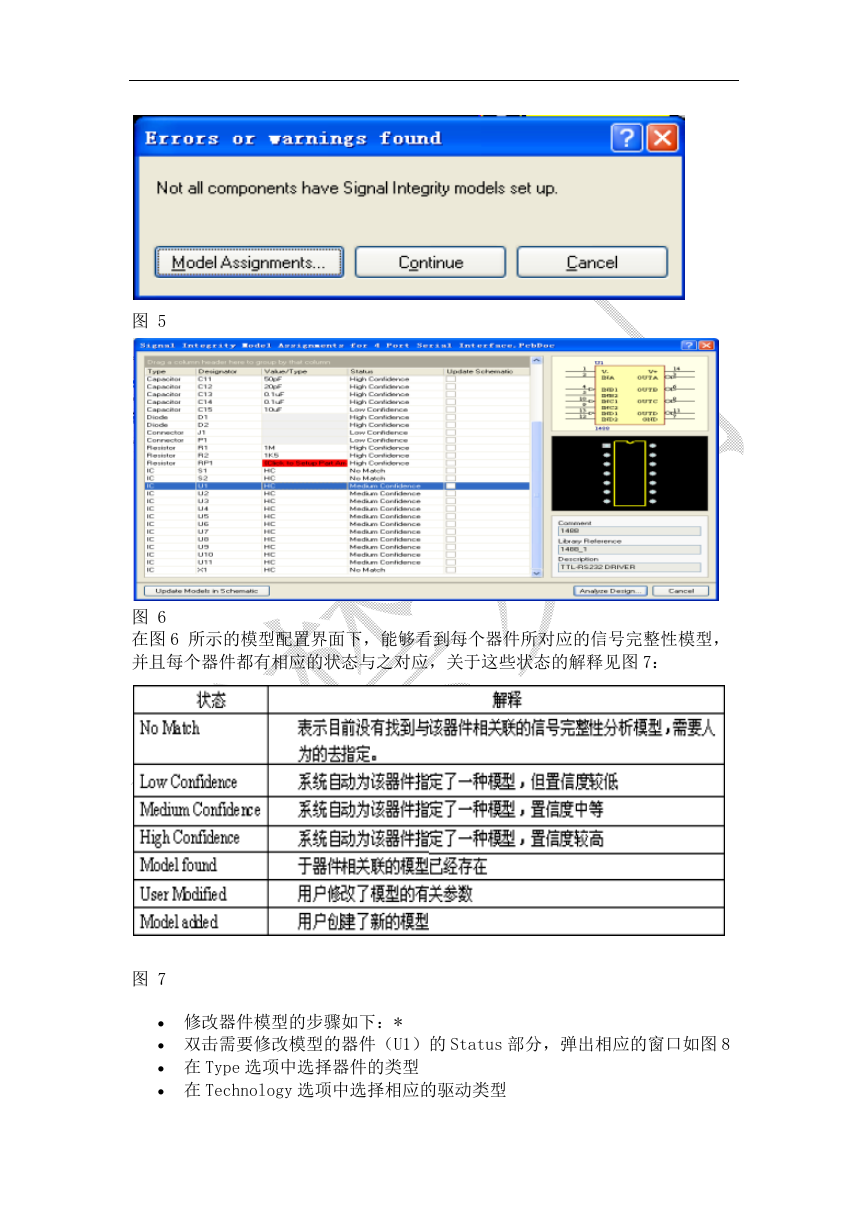

选择 Tools\Signal Integrity…,在弹出的窗口中(图 5)选择 Model

Assignments…,就会进入模型配置的界面(图 6)。

�

图 5

图 6

在图 6 所示的模型配置界面下,能够看到每个器件所对应的信号完整性模型,

并且每个器件都有相应的状态与之对应,关于这些状态的解释见图 7:

图 7

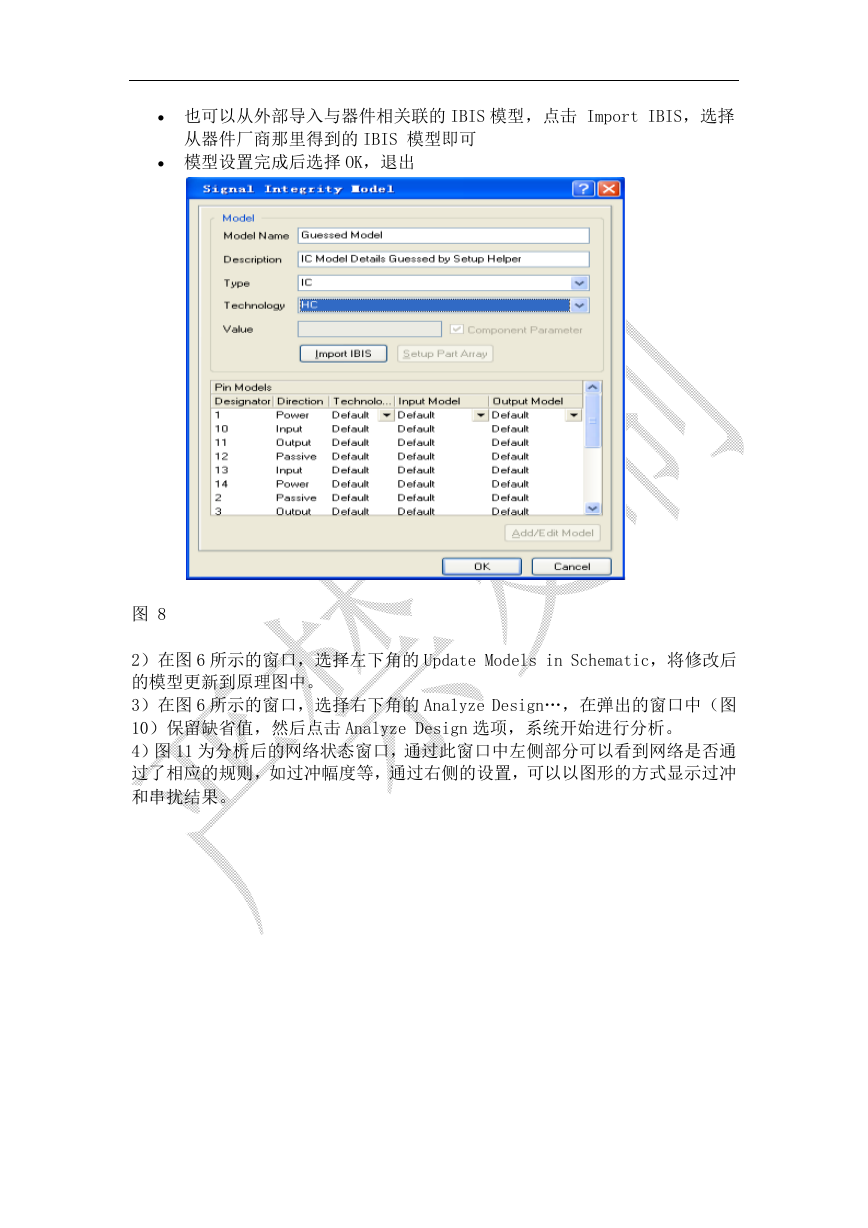

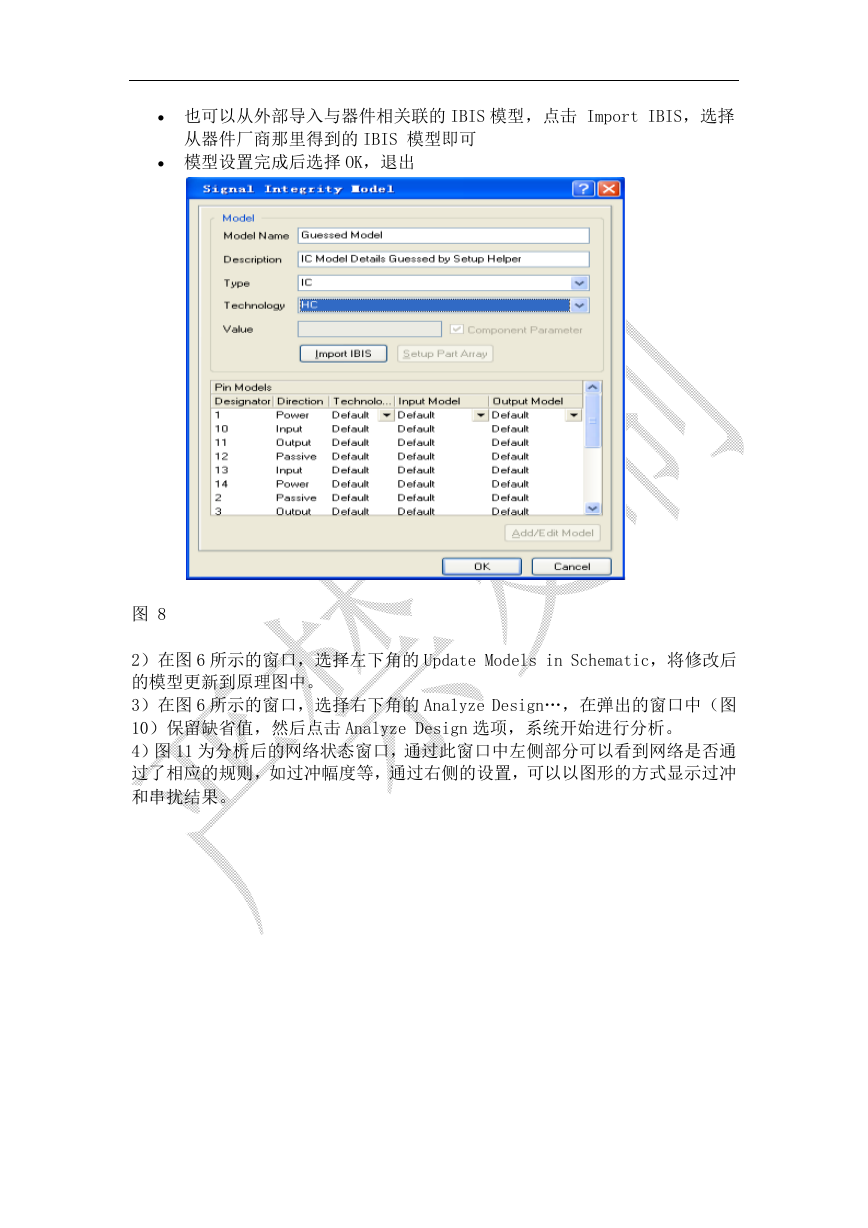

修改器件模型的步骤如下:*

双击需要修改模型的器件(U1)的 Status 部分,弹出相应的窗口如图 8

在 Type 选项中选择器件的类型

在 Technology 选项中选择相应的驱动类型

�

也可以从外部导入与器件相关联的 IBIS 模型,点击 Import IBIS,选择

从器件厂商那里得到的 IBIS 模型即可

模型设置完成后选择 OK,退出

图 8

2)在图 6 所示的窗口,选择左下角的 Update Models in Schematic,将修改后

的模型更新到原理图中。

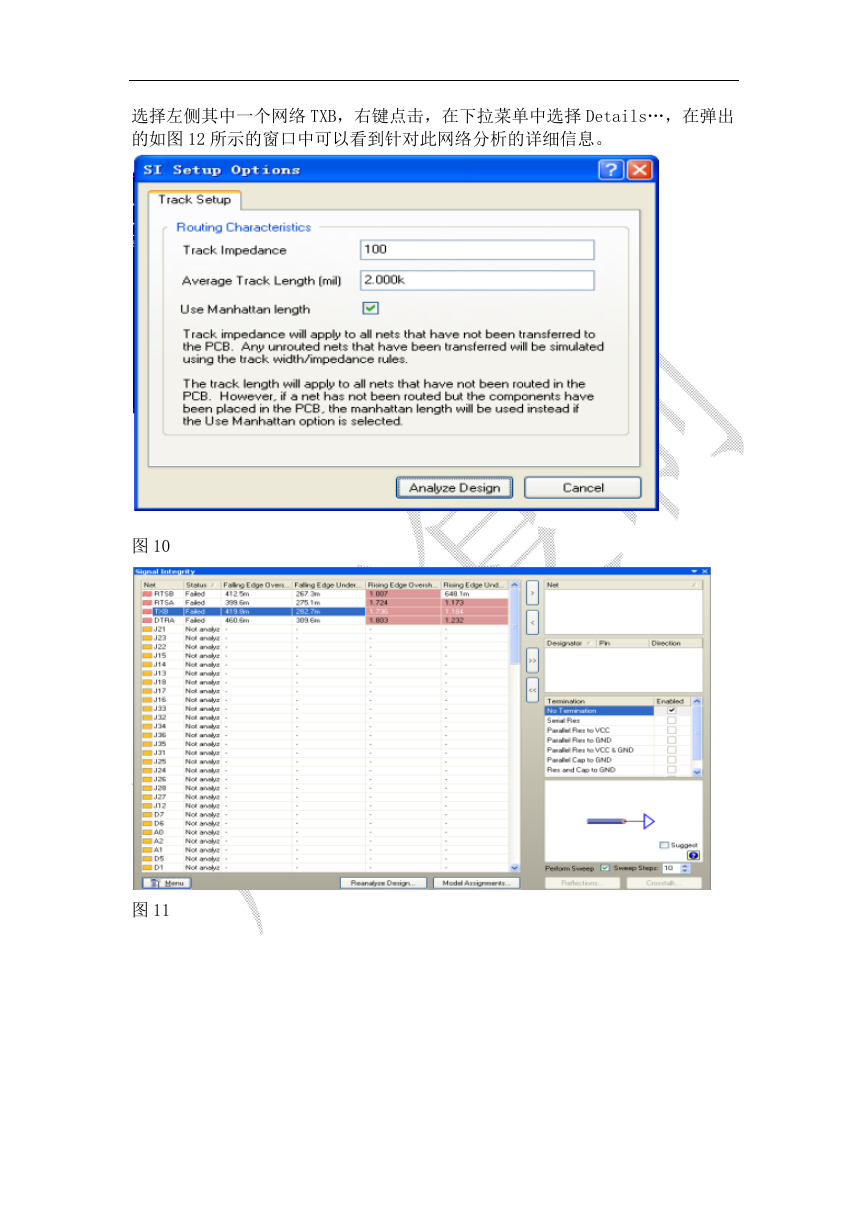

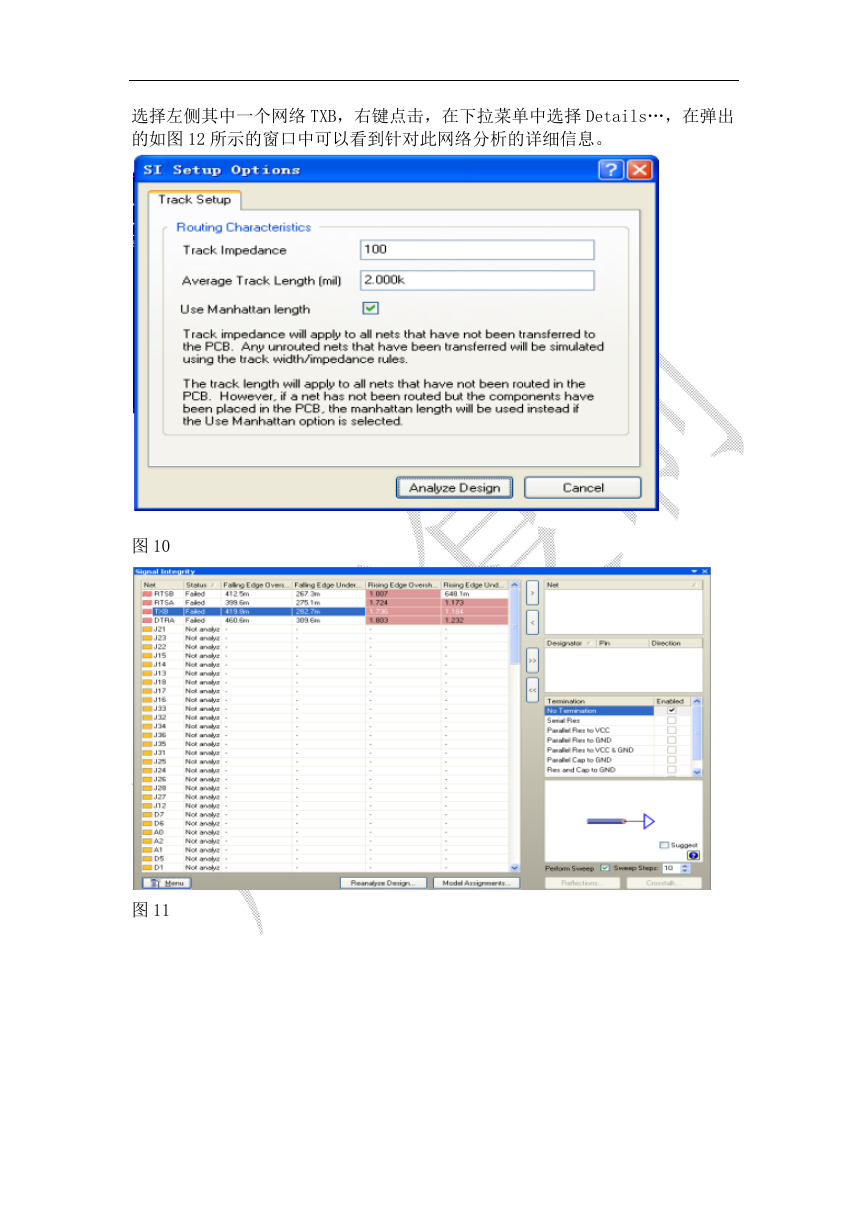

3)在图 6 所示的窗口,选择右下角的 Analyze Design…,在弹出的窗口中(图

10)保留缺省值,然后点击 Analyze Design 选项,系统开始进行分析。

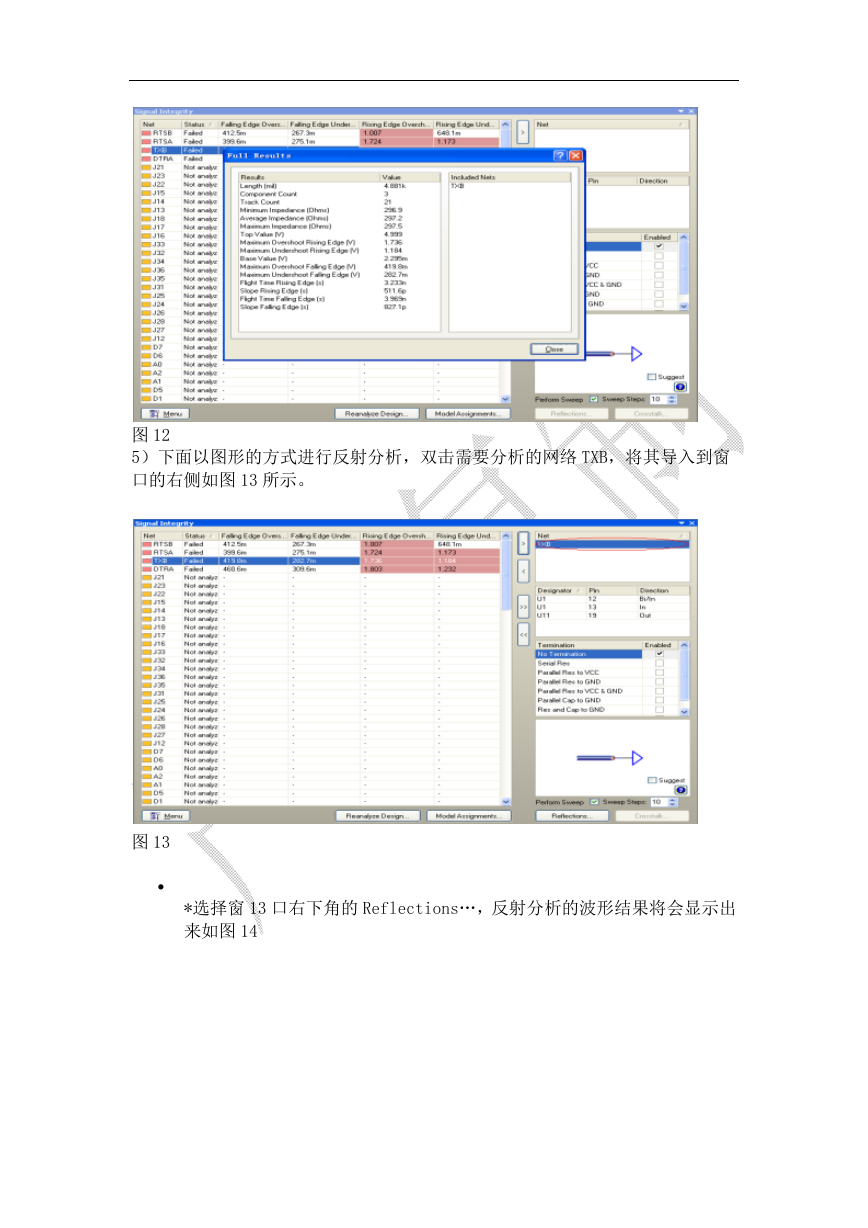

4)图 11 为分析后的网络状态窗口,通过此窗口中左侧部分可以看到网络是否通

过了相应的规则,如过冲幅度等,通过右侧的设置,可以以图形的方式显示过冲

和串扰结果。

�

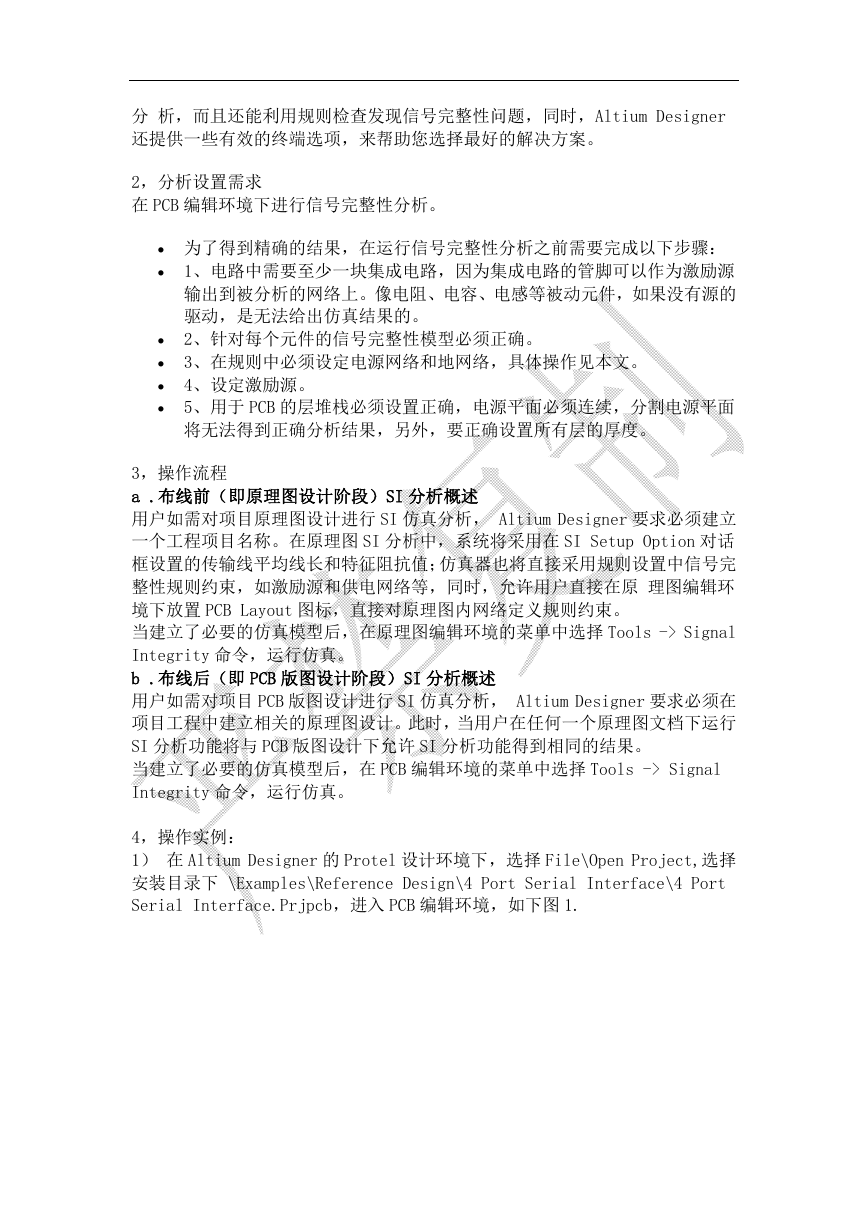

选择左侧其中一个网络 TXB,右键点击,在下拉菜单中选择 Details…,在弹出

的如图 12 所示的窗口中可以看到针对此网络分析的详细信息。

图 10

图 11

�

图 12

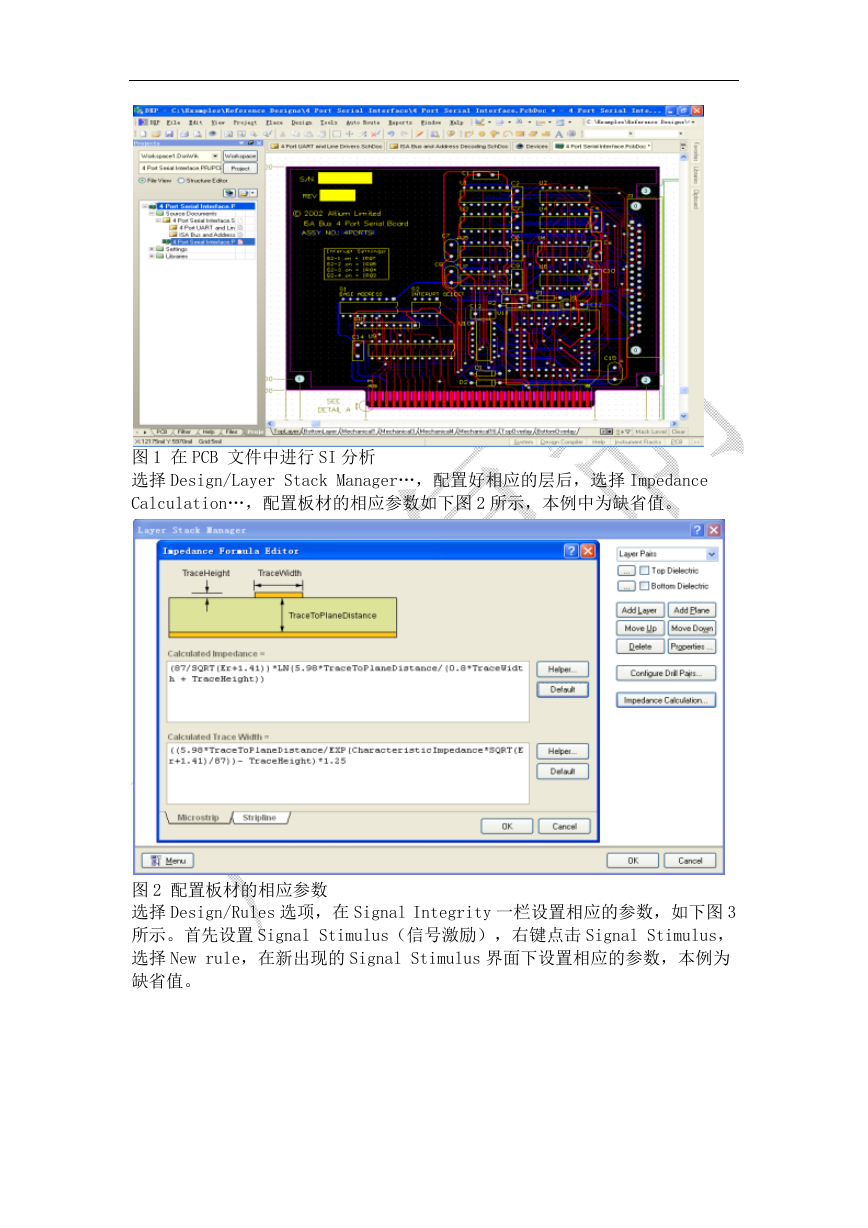

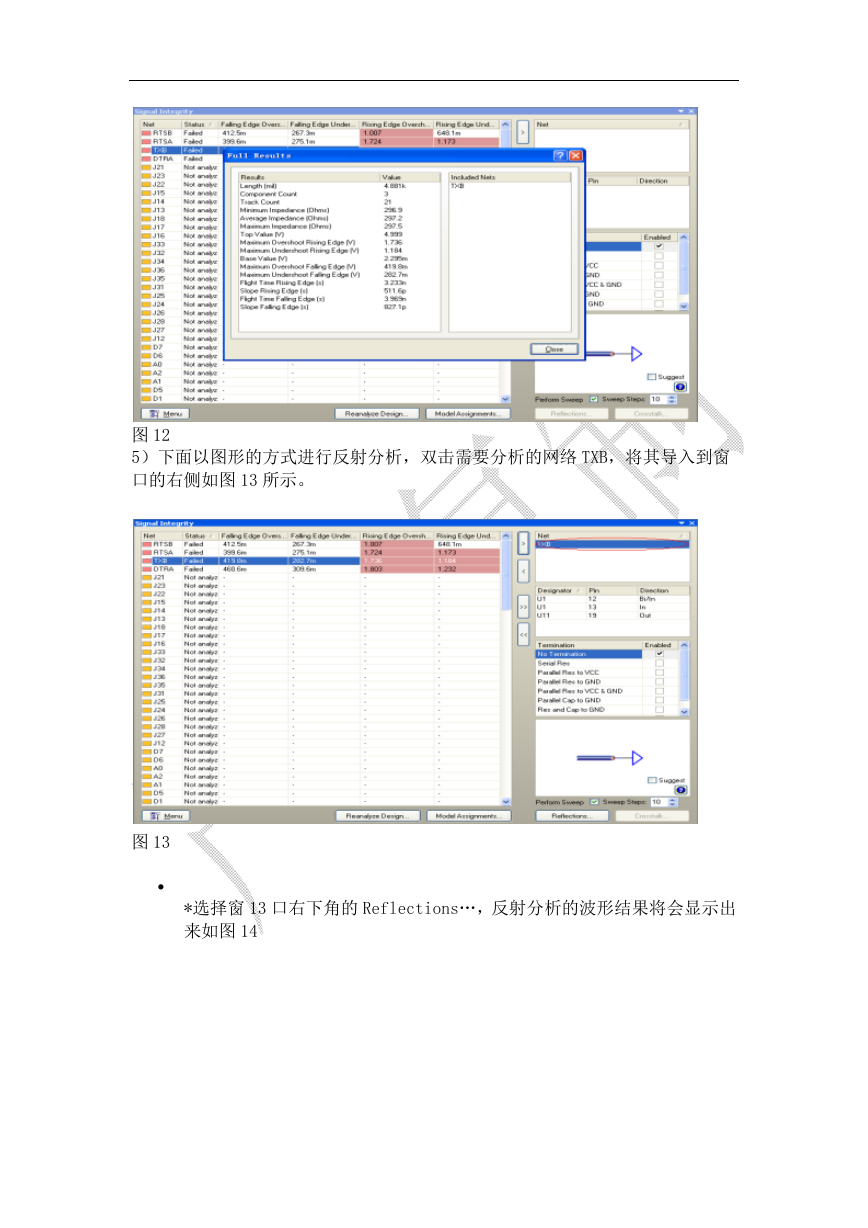

5)下面以图形的方式进行反射分析,双击需要分析的网络 TXB,将其导入到窗

口的右侧如图 13 所示。

图 13

*选择窗 13 口右下角的 Reflections…,反射分析的波形结果将会显示出

来如图 14

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc