Calibre xRC 的使用

1.版图中的寄生参数

在使用 Calibre xRC 提取寄生参数之前,先介绍一下电路中的寄生参数。一般来讲,寄

生参数有寄生电阻、寄生电容、寄生电感等,其中寄生电阻和寄生电容对电路的影响最为明

显。

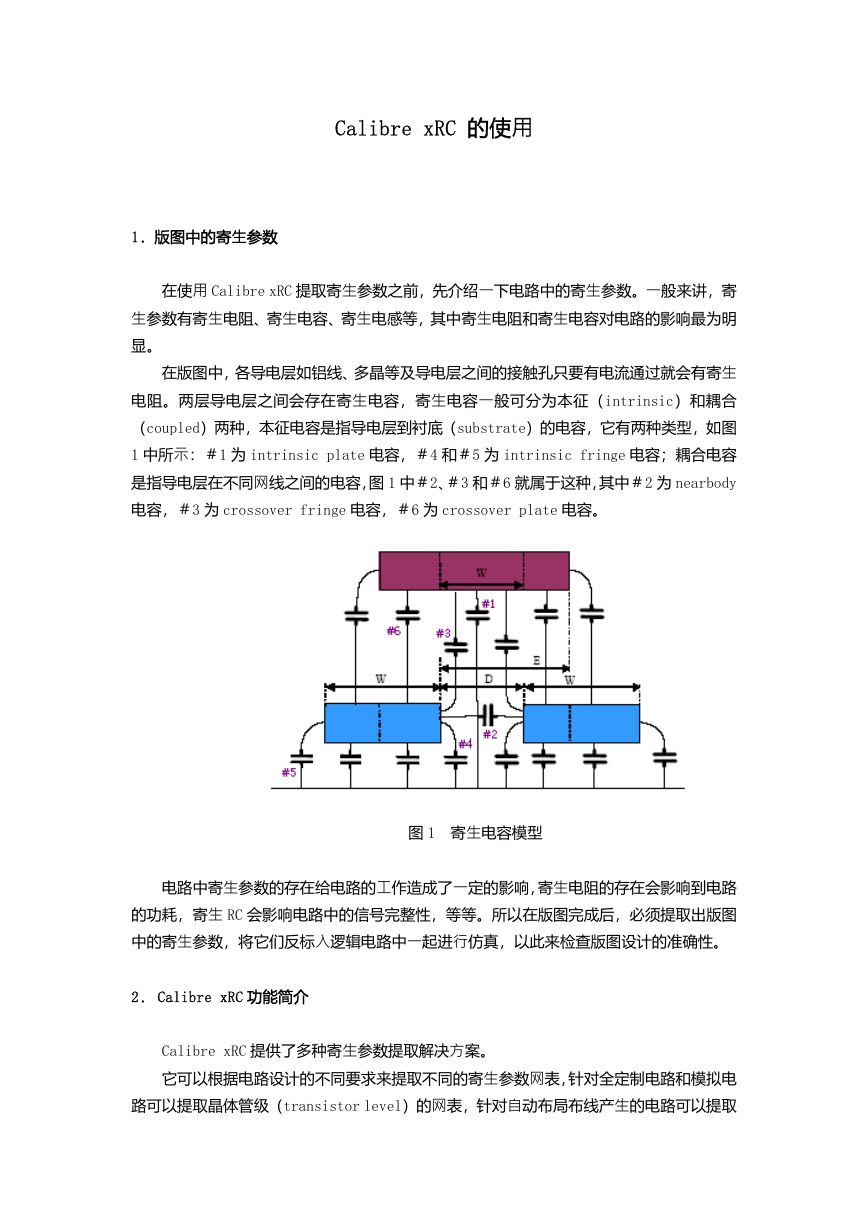

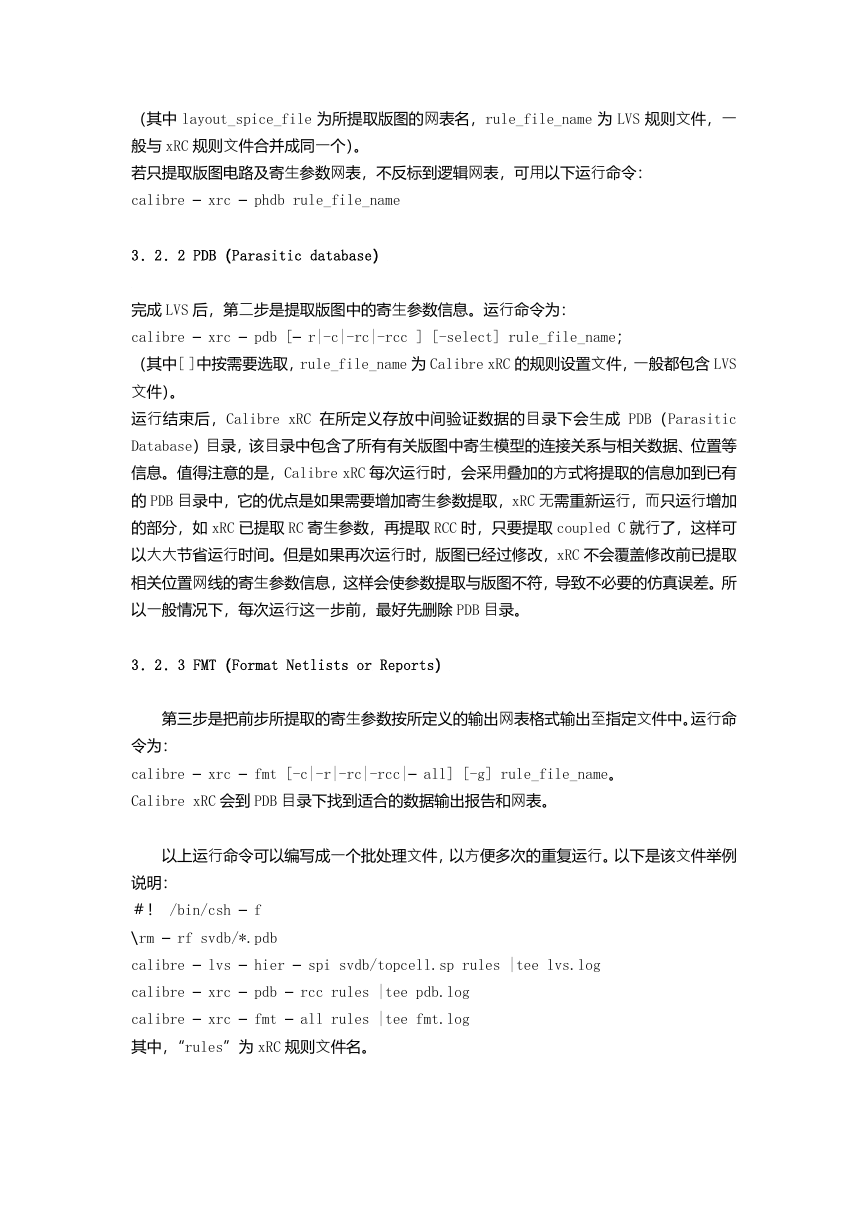

在版图中,各导电层如铝线、多晶等及导电层之间的接触孔只要有电流通过就会有寄生

电阻。两层导电层之间会存在寄生电容,寄生电容一般可分为本征(intrinsic)和耦合

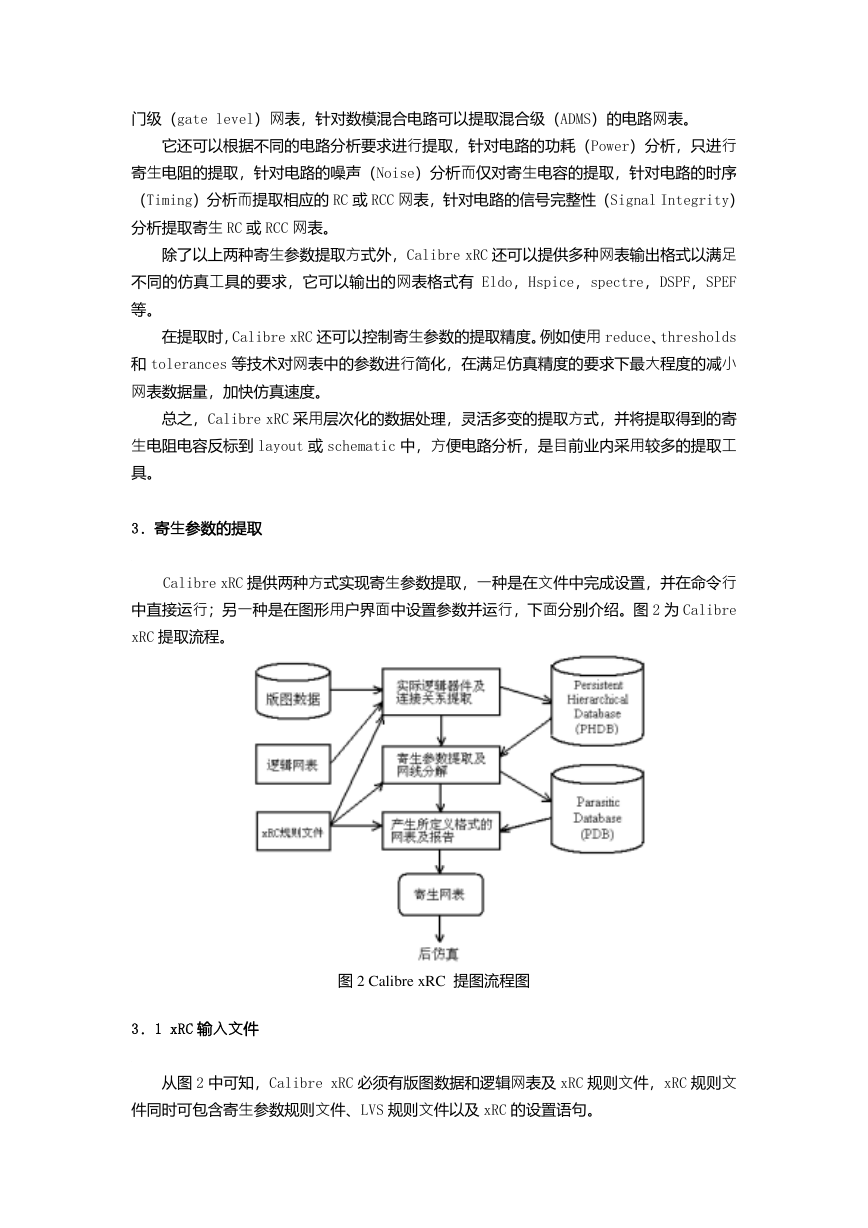

(coupled)两种,本征电容是指导电层到衬底(substrate)的电容,它有两种类型,如图

1 中所示:#1 为 intrinsic plate 电容,#4 和#5 为 intrinsic fringe 电容;耦合电容

是指导电层在不同网线之间的电容,图 1 中#2、#3 和#6 就属于这种,其中#2 为 nearbody

电容,#3 为 crossover fringe 电容,#6 为 crossover plate 电容。

图 1 寄生电容模型

电路中寄生参数的存在给电路的工作造成了一定的影响,寄生电阻的存在会影响到电路

的功耗,寄生 RC 会影响电路中的信号完整性,等等。所以在版图完成后,必须提取出版图

中的寄生参数,将它们反标入逻辑电路中一起进行仿真,以此来检查版图设计的准确性。

2. Calibre xRC 功能简介

Calibre xRC 提供了多种寄生参数提取解决方案。

它可以根据电路设计的不同要求来提取不同的寄生参数网表,针对全定制电路和模拟电

路可以提取晶体管级(transistor level)的网表,针对自动布局布线产生的电路可以提取

�

门级(gate level)网表,针对数模混合电路可以提取混合级(ADMS)的电路网表。

它还可以根据不同的电路分析要求进行提取,针对电路的功耗(Power)分析,只进行

寄生电阻的提取,针对电路的噪声(Noise)分析而仅对寄生电容的提取,针对电路的时序

(Timing)分析而提取相应的 RC 或 RCC 网表,针对电路的信号完整性(Signal Integrity)

分析提取寄生 RC 或 RCC 网表。

除了以上两种寄生参数提取方式外,Calibre xRC 还可以提供多种网表输出格式以满足

不同的仿真工具的要求,它可以输出的网表格式有 Eldo,Hspice,spectre,DSPF,SPEF

等。

在提取时,Calibre xRC 还可以控制寄生参数的提取精度。例如使用 reduce、thresholds

和 tolerances 等技术对网表中的参数进行简化,在满足仿真精度的要求下最大程度的减小

网表数据量,加快仿真速度。

总之,Calibre xRC 采用层次化的数据处理,灵活多变的提取方式,并将提取得到的寄

生电阻电容反标到 layout 或 schematic 中,方便电路分析,是目前业内采用较多的提取工

具。

3.寄生参数的提取

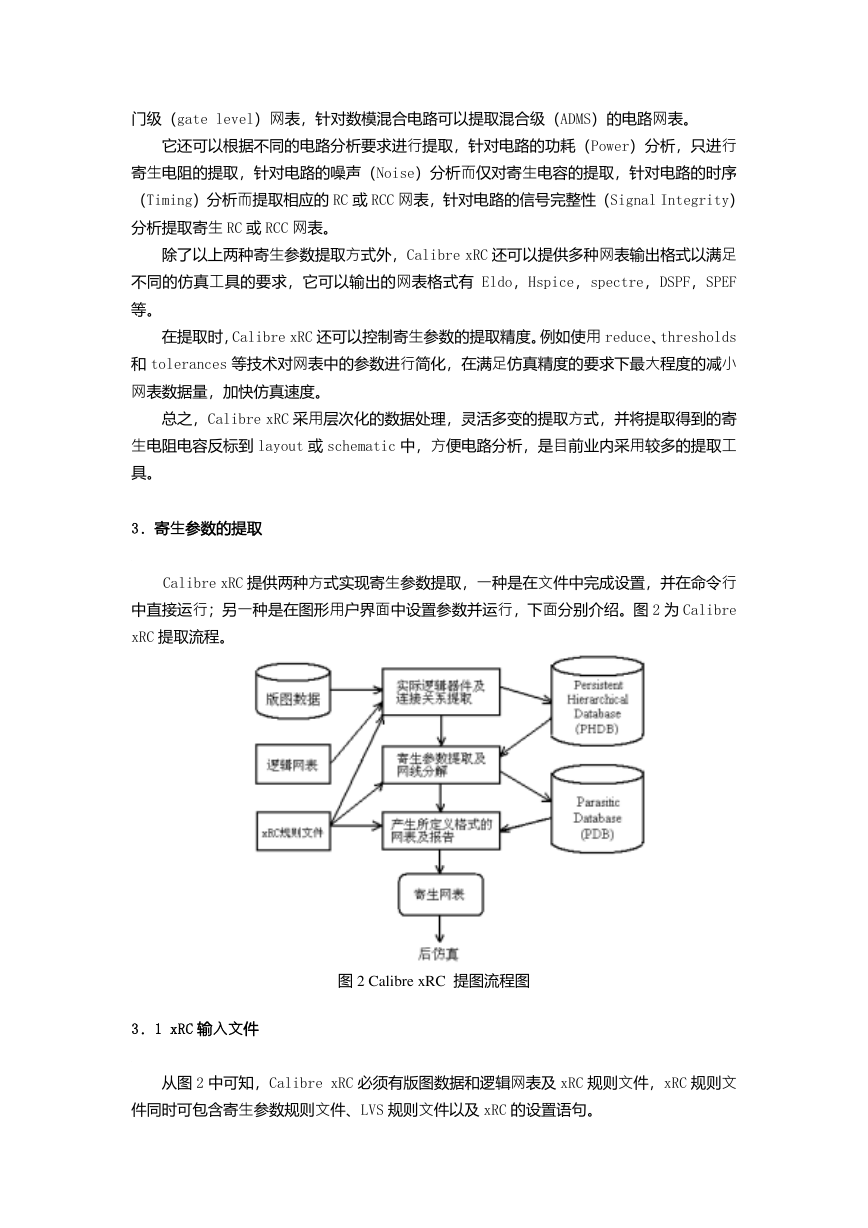

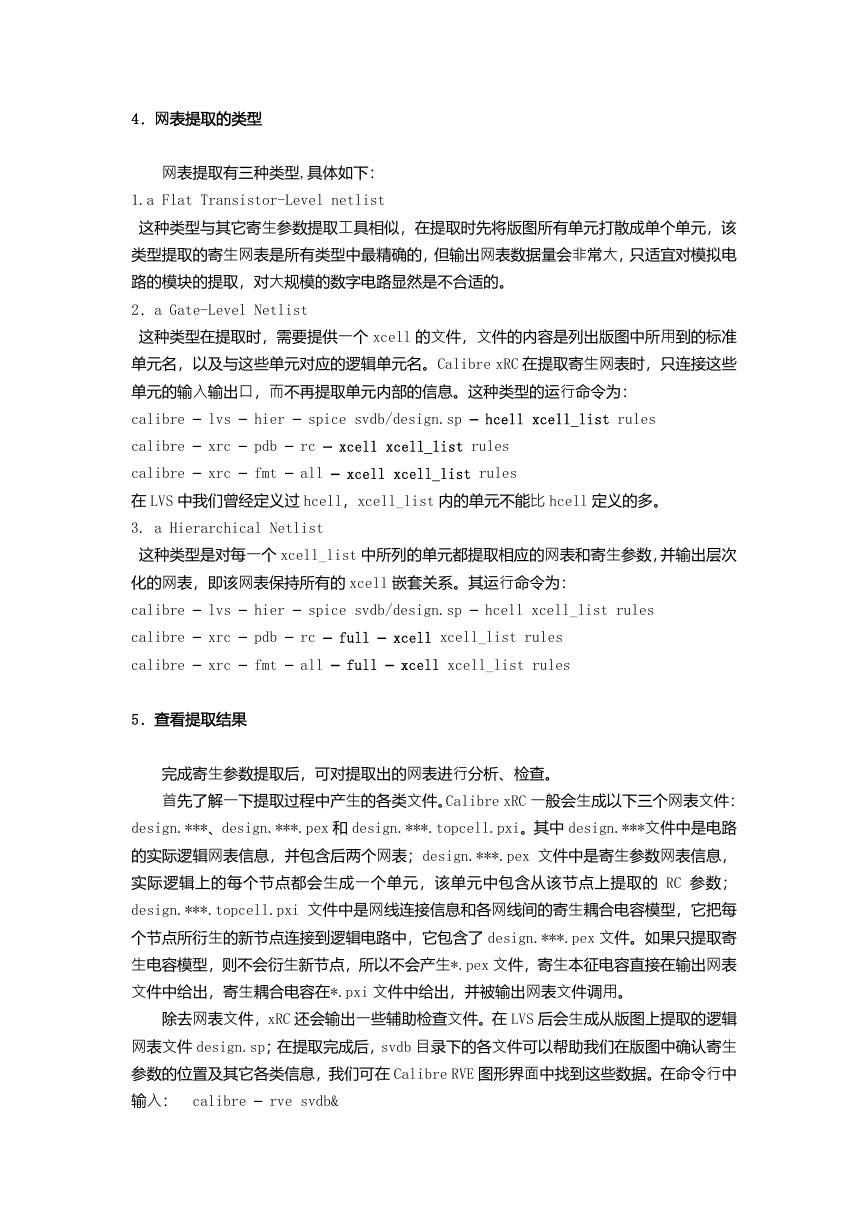

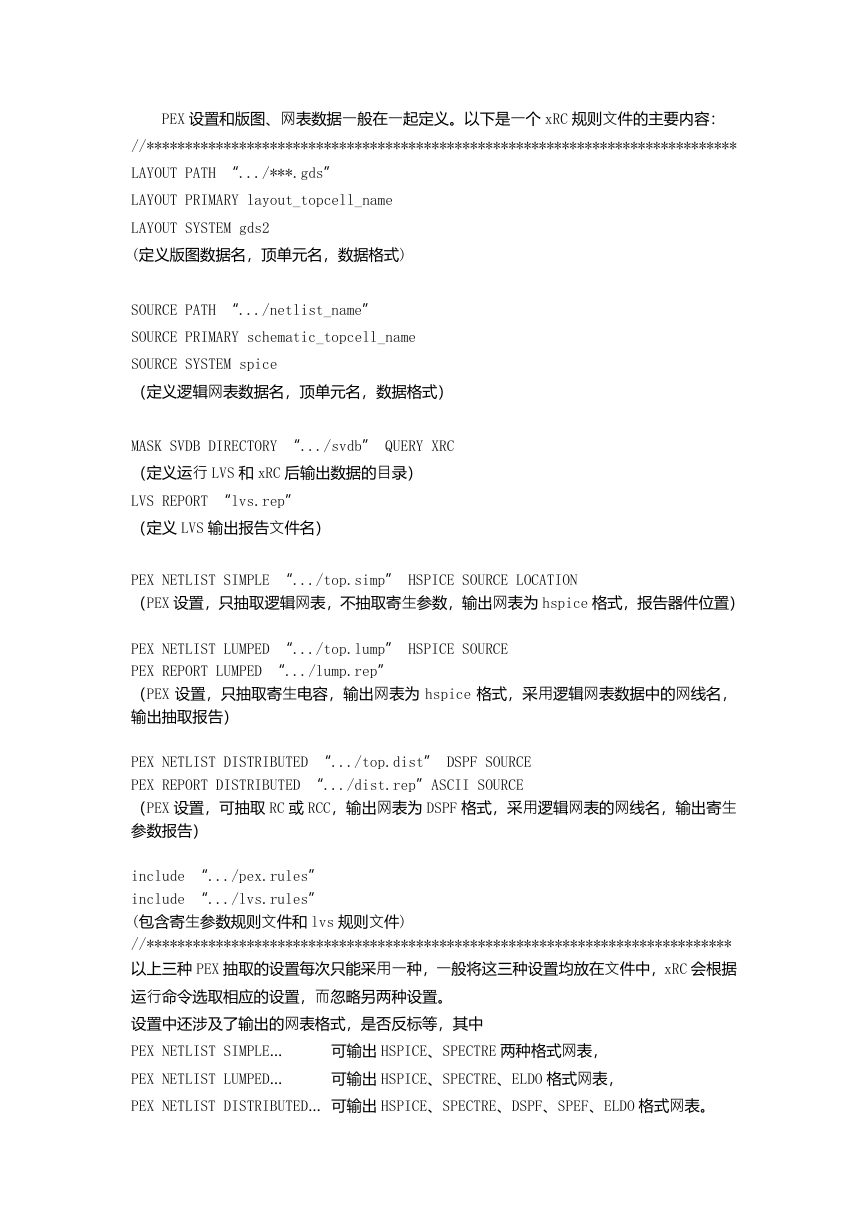

Calibre xRC 提供两种方式实现寄生参数提取,一种是在文件中完成设置,并在命令行

中直接运行;另一种是在图形用户界面中设置参数并运行,下面分别介绍。图 2 为 Calibre

xRC 提取流程。

图 2 Calibre xRC 提图流程图

3.1 xRC 输入文件

从图 2 中可知,Calibre xRC 必须有版图数据和逻辑网表及 xRC 规则文件,xRC 规则文

件同时可包含寄生参数规则文件、LVS 规则文件以及 xRC 的设置语句。

�

3.1.1 寄生参数规则文件

我们知道,平板电容的大小与其介质层的厚度有关、侧壁电容的大小与导电层的厚度、

导电层之间的距离等有关,电阻的大小也与材料、掺杂浓度有关,而在不同的制造工艺中,

这些与寄生电容、电阻有关的参数都是不同的,所以要准确提取版图的寄生参数,首先要提

供符合所提版图的各类工艺参数。Calibre 提供了寄生参数模型产生工具 xCalibrate,可以

产生提取寄生电容时所使用的电容计算规则文件。直接在命令行中键入 xcalibrate,导出

图形界面,在相应的区域内输入版图所采用的工艺的描述(导电层名称及相应的厚度、宽度,

介质层介电常数、厚度等),xCalibrate 就可以为指定的工艺确定基本的几何相互作用关系,

经分析产生寄生参数规则文件中的电容方程。该文件产生后,还须加入各导电层之间纵向连

接的上下顺序以确定导电层之间的屏蔽(shielding)问题。例如,有以下定义:

CAPACITANCE ORDER ndiff pdiff poly1 metal1 metal2

若版图中 metal1 和衬底之间有 poly 层,则 poly 层会将 metal1 和衬底之间在 poly 位置的

寄生电容予以屏蔽。

电阻规则文件的产生较简单,一般只要将相关工艺的各导电层的方块电阻和接触电阻直

接使用 Calibre 定义的 SVRF 语句输入即可,如 metal1 的方块电阻为 0.2ohm,metal1 和 poly1

之间的接触电阻为 10ohm,则定义为:

RESISTANCE SHEET METAL1 [0.2 0]

RESISTANCE CONNECTION METAL1 POLY1 [10 0]

3.1.2 LVS 规则文件和 PEX 设置

LVS 规则文件是做 LVS 时需使用的文件,它包含版图所用到的层次定义、层次间的连接

定义、层次间的运算、器件定义及规则检查等。

PEX 设置主要是设置寄生网表产生的类型及提取中的一些定向约减设置,寄生类型设置

须与 xRC 运行命令对应使用,可生成 5 种不同的寄生类型:Lumped C,RC,RCC,R-only,

不提取。下表是 PEX 设置、运行命令与相应的提取寄生网表类型:

PEX 设置语句

PEX NETLIST SIMPLE

PEX NETLIST LUMPED

PEX NETLIST DISTRIBUTED

xRC 运行语句

提取寄生类型

Calibre –xrc –pdb –rcc rules

Calibre –xrc –fmt –simple rules

Calibre –xrc –pdb –rcc rules

Calibre –xrc –fmt –c rules

Calibre –xrc –pdb –rcc rules

Calibre –xrc –fmt –rc rules

Calibre –xrc –pdb –rcc rules

Calibre –xrc –fmt –rcc rules

Calibre –xrc –pdb –rcc rules

Calibre –xrc –fmt –r rules

不提取

Lumped C

RC

RCC

R

�

PEX 设置和版图、网表数据一般在一起定义。以下是一个 xRC 规则文件的主要内容:

//*****************************************************************************

LAYOUT PATH “.../***.gds”

LAYOUT PRIMARY layout_topcell_name

LAYOUT SYSTEM gds2

(定义版图数据名,顶单元名,数据格式)

SOURCE PATH “.../netlist_name”

SOURCE PRIMARY schematic_topcell_name

SOURCE SYSTEM spice

(定义逻辑网表数据名,顶单元名,数据格式)

MASK SVDB DIRECTORY “.../svdb” QUERY XRC

(定义运行 LVS 和 xRC 后输出数据的目录)

LVS REPORT “lvs.rep”

(定义 LVS 输出报告文件名)

PEX NETLIST SIMPLE “.../top.simp” HSPICE SOURCE LOCATION

(PEX 设置,只抽取逻辑网表,不抽取寄生参数,输出网表为 hspice 格式,报告器件位置)

PEX NETLIST LUMPED “.../top.lump” HSPICE SOURCE

PEX REPORT LUMPED “.../lump.rep”

(PEX 设置,只抽取寄生电容,输出网表为 hspice 格式,采用逻辑网表数据中的网线名,

输出抽取报告)

PEX NETLIST DISTRIBUTED “.../top.dist” DSPF SOURCE

PEX REPORT DISTRIBUTED “.../dist.rep”ASCII SOURCE

(PEX 设置,可抽取 RC 或 RCC,输出网表为 DSPF 格式,采用逻辑网表的网线名,输出寄生

参数报告)

include “.../pex.rules”

include “.../lvs.rules”

(包含寄生参数规则文件和 lvs 规则文件)

//****************************************************************************

以上三种 PEX 抽取的设置每次只能采用一种,一般将这三种设置均放在文件中,xRC 会根据

运行命令选取相应的设置,而忽略另两种设置。

设置中还涉及了输出的网表格式,是否反标等,其中

PEX NETLIST SIMPLE… 可输出 HSPICE、SPECTRE 两种格式网表,

PEX NETLIST LUMPED… 可输出 HSPICE、SPECTRE、ELDO 格式网表,

PEX NETLIST DISTRIBUTED… 可输出 HSPICE、SPECTRE、DSPF、SPEF、ELDO 格式网表。

�

3.1.3 PEX 选择及约减设置

1.选择(Excluding and selection)

PEX EXCLUDE LUMPED SOURCE “net1” “net2”

PEX EXCLUDE DISTRIBUTED SOURCE “net1” “net2”

(net1 和 net2 线上的寄生参数不抽取,一般会定义电源和地线)

PEX INCLUDE LUMPED “net1” “net2”

PEX INCLUDE DISTRIBUTED “net1” “net2”

(只抽取 net1 和 net2 线上的寄生参数,net1、net2 与其它网线之间的电容不抽取)

PEX EXCLUDE 和 PEX INCLUDE 一次只能使用一种,它由运行命令决定。若运行命令 calibre

–xrc –pdb 时有 -select 选项,则 xRC 执行 PEX INCLUDE 设置,若无,则执行 PEX EXCLUDE

选项。

2.约减(Reduction)

PEX TOLERANCE DISTRIBUTED

TICER(Time Constant Equilibration Reduction)

PEX THRESHOLD

PEX REDUCE LUMPED C

PEX REDUCE COUPLED(该定义在 calibre –xrc –fmt 命令中加后缀“-g”时会被忽略)

上述语句均可用于约减网表中对电路影响较小的寄生参数,以缩小寄生网表规模,便于后仿

真分析。大家可查看帮助手册 mgcdocs,在此不再详述。

3.2 寄生参数提取流程

如图 2 所示,用 Calibre xRC 提取寄生参数分三个步骤,下面逐一介绍。

3.2.1 LVS(Layout vs. Schematic)or PHDB(Persistent Hierarchical Database)

在提取之前首先需要做 DRC 和 LVS,以确定版图的准确性,如果需要将提取的参数反标

到逻辑网表,则必须保证 LVS 的结果零错误,DRC 和 LVS 文件均采用 Calibre 定义的 SVRF

(Standard Verification Rule Format)语句编写。运行 LVS 时 Calibre 会生成一个 SVDB

(Standard Verification Database)的目录,该目录下存储 LVS 和 xRC 运行过程中产生的

与版图有关的所有信息,例如在完成 LVS 后,在 SVDB 目录下会产生 LVS 所提取的版图网表

文 件 topcell.sp ( 该 文 件 名 称 必 须 以 版 图 的 顶 单 元 名 命 名 ) 和 PHDB ( Persistent

Hierarchical Database)的目录,该目录下包含了层次化的连接关系和原始的网线、器件

的数据、位置等信息。

LVS 运行命令为:

calibre –lvs –hier –spi svdb/layout_spice_file rule_file_name;

�

(其中 layout_spice_file 为所提取版图的网表名,rule_file_name 为 LVS 规则文件,一

般与 xRC 规则文件合并成同一个)。

若只提取版图电路及寄生参数网表,不反标到逻辑网表,可用以下运行命令:

calibre –xrc –phdb rule_file_name

3.2.2 PDB(Parasitic database)

完成 LVS 后,第二步是提取版图中的寄生参数信息。运行命令为:

calibre –xrc –pdb [–r|-c|-rc|-rcc ] [-select] rule_file_name;

(其中[ ]中按需要选取,rule_file_name 为 Calibre xRC 的规则设置文件,一般都包含 LVS

文件)。

运行结束后,Calibre xRC 在所定义存放中间验证数据的目录下会生成 PDB(Parasitic

Database)目录,该目录中包含了所有有关版图中寄生模型的连接关系与相关数据、位置等

信息。值得注意的是,Calibre xRC 每次运行时,会采用叠加的方式将提取的信息加到已有

的 PDB 目录中,它的优点是如果需要增加寄生参数提取,xRC 无需重新运行,而只运行增加

的部分,如 xRC 已提取 RC 寄生参数,再提取 RCC 时,只要提取 coupled C 就行了,这样可

以大大节省运行时间。但是如果再次运行时,版图已经过修改,xRC 不会覆盖修改前已提取

相关位置网线的寄生参数信息,这样会使参数提取与版图不符,导致不必要的仿真误差。所

以一般情况下,每次运行这一步前,最好先删除 PDB 目录。

3.2.3 FMT(Format Netlists or Reports)

第三步是把前步所提取的寄生参数按所定义的输出网表格式输出至指定文件中。运行命

令为:

calibre –xrc –fmt [-c|-r|-rc|-rcc|–all] [-g] rule_file_name。

Calibre xRC 会到 PDB 目录下找到适合的数据输出报告和网表。

以上运行命令可以编写成一个批处理文件,以方便多次的重复运行。以下是该文件举例

说明:

#! /bin/csh –f

\rm –rf svdb/*.pdb

calibre –lvs –hier –spi svdb/topcell.sp rules |tee lvs.log

calibre –xrc –pdb –rcc rules |tee pdb.log

calibre –xrc –fmt –all rules |tee fmt.log

其中,“rules”为 xRC 规则文件名。

�

4.网表提取的类型

网表提取有三种类型,具体如下:

1.a Flat Transistor-Level netlist

这种类型与其它寄生参数提取工具相似,在提取时先将版图所有单元打散成单个单元,该

类型提取的寄生网表是所有类型中最精确的,但输出网表数据量会非常大,只适宜对模拟电

路的模块的提取,对大规模的数字电路显然是不合适的。

2.a Gate-Level Netlist

这种类型在提取时,需要提供一个 xcell 的文件,文件的内容是列出版图中所用到的标准

单元名,以及与这些单元对应的逻辑单元名。Calibre xRC 在提取寄生网表时,只连接这些

单元的输入输出口,而不再提取单元内部的信息。这种类型的运行命令为:

calibre –lvs –hier –spice svdb/design.sp –hcell xcell_list rules

calibre –xrc –pdb –rc –xcell xcell_list rules

calibre –xrc –fmt –all –xcell xcell_list rules

在 LVS 中我们曾经定义过 hcell,xcell_list 内的单元不能比 hcell 定义的多。

3. a Hierarchical Netlist

这种类型是对每一个 xcell_list 中所列的单元都提取相应的网表和寄生参数,并输出层次

化的网表,即该网表保持所有的 xcell 嵌套关系。其运行命令为:

calibre –lvs –hier –spice svdb/design.sp –hcell xcell_list rules

calibre –xrc –pdb –rc –full –xcell xcell_list rules

calibre –xrc –fmt –all –full –xcell xcell_list rules

5.查看提取结果

完成寄生参数提取后,可对提取出的网表进行分析、检查。

首先了解一下提取过程中产生的各类文件。Calibre xRC 一般会生成以下三个网表文件:

design.***、design.***.pex 和 design.***.topcell.pxi。其中 design.***文件中是电路

的实际逻辑网表信息,并包含后两个网表;design.***.pex 文件中是寄生参数网表信息,

实际逻辑上的每个节点都会生成一个单元,该单元中包含从该节点上提取的 RC 参数;

design.***.topcell.pxi 文件中是网线连接信息和各网线间的寄生耦合电容模型,它把每

个节点所衍生的新节点连接到逻辑电路中,它包含了 design.***.pex 文件。如果只提取寄

生电容模型,则不会衍生新节点,所以不会产生*.pex 文件,寄生本征电容直接在输出网表

文件中给出,寄生耦合电容在*.pxi 文件中给出,并被输出网表文件调用。

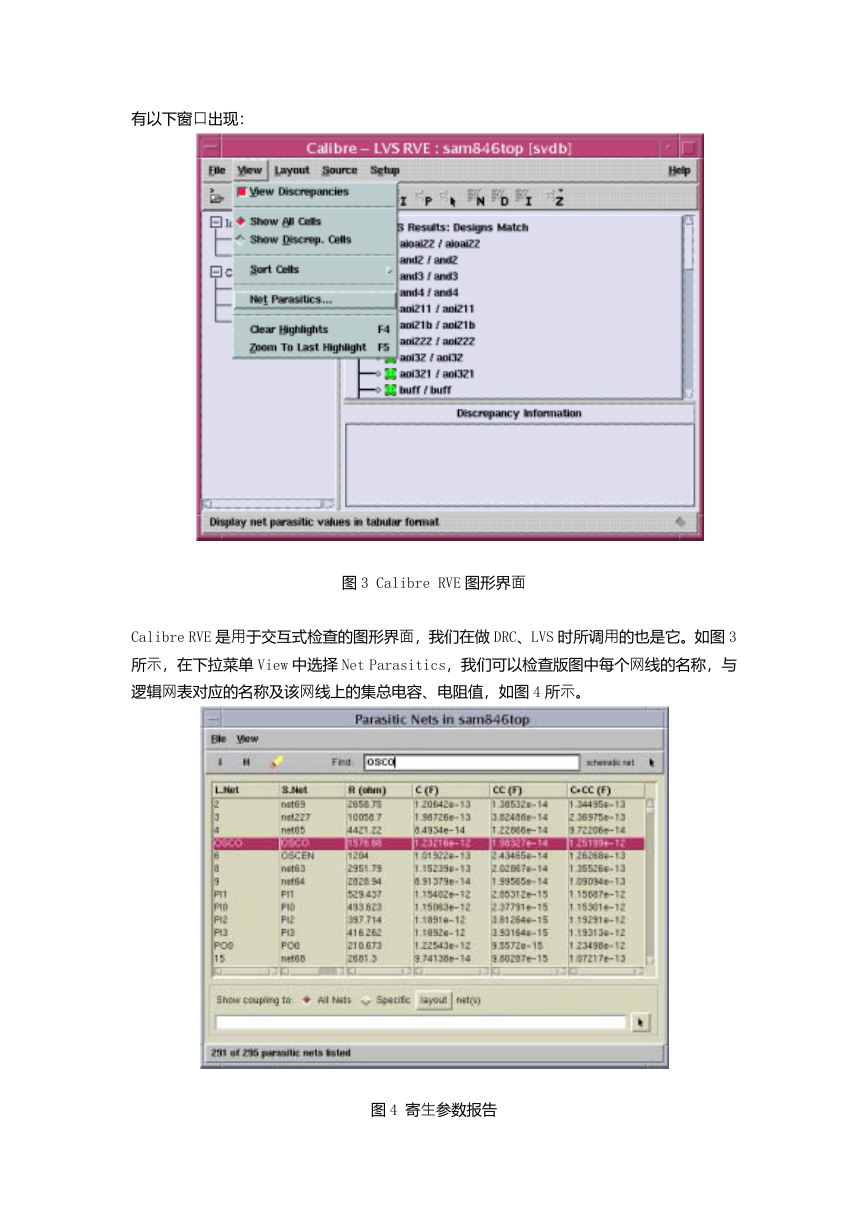

除去网表文件,xRC 还会输出一些辅助检查文件。在 LVS 后会生成从版图上提取的逻辑

网表文件 design.sp;在提取完成后,svdb 目录下的各文件可以帮助我们在版图中确认寄生

参数的位置及其它各类信息,我们可在 Calibre RVE 图形界面中找到这些数据。在命令行中

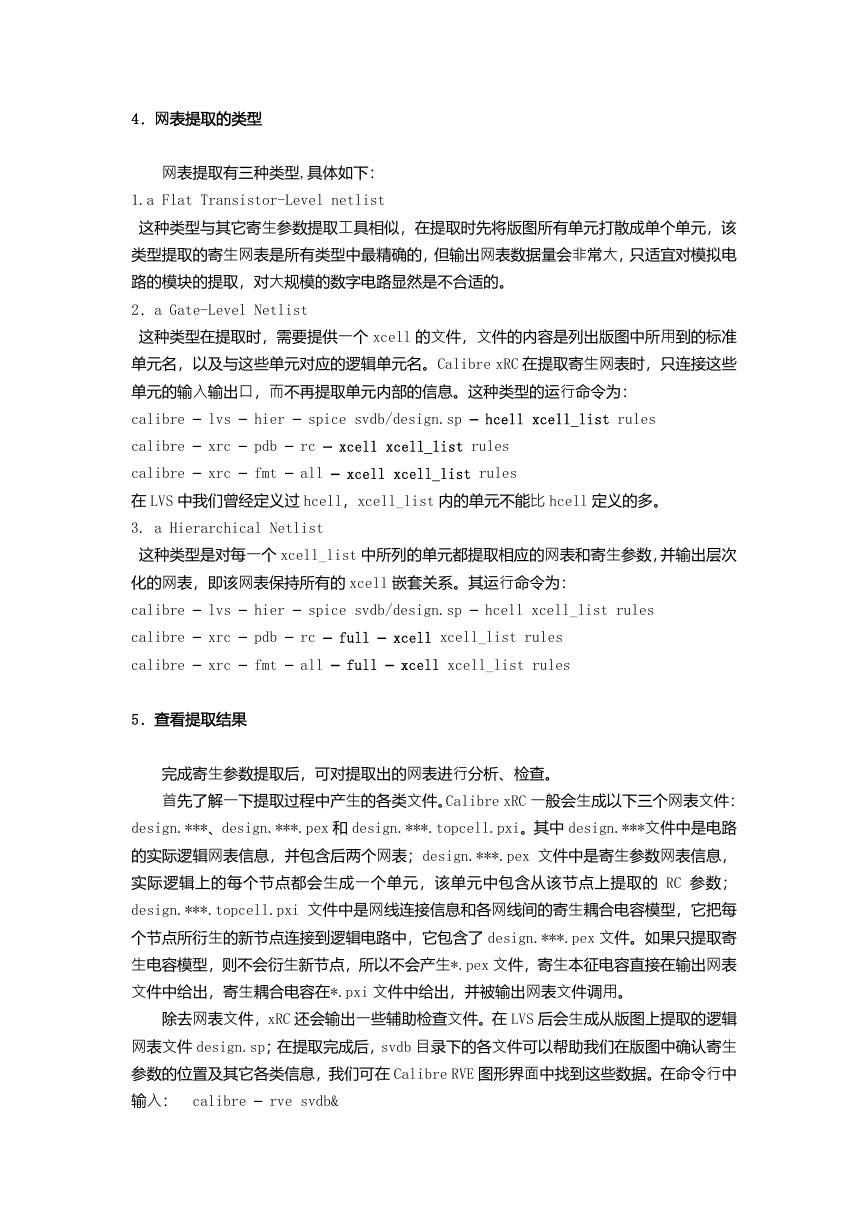

输入: calibre –rve svdb&

�

有以下窗口出现:

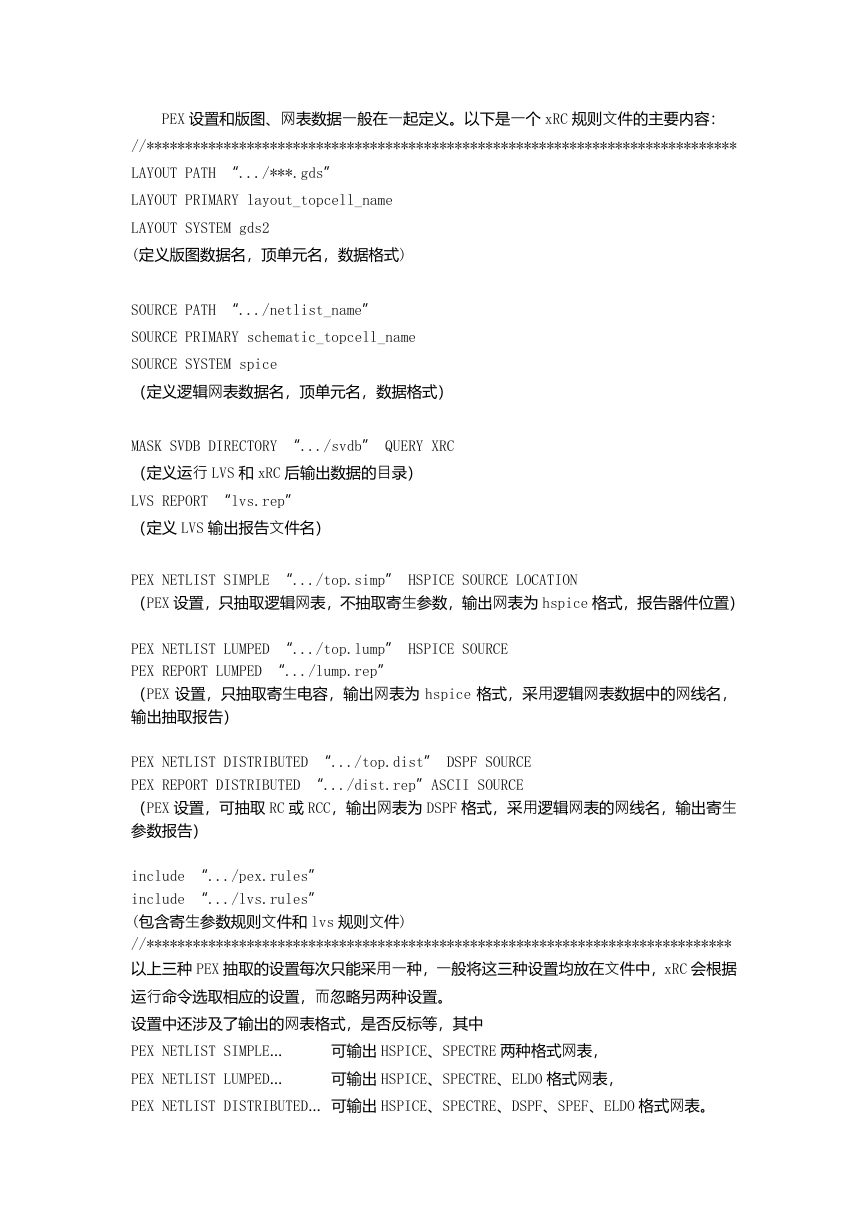

图 3 Calibre RVE 图形界面

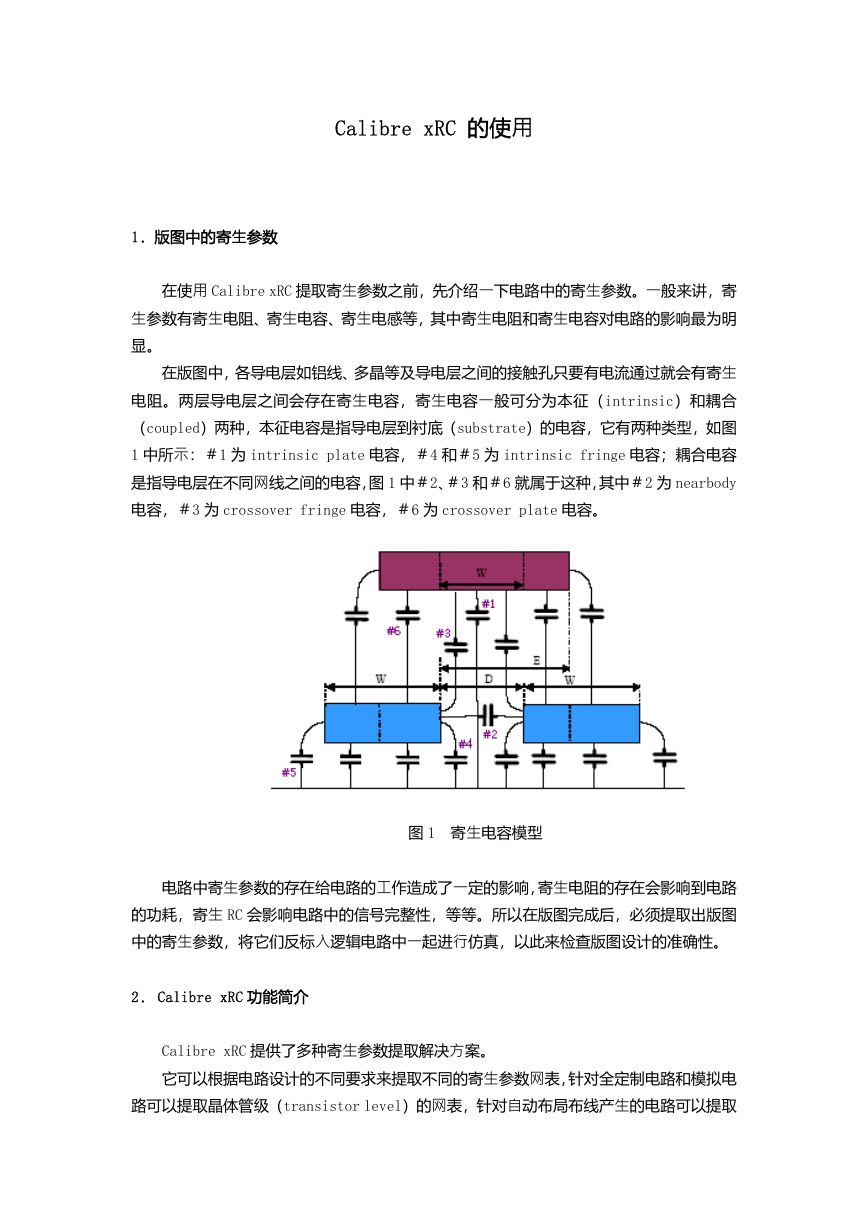

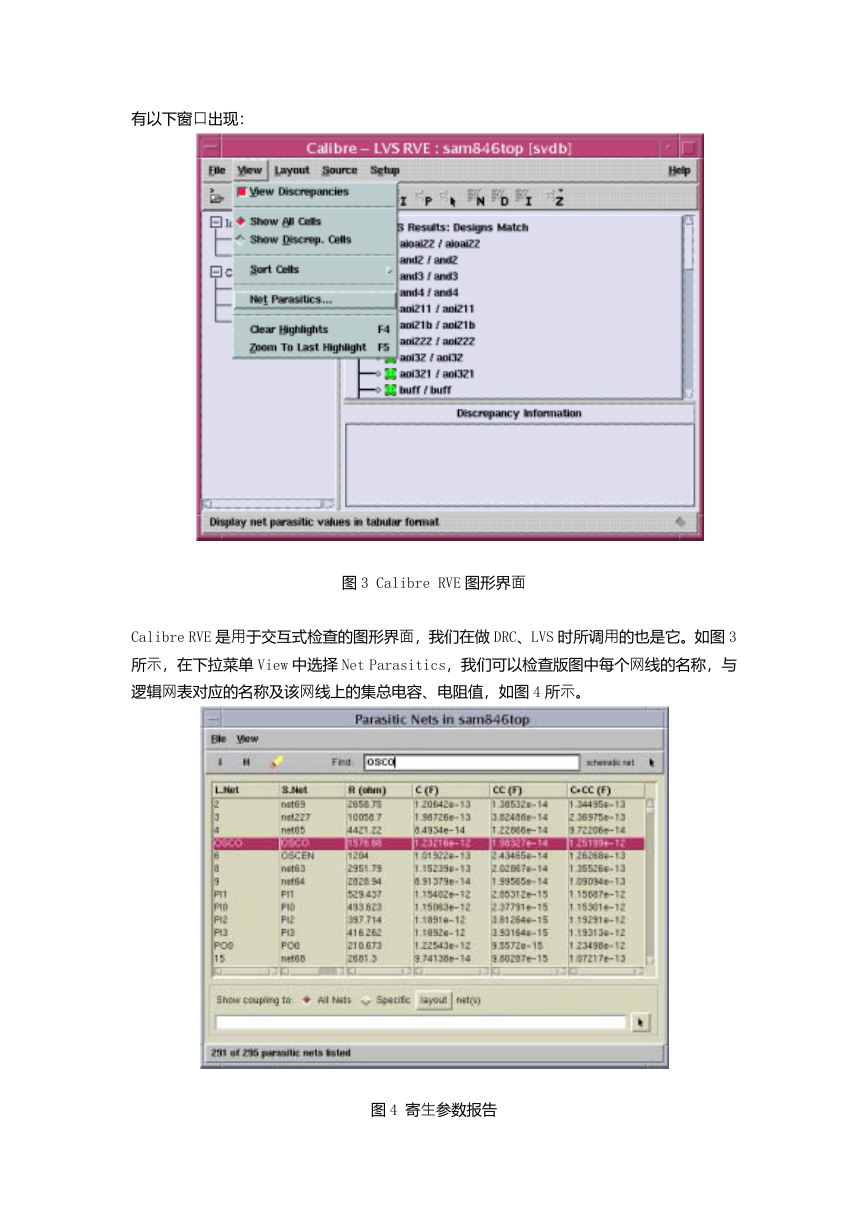

Calibre RVE 是用于交互式检查的图形界面,我们在做 DRC、LVS 时所调用的也是它。如图 3

所示,在下拉菜单 View 中选择 Net Parasitics,我们可以检查版图中每个网线的名称,与

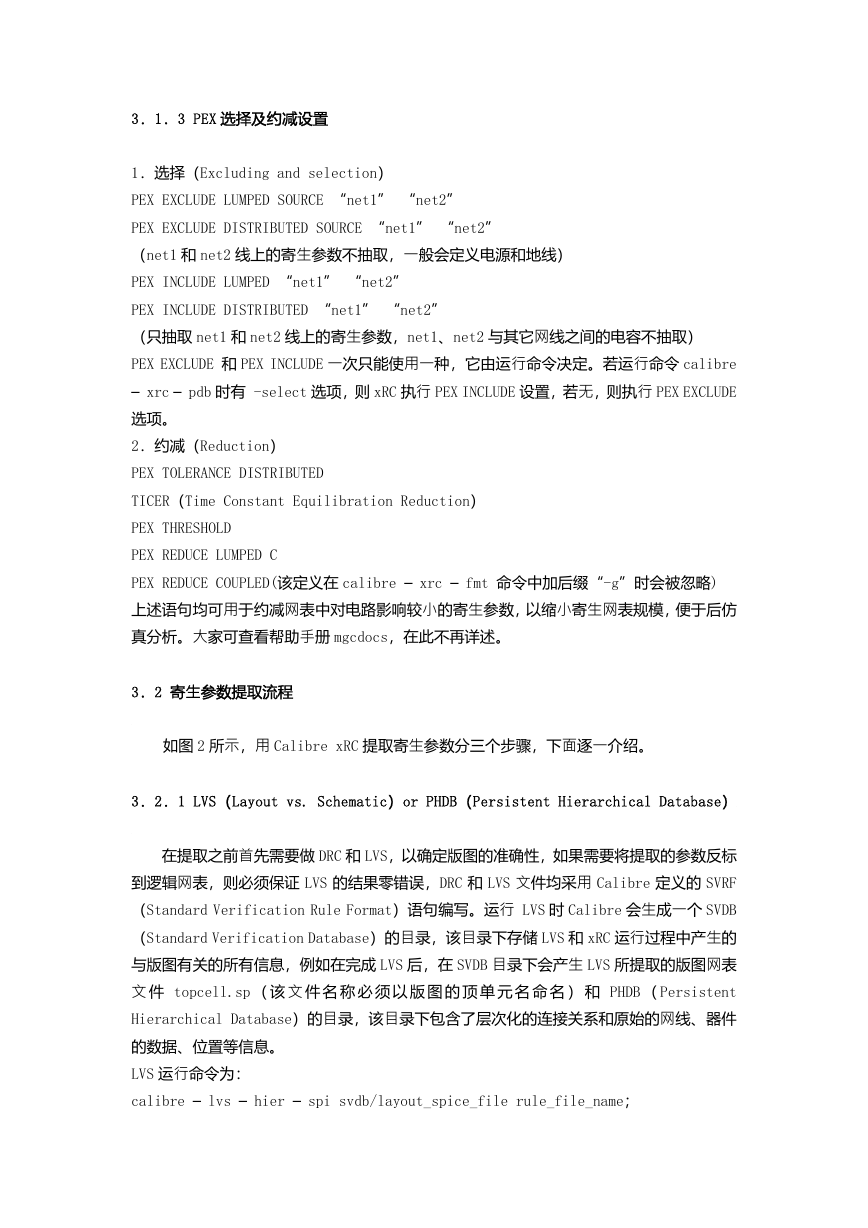

逻辑网表对应的名称及该网线上的集总电容、电阻值,如图 4 所示。

图 4 寄生参数报告

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc