D

C

B

A

5

4

3

2

1

RTL8211F(D)(I) UTP <=> RGMII

QFN-40 Pin Reference Schematic

Page Index

P1. Title Page

P2. Ethernet PHY

D

C

B

REVISION HISTORY

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic V1.0

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic V1.01

* Change the value of C5/C6 for RTL8211FDI/FI application.

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic V1.02

* Fix the name of the path.

Realtek Semiconductor Corp.

Realtek Semiconductor Corp.

Realtek Semiconductor Corp.

No.2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

No.2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

No.2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

A

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic: Index

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic: Index

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic: Index

Document Number

Document Number

Document Number

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic

Re v

Rev

Rev

1.02

1.02

1.02

Title

Title

Title

Size

Size

Size

A

A

A

Date:

Date:

Date:

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

Sheet

Sheet

Sheet

1

1

1

o f

o f

o f

2

2

2

5

4

3

2

1

�

D

C

B

A

5

4

3

2

1

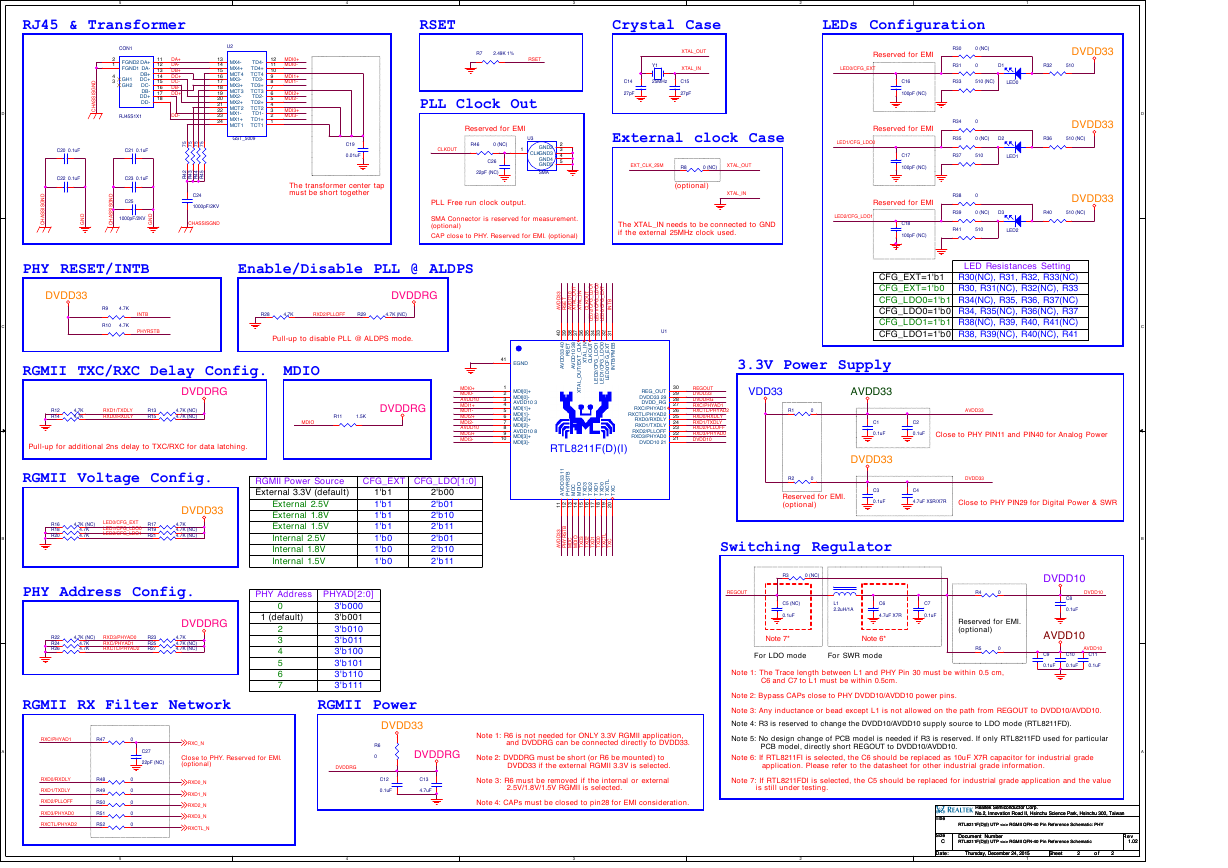

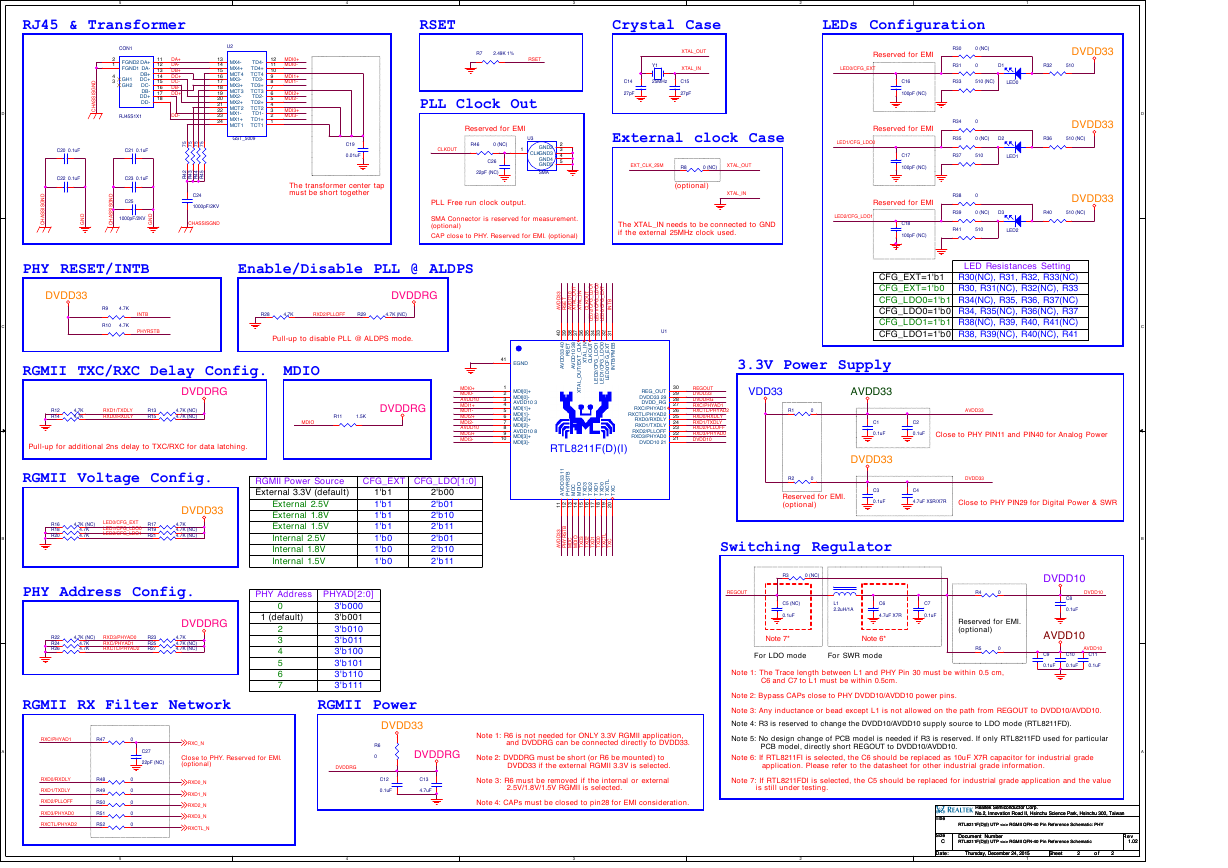

RJ45 & Transformer

RSET

Crystal Case

LEDs Configuration

CON1

2

1

4

3

FGND2

FGND1

GH1

GH2

11

12

13

14

15

16

17

18

DA+

DA-

DB+

DC+

DC-

DB-

DD+

DD-

RJ45S1X1

DA+

DA-

DB+

DC+

DC-

DB-

DD+

DD-

I

D

N

G

S

S

S

A

H

C

U2

MX4-

MX4+

MCT4

MX3-

MX3+

MCT3

MX2-

MX2+

MCT2

MX1-

MX1+

MCT1

13

14

15

16

17

18

19

20

21

22

23

24

12

11

10

9

8

7

6

5

4

3

2

1

TD4-

TD4+

TCT4

TD3-

TD3+

TCT3

TD2-

TD2+

TCT2

TD1-

TD1+

TCT1

MDI0+

MDI0-

MDI1+

MDI1-

MDI2+

MDI2-

MDI3+

MDI3-

GST_5009

C20 0.1uF

C21 0.1uF

C22 0.1uF

C23 0.1uF

5

7

5

7

5

7

5

7

2

4

R

3

4

R

4

4

R

5

4

R

I

D

N

G

S

S

S

A

H

C

I

D

N

G

S

S

S

A

H

C

C25

1000pF/2KV

D

N

G

D

N

G

C24

1000pF/2KV

CHASSISGND

C19

0.01uF

The transformer center tap

must be short together

R7

2.49K 1%

RSET

PLL Clock Out

Reserved for EMI

CLKOUT

R46

0 (NC)

C26

22pF (NC)

U3

1

CLK

GND2

GND3

GND4

GND5

SMA

2

3

4

5

PLL Free run clock output.

SMA Connector is reserved for measurement.

(optional)

CAP close to PHY. Reserved for EMI. (optional)

Y1

25MHz

C14

27pF

XTAL_OUT

XTAL_IN

C15

27pF

Reserved for EMI

R30

0 (NC)

DVDD33

LED0/CFG_EXT

R31

0

D1

R32

510

C16

100pF (NC)

R33

510 (NC)

LED0

External clock Case

Reserved for EMI

R34

0

DVDD33

LED1/CFG_LDO0

R35

0 (NC)

D2

R36

510 (NC)

EXT_CLK_25M

R8

0 (NC)

XTAL_OUT

(optional)

XTAL_IN

C17

100pF (NC)

R37

510

LED1

Reserved for EMI

R38

0

DVDD33

LED2/CFG_LDO1

R39

0 (NC)

D3

R40

510 (NC)

The XTAL_IN needs to be connected to GND

if the external 25MHz clock used.

C18

100pF (NC)

R41

510

LED2

PHY RESET/INTB

Enable/Disable PLL @ ALDPS

DVDD33

R9

4.7K

R10

4.7K

INTB

PHYRSTB

DVDDRG

R28

4.7K

RXD2/PLLOFF

R29

4.7K (NC)

Pull-up to disable PLL @ ALDPS mode.

T

U

O

_

L

A

T

X

0

1

D

D

V

A

I

N

_

L

A

T

X

3

3

D

D

V

A

T

E

S

R

T

U

O

K

L

C

1

O

D

L

_

G

F

C

2

D

E

L

0

O

D

L

_

G

F

C

1

D

E

L

/

/

T

X

E

_

G

F

C

0

D

E

L

/

B

T

N

I

0

4

9

3

8

3

7

3

6

3

5

3

4

3

3

3

2

3

1

3

RGMII TXC/RXC Delay Config. MDIO

DVDDRG

R12

R14

4.7K

4.7K

RXD1/TXDLY

RXD0/RXDLY

R13

R15

4.7K (NC)

4.7K (NC)

R11

1.5K

MDIO

DVDDRG

Pull-up for additional 2ns delay to TXC/RXC for data latching.

RGMII Voltage Config.

R16

R18

R20

4.7K (NC)

4.7K

4.7K

LED0/CFG_EXT

LED1/CFG_LDO0

LED2/CFG_LDO1

R17

R19

R21

4.7K

4.7K (NC)

4.7K (NC)

DVDD33

RGMII Power Source

External 3.3V (default)

External 2.5V

External 1.8V

External 1.5V

Internal 2.5V

Internal 1.8V

Internal 1.5V

CFG_EXT

CFG_LDO[1:0]

1'b1

1'b1

1'b1

1'b1

1'b0

1'b0

1'b0

2'b00

2'b01

2'b10

2'b11

2'b01

2'b10

2'b11

41

1

2

3

4

5

6

7

8

9

10

EGND

MDI[0]+

MDI[0]-

AVDD10 3

MDI[1]+

MDI[1]-

MDI[2]+

MDI[2]-

AVDD10 8

MDI[3]+

MDI[3]-

MDI0+

MDI0-

AVDD10

MDI1+

MDI1-

MDI2+

MDI2-

AVDD10

MDI3+

MDI3-

0

4

3

3

D

D

V

A

T

E

S

R

8

3

0

1

D

D

V

A

I

N

_

L

A

T

X

T

U

O

K

L

C

B

E

M

P

B

T

N

/

I

1

O

D

L

_

G

F

C

2

D

E

L

0

O

D

L

_

G

F

C

1

D

E

L

/

/

T

X

E

_

G

F

C

0

D

E

L

/

/

K

L

C

_

T

X

E

T

U

O

_

L

A

T

X

RTL8211F(D)(I)

1

1

3

3

D

D

V

A

B

T

S

R

Y

H

P

C

D

M

I

O

D

M

3

D

X

T

2

D

X

T

1

D

X

T

0

D

X

T

L

T

C

X

T

C

X

T

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

1

0

2

B

T

S

R

Y

H

P

3

3

D

D

V

A

C

D

M

I

O

D

M

3

D

X

T

2

D

X

T

1

D

X

T

0

D

X

T

L

T

C

X

T

C

X

T

PHY Address Config.

PHY Address

PHYAD[2:0]

R22

R24

R26

4.7K (NC)

4.7K

4.7K

RXD3/PHYAD0

RXC/PHYAD1

RXCTL/PHYAD2

R23

R25

R27

4.7K

4.7K (NC)

4.7K (NC)

DVDDRG

0

1 (default)

2

3

4

5

6

7

3'b000

3'b001

3'b010

3'b011

3'b100

3'b101

3'b110

3'b111

RGMII RX Filter Network

RGMII Power

DVDD33

RXC_N

C27

22pF (NC)

Close to PHY. Reserved for EMI.

(optional)

R6

0

DVDDRG

DVDDRG

RXC/PHYAD1

R47

RXD0/RXDLY

RXD1/TXDLY

RXD2/PLLOFF

RXD3/PHYAD0

RXCTL/PHYAD2

R48

R49

R50

R51

R52

0

0

0

0

0

0

RXD0_N

RXD1_N

RXD2_N

RXD3_N

RXCTL_N

U1

REG_OUT

DVDD33 29

DVDD_RG

RXC/PHYAD1

RXCTL/PHYAD2

RXD0/RXDLY

RXD1/TXDLY

RXD2/PLLOFF

RXD3/PHYAD0

DVDD10 21

30

29

28

27

26

25

24

23

22

21

REGOUT

DVDD33

DVDDRG

RXC/PHYAD1

RXCTL/PHYAD2

RXD0/RXDLY

RXD1/TXDLY

RXD2/PLLOFF

RXD3/PHYAD0

DVDD10

CFG_EXT=1'b1

CFG_EXT=1'b0

CFG_LDO0=1'b1

CFG_LDO0=1'b0

CFG_LDO1=1'b1

CFG_LDO1=1'b0

LED Resistances Setting

R30(NC), R31, R32, R33(NC)

R30, R31(NC), R32(NC), R33

R34(NC), R35, R36, R37(NC)

R34, R35(NC), R36(NC), R37

R38(NC), R39, R40, R41(NC)

R38, R39(NC), R40(NC), R41

3.3V Power Supply

VDD33

AVDD33

R1

0

AVDD33

C1

0.1uF

C2

0.1uF

DVDD33

Close to PHY PIN11 and PIN40 for Analog Power

R2

0

DVDD33

Reserved for EMI.

(optional)

C3

0.1uF

C4

4.7uF X5R/X7R

Close to PHY PIN29 for Digital Power & SWR

Switching Regulator

R3

0 (NC)

REGOUT

R4

0

C5 (NC)

0.1uF

L1

2.2uH/1A

C6

4.7uF X7R

C7

0.1uF

Note 7*

Note 6*

For LDO mode

For SWR mode

Reserved for EMI.

(optional)

R5

0

Note 1: The Trace length between L1 and PHY Pin 30 must be within 0.5 cm,

C6 and C7 to L1 must be within 0.5cm.

Note 2: Bypass CAPs close to PHY DVDD10/AVDD10 power pins.

DVDD10

DVDD10

C8

0.1uF

AVDD10

C9

C10

AVDD10

C11

0.1uF

0.1uF

0.1uF

Note 1: R6 is not needed for ONLY 3.3V RGMII application,

and DVDDRG can be connected directly to DVDD33.

Note 2: DVDDRG must be short (or R6 be mounted) to

DVDD33 if the external RGMII 3.3V is selected.

Note 3: Any inductance or bead except L1 is not allowed on the path from REGOUT to DVDD10/AVDD10.

Note 4: R3 is reserved to change the DVDD10/AVDD10 supply source to LDO mode (RTL8211FD).

Note 5: No design change of PCB model is needed if R3 is reserved. If only RTL8211FD used for particular

PCB model, directly short REGOUT to DVDD10/AVDD10.

Note 6: If RTL8211FI is selected, the C6 should be replaced as 10uF X7R capacitor for industrial grade

application. Please refer to the datasheet for other industrial grade information.

C12

0.1uF

C13

4.7uF

Note 3: R6 must be removed if the internal or external

2.5V/1.8V/1.5V RGMII is selected.

Note 7: If RTL8211FDI is selected, the C5 should be replaced for industrial grade application and the value

is still under testing.

Note 4: CAPs must be closed to pin28 for EMI consideration.

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

Realtek Semiconductor Corp.

Realtek Semiconductor Corp.

Realtek Semiconductor Corp.

No.2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

No.2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

No.2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic: PHY

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic: PHY

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic: PHY

Document Number

Document Number

Document Number

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic

RTL8211F(D)(I) UTP <=> RGMII QFN-40 Pin Reference Schematic

R e v

R e v

R e v

1.02

1.02

1.02

Thursday, December 24, 2015

Thursday, December 24, 2015

Thursday, December 24, 2015

1

Sheet

Sheet

Sheet

2

2

2

o f

o f

o f

2

2

2

5

4

3

2

D

C

B

A

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc