CameraLink 资料

一. Camera Link 简介

Camera Link 是专门为数字摄像机的数据传输提出的接口标准,专为数字

相机制定的一种图像数据、视频数据控制信号及相机控制信号传输的总线接口。

图 1 camerlink 物理接口

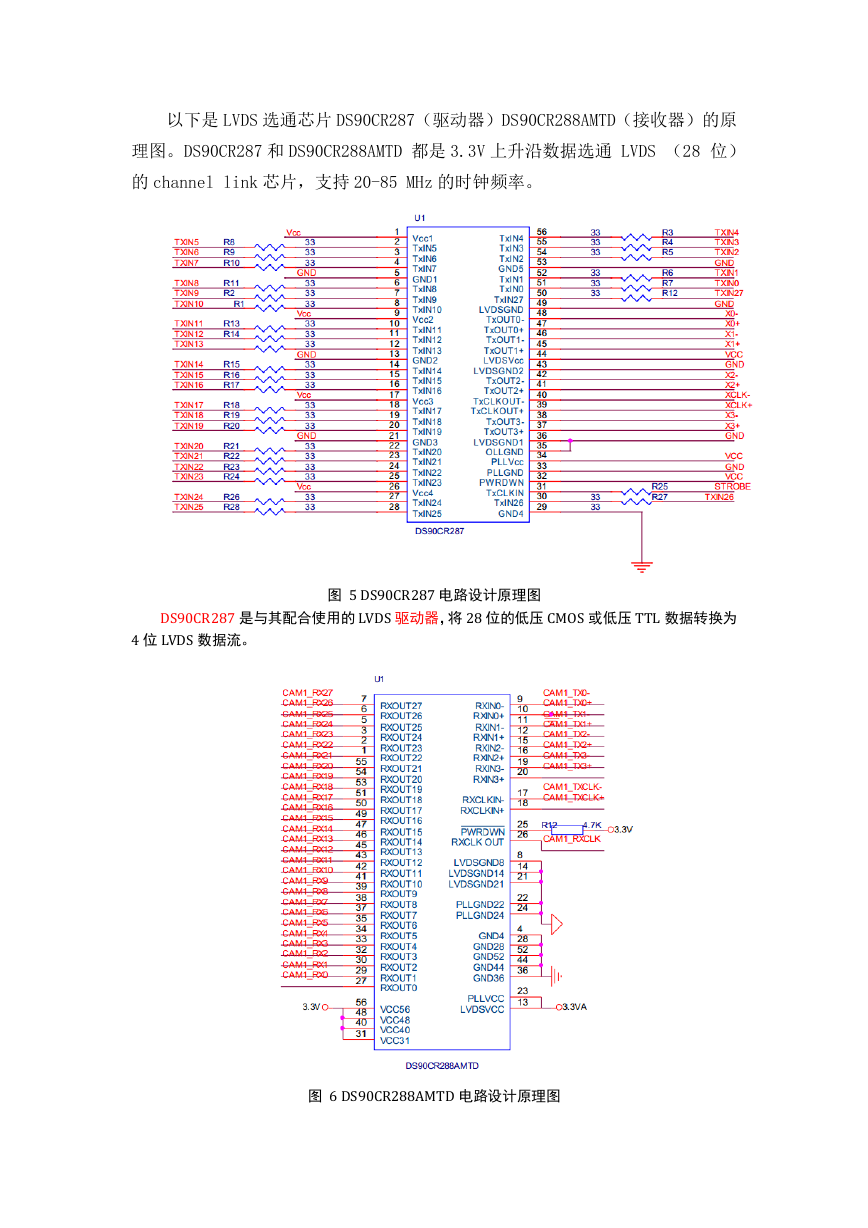

图 2 camerlink 原理图接口

CameraLink 是一种专门针对机器视觉应用领域的串行通信协议,使用低压差

分信号 LVDS 传输。CameraLink 标准在 ChannelLink 标准的基础上有多加了 6 对

差分信号线,4 对用于并行传输相机控制信号,其它 2 对用于相机和图像采集卡

(或其它图像接受处理设备)之间的串行通信。CameraLink 标准中,相机信号分

为四种: 电源信号、视频数据信号(ChannelLink 标准)、相机控制信号、串行通

信信号。

�

图 3 Camera link 整体框架图

二. 信号类型

图 4 信号分类

1. 视频数据信号

视频数据信号部分是 CameraLink 的核心,该部分为其实就是 ChannelLink

协议。主要包括 5 对差分信号,即 X0-~X0+、X1-~X1+、X2-~X2+、X3-~X3+、

Xclk-~Xclk+;视频部分发送端将 28 位的数据信号和 1 个时钟信号,按 7:1 的比

例将数据转换成 5 对差分信号,接收端使用 Channel Link 芯片(如 Channel Link

转 TTL/CMOS 的芯片 DS90CR288A)将 5 对差分信号转换成 28 位的数据信号和 1

个时钟信号。28 位的数据信号包括 4 位视频控制信号和 24 位图像数据信号。这

样不但减少了传输线的使用量,而且由于采用串行差分传输方式,还减少了传输

过程中的电磁干扰。

�

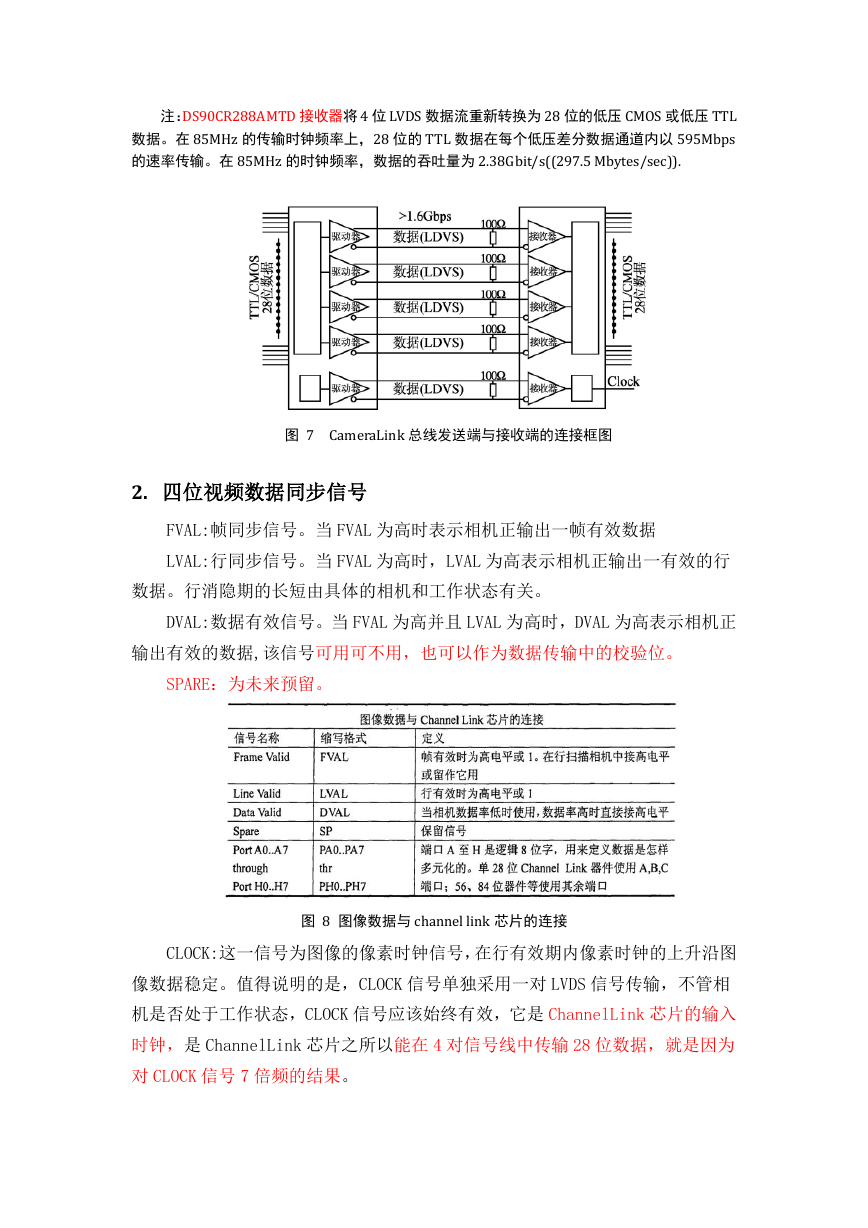

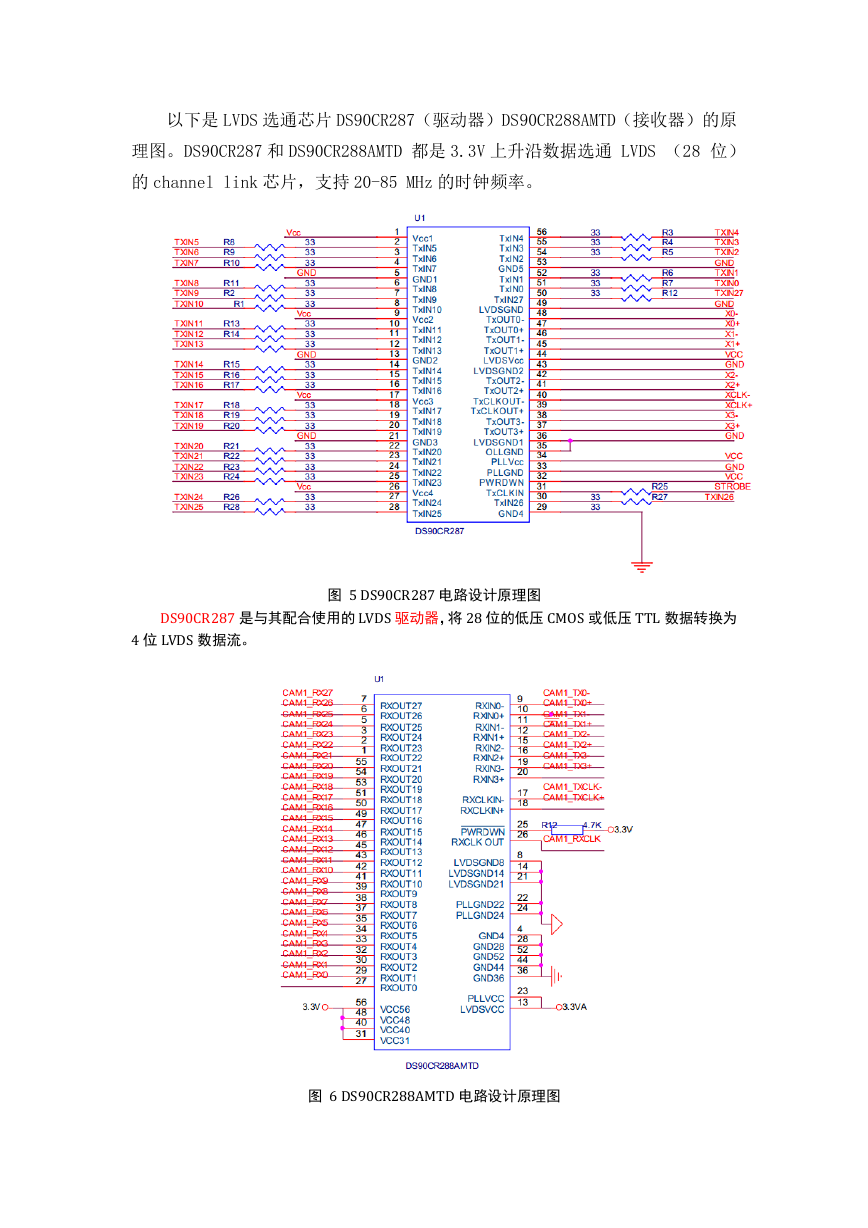

以下是 LVDS 选通芯片 DS90CR287(驱动器)DS90CR288AMTD(接收器)的原

理图。DS90CR287 和 DS90CR288AMTD 都是 3.3V 上升沿数据选通 LVDS (28 位)

的 channel link 芯片,支持 20-85 MHz 的时钟频率。

DS90CR287 是与其配合使用的 LVDS 驱动器,将 28 位的低压 CMOS 或低压 TTL 数据转换为

图 5 DS90CR287 电路设计原理图

4 位 LVDS 数据流。

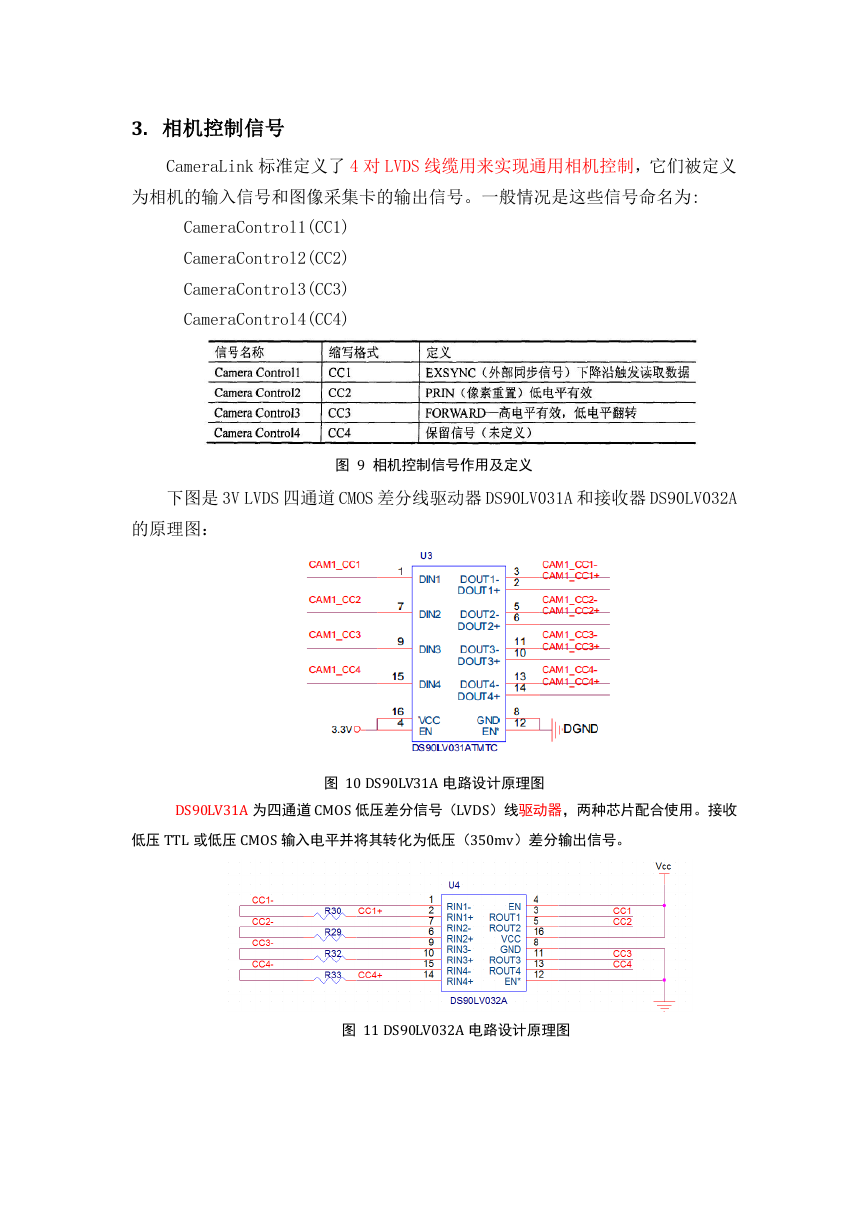

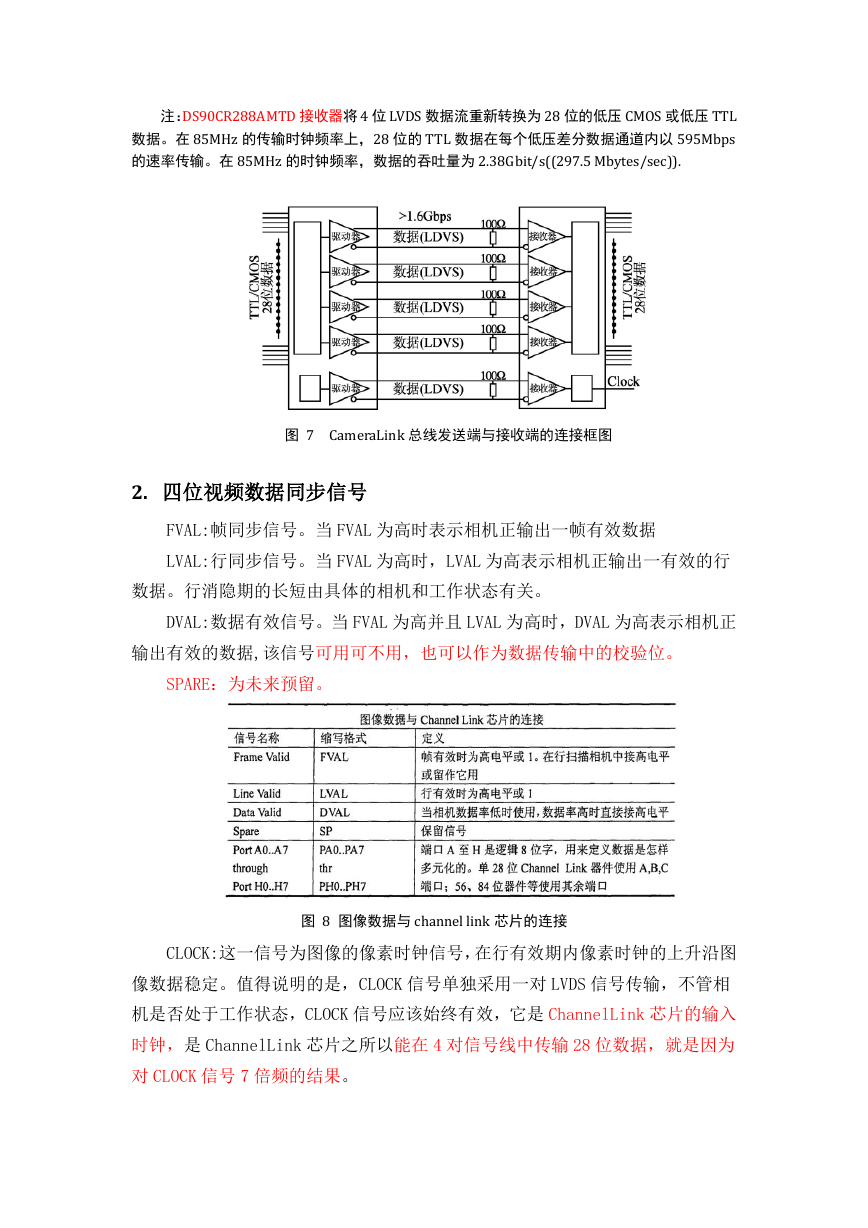

图 6 DS90CR288AMTD 电路设计原理图

�

注:DS90CR288AMTD 接收器将 4 位 LVDS 数据流重新转换为 28 位的低压 CMOS 或低压 TTL

数据。在 85MHz 的传输时钟频率上,28 位的 TTL 数据在每个低压差分数据通道内以 595Mbps

的速率传输。在 85MHz 的时钟频率,数据的吞吐量为 2.38Gbit/s((297.5 Mbytes/sec)).

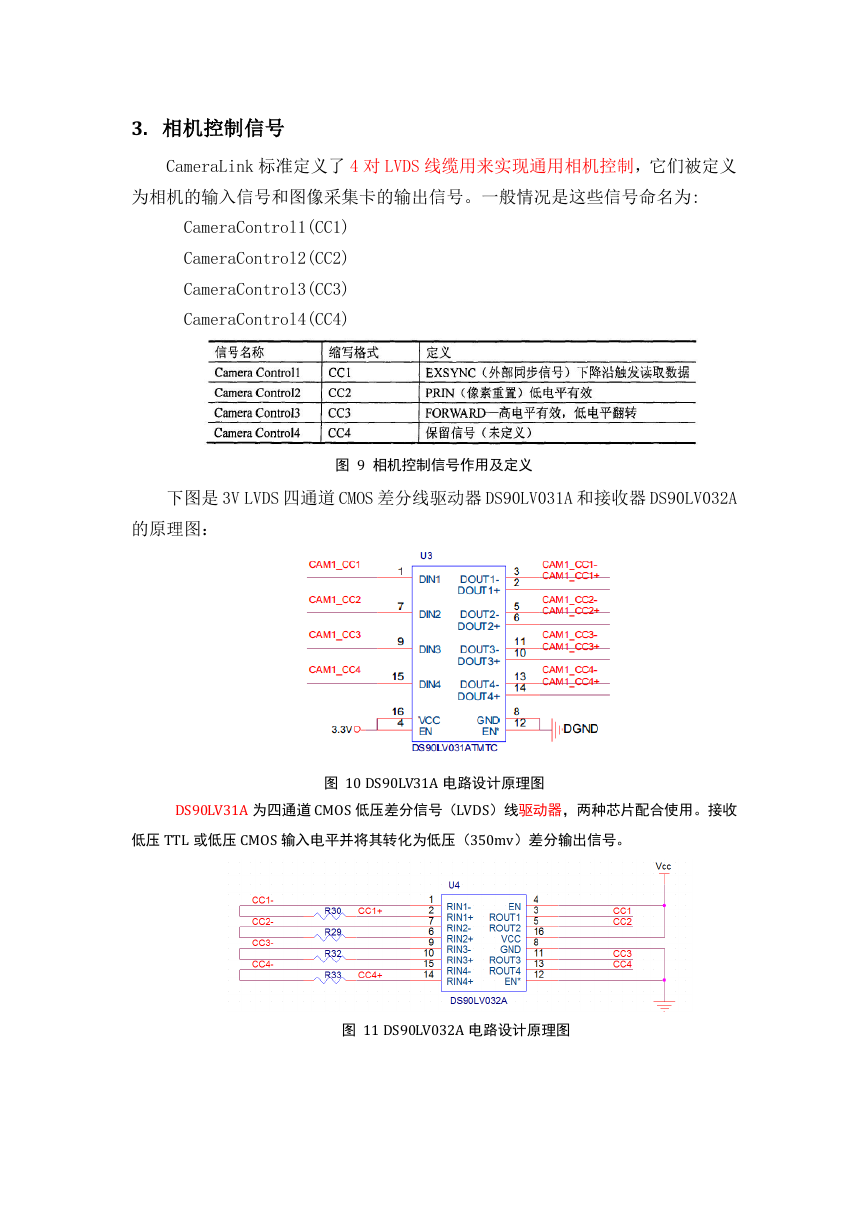

图 7 CameraLink 总线发送端与接收端的连接框图

2. 四位视频数据同步信号

FVAL:帧同步信号。当 FVAL 为高时表示相机正输出一帧有效数据

LVAL:行同步信号。当 FVAL 为高时,LVAL 为高表示相机正输出一有效的行

数据。行消隐期的长短由具体的相机和工作状态有关。

DVAL:数据有效信号。当 FVAL 为高并且 LVAL 为高时,DVAL 为高表示相机正

输出有效的数据,该信号可用可不用,也可以作为数据传输中的校验位。

SPARE:为未来预留。

图 8 图像数据与 channel link 芯片的连接

CLOCK:这一信号为图像的像素时钟信号,在行有效期内像素时钟的上升沿图

像数据稳定。值得说明的是,CLOCK 信号单独采用一对 LVDS 信号传输,不管相

机是否处于工作状态,CLOCK 信号应该始终有效,它是 ChannelLink 芯片的输入

时钟,是 ChannelLink 芯片之所以能在 4 对信号线中传输 28 位数据,就是因为

对 CLOCK 信号 7 倍频的结果。

�

3. 相机控制信号

CameraLink 标准定义了 4 对 LVDS 线缆用来实现通用相机控制,它们被定义

为相机的输入信号和图像采集卡的输出信号。一般情况是这些信号命名为:

CameraControl1(CC1)

CameraControl2(CC2)

CameraControl3(CC3)

CameraControl4(CC4)

图 9 相机控制信号作用及定义

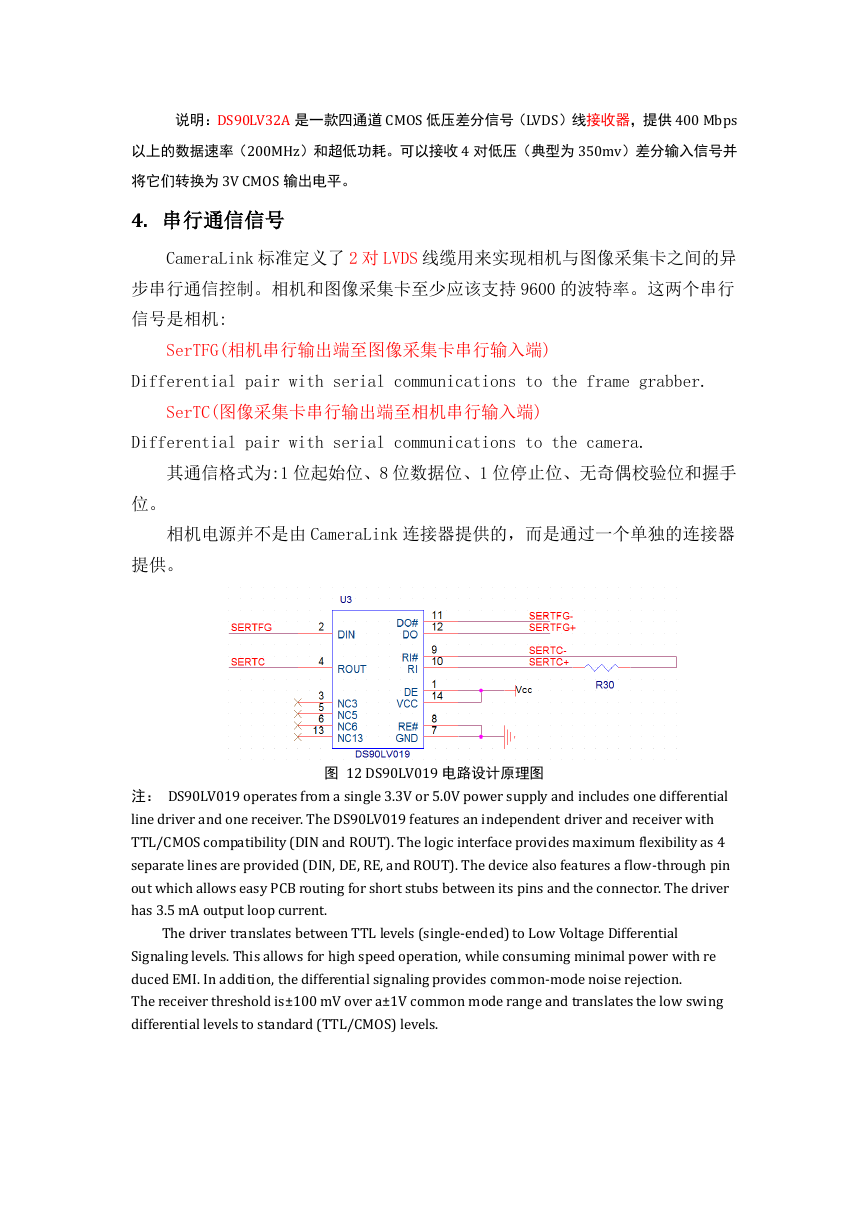

下图是 3V LVDS 四通道 CMOS 差分线驱动器 DS90LV031A 和接收器 DS90LV032A

的原理图:

图 10 DS90LV31A 电路设计原理图

DS90LV31A 为四通道 CMOS 低压差分信号(LVDS)线驱动器,两种芯片配合使用。接收

低压 TTL 或低压 CMOS 输入电平并将其转化为低压(350mv)差分输出信号。

图 11 DS90LV032A 电路设计原理图

�

说明:DS90LV32A 是一款四通道 CMOS 低压差分信号(LVDS)线接收器,提供 400 Mbps

以上的数据速率(200MHz)和超低功耗。可以接收 4 对低压(典型为 350mv)差分输入信号并

将它们转换为 3V CMOS 输出电平。

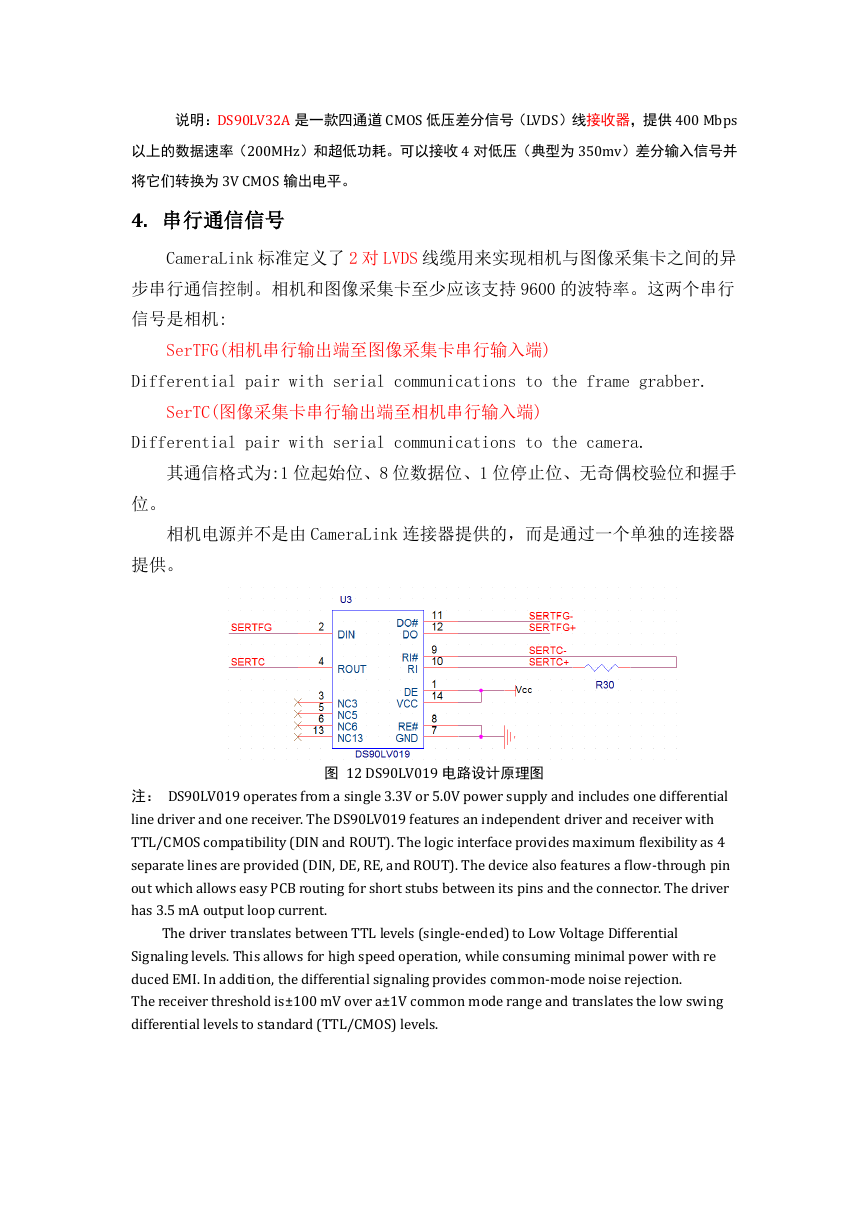

4. 串行通信信号

CameraLink 标准定义了 2 对 LVDS 线缆用来实现相机与图像采集卡之间的异

步串行通信控制。相机和图像采集卡至少应该支持 9600 的波特率。这两个串行

信号是相机:

SerTFG(相机串行输出端至图像采集卡串行输入端)

Differential pair with serial communications to the frame grabber.

SerTC(图像采集卡串行输出端至相机串行输入端)

Differential pair with serial communications to the camera.

其通信格式为:1 位起始位、8 位数据位、1 位停止位、无奇偶校验位和握手

位。

相机电源并不是由 CameraLink 连接器提供的,而是通过一个单独的连接器

提供。

图 12 DS90LV019 电路设计原理图

注: DS90LV019 operates from a single 3.3V or 5.0V power supply and includes one differential

line driver and one receiver. The DS90LV019 features an independent driver and receiver with

TTL/CMOS compatibility (DIN and ROUT). The logic interface provides maximum flexibility as 4

separate lines are provided (DIN, DE, RE, and ROUT). The device also features a flow-through pin

out which allows easy PCB routing for short stubs between its pins and the connector. The driver

has 3.5 mA output loop current.

The driver translates between TTL levels (single-ended) to Low Voltage Differential

Signaling levels. This allows for high speed operation, while consuming minimal power with re

duced EMI. In addition, the differential signaling provides common-mode noise rejection.

The receiver threshold is±100 mV over a±1V common mode range and translates the low swing

differential levels to standard (TTL/CMOS) levels.

�

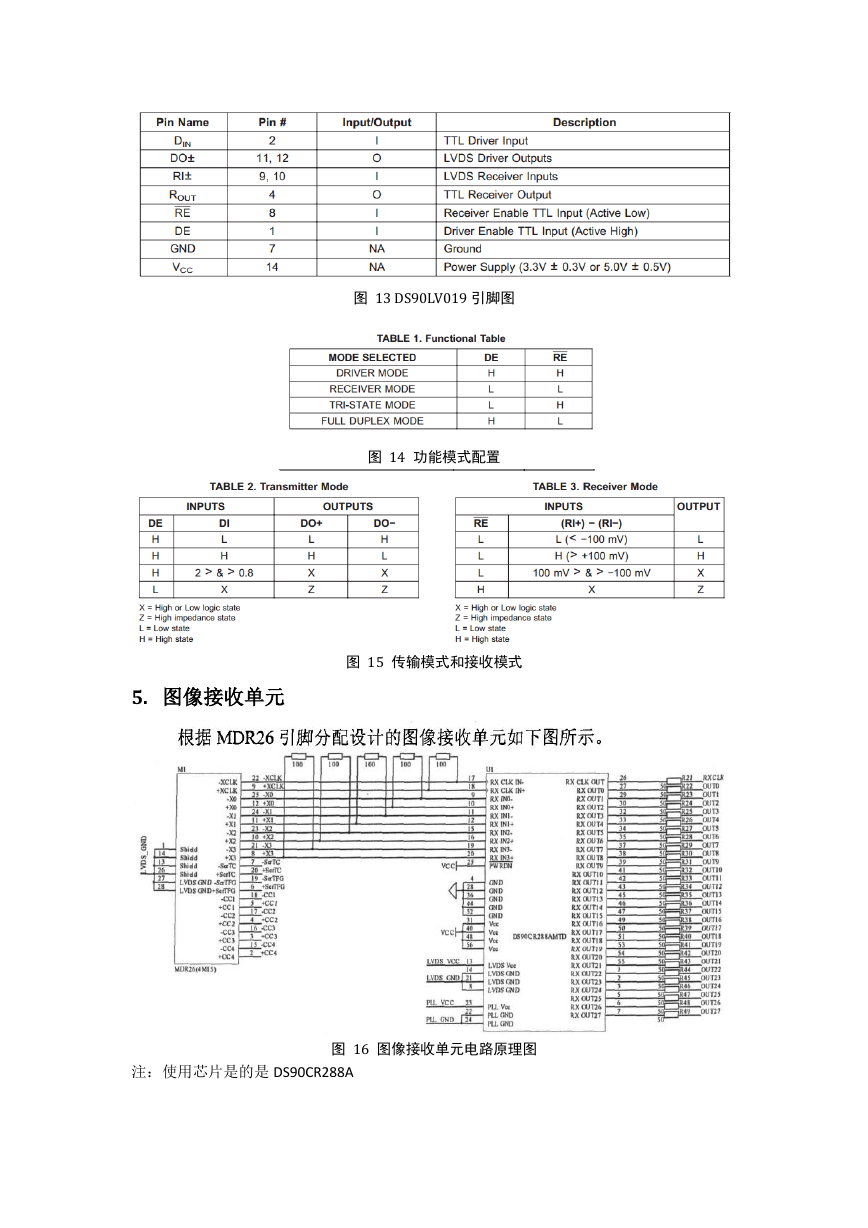

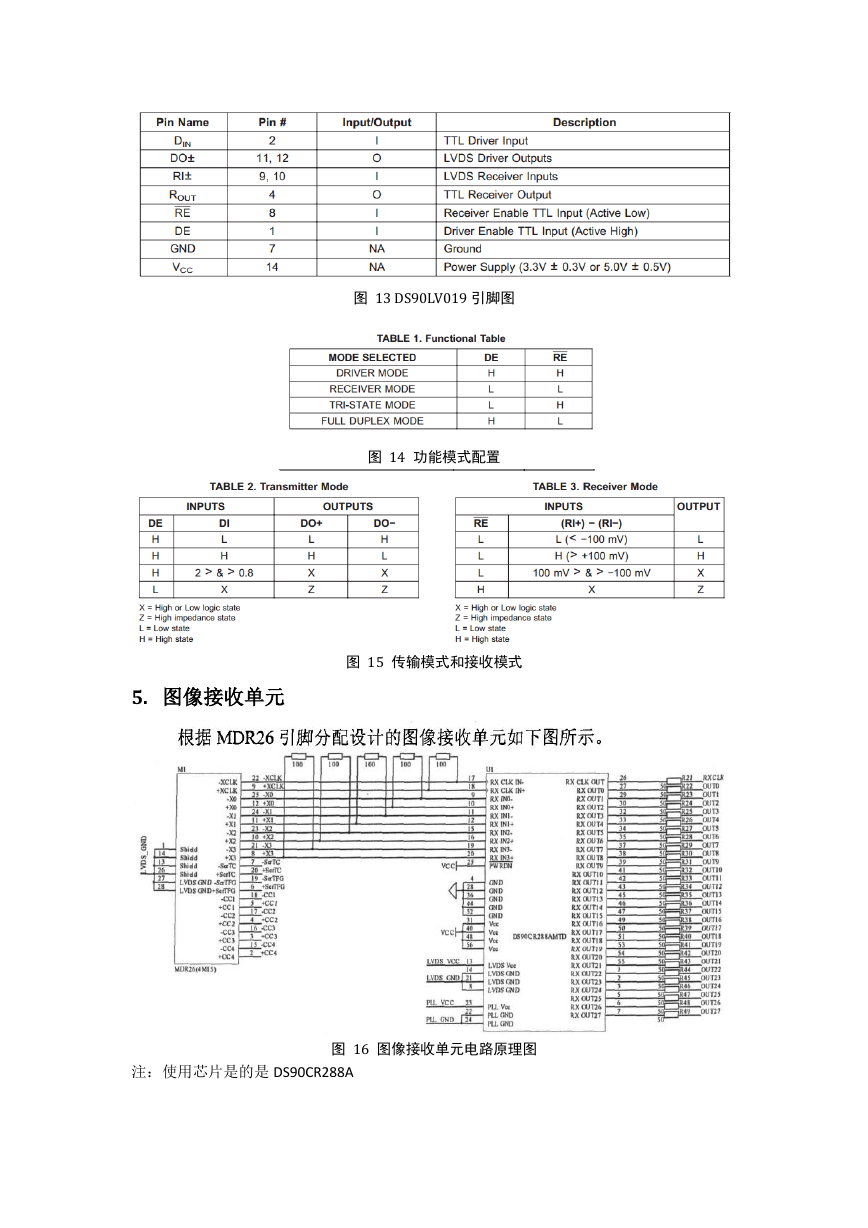

图 13 DS90LV019 引脚图

图 14 功能模式配置

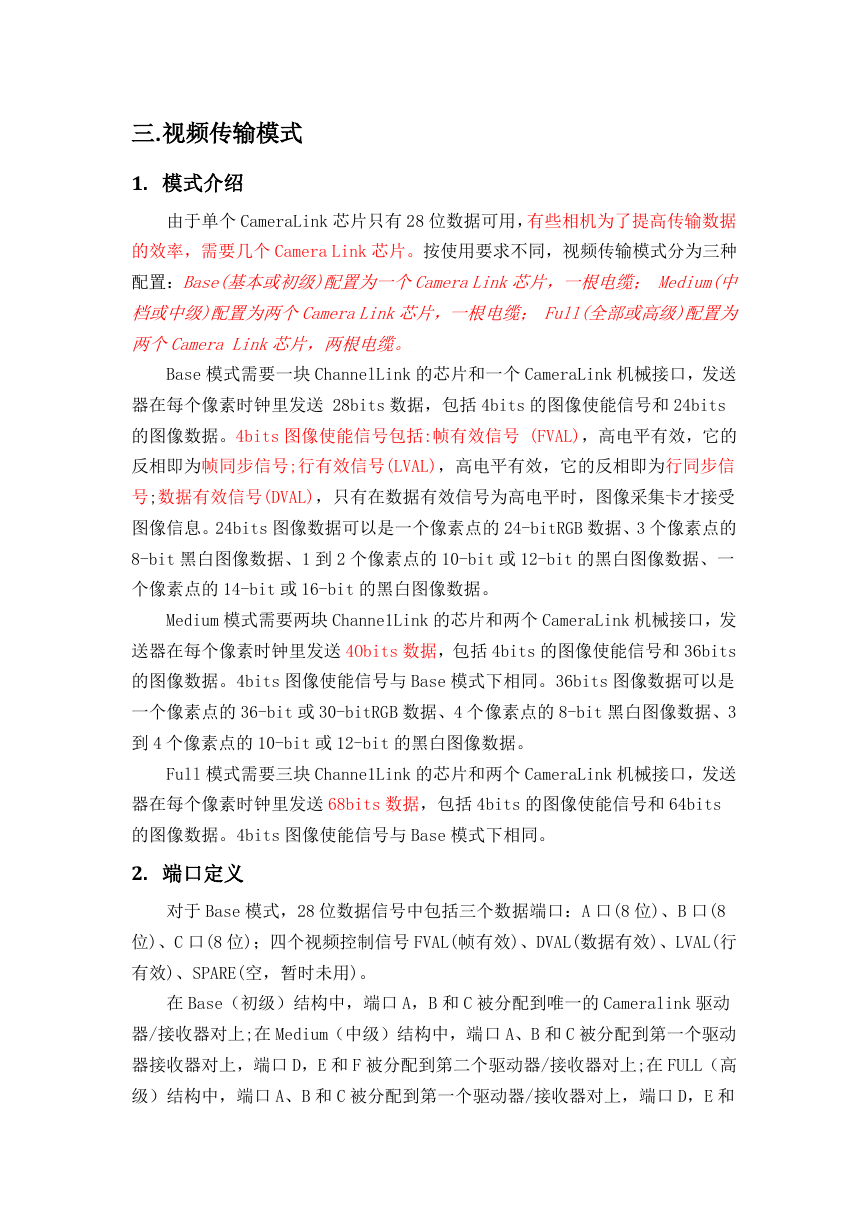

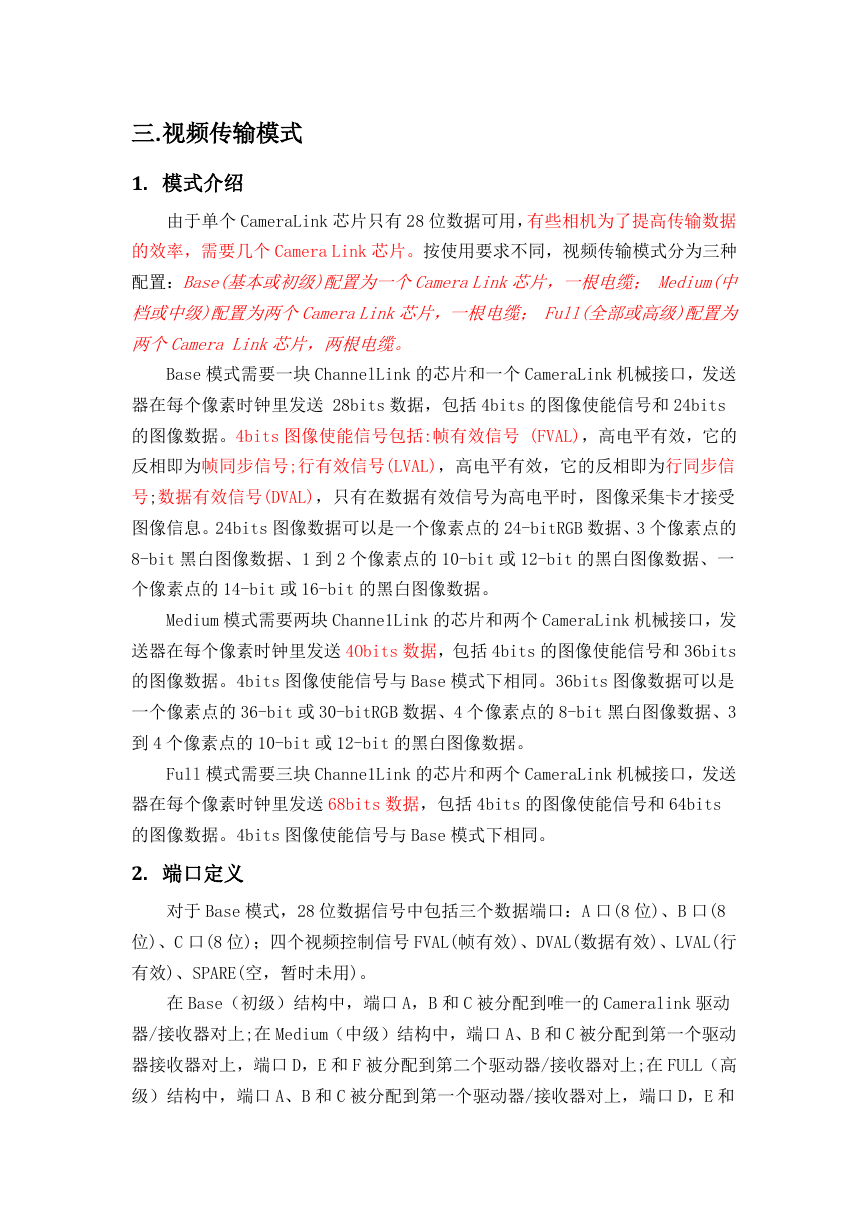

5. 图像接收单元

图 15 传输模式和接收模式

注:使用芯片是的是 DS90CR288A

图 16 图像接收单元电路原理图

�

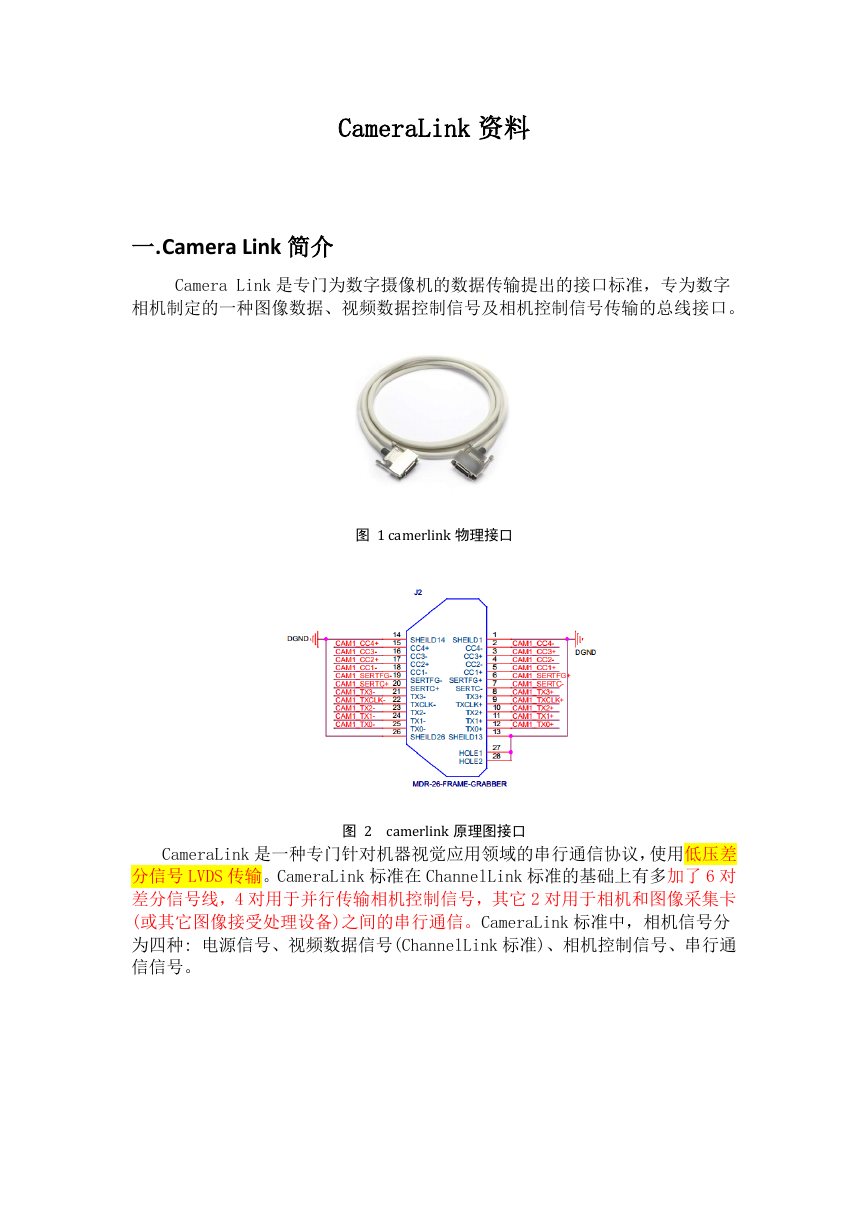

三. 视频传输模式

1. 模式介绍

由于单个 CameraLink 芯片只有 28 位数据可用,有些相机为了提高传输数据

的效率,需要几个 Camera Link 芯片。按使用要求不同,视频传输模式分为三种

配置:Base(基本或初级)配置为一个Camera Link芯片,一根电缆; Medium(中

档或中级)配置为两个Camera Link芯片,一根电缆; Full(全部或高级)配置为

两个Camera Link芯片,两根电缆。

Base 模式需要一块 ChannelLink 的芯片和一个 CameraLink 机械接口,发送

器在每个像素时钟里发送 28bits 数据,包括 4bits 的图像使能信号和 24bits

的图像数据。4bits 图像使能信号包括:帧有效信号 (FVAL),高电平有效,它的

反相即为帧同步信号;行有效信号(LVAL),高电平有效,它的反相即为行同步信

号;数据有效信号(DVAL),只有在数据有效信号为高电平时,图像采集卡才接受

图像信息。24bits 图像数据可以是一个像素点的 24-bitRGB 数据、3 个像素点的

8-bit 黑白图像数据、1 到 2 个像素点的 10-bit 或 12-bit 的黑白图像数据、一

个像素点的 14-bit 或 16-bit 的黑白图像数据。

Medium 模式需要两块 Channe1Link 的芯片和两个 CameraLink 机械接口,发

送器在每个像素时钟里发送 4Obits 数据,包括 4bits 的图像使能信号和 36bits

的图像数据。4bits 图像使能信号与 Base 模式下相同。36bits 图像数据可以是

一个像素点的 36-bit 或 30-bitRGB 数据、4 个像素点的 8-bit 黑白图像数据、3

到 4 个像素点的 10-bit 或 12-bit 的黑白图像数据。

Full 模式需要三块 Channe1Link 的芯片和两个 CameraLink 机械接口,发送

器在每个像素时钟里发送 68bits 数据,包括 4bits 的图像使能信号和 64bits

的图像数据。4bits 图像使能信号与 Base 模式下相同。

2. 端口定义

对于 Base 模式,28 位数据信号中包括三个数据端口:A 口(8 位)、B 口(8

位)、C 口(8 位);四个视频控制信号 FVAL(帧有效)、DVAL(数据有效)、LVAL(行

有效)、SPARE(空,暂时未用)。

在 Base(初级)结构中,端口 A,B 和 C 被分配到唯一的 Cameralink 驱动

器/接收器对上;在 Medium(中级)结构中,端口 A、B 和 C 被分配到第一个驱动

器接收器对上,端口 D,E 和 F 被分配到第二个驱动器/接收器对上;在 FULL(高

级)结构中,端口 A、B 和 C 被分配到第一个驱动器/接收器对上,端口 D,E 和

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc