Verilog 的的`include用法详解

用法详解

最近在看彬哥的程序,看到彬哥把`include用的很酷,还有看xzy610030。博客说道,华为FPGA面试居然也问

道了`include的用法,这里就总结一下。引用彬哥的一句话,不总结的人生等于白活~~

话说Verilog 的`include和C语言的include用法是一样一样的,要说区别可能就在于那个点吧。

include一般就是包含一个文件,对于Verilog这个文件里的内容无非是一些参数定义,所以这里再提几个关键字:`ifdef `define

`endif(他们都带个点,呵呵)。

他们联合起来使用,确实能让你的程序多样化,就拿彬哥VGA程序说事吧。

首先,你可以新建一个.h文件(可以直接新建一个TXT,让后将后缀换成.h)其实这个后缀没所谓,.v也是可以的,我觉得,

写成.h更能体现出这个文件的意义。

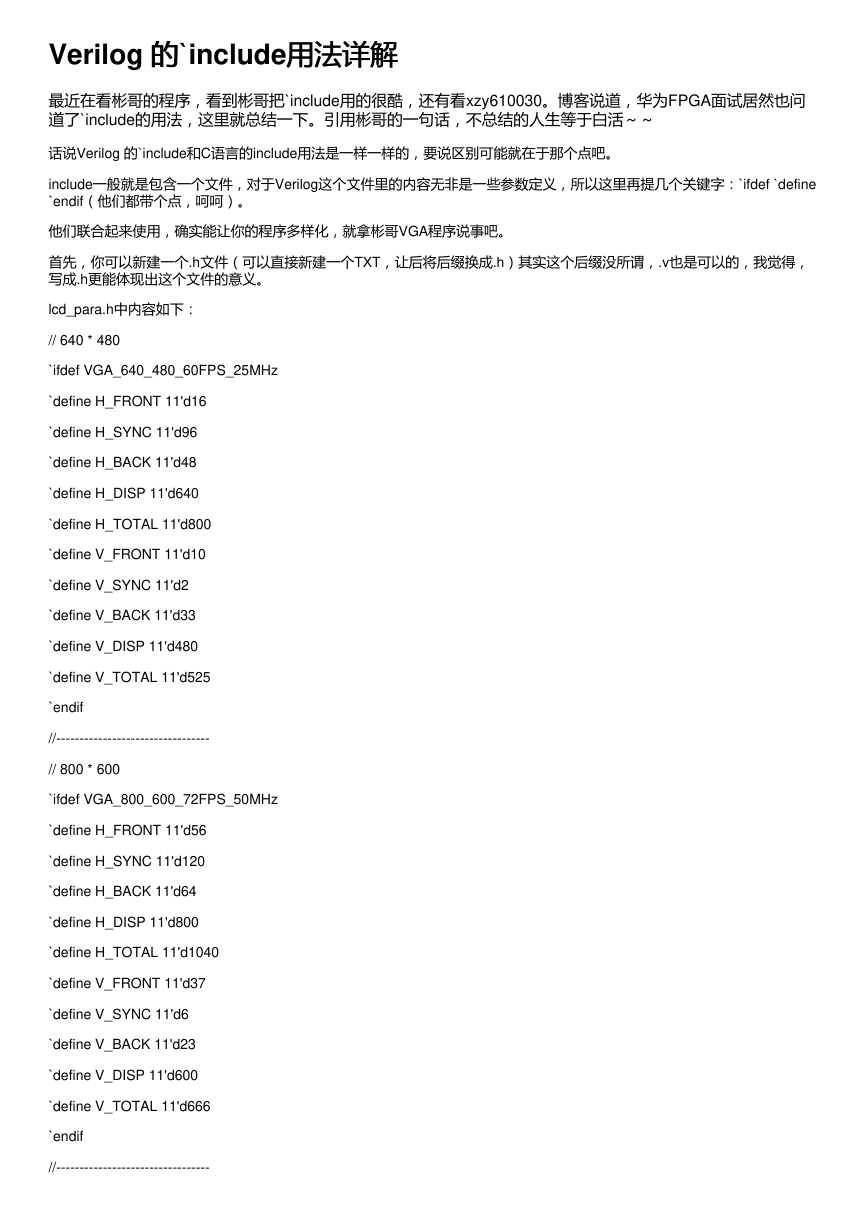

lcd_para.h中内容如下:

// 640 * 480

`ifdef VGA_640_480_60FPS_25MHz

`define H_FRONT 11'd16

`define H_SYNC 11'd96

`define H_BACK 11'd48

`define H_DISP 11'd640

`define H_TOTAL 11'd800

`define V_FRONT 11'd10

`define V_SYNC 11'd2

`define V_BACK 11'd33

`define V_DISP 11'd480

`define V_TOTAL 11'd525

`endif

//---------------------------------

// 800 * 600

`ifdef VGA_800_600_72FPS_50MHz

`define H_FRONT 11'd56

`define H_SYNC 11'd120

`define H_BACK 11'd64

`define H_DISP 11'd800

`define H_TOTAL 11'd1040

`define V_FRONT 11'd37

`define V_SYNC 11'd6

`define V_BACK 11'd23

`define V_DISP 11'd600

`define V_TOTAL 11'd666

`endif

//---------------------------------

�

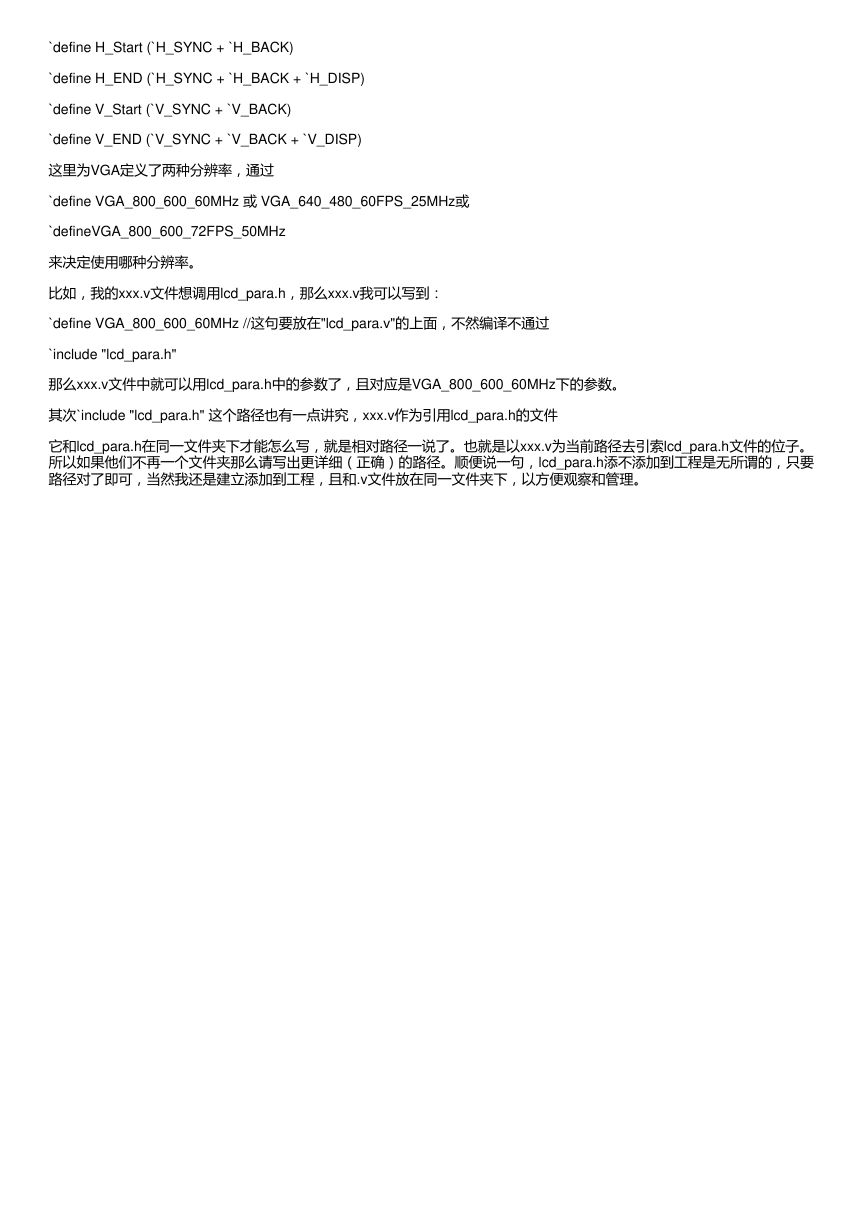

`define H_Start (`H_SYNC + `H_BACK)

`define H_END (`H_SYNC + `H_BACK + `H_DISP)

`define V_Start (`V_SYNC + `V_BACK)

`define V_END (`V_SYNC + `V_BACK + `V_DISP)

这里为VGA定义了两种分辨率,通过

`define VGA_800_600_60MHz 或 VGA_640_480_60FPS_25MHz或

`defineVGA_800_600_72FPS_50MHz

来决定使用哪种分辨率。

比如,我的xxx.v文件想调用lcd_para.h,那么xxx.v我可以写到:

`define VGA_800_600_60MHz //这句要放在"lcd_para.v"的上面,不然编译不通过

`include "lcd_para.h"

那么xxx.v文件中就可以用lcd_para.h中的参数了,且对应是VGA_800_600_60MHz下的参数。

其次`include "lcd_para.h" 这个路径也有一点讲究,xxx.v作为引用lcd_para.h的文件

它和lcd_para.h在同一文件夹下才能怎么写,就是相对路径一说了。也就是以xxx.v为当前路径去引索lcd_para.h文件的位子。

所以如果他们不再一个文件夹那么请写出更详细(正确)的路径。顺便说一句,lcd_para.h添不添加到工程是无所谓的,只要

路径对了即可,当然我还是建立添加到工程,且和.v文件放在同一文件夹下,以方便观察和管理。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc