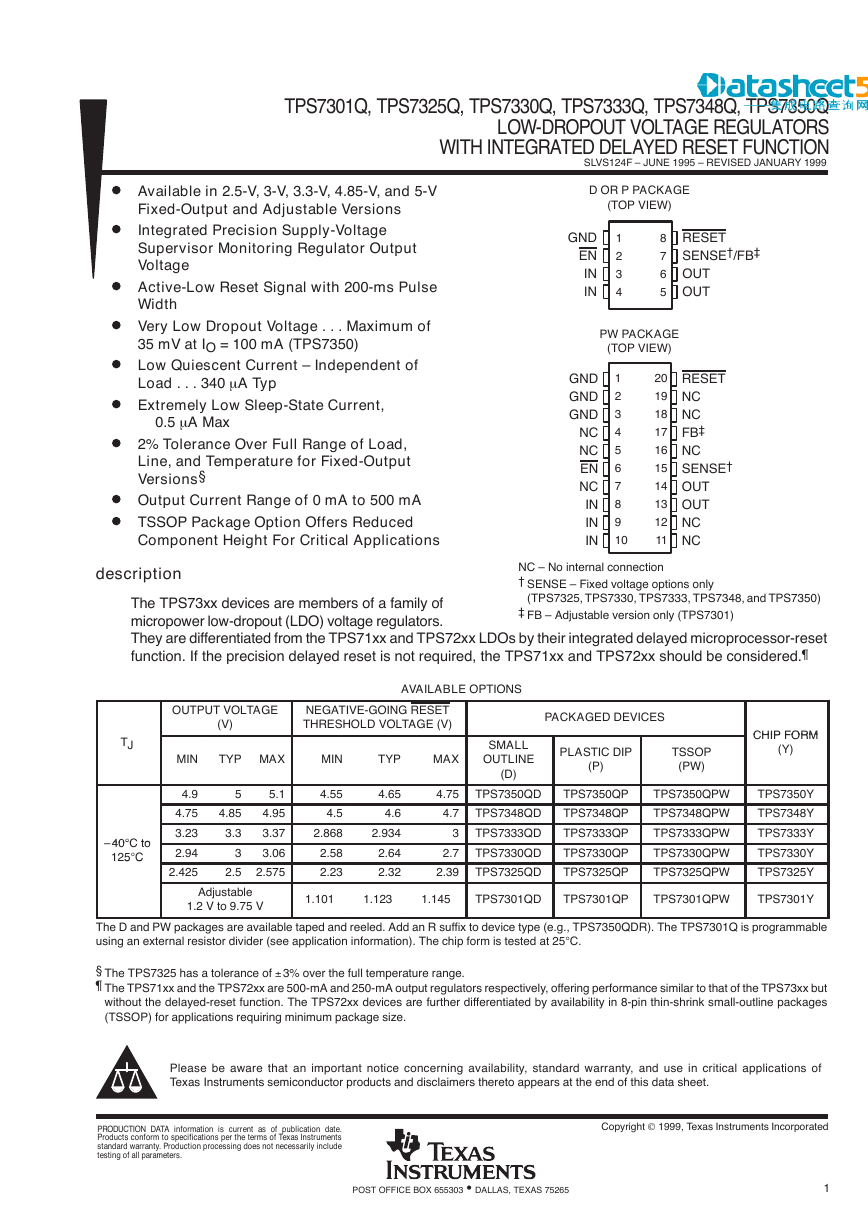

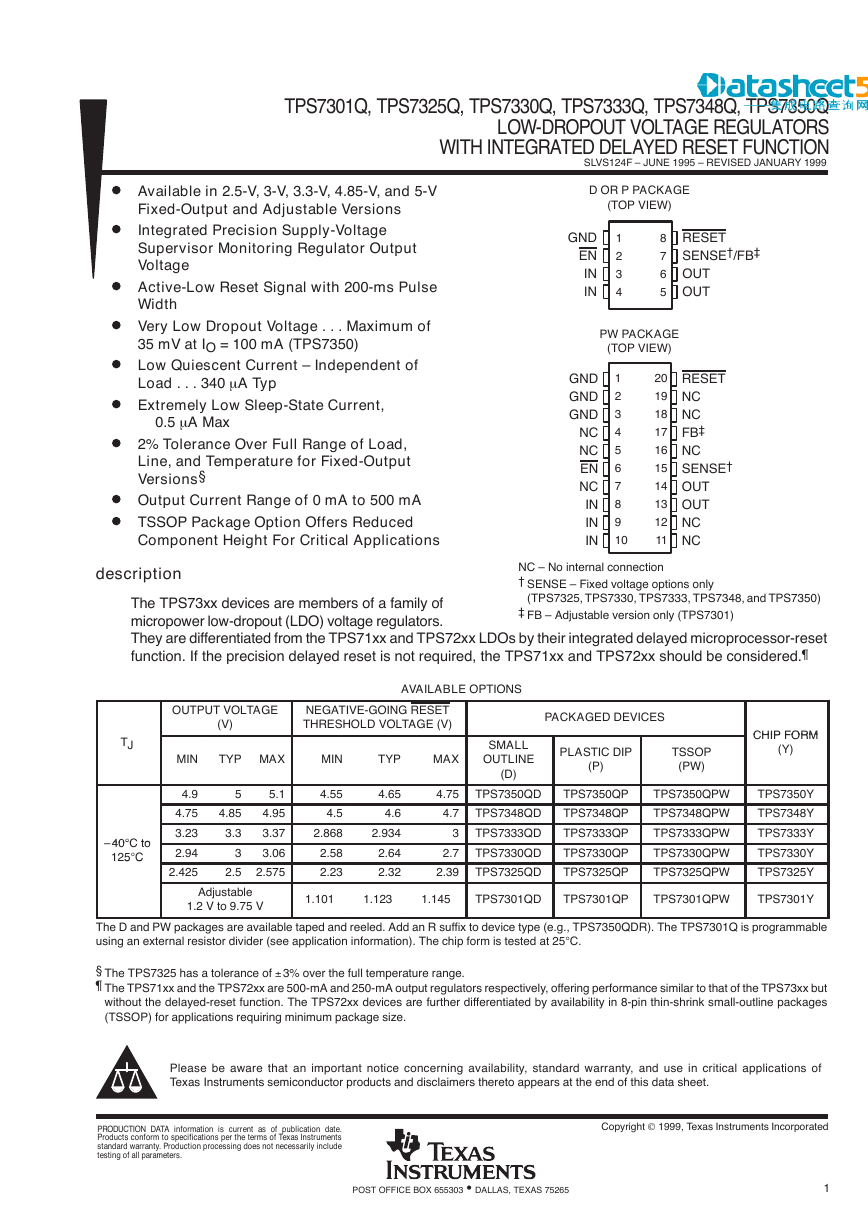

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350QLOW-DROPOUT VOLTAGE REGULATORSWITH INTEGRATED DELAYED RESET FUNCTION SLVS124F – JUNE 1995 – REVISED JANUARY 19991POST OFFICE BOX 655303 • DALLAS, TEXAS 75265DAvailable in 2.5-V, 3-V, 3.3-V, 4.85-V, and 5-VFixed-Output and Adjustable VersionsDIntegrated Precision Supply-VoltageSupervisor Monitoring Regulator OutputVoltageDActive-Low Reset Signal with 200-ms PulseWidthDVery Low Dropout Voltage...Maximum of35 mV at IO = 100 mA (TPS7350)DLow Quiescent Current – Independent ofLoad...340 mA TypDExtremely Low Sleep-State Current,0.5 mA MaxD2% Tolerance Over Full Range of Load,Line, and Temperature for Fixed-OutputVersions§DOutput Current Range of 0 mA to 500 mADTSSOP Package Option Offers ReducedComponent Height For Critical Applications descriptionThe TPS73xx devices are members of a family ofmicropower low-dropout (LDO) voltage regulators.They are differentiated from the TPS71xx and TPS72xx LDOs by their integrated delayed microprocessor-resetfunction. If the precision delayed reset is not required, the TPS71xx and TPS72xx should be considered.¶AVAILABLE OPTIONSOUTPUT VOLTAGE(V)NEGATIVE-GOING RESETTHRESHOLD VOLTAGE (V)PACKAGED DEVICESCHIPFORMTJMINTYPMAXMINTYPMAXSMALLOUTLINE(D)PLASTIC DIP(P)TSSOP(PW)CHIP FORM(Y)4.955.14.554.654.75TPS7350QDTPS7350QPTPS7350QPWTPS7350Y4.754.854.954.54.64.7TPS7348QDTPS7348QPTPS7348QPWTPS7348Y40°Cto3.233.33.372.8682.9343TPS7333QDTPS7333QPTPS7333QPWTPS7333Y–40°C to125°C2.9433.062.582.642.7TPS7330QDTPS7330QPTPS7330QPWTPS7330Y125C2.4252.52.5752.232.322.39TPS7325QDTPS7325QPTPS7325QPWTPS7325YAdjustable1.2 V to 9.75 V1.1011.1231.145TPS7301QDTPS7301QPTPS7301QPWTPS7301YThe D and PW packages are available taped and reeled. Add an R suffix to device type (e.g., TPS7350QDR). The TPS7301Q is programmableusing an external resistor divider (see application information). The chip form is tested at 25°C.§The TPS7325 has a tolerance of ±3% over the full temperature range.¶The TPS71xx and the TPS72xx are 500-mA and 250-mA output regulators respectively, offering performance similar to that of the TPS73xx butwithout the delayed-reset function. The TPS72xx devices are further differentiated by availability in 8-pin thin-shrink small-outline packages(TSSOP) for applications requiring minimum package size.Please be aware that an important notice concerning availability, standard warranty, and use in critical applications ofTexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.Copyright 1999, Texas Instruments IncorporatedPRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instrumentsstandard warranty. Production processing does not necessarily includetesting of all parameters.1234 567891020191817161514131211GNDGNDGNDNCNCENNCINININRESETNCNCFB‡NCSENSE†OUTOUTNCNCPW PACKAGE(TOP VIEW)NC – No internal connection†SENSE – Fixed voltage options only(TPS7325, TPS7330, TPS7333, TPS7348, and TPS7350)‡FB – Adjustable version only (TPS7301)12348765GNDENININRESETSENSE†/FB‡OUTOUTD OR P PACKAGE(TOP VIEW)�

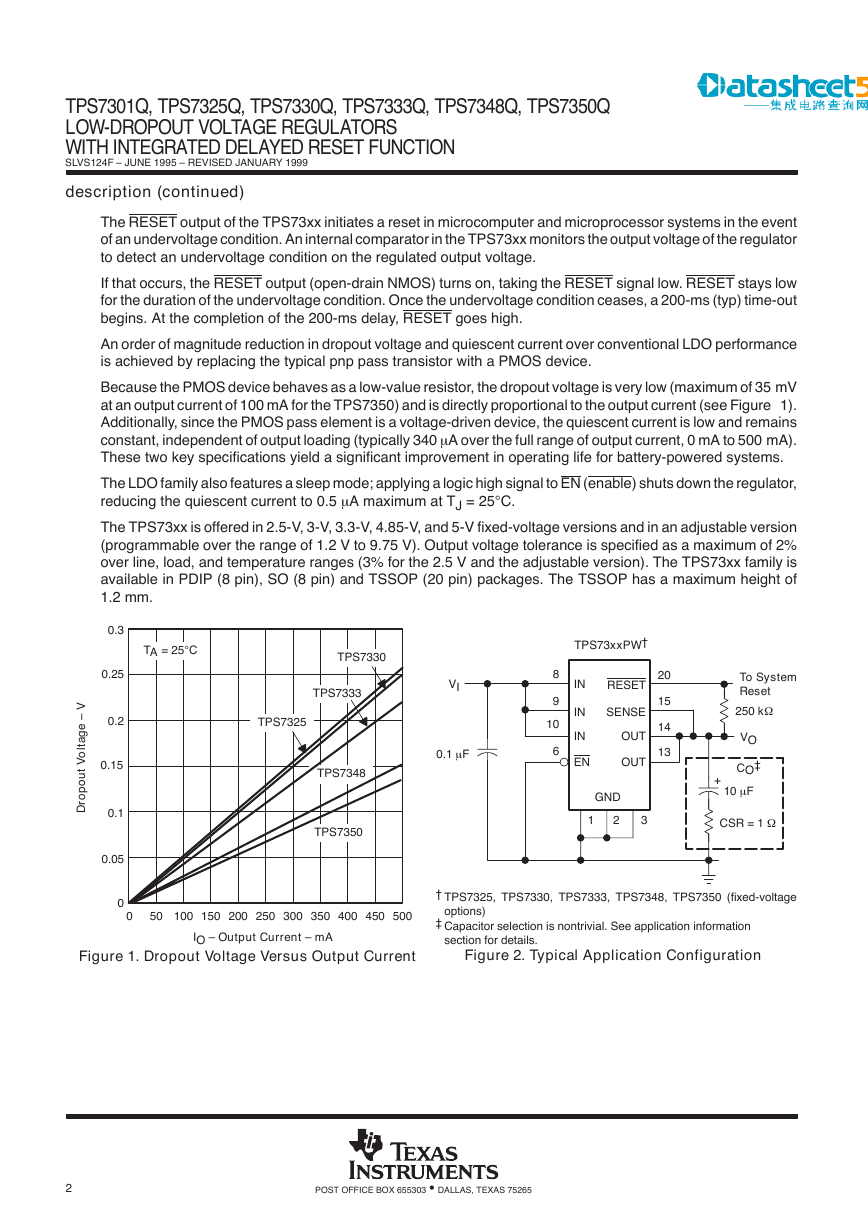

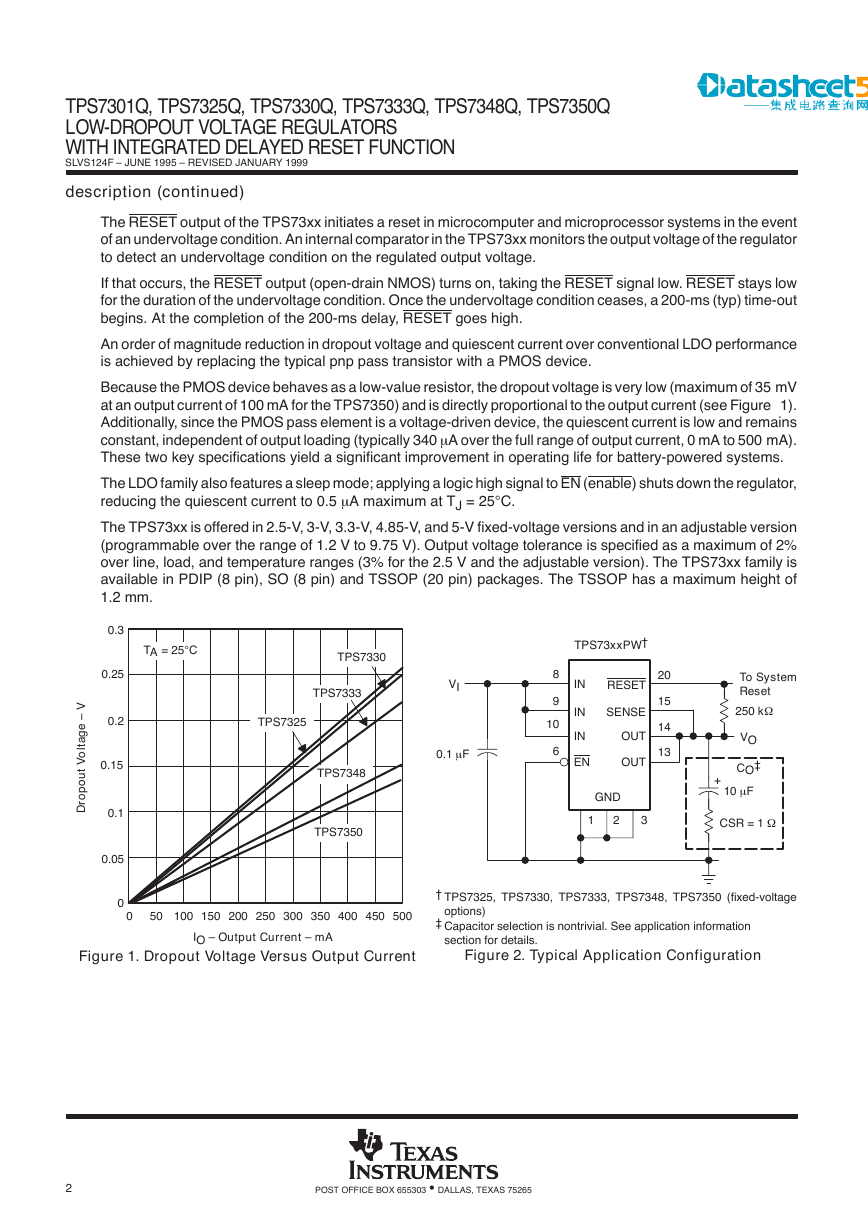

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350QLOW-DROPOUT VOLTAGE REGULATORSWITH INTEGRATED DELAYED RESET FUNCTION SLVS124F – JUNE 1995 – REVISED JANUARY 19992POST OFFICE BOX 655303 • DALLAS, TEXAS 75265description (continued)The RESET output of the TPS73xx initiates a reset in microcomputer and microprocessor systems in the eventof an undervoltage condition. An internal comparator in the TPS73xx monitors the output voltage of the regulatorto detect an undervoltage condition on the regulated output voltage.If that occurs, the RESET output (open-drain NMOS) turns on, taking the RESET signal low. RESET stays lowfor the duration of the undervoltage condition. Once the undervoltage condition ceases, a 200-ms (typ) time-outbegins. At the completion of the 200-ms delay, RESET goes high.An order of magnitude reduction in dropout voltage and quiescent current over conventional LDO performanceis achieved by replacing the typical pnp pass transistor with a PMOS device.Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (maximum of 35mVat an output current of 100 mA for the TPS7350) and is directly proportional to the output current (see Figure1).Additionally, since the PMOS pass element is a voltage-driven device, the quiescent current is low and remainsconstant, independent of output loading (typically 340 mA over the full range of output current, 0 mA to 500mA).These two key specifications yield a significant improvement in operating life for battery-powered systems.The LDO family also features a sleep mode; applying a logic high signal to EN (enable) shuts down the regulator,reducing the quiescent current to 0.5 mA maximum at TJ = 25°C.The TPS73xx is offered in 2.5-V, 3-V, 3.3-V, 4.85-V, and 5-V fixed-voltage versions and in an adjustable version(programmable over the range of 1.2 V to 9.75 V). Output voltage tolerance is specified as a maximum of 2%over line, load, and temperature ranges (3% for the 2.5 V and the adjustable version). The TPS73xx family isavailable in PDIP (8 pin), SO (8 pin) and TSSOP (20 pin) packages. The TSSOP has a maximum height of1.2mm.Figure 1. Dropout Voltage Versus Output Current0.250.20.10.0500.150501001502002503000.3350400450500TA = 25°CTPS7348TPS7350Dropout Voltage – VIO – Output Current – mATPS7333TPS7330TPS7325Figure 2. Typical Application Configuration†TPS7325, TPS7330, TPS7333, TPS7348, TPS7350 (fixed-voltageoptions)‡Capacitor selection is nontrivial. See application informationsection for details.SENSERESETOUTOUT98610INININENGND32120151413VI0.1 mFTo SystemResetCSR = 1 WVO10 mF+TPS73xxPW†CO‡250 kW�

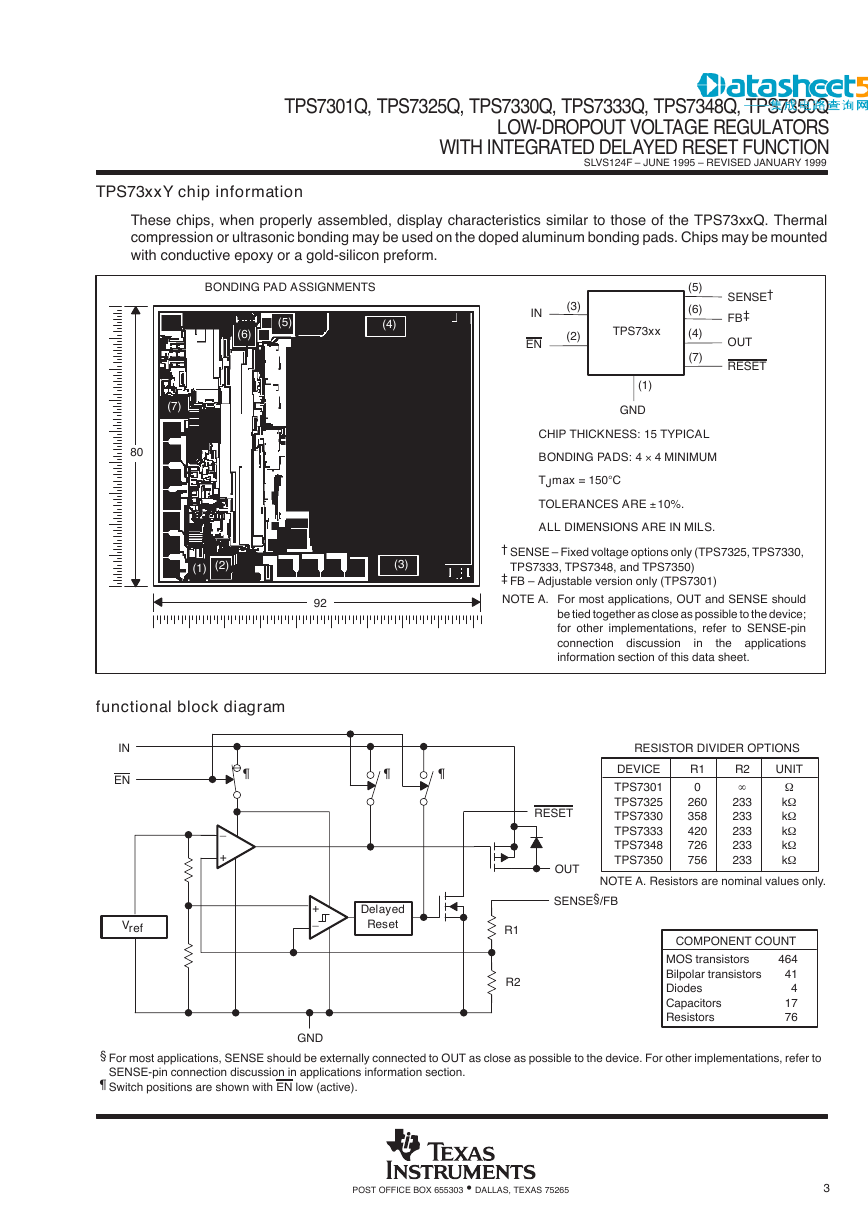

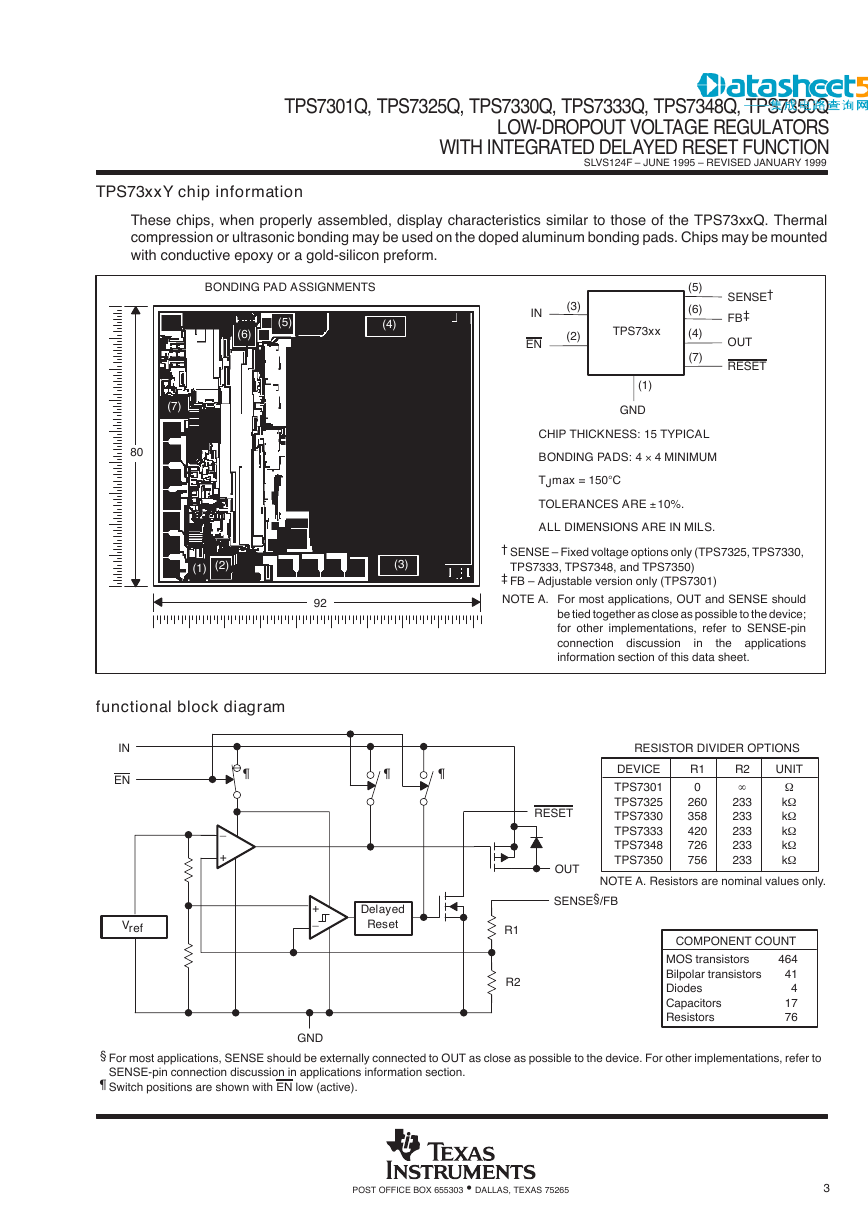

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350QLOW-DROPOUT VOLTAGE REGULATORSWITH INTEGRATED DELAYED RESET FUNCTION SLVS124F – JUNE 1995 – REVISED JANUARY 19993POST OFFICE BOX 655303 • DALLAS, TEXAS 75265TPS73xxY chip informationThese chips, when properly assembled, display characteristics similar to those of the TPS73xxQ. Thermalcompression or ultrasonic bonding may be used on the doped aluminum bonding pads. Chips may be mountedwith conductive epoxy or a gold-silicon preform.(6)(4)(3)(7)(2)(1)GNDFB‡OUTRESETINENTPS73xx8092CHIP THICKNESS: 15 TYPICALBONDING PADS: 4 × 4 MINIMUMTJmax = 150°CTOLERANCES ARE ±10%.ALL DIMENSIONS ARE IN MILS.†SENSE – Fixed voltage options only (TPS7325, TPS7330,TPS7333, TPS7348, and TPS7350)‡FB – Adjustable version only (TPS7301)BONDING PAD ASSIGNMENTSSENSE†(5)NOTE A.For most applications, OUT and SENSE shouldbe tied together as close as possible to the device;for other implementations, refer to SENSE-pinconnection discussion in the applicationsinformation section of this data sheet.(3)(4)(5)(6)(7)(2)(1)functional block diagram¶_+VrefOUTSENSE§/FBENINGNDR1R2RESET_+TPS7301TPS7325TPS7330TPS7333TPS7348TPS7350DEVICEUNITR1R20260358420726756∞233233233233233WkWkWkWkWkWRESISTOR DIVIDER OPTIONS§For most applications, SENSE should be externally connected to OUT as close as possible to the device. For other implementations, refer toSENSE-pin connection discussion in applications information section.¶Switch positions are shown with EN low (active).NOTE A. Resistors are nominal values only.DelayedReset¶¶MOS transistorsBilpolar transistorsDiodesCapacitorsResistorsCOMPONENT COUNT4644141776�

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350QLOW-DROPOUT VOLTAGE REGULATORSWITH INTEGRATED DELAYED RESET FUNCTION SLVS124F – JUNE 1995 – REVISED JANUARY 19994POST OFFICE BOX 655303 • DALLAS, TEXAS 75265timing diagram†Vres is the minimum input voltage for a valid RESET. The symbol Vres is not currently listed within EIA or JEDEC standardsfor semiconductor symbology.ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎVIVres†VrestttVOThresholdVoltageRESETOutput200 msDelay200 msDelayOutputUndefinedOutputUndefinedVIT+VIT–VIT–VIT+absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡Input voltage range§, VI, RESET, SENSE, EN –0.3 V to 11 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Output current, IO 2 A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Continuous total power dissipation See Dissipation Rating Tables 1 and 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . Operating virtual junction temperature range, TJ –55°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Storage temperature range, Tstg –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ‡Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, andfunctional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is notimplied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.§All voltage values are with respect to network terminal ground.�

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350QLOW-DROPOUT VOLTAGE REGULATORSWITH INTEGRATED DELAYED RESET FUNCTION SLVS124F – JUNE 1995 – REVISED JANUARY 19995POST OFFICE BOX 655303 • DALLAS, TEXAS 75265DISSIPATION RATING TABLE 1 – FREE-AIR TEMPERATURE (SEE FIGURE 3)PACKAGETA ≤ 25°CDERATING FACTORTA = 70°CTA = 125°CPACKAGEAPOWER RATINGABOVE TA = 25°CAPOWER RATINGAPOWER RATINGD725 mW5.8 mW/°C464 mW145 mWP1175 mW9.4 mW/°C752 mW235 mWPW†700 mW5.6 mW/°C448 mW140 mWDISSIPATION RATING TABLE 2 – CASE TEMPERATURE (SEE FIGURE 4)PACKAGETC ≤ 25°CDERATING FACTORTC = 70°CTC = 125°CPACKAGECPOWER RATINGABOVE TC = 25°CCPOWER RATINGCPOWER RATINGD2188 mW9.4 mW/°C1765 mW1248 mWP2738 mW21.9 mW/°C1752 mW548 mWPW†4025 mW32.2 mW/°C2576 mW805 mW†Refer to Thermal Information section for detailed power dissipation considerations when using theTSSOP package.Figure 3PW PackageRqJA = 178°C/W12008004000255075100– Maximum Continuous Dissipation – mWMAXIMUM CONTINUOUS DISSIPATIONvsFREE-AIR TEMPERATURE12515014001000600200PDTA – Free-Air Temperature – °CD PackageRqJA = 172°C/WP PackageRqJA = 106°C/WFigure 4240016008000255075100– Maximum Continuous Dissipation – mW32004000MAXIMUM CONTINUOUS DISSIPATIONvsCASE TEMPERATURE480012515044003600280020001200400PDTC – Case Temperature – °CD PackageRqJC = 57°C/WP PackageRqJC = 46°C/WPW PackageRqJC = 37°C/W�

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350QLOW-DROPOUT VOLTAGE REGULATORSWITH INTEGRATED DELAYED RESET FUNCTION SLVS124F – JUNE 1995 – REVISED JANUARY 19996POST OFFICE BOX 655303 • DALLAS, TEXAS 75265recommended operating conditionsMINMAXUNIT†TPS7301Q2.4710V†TPS7325Q3.110VInputvoltageVI†TPS7330Q3.510VInput voltage, VI†TPS7333Q3.7710TPS7348Q5.210VTPS7350Q5.3310High-level input voltage at EN, VIH2VLow-level input voltage at EN, VIL0.5VOutput current range, IO0500mAOperating virtual junction temperature range, TJ–40125°C†Minimum input voltage defined in the recommended operating conditions is the maximum specified output voltage plus dropout voltage, VDO,at the maximum specified load range. Since dropout voltage is a function of output current, the usable range can be extended for lighter loads.To calculate the minimum input voltage for the maximum load current used in a given application, use the following equation:VI(min)+VO(max))VDO(maxload)Because the TPS7301 is programmable, rDS(on) should be used to calculate VDO before applying the above equation. The equation for calculatingVDO from rDS(on) is given in Note 2 in the TPS7301 electrical characteristics table. The minimum value of 2.97 V is the absolute lower limit forthe recommended input voltage range for the TPS7301.�

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350QLOW-DROPOUT VOLTAGE REGULATORSWITH INTEGRATED DELAYED RESET FUNCTION SLVS124F – JUNE 1995 – REVISED JANUARY 19997POST OFFICE BOX 655303 • DALLAS, TEXAS 75265electrical characteristics at IO = 10 mA, EN = 0 V, Co = 4.7 mF (CSR‡ = 1 W), SENSE/FB shorted toOUT (unless otherwise noted)PARAMETERTEST CONDITIONS§TJMINTYPMAXUNITGroundcurrent(activemode)EN ≤ 0.5 V, VI = VO + 1 V,25°C340400mAGround current (active mode)EN ≤ 0.5 V, VI VO + 1 V,0 mA ≤ IO ≤ 500 mA–40°C to 125°C550mAInputcurrent(standbymode)ENV27V≤V≤10V25°C0.010.5mAInput current (standby mode)EN = VI,2.7 V ≤ VI ≤ 10 V–40°C to 125°C2mAOutputcurrentlimitVO=0VVI=10V25°C1.22AOutput current limitVO = 0 V,VI = 10 V–40°C to 125°C2APass-element leakage current in standbyENV27V≤V≤10V25°C0.010.5mAgymodeEN = VI,2.7 V ≤ VI ≤ 10 V–40°C to 125°C1mARESETleakagecurrentNormaloperationVatRESET10V25°C0.020.5mARESET leakage currentNormal operation,V at RESET = 10 V–40°C to 125°C0.5mAOutput voltage temperature coefficient–40°C to 125°C6175ppm/°CThermal shutdown junction temperature165°CENlogichigh(standbymode)2.5 V ≤ VI ≤ 6 V40°Cto125°C2VEN logic high (standby mode)6 V ≤ VI ≤ 10 V–40°C to 125°C2.7VENlogiclow(activemode)27V≤VI≤10V25°C0.5VEN logic low (active mode)2.7 V ≤ VI ≤ 10 V–40°C to 125°C0.5VEN hysteresis voltage25°C50mVENinputcurrent0V≤VI≤10V25°C–0.50.0010.5mAEN input current0 V ≤ VI ≤ 10 V–40°C to 125°C–0.50.5mAMinimumVIforactivepasselement25°C2.052.5VMinimum VI for active pass element–40°C to 125°C2.5VMinimumVIforvalidRESETIO(RESET)=300mA25°C11.5VMinimum VI for valid RESETIO(RESET) = –300 mA–40°C to 125°C1.9V‡CSR (compensation series resistance) refers to the total series resistance, including the equivalent series resistance (ESR) of the capacitor, anyseries resistance added externally, and PWB trace resistance to Co.§Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects mustbe taken into account separately.�

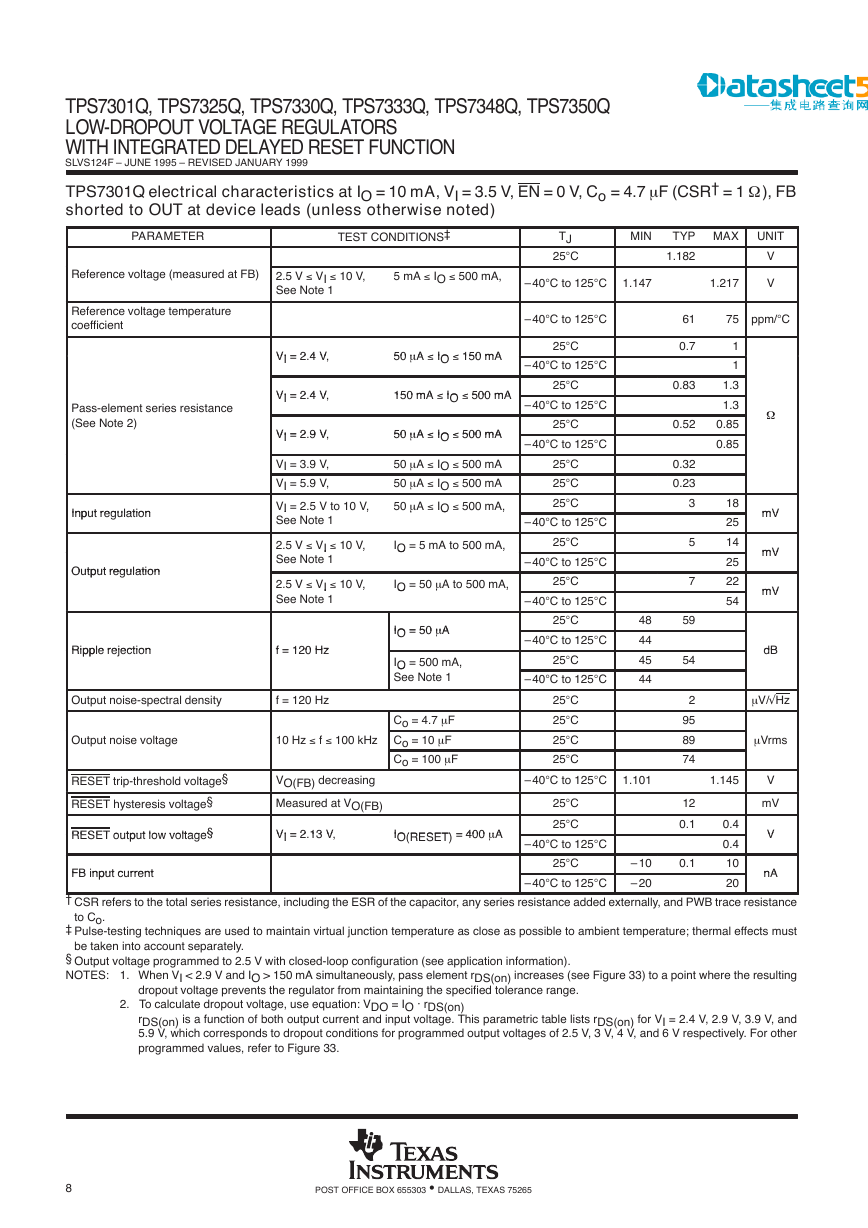

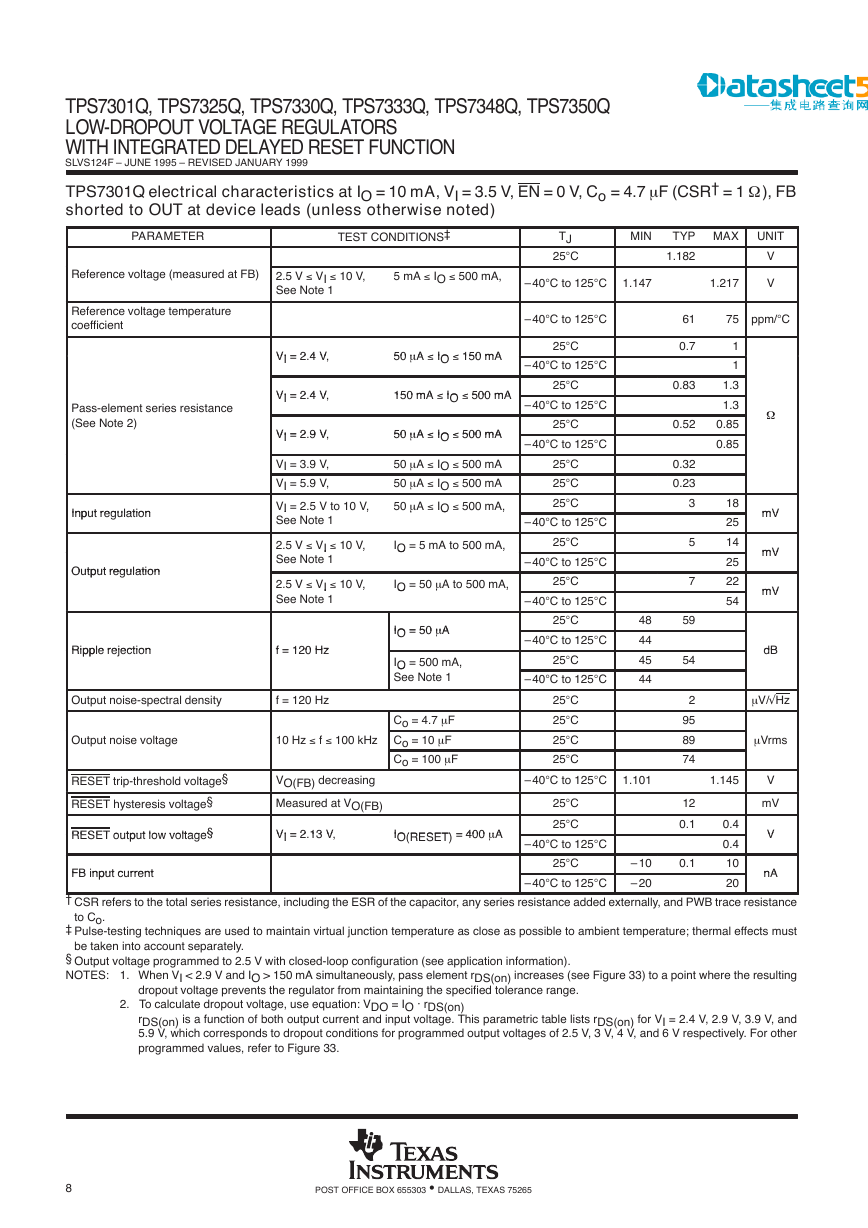

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350QLOW-DROPOUT VOLTAGE REGULATORSWITH INTEGRATED DELAYED RESET FUNCTION SLVS124F – JUNE 1995 – REVISED JANUARY 19998POST OFFICE BOX 655303 • DALLAS, TEXAS 75265TPS7301Q electrical characteristics at IO = 10 mA, VI = 3.5 V, EN = 0 V, Co = 4.7 mF (CSR† = 1 W), FBshorted to OUT at device leads (unless otherwise noted)PARAMETERTEST CONDITIONS‡TJMINTYPMAXUNIT25°C1.182VReference voltage (measured at FB)2.5 V ≤ VI ≤ 10 V,See Note 15 mA ≤ IO ≤ 500 mA,–40°C to 125°C1.1471.217VReference voltage temperaturecoefficient–40°C to 125°C6175ppm/°CVI=24V50mA≤IO≤150mA25°C0.71VI = 2.4 V,50 mA ≤ IO ≤ 150 mA–40°C to 125°C1VI=24V150mA≤IO≤500mA25°C0.831.3Pass-element series resistance VI = 2.4 V,150 mA ≤ IO ≤ 500 mA–40°C to 125°C1.3W(See Note 2)VI=29V50mA≤IO≤500mA25°C0.520.85WVI = 2.9 V,50 mA ≤ IO ≤ 500 mA–40°C to 125°C0.85VI = 3.9 V,50 mA ≤ IO ≤ 500 mA25°C0.32VI = 5.9 V,50 mA ≤ IO ≤ 500 mA25°C0.23InputregulationVI = 2.5 V to 10 V,50 mA ≤ IO ≤ 500 mA,25°C318mVInput regulationI,See Note 1mO,–40°C to 125°C25mV2.5 V ≤ VI ≤ 10 V,IO = 5 mA to 500 mA,25°C514mVOutputregulationI,See Note 1O,–40°C to 125°C25mVOutput regulation2.5 V ≤ VI ≤ 10 V,IO = 50 mA to 500 mA,25°C722mVI,See Note 1Om,–40°C to 125°C54mVIO=50mA25°C4859Ripplerejectionf=120HzIO = 50 mA–40°C to 125°C44dBRipple rejectionf = 120 HzIO = 500 mA,25°C4554dBO,See Note 1–40°C to 125°C44Output noise-spectral densityf = 120 Hz25°C2mV/√HzCo = 4.7 mF25°C95Output noise voltage10 Hz ≤ f ≤ 100 kHzCo = 10 mF25°C89mVrmsCo = 100 mF25°C74RESET trip-threshold voltage§VO(FB) decreasing–40°C to 125°C1.1011.145VRESET hysteresis voltage§Measured at VO(FB)25°C12mVRESEToutputlowvoltage§VI=213VIO(RESET)=400mA25°C0.10.4VRESET output low voltage§VI = 2.13 V,IO(RESET) = 400 mA–40°C to 125°C0.4VFBinputcurrent25°C–100.110nAFB input current–40°C to 125°C–2020nA†CSR refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistanceto Co.‡Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effects mustbe taken into account separately.§Output voltage programmed to 2.5 V with closed-loop configuration (see application information).NOTES:1.When VI < 2.9 V and IO > 150 mA simultaneously, pass element rDS(on) increases (see Figure 33) to a point where the resultingdropout voltage prevents the regulator from maintaining the specified tolerance range.2.To calculate dropout voltage, use equation: VDO = IO ⋅ rDS(on)rDS(on) is a function of both output current and input voltage. This parametric table lists rDS(on) for VI = 2.4 V, 2.9 V, 3.9 V, and5.9 V, which corresponds to dropout conditions for programmed output voltages of 2.5 V, 3 V, 4 V, and 6 V respectively. For otherprogrammed values, refer to Figure 33.�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc