Intel® Data Plane Development Kit (Intel® DPDK)

Revision History

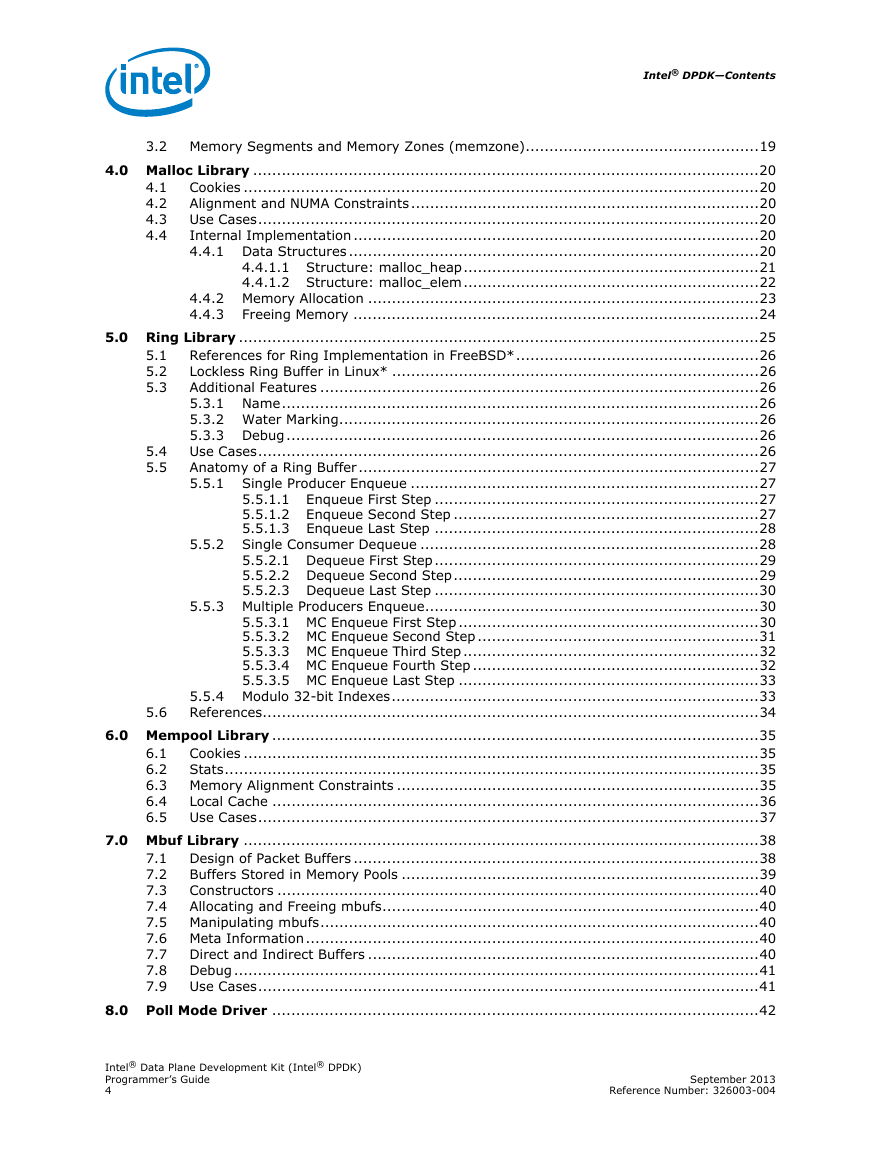

Contents

Figures

Legal Lines and Disclaimers

1.0 Introduction

1.1 Documentation Roadmap

1.2 Related Publications

Part 1: Architecture Overview

2.0 Overview

2.1 Development Environment

2.2 Environment Abstraction Layer

2.3 Core Components

2.3.1 Memory Manager (librte_malloc)

2.3.2 Ring Manager (librte_ring)

2.3.3 Memory Pool Manager (librte_mempool)

2.3.4 Network Packet Buffer Management (librte_mbuf)

2.3.5 Timer Manager (librte_timer)

2.4 Ethernet* Poll Mode Driver Architecture

2.5 Packet Forwarding Algorithm Support

2.6 librte_net

3.0 Environment Abstraction Layer

3.1 EAL in a Linux-userland Execution Environment

3.1.1 Initialization and Core Launching

3.1.2 Multi-process Support

3.1.3 Memory Mapping Discovery and Memory Reservation

3.1.4 PCI Access

3.1.5 Per-lcore and Shared Variables

3.1.6 Logs

3.1.6.1 Trace and Debug Functions

3.1.7 CPU Feature Identification

3.1.8 User Space Interrupt and Alarm Handling

3.1.9 Blacklisting

3.1.10 Misc Functions

3.2 Memory Segments and Memory Zones (memzone)

4.0 Malloc Library

4.1 Cookies

4.2 Alignment and NUMA Constraints

4.3 Use Cases

4.4 Internal Implementation

4.4.1 Data Structures

4.4.1.1 Structure: malloc_heap

4.4.1.2 Structure: malloc_elem

4.4.2 Memory Allocation

4.4.3 Freeing Memory

5.0 Ring Library

5.1 References for Ring Implementation in FreeBSD*

5.2 Lockless Ring Buffer in Linux*

5.3 Additional Features

5.3.1 Name

5.3.2 Water Marking

5.3.3 Debug

5.4 Use Cases

5.5 Anatomy of a Ring Buffer

5.5.1 Single Producer Enqueue

5.5.1.1 Enqueue First Step

5.5.1.2 Enqueue Second Step

5.5.1.3 Enqueue Last Step

5.5.2 Single Consumer Dequeue

5.5.2.1 Dequeue First Step

5.5.2.2 Dequeue Second Step

5.5.2.3 Dequeue Last Step

5.5.3 Multiple Producers Enqueue

5.5.3.1 MC Enqueue First Step

5.5.3.2 MC Enqueue Second Step

5.5.3.3 MC Enqueue Third Step

5.5.3.4 MC Enqueue Fourth Step

5.5.3.5 MC Enqueue Last Step

5.5.4 Modulo 32-bit Indexes

5.6 References

6.0 Mempool Library

6.1 Cookies

6.2 Stats

6.3 Memory Alignment Constraints

6.4 Local Cache

6.5 Use Cases

7.0 Mbuf Library

7.1 Design of Packet Buffers

7.2 Buffers Stored in Memory Pools

7.3 Constructors

7.4 Allocating and Freeing mbufs

7.5 Manipulating mbufs

7.6 Meta Information

7.7 Direct and Indirect Buffers

7.8 Debug

7.9 Use Cases

8.0 Poll Mode Driver

8.1 Requirements and Assumptions

8.2 Design Principles

8.3 Logical Cores, Memory and NIC Queues Relationships

8.4 Device Identification and Configuration

8.4.1 Device Identification

8.4.2 Device Configuration

8.4.3 On-the-Fly Configuration

8.4.4 Configuration of Transmit and Receive Queues

8.5 Poll Mode Driver API

8.5.1 Generalities

8.5.2 Generic Packet Representation

8.5.3 Ethernet Device API

9.0 IXGBE/IGB Virtual Function Driver

9.1 SR-IOV Mode Utilization in an Intel® DPDK Environment

9.1.1 Physical and Virtual Function Infrastructure

9.1.1.1 Intel® 82599 10 Gigabit Ethernet Controller VF Infrastructure

9.1.1.2 Intel® 82576 Gigabit Ethernet Controller and Intel® Ethernet Controller I350 Family VF Infrastructure

9.1.2 Validated Hypervisors

9.1.3 Expected Guest Operating System in Virtual Machine

9.2 Setting Up a KVM Virtual Machine Monitor

9.3 Intel® DPDK SR-IOV PMD PF/VF Driver Usage Model

9.3.1 Fast Host-based Packet Processing

9.4 SR-IOV (PF/VF) Approach for Inter-VM Communication

10.0 Driver for VM Emulated Devices

10.1 Validated Hypervisors

10.2 Recommended Guest Operating System in Virtual Machine

10.3 Setting Up a KVM Virtual Machine

10.4 Known Limitations of Emulated Devices

11.0 Poll Mode Driver for Emulated Virtio NIC

11.1 Virtio Implementation in the Intel® DPDK

11.2 Features and Limitations of the Virtio PMD

11.3 Prerequisites

11.4 Virtio with kni vhost Backend

11.5 Virtio with a qemu virtio Backend

12.0 Libpcap and Ring Based Poll Mode Drivers

12.1 Using the Drivers from the EAL Command Line

12.1.1 Libpcap-based PMD

12.1.1.1 Device Streams

12.1.1.2 Examples of Usage

12.1.1.3 Using libpcap-based PMD with the testpmd Application

12.1.2 Rings-based PMD

12.1.3 Using the Poll Mode Driver from an Application

12.1.3.1 Usage Examples

13.0 Timer Library

13.1 Implementation Details

13.2 Use Cases

13.3 References

14.0 Hash Library

14.1 Hash API Overview

14.2 Implementation Details

14.3 Use Case: Flow Classification

14.4 References

15.0 LPM Library

15.1 LPM API Overview

15.2 Implementation Details

15.3 Use Case: IPv4 Forwarding

15.4 References

16.0 LPM6 Library

16.1 LPM6 API Overview

16.2 Implementation Details

16.3 Use Case: IPv6 Forwarding

17.0 Multi-process Support

17.1 Memory Sharing

17.2 Deployment Models

17.2.1 Symmetric/Peer Processes

17.2.2 Asymmetric/Non-Peer Processes

17.2.3 Running Multiple Independent Intel® DPDK Applications

17.2.4 Running Multiple Independent Groups of Intel® DPDK Applications

17.3 Multi-process Limitations

18.0 Kernel NIC Interface

Figure 17. Components of an Intel® DPDK KNI Application

18.1 The Intel® DPDK KNI Kernel Module

18.2 KNI Creation and Deletion

18.3 Intel® DPDK mbuf Flow

Figure 18. Packet Flow via mbufs in the Intel® DPDK KNI

18.4 Use Case: Ingress

18.5 Use Case: Egress

18.6 Ethtool

18.7 Link state and MTU change

18.8 KNI Working as a Kernel vHost Backend

18.8.1 Overview

Figure 19. vHost-net Architecture Overview

18.8.2 Packet Flow

Figure 20. KNI Traffic Flow

18.8.3 Sample Usage

18.8.4 Compatibility Configure Option

19.0 Thread Safety of Intel® DPDK Functions

19.1 Fast-Path APIs

19.2 Performance Insensitive API

19.3 Library Initialization

19.4 Interrupt Thread

20.0 Quality of Service (QoS) Framework

20.1 Packet Pipeline with QoS Support

20.2 Hierarchical Scheduler

20.2.1 Overview

20.2.2 Scheduling Hierarchy

20.2.3 Application Programming Interface (API)

20.2.3.1 Port Scheduler Configuration API

20.2.3.2 Port Scheduler Enqueue API

20.2.3.3 Port Scheduler Dequeue API

20.2.3.4 Usage Example

20.2.4 Implementation

20.2.4.1 Internal Data Structures per Port

20.2.4.2 Multicore Scaling Strategy

20.2.4.3 Enqueue Pipeline

20.2.4.4 Dequeue State Machine

20.2.4.5 Timing and Synchronization

20.2.4.6 Credit Logic

无标题

20.2.5 Worst Case Scenarios for Performance

20.2.5.1 Lots of Active Queues with Not Enough Credits

20.2.5.2 Single Queue with 100% Line Rate

20.3 Dropper

20.3.1 Configuration

20.3.2 Enqueue Operation

20.3.2.1 EWMA Filter Microblock

20.3.2.2 Drop Decision Block

20.3.3 Queue Empty Operation

20.3.4 Source Files Location

20.3.5 Integration with the Intel® DPDK QoS Scheduler

20.3.6 Integration with the Intel® DPDK QoS Scheduler Sample Application

20.3.7 Application Programming Interface (API)

20.3.7.1 Enqueue API

20.3.7.2 Empty API

20.4 Traffic Metering

20.4.1 Functional Overview

20.4.1.1 Color Blind and Color Aware Modes

20.4.2 Implementation Overview

21.0 Power Management

21.1 CPU Frequency Scaling

21.2 Core-load Throttling through C-States

21.3 API Overview of the Power Library

21.4 User Cases

21.5 References

Part 2: Development Environment

22.0 Source Organization

22.1 Makefiles and Config

22.2 Libraries

22.3 Applications

23.0 Development Kit Build System

23.1 Building the Development Kit Binary

23.1.1 Build Directory Concept

23.2 Building External Applications

23.3 Makefile Description

23.3.1 General Rules For Intel® DPDK Makefiles

23.3.2 Makefile Types

23.3.2.1 Application

23.3.2.2 Library

23.3.2.3 Install

23.3.2.4 Kernel Module

23.3.2.5 Objects

23.3.2.6 Misc

23.3.3 Useful Variables Provided by the Build System

23.3.4 Variables that Can be Set/Overridden in a Makefile Only

23.3.5 Variables that can be Set/Overridden by the User on the Command Line Only

23.3.6 Variables that Can be Set/Overridden by the User in a Makefile or Command Line

24.0 Development Kit Root Makefile Help

24.1 Configuration Targets

24.2 Build Targets

24.3 Install Targets

24.4 Test Targets

24.5 Documentation Targets

24.6 Deps Targets

24.7 Misc Targets

24.8 Other Useful Command-line Variables

24.9 Make in a Build Directory

24.10 Compiling for Debug

25.0 Extending the Intel® DPDK

25.1 Example: Adding a New Library libfoo

25.1.1 Example: Using libfoo in the Test Application

26.0 Building Your Own Application

26.1 Compiling a Sample Application in the Development Kit Directory

26.2 Build Your Own Application Outside the Development Kit

26.3 Customizing Makefiles

26.3.1 Application Makefile

26.3.2 Library Makefile

26.3.3 Customize Makefile Actions

27.0 External Application/Library Makefile help

27.1 Prerequisites

27.2 Build Targets

27.3 Help Targets

27.4 Other Useful Command-line Variables

27.5 Make from Another Directory

Part 3: Performance Optimization

28.0 Performance Optimization Guidelines

28.1 Introduction

29.0 Writing Efficient Code

29.1 Memory

29.1.1 Memory Copy: Do not Use libc in the Data Plane

29.1.2 Memory Allocation

29.1.3 Concurrent Access to the Same Memory Area

29.1.4 NUMA

29.1.5 Distribution Across Memory Channels

29.2 Communication Between lcores

29.3 PMD Driver

29.3.1 Lower Packet Latency

无标题

29.4 Locks and Atomic Operations

29.5 Coding Considerations

29.5.1 Inline Functions

29.5.2 Branch Prediction

29.6 Setting the Target CPU Type

30.0 Profile Your Application

31.0 Glossary

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc