AML7366-M6C/M6L Quick Reference Manual

Revision 0.4

AML7366-M6C

AML7366-M6L

Quick Reference Manual

Revision: 0.4

Release date: 8/15/2013

Amlogic, Inc.

1/40

AMLOGIC, Inc. Proprietary

Distribute to Shinco!�

AML7366-M6C/M6L Quick Reference Manual

Revision 0.4

COPYRIGHT

© 2012 Amlogic, Inc.

All rights reserved. No part of this document may be reproduced. Transmitted, transcribed, or translated into any language

in any form or by any means with the written permission of Amlogic, Inc.

TRADEMARKS

AMLOGIC is a trademark of Amlogic, Inc. All other trademarks and registered trademarks are property of their respective

companies.

DISCLAIMER

Amlogic Inc. may make improvements and/or changes in this document or in the product described in this document at any

time.

This product is not intended for use in medical, life saving, or life sustaining applications.

Circuit diagrams and other information relating to products of Amlogic Inc. are included as a means or illustrating typical

applications. Consequently, complete information sufficient for production design is not necessarily given. Amlogic makes

no representations or warranties with respect to the accuracy or completeness of the contents presented in this document.

REVISION HISTORY

Revision

Number

0.1

0.2

0.3

0.4

Revision Date

Changes

2012/11/29

2013/01/14

2013/01/24

2013/08/13

Initial draft

Update Recommended Operating Conditions

Add comments to CEC support on AML7366-M6C

Update operation conditions

CONTACT INFORMATION

Amlogic, Inc.

3930 Freedom Circle, Suite 101

Santa Clara, CA 95054

U.S.A.

www.amlogic.com

2/40

AMLOGIC, Inc. Proprietary

Distribute to Shinco!�

AML7366-M6C/M6L Quick Reference Manual

Revision 0.4

Contents

1. General Description .............................................................................................................................................. 4

2.

Features Summary ................................................................................................................................................ 6

3. Pin Out Specification .......................................................................................................................................... 10

3.1

Pin-Out Diagram (top view) ......................................................................................................................... 10

3.2

Pin Assignments ........................................................................................................................................... 11

3.3

Pin Multiplexing Tables ................................................................................................................................ 25

3.4

Signal Descriptions ....................................................................................................................................... 29

4. Operating Conditions .......................................................................................................................................... 36

4.1 Absolute Maximum Ratings ......................................................................................................................... 36

4.2

Recommended Operating Conditions .......................................................................................................... 36

4.3 DC Characteristics ........................................................................................................................................ 36

4.4 DDR3 SDRAM Timing Specifications ............................................................................................................ 37

4.4.1

Recommended Operating Codditions .................................................................................................. 37

4.4.2 DC specifications - DDR3 mode ............................................................................................................ 37

4.4.3

AC specifications - DDR3 mode ............................................................................................................. 37

4.5

Recommended Power on sequence ............................................................................................................ 38

5. Mechanical Dimensions ...................................................................................................................................... 39

3/40

AMLOGIC, Inc. Proprietary

Distribute to Shinco!�

AML7366-M6C/M6L Quick Reference Manual

Revision 0.4

1. General Description

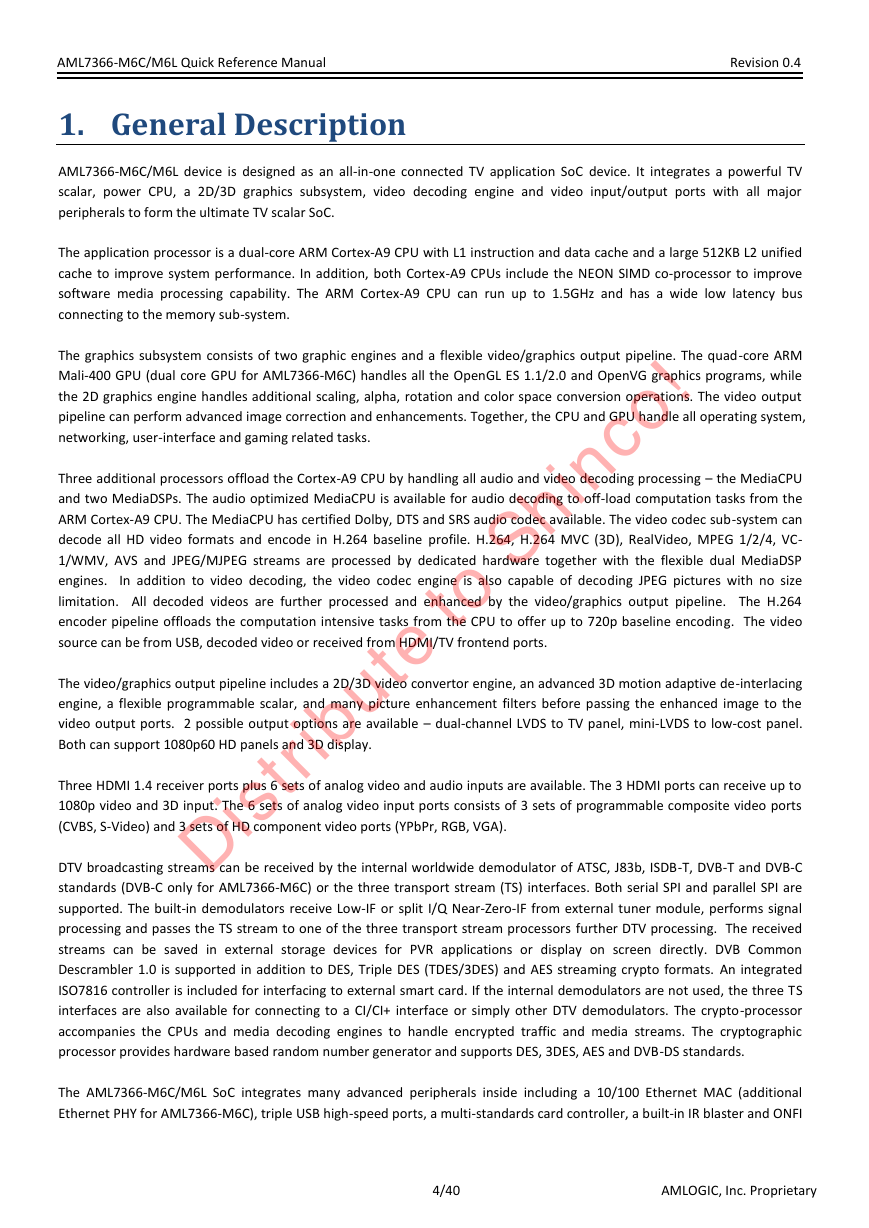

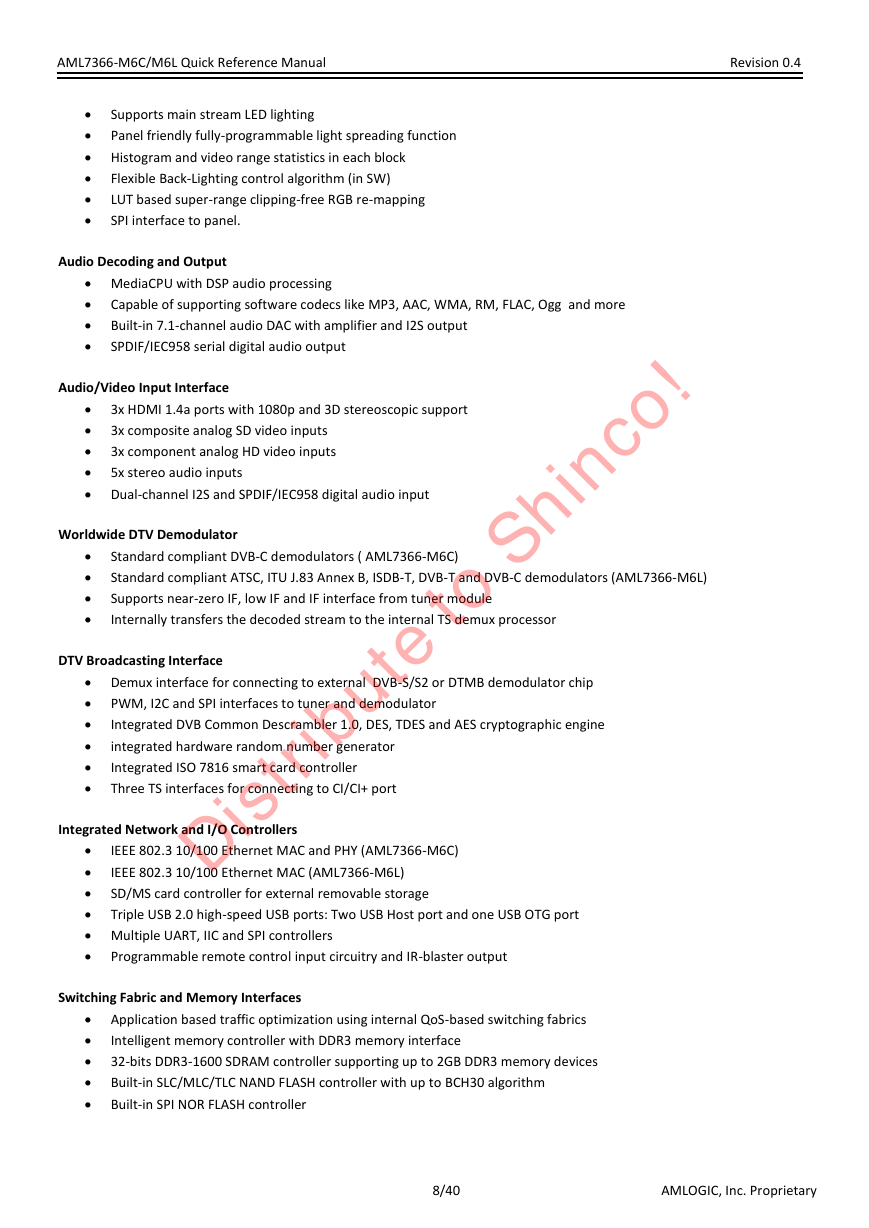

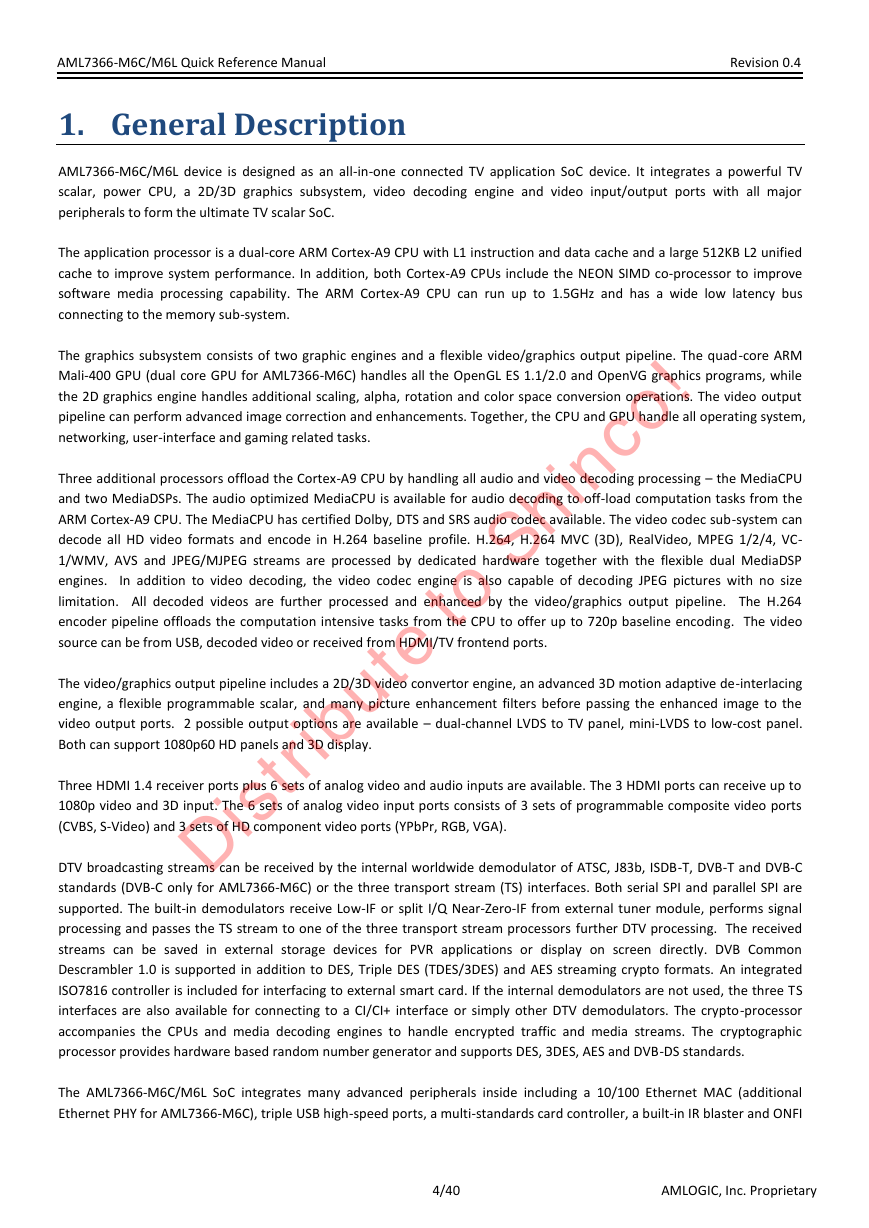

AML7366-M6C/M6L device is designed as an all-in-one connected TV application SoC device. It integrates a powerful TV

scalar, power CPU, a 2D/3D graphics subsystem, video decoding engine and video input/output ports with all major

peripherals to form the ultimate TV scalar SoC.

The application processor is a dual-core ARM Cortex-A9 CPU with L1 instruction and data cache and a large 512KB L2 unified

cache to improve system performance. In addition, both Cortex-A9 CPUs include the NEON SIMD co-processor to improve

software media processing capability. The ARM Cortex-A9 CPU can run up to 1.5GHz and has a wide low latency bus

connecting to the memory sub-system.

The graphics subsystem consists of two graphic engines and a flexible video/graphics output pipeline. The quad-core ARM

Mali-400 GPU (dual core GPU for AML7366-M6C) handles all the OpenGL ES 1.1/2.0 and OpenVG graphics programs, while

the 2D graphics engine handles additional scaling, alpha, rotation and color space conversion operations. The video output

pipeline can perform advanced image correction and enhancements. Together, the CPU and GPU handle all operating system,

networking, user-interface and gaming related tasks.

Three additional processors offload the Cortex-A9 CPU by handling all audio and video decoding processing – the MediaCPU

and two MediaDSPs. The audio optimized MediaCPU is available for audio decoding to off-load computation tasks from the

ARM Cortex-A9 CPU. The MediaCPU has certified Dolby, DTS and SRS audio codec available. The video codec sub-system can

decode all HD video formats and encode in H.264 baseline profile. H.264, H.264 MVC (3D), RealVideo, MPEG 1/2/4, VC-

1/WMV, AVS and JPEG/MJPEG streams are processed by dedicated hardware together with the flexible dual MediaDSP

engines. In addition to video decoding, the video codec engine is also capable of decoding JPEG pictures with no size

limitation. All decoded videos are further processed and enhanced by the video/graphics output pipeline. The H.264

encoder pipeline offloads the computation intensive tasks from the CPU to offer up to 720p baseline encoding. The video

source can be from USB, decoded video or received from HDMI/TV frontend ports.

The video/graphics output pipeline includes a 2D/3D video convertor engine, an advanced 3D motion adaptive de-interlacing

engine, a flexible programmable scalar, and many picture enhancement filters before passing the enhanced image to the

video output ports. 2 possible output options are available – dual-channel LVDS to TV panel, mini-LVDS to low-cost panel.

Both can support 1080p60 HD panels and 3D display.

Three HDMI 1.4 receiver ports plus 6 sets of analog video and audio inputs are available. The 3 HDMI ports can receive up to

1080p video and 3D input. The 6 sets of analog video input ports consists of 3 sets of programmable composite video ports

(CVBS, S-Video) and 3 sets of HD component video ports (YPbPr, RGB, VGA).

DTV broadcasting streams can be received by the internal worldwide demodulator of ATSC, J83b, ISDB-T, DVB-T and DVB-C

standards (DVB-C only for AML7366-M6C) or the three transport stream (TS) interfaces. Both serial SPI and parallel SPI are

supported. The built-in demodulators receive Low-IF or split I/Q Near-Zero-IF from external tuner module, performs signal

processing and passes the TS stream to one of the three transport stream processors further DTV processing. The received

streams can be saved in external storage devices for PVR applications or display on screen directly. DVB Common

Descrambler 1.0 is supported in addition to DES, Triple DES (TDES/3DES) and AES streaming crypto formats. An integrated

ISO7816 controller is included for interfacing to external smart card. If the internal demodulators are not used, the three TS

interfaces are also available for connecting to a CI/CI+ interface or simply other DTV demodulators. The crypto-processor

accompanies the CPUs and media decoding engines to handle encrypted traffic and media streams. The cryptographic

processor provides hardware based random number generator and supports DES, 3DES, AES and DVB-DS standards.

The AML7366-M6C/M6L SoC integrates many advanced peripherals inside including a 10/100 Ethernet MAC (additional

Ethernet PHY for AML7366-M6C), triple USB high-speed ports, a multi-standards card controller, a built-in IR blaster and ONFI

4/40

AMLOGIC, Inc. Proprietary

Distribute to Shinco!�

AML7366-M6C/M6L Quick Reference Manual

Revision 0.4

SLC/MLC/TLC NAND flash controller. The flexible and programmable QoS-based switch fabric and memory controller tie all

the processing cores and peripherals together and connects to the DDR3-1600 memory bus.

The AML7366-M6C/M6L SoC supports industrial standard Linux and Android operating system. Standard development

environment utilizing gcc tool chain is supported. Please contact your AMLOGIC Sales for more information.

5/40

AMLOGIC, Inc. Proprietary

Distribute to Shinco!�

AML7366-M6C/M6L Quick Reference Manual

Revision 0.4

2. Features Summary

CPU Sub-system

32KB instruction cache, 32KB data cache

Supports ARMv7 ISA with Thumb-2 technology

Dual ARM Cortex A9 CPU, up to 1.5GHz frequency, 2.5 DMIPS/MHz. Total 7500 DMIPS.

Multi-issue superscalar, out-of-order design

Unified 512KB L2 cache

Memory Management Unit and pre-fetch engine

Advanced NEON SIMD media accelerator

TrustZone security

Supporting Linux and Android operating system

3D Graphics Processing Unit

Dual ARM Mali-400 3D GPU, 800Mpix/sec and 44Mtri/sec (AML7366-M6C)

Quad ARM Mali-400 3D GPU 1600Mpix/sec and 44Mtri/sec ( AML7366-M6L)

Full scene over-sampled 4X anti-aliasing engine with no additional bandwidth usage

GPU-L2 cache for reduction of graphics data bandwidth

GPU-Memory Management Unit

6/40

AMLOGIC, Inc. Proprietary

Core and FabricDTV DemodulatorsSystem InterfacePLLsPMUJTAGVideo Output UnitColor mapperImaging EngineInput/Output InterfacesAudio Input UnitAudio interfaceSPDIFVideo Input UnitHDMI x3Audio Output UnitTrustzone Security512KB L2 CacheMediaCPUMCODECVideo DSPVideo DSP2.5D GraphicProcessingCryptoEngineOTPMMUARM Cortex-A9up to 1.5GHz32KBI-Cache32KBD-CacheNEON VFPARM Cortex-A9up to 1.5GHz32KBI-Cache32KBD-CacheNEON VFPMali-400 GPUMMUPower ManagementProcessorMemory InterfaceDDR3-1600 Memory ControllerNAND/eMMC/iNANDFlash ControllerSPI NOR FlashControllerDe-interlacer2D-to-3D ConvertorLVDS &Mini-LVDS +TCONI2S (2 CH)Analog Audio (x5)3D DetectionVideo DecoderCVBS x3YPbPr/VGA x3Multi-DemuxDVB-CAudio interfaceSPDIFI2S (7.1)Analog AudioMali-400 GPULocal Dimming10/100EthernetMAC+PHY (**)USBHostx2SARADCRemoteInputUARTx3CI+ &ISO7816USBOTGx1I2C Masterx2SD CardCntlrI2C Slavex2* 64KB Graphic cache for AML7366-M6CFor AML7366-M6L Only** Ethernet MAC only for AML7366-M6LISDB-TJ83bATSCDVB-T128KB Cache (*) Mali-400GPU Mali-400GPUDistribute to Shinco!�

AML7366-M6C/M6L Quick Reference Manual

Revision 0.4

Independent and concurrent GPU and CPU processing

OpenGL ES 1.1/2.0 and OpenVG 1.1 software driver

2D Graphics Processor

Fast bitblt engine with dual inputs and single output

Programmable raster (ROP) and alpha (AOP) operations

Programmable polyphase scaling filter

Supports multiple video formats 4:2:0, 4:2:2 and 4:4:4 and multiple pixel formats (8/16/24/32 bits graphics layer)

Fast color space conversion

Advanced anti-flickering filter

Accelerated Video/Picture Codec Hardware

Dual programmable DSP engines at 300MHz with DSP instructions and direct video codec hardware interfaces

H.264 baseline encoding support for up to 720p resolution

MPEG-1 MP/HL conforming to ISO-11172 (1080P)

MPEG-2 MP/HL conforming to ISO-13818 (1080P)

MPEG-4 Part 2 ASP ISO-14496-2 (1080P)

WMV/VC-1 SP/MP/AP (1080P, progressive/interlace frame picture)

H.264 HP@L4.1 w/ Annex H (1080P, MVC)

AVS JiZhun Profile (1080p)

RealVideo 8/9/10 Decoding (720p)

M-JPEG and JPEG decoding ISO/IEC-10918 – Unlimited pixel resolution (currently test with 16M pixel digital camera

and 100M pixel Photoshop file)

Supports JPEG thumbnail, scaling, rotation and transition effects

Multiple language and multiple format sub-title video support

Supports *.mkv,*.wmv,*.mpg, *.mpeg, *.dat, *.avi, *.mov, *.iso, *.mp4, and *.jpg file formats

2D/3D processor, TV Scalar and Video Post-Processing Controller

Motion adaptive 2D/3D conversion processor converts 1080p video to 3D output on-the-fly

Motion adaptive 3D noise reduction filter

Advanced motion adaptive edge enhancing de-interlacing engine

3:2 pull-down support

Programmable poly-phase TV scalar for both horizontal and vertical dimension for zoom and windowing

Programmable color management filter (to enhance blue, green, red, face and other colors)

Chroma coloring and black extension processing

Dynamic Non-Linear Luma filter

Video mixer: 2 video planes and 2 graphics planes

Programmable color matrix pipeline

LCD Panel Output

Dual channels LVDS output supporting up to 1920x1080 60Hz resolution

Dual channels mini-LVDS output supporting up to 1920x1080 60Hz resolution

Dithering logic for mapping to different LCD panel color depth

Three independent Gamma table for LCD panel tuning

Integrated programmable timing controller (TCON)

Local Dimming

Maximum 8x8 blocks support for local dimming

7/40

AMLOGIC, Inc. Proprietary

Distribute to Shinco!�

AML7366-M6C/M6L Quick Reference Manual

Revision 0.4

Supports main stream LED lighting

Panel friendly fully-programmable light spreading function

Histogram and video range statistics in each block

Flexible Back-Lighting control algorithm (in SW)

LUT based super-range clipping-free RGB re-mapping

SPI interface to panel.

Audio Decoding and Output

Capable of supporting software codecs like MP3, AAC, WMA, RM, FLAC, Ogg and more

MediaCPU with DSP audio processing

Built-in 7.1-channel audio DAC with amplifier and I2S output

SPDIF/IEC958 serial digital audio output

Audio/Video Input Interface

3x HDMI 1.4a ports with 1080p and 3D stereoscopic support

3x composite analog SD video inputs

3x component analog HD video inputs

5x stereo audio inputs

Dual-channel I2S and SPDIF/IEC958 digital audio input

Worldwide DTV Demodulator

Standard compliant DVB-C demodulators ( AML7366-M6C)

Standard compliant ATSC, ITU J.83 Annex B, ISDB-T, DVB-T and DVB-C demodulators (AML7366-M6L)

Supports near-zero IF, low IF and IF interface from tuner module

Internally transfers the decoded stream to the internal TS demux processor

DTV Broadcasting Interface

Demux interface for connecting to external DVB-S/S2 or DTMB demodulator chip

PWM, I2C and SPI interfaces to tuner and demodulator

Integrated DVB Common Descrambler 1.0, DES, TDES and AES cryptographic engine

integrated hardware random number generator

Integrated ISO 7816 smart card controller

Three TS interfaces for connecting to CI/CI+ port

Integrated Network and I/O Controllers

IEEE 802.3 10/100 Ethernet MAC and PHY (AML7366-M6C)

IEEE 802.3 10/100 Ethernet MAC (AML7366-M6L)

SD/MS card controller for external removable storage

Triple USB 2.0 high-speed USB ports: Two USB Host port and one USB OTG port

Multiple UART, IIC and SPI controllers

Programmable remote control input circuitry and IR-blaster output

Switching Fabric and Memory Interfaces

Application based traffic optimization using internal QoS-based switching fabrics

Intelligent memory controller with DDR3 memory interface

32-bits DDR3-1600 SDRAM controller supporting up to 2GB DDR3 memory devices

Built-in SLC/MLC/TLC NAND FLASH controller with up to BCH30 algorithm

Built-in SPI NOR FLASH controller

8/40

AMLOGIC, Inc. Proprietary

Distribute to Shinco!�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc