ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition

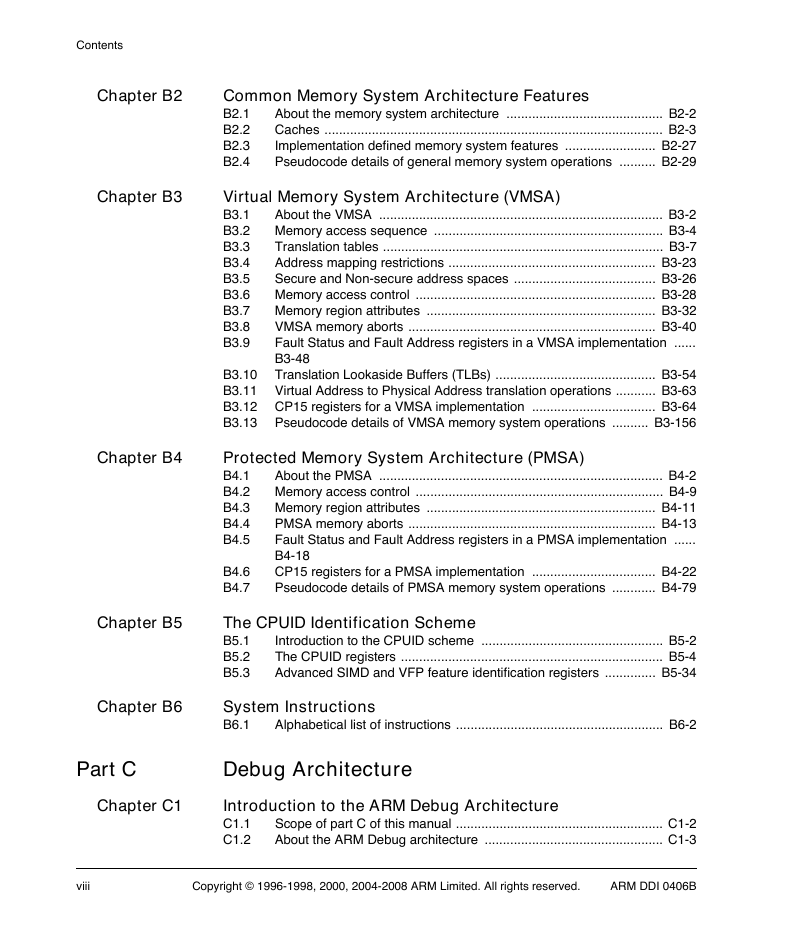

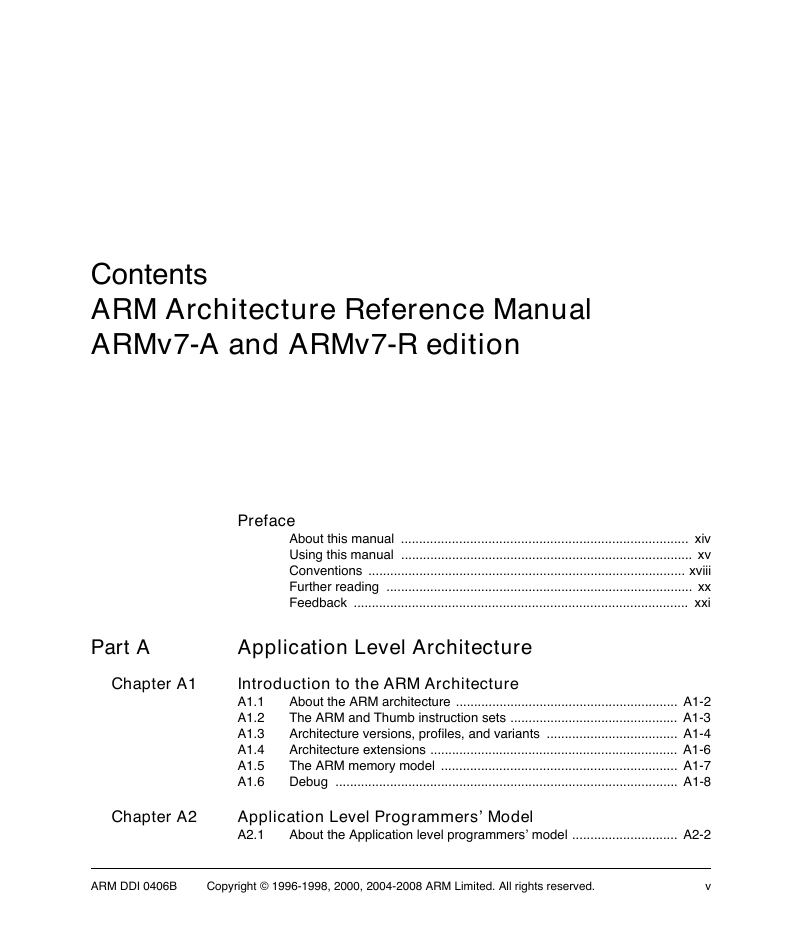

Contents

Preface

About this manual

Using this manual

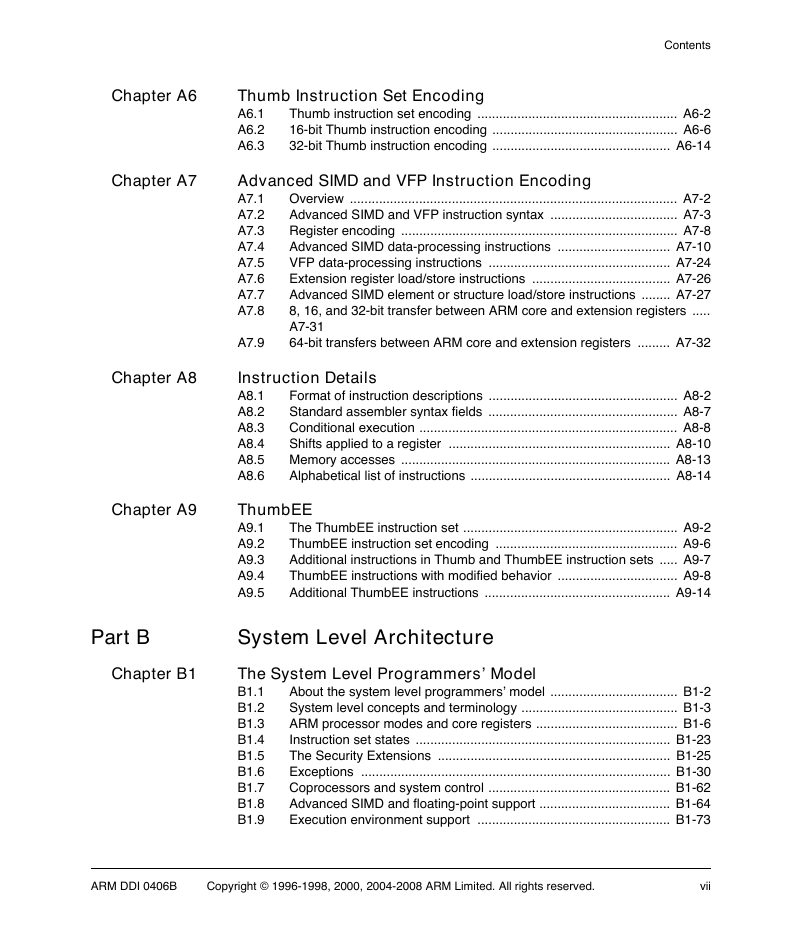

Part A, Application Level Architecture

Part B, System Level Architecture

Part C, Debug Architecture

Part D, Appendices

Conventions

General typographic conventions

Signals

Numbers

Bit values

Pseudocode descriptions

Assembler syntax descriptions

Further reading

ARM publications

External publications

Feedback

Feedback on this manual

Application Level Architecture

Introduction to the ARM Architecture

A1.1 About the ARM architecture

A1.2 The ARM and Thumb instruction sets

A1.3 Architecture versions, profiles, and variants

A1.4 Architecture extensions

A1.5 The ARM memory model

A1.6 Debug

Application Level Programmers’ Model

A2.1 About the Application level programmers’ model

A2.2 ARM core data types and arithmetic

A2.2.1 Integer arithmetic

Shift and rotate operations

Pseudocode details of addition and subtraction

Pseudocode details of saturation

A2.3 ARM core registers

A2.3.1 Pseudocode details of operations on ARM core registers

A2.4 The Application Program Status Register (APSR)

A2.5 Execution state registers

A2.5.1 ISETSTATE

Pseudocode details of ISETSTATE operations

A2.5.2 ITSTATE

Pseudocode details of ITSTATE operations

A2.5.3 ENDIANSTATE

Pseudocode details of ENDIANSTATE operations

A2.6 Advanced SIMD and VFP extensions

A2.6.1 Advanced SIMD and VFP extension registers

Advanced SIMD views of the extension register set

VFP views of the extension register set

Advanced SIMD and VFP register mapping

Pseudocode details of Advanced SIMD and VFP extension registers

A2.6.2 Data types supported by the Advanced SIMD extension

A2.6.3 Advanced SIMD vectors

Pseudocode details of Advanced SIMD vectors

A2.6.4 Advanced SIMD and VFP system registers

Floating-point Status and Control Register (FPSCR)

A2.6.5 VFPv3U

A2.7 Floating-point data types and arithmetic

A2.7.1 ARM standard floating-point input and output values

A2.7.2 Advanced SIMD and VFP single-precision format

A2.7.3 VFP double-precision format

A2.7.4 Advanced SIMD and VFP half-precision formats

A2.7.5 Flush-to-zero

A2.7.6 NaN handling and the Default NaN

A2.7.7 Floating-point exceptions

Combinations of exceptions

A2.7.8 Pseudocode details of floating-point operations

Generation of specific floating-point values

Negation and absolute value

Floating-point value unpacking

Floating-point exception and NaN handling

Floating-point rounding

Selection of ARM standard floating-point arithmetic

Comparisons

Maximum and minimum

Addition and subtraction

Multiplication and division

Reciprocal estimate and step

Square root

Reciprocal square root

Conversions

A2.8 Polynomial arithmetic over {0,1}

A2.8.1 Pseudocode details of polynomial multiplication

A2.9 Coprocessor support

A2.10 Execution environment support

A2.10.1 Thumb Execution Environment

ThumbEE instructions

ThumbEE configuration

A2.10.2 Jazelle direct bytecode execution support

Subarchitectures

Jazelle state

Jazelle state entry instruction, BXJ

Application level configuration and control of the Jazelle extension

EJVM operation

A2.11 Exceptions, debug events and checks

A2.11.1 The Yield instruction

Application Level Memory Model

A3.1 Address space

A3.1.1 Address incrementing and address space overflow

A3.2 Alignment support

A3.2.1 Unaligned data access

A3.2.2 Cases where unaligned accesses are unpredictable

A3.2.3 Unaligned data access restrictions in ARMv7 and ARMv6

A3.3 Endian support

A3.3.1 Control of the endianness mapping scheme in ARMv7

A3.3.2 Instruction endianness

Instruction endianness static configuration, ARMv7-R only

A3.3.3 Element size and endianness

A3.3.4 Instructions to reverse bytes in a general-purpose register

A3.3.5 Endianness in Advanced SIMD

A3.4 Synchronization and semaphores

A3.4.1 Exclusive access instructions and Non-shareable memory regions

A3.4.2 Exclusive access instructions and Shareable memory regions

Operation of the global monitor

A3.4.3 Tagging and the size of the tagged memory block

A3.4.4 Context switch support

A3.4.5 Load-Exclusive and Store-Exclusive usage restrictions

A3.4.6 Semaphores

A3.4.7 Synchronization primitives and the memory order model

A3.4.8 Use of WFE and SEV instructions by spin-locks

A3.5 Memory types and attributes and the memory order model

A3.5.1 Memory types

A3.5.2 Summary of ARMv7 memory attributes

A3.5.3 Atomicity in the ARM architecture

Single-copy atomicity

Multi-copy atomicity

A3.5.4 Normal memory

Non-shareable Normal memory

Shareable, Inner Shareable, and Outer Shareable Normal memory

Write-Through Cacheable, Write-Back Cacheable and Non-cacheable Normal memory

A3.5.5 Device memory

Shareable attribute for Device memory regions

A3.5.6 Strongly-ordered memory

A3.5.7 Memory access restrictions

A3.5.8 Backwards compatibility

A3.5.9 The effect of the Security Extensions

A3.6 Access rights

A3.6.1 Privilege level access controls for data accesses

A3.6.2 Privilege level access controls for instruction accesses

A3.6.3 Memory region security status

A3.7 Virtual and physical addressing

A3.8 Memory access order

A3.8.1 Reads and writes

Reads

Writes

Synchronization primitives

Observability and completion

A3.8.2 Ordering requirements for memory accesses

Program order for instruction execution

A3.8.3 Memory barriers

Data Memory Barrier (DMB)

Data Synchronization Barrier (DSB)

Instruction Synchronization Barrier (ISB)

Pseudocode details of memory barriers

A3.9 Caches and memory hierarchy

A3.9.1 Introduction to caches

A3.9.2 Memory hierarchy

A3.9.3 Implication of caches for the application programmer

Data coherency issues

Instruction coherency issues

A3.9.4 Preloading caches

The Instruction Sets

A4.1 About the instruction sets

A4.1.1 Changing between Thumb state and ARM state

A4.1.2 Conditional execution

A4.2 Unified Assembler Language

A4.2.1 Conditional instructions

A4.2.2 Use of labels in UAL instruction syntax

A4.3 Branch instructions

A4.4 Data-processing instructions

A4.4.1 Standard data-processing instructions

A4.4.2 Shift instructions

A4.4.3 Multiply instructions

A4.4.4 Saturating instructions

A4.4.5 Packing and unpacking instructions

A4.4.6 Miscellaneous data-processing instructions

A4.4.7 Parallel addition and subtraction instructions

A4.4.8 Divide instructions

A4.5 Status register access instructions

A4.6 Load/store instructions

A4.6.1 Loads to the PC

A4.6.2 Halfword and byte loads and stores

A4.6.3 Unprivileged loads and stores

A4.6.4 Exclusive loads and stores

A4.6.5 Addressing modes

A4.7 Load/store multiple instructions

A4.7.1 Loads to the PC

A4.8 Miscellaneous instructions

A4.9 Exception-generating and exception-handling instructions

A4.10 Coprocessor instructions

A4.11 Advanced SIMD and VFP load/store instructions

A4.11.1 Element and structure load/store instructions

A4.12 Advanced SIMD and VFP register transfer instructions

A4.13 Advanced SIMD data-processing operations

A4.13.1 Advanced SIMD parallel addition and subtraction

A4.13.2 Bitwise Advanced SIMD data-processing instructions

A4.13.3 Advanced SIMD comparison instructions

A4.13.4 Advanced SIMD shift instructions

A4.13.5 Advanced SIMD multiply instructions

A4.13.6 Miscellaneous Advanced SIMD data-processing instructions

A4.14 VFP data-processing instructions

ARM Instruction Set Encoding

A5.1 ARM instruction set encoding

A5.1.1 The condition field

A5.1.2 UNDEFINED and UNPREDICTABLE instruction set space

A5.1.3 The PC and the use of 0b1111 as a register specifier

A5.1.4 The SP and the use of 0b1101 as a register specifier

A5.2 Data-processing and miscellaneous instructions

A5.2.1 Data-processing (register)

A5.2.2 Data-processing (register-shifted register)

A5.2.3 Data-processing (immediate)

A5.2.4 Modified immediate constants in ARM instructions

Carry out

Constants with multiple encodings

Operation

A5.2.5 Multiply and multiply-accumulate

A5.2.6 Saturating addition and subtraction

A5.2.7 Halfword multiply and multiply-accumulate

A5.2.8 Extra load/store instructions

A5.2.9 Extra load/store instructions (unprivileged)

A5.2.10 Synchronization primitives

A5.2.11 MSR (immediate), and hints

A5.2.12 Miscellaneous instructions

A5.3 Load/store word and unsigned byte

A5.4 Media instructions

A5.4.1 Parallel addition and subtraction, signed

A5.4.2 Parallel addition and subtraction, unsigned

A5.4.3 Packing, unpacking, saturation, and reversal

A5.4.4 Signed multiplies

A5.5 Branch, branch with link, and block data transfer

A5.6 Supervisor Call, and coprocessor instructions

A5.7 Unconditional instructions

A5.7.1 Miscellaneous instructions, memory hints, and Advanced SIMD instructions

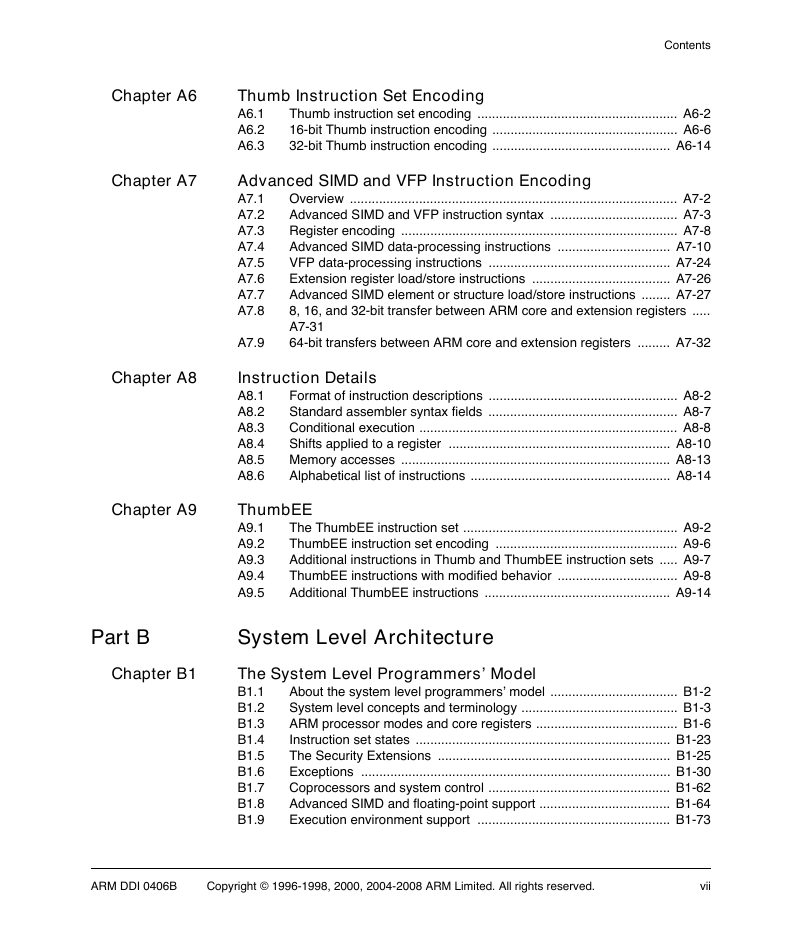

Thumb Instruction Set Encoding

A6.1 Thumb instruction set encoding

A6.1.1 UNDEFINED and UNPREDICTABLE instruction set space

A6.1.2 Use of 0b1111 as a register specifier

A6.1.3 Use of 0b1101 as a register specifier

R13[1:0] definition

32-bit Thumb instruction support for R13

16-bit Thumb instruction support for R13

A6.2 16-bit Thumb instruction encoding

A6.2.1 Shift (immediate), add, subtract, move, and compare

A6.2.2 Data-processing

A6.2.3 Special data instructions and branch and exchange

A6.2.4 Load/store single data item

A6.2.5 Miscellaneous 16-bit instructions

If-Then, and hints

A6.2.6 Conditional branch, and Supervisor Call

A6.3 32-bit Thumb instruction encoding

A6.3.1 Data-processing (modified immediate)

A6.3.2 Modified immediate constants in Thumb instructions

Carry out

Operation

A6.3.3 Data-processing (plain binary immediate)

A6.3.4 Branches and miscellaneous control

Change Processor State, and hints

Miscellaneous control instructions

A6.3.5 Load/store multiple

A6.3.6 Load/store dual, load/store exclusive, table branch

A6.3.7 Load word

A6.3.8 Load halfword, memory hints

A6.3.9 Load byte, memory hints

A6.3.10 Store single data item

A6.3.11 Data-processing (shifted register)

A6.3.12 Data-processing (register)

A6.3.13 Parallel addition and subtraction, signed

A6.3.14 Parallel addition and subtraction, unsigned

A6.3.15 Miscellaneous operations

A6.3.16 Multiply, multiply accumulate, and absolute difference

A6.3.17 Long multiply, long multiply accumulate, and divide

A6.3.18 Coprocessor instructions

Advanced SIMD and VFP Instruction Encoding

A7.1 Overview

A7.1.1 Advanced SIMD

A7.1.2 VFP

A7.2 Advanced SIMD and VFP instruction syntax

A7.2.1 Advanced SIMD Instruction modifiers

A7.2.2 Advanced SIMD Operand shapes

A7.2.3 Data type specifiers

Syntax flexibility

A7.2.4 Register specifiers

A7.2.5 Register lists

Syntax flexibility

A7.3 Register encoding

A7.3.1 Advanced SIMD scalars

A7.4 Advanced SIMD data-processing instructions

A7.4.1 Three registers of the same length

A7.4.2 Three registers of different lengths

A7.4.3 Two registers and a scalar

A7.4.4 Two registers and a shift amount

A7.4.5 Two registers, miscellaneous

A7.4.6 One register and a modified immediate value

Operation

A7.5 VFP data-processing instructions

A7.5.1 Operation

A7.6 Extension register load/store instructions

A7.7 Advanced SIMD element or structure load/store instructions

A7.7.1 Advanced SIMD addressing mode

A7.8 8, 16, and 32-bit transfer between ARM core and extension registers

A7.9 64-bit transfers between ARM core and extension registers

Instruction Details

A8.1 Format of instruction descriptions

A8.1.1 Instruction section title

A8.1.2 Introduction to the instruction

A8.1.3 Instruction encodings

A8.1.4 Assembler syntax

Assembler syntax prototype line conventions

A8.1.5 Pseudocode describing how the instruction operates

A8.1.6 Exception information

A8.1.7 Notes

A8.2 Standard assembler syntax fields

A8.3 Conditional execution

A8.3.1 Pseudocode details of conditional execution

A8.4 Shifts applied to a register

A8.4.1 Constant shifts

Encoding

A8.4.2 Register controlled shifts

A8.4.3 Pseudocode details of instruction-specified shifts and rotates

A8.5 Memory accesses

A8.6 Alphabetical list of instructions

A8.6.1 ADC (immediate)

Assembler syntax

Operation

Exceptions

A8.6.2 ADC (register)

Assembler syntax

Operation

Exceptions

A8.6.3 ADC (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.4 ADD (immediate, Thumb)

Assembler syntax

Operation

Exceptions

A8.6.5 ADD (immediate, ARM)

Assembler syntax

Operation

Exceptions

A8.6.6 ADD (register)

Assembler syntax

Operation

Exceptions

A8.6.7 ADD (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.8 ADD (SP plus immediate)

Assembler syntax

Operation

Exceptions

A8.6.9 ADD (SP plus register)

Assembler syntax

Operation

Exceptions

A8.6.10 ADR

Assembler syntax

Operation

Exceptions

A8.6.11 AND (immediate)

Assembler syntax

Operation

Exceptions

A8.6.12 AND (register)

Assembler syntax

Operation

Exceptions

A8.6.13 AND (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.14 ASR (immediate)

Assembler syntax

Operation

Exceptions

A8.6.15 ASR (register)

Assembler syntax

Operation

Exceptions

A8.6.16 B

Assembler syntax

Operation

Exceptions

A8.6.17 BFC

Assembler syntax

Operation

Exceptions

A8.6.18 BFI

Assembler syntax

Operation

Exceptions

A8.6.19 BIC (immediate)

Assembler syntax

Operation

Exceptions

A8.6.20 BIC (register)

Assembler syntax

Operation

Exceptions

A8.6.21 BIC (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.22 BKPT

Assembler syntax

Operation

Exceptions

A8.6.23 BL, BLX (immediate)

Assembler syntax

Operation

Exceptions

Branch range before ARMv6T2

A8.6.24 BLX (register)

Assembler syntax

Operation

Exceptions

A8.6.25 BX

Assembler syntax

Operation

Exceptions

A8.6.26 BXJ

Assembler syntax

Operation

Exceptions

A8.6.27 CBNZ, CBZ

Assembler syntax

Operation

Exceptions

A8.6.28 CDP, CDP2

Assembler syntax

Operation

Exceptions

A8.6.29 CHKA

A8.6.30 CLREX

Assembler syntax

Operation

Exceptions

A8.6.31 CLZ

Assembler syntax

Operation

Exceptions

A8.6.32 CMN (immediate)

Assembler syntax

Operation

Exceptions

A8.6.33 CMN (register)

Assembler syntax

Operation

Exceptions

A8.6.34 CMN (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.35 CMP (immediate)

Assembler syntax

Operation

Exceptions

A8.6.36 CMP (register)

Assembler syntax

Operation

Exceptions

A8.6.37 CMP (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.38 CPS

A8.6.39 CPY

Assembler syntax

Exceptions

A8.6.40 DBG

Assembler syntax

Operation

Exceptions

A8.6.41 DMB

Assembler syntax

Operation

Exceptions

A8.6.42 DSB

Assembler syntax

Operation

Exceptions

A8.6.43 ENTERX

A8.6.44 EOR (immediate)

Assembler syntax

Operation

Exceptions

A8.6.45 EOR (register)

Assembler syntax

Operation

Exceptions

A8.6.46 EOR (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.47 F* (former VFP instruction mnemonics)

FLDMX, FSTMX

A8.6.48 HB, HBL, HBLP, HBP

A8.6.49 ISB

Assembler syntax

Operation

Exceptions

A8.6.50 IT

Assembler syntax

Operation

Exceptions

A8.6.51 LDC, LDC2 (immediate)

Assembler syntax

Operation

Exceptions

A8.6.52 LDC, LDC2 (literal)

Assembler syntax

Operation

Exceptions

A8.6.53 LDM / LDMIA / LDMFD

Assembler syntax

Operation

Exceptions

A8.6.54 LDMDA / LDMFA

Assembler syntax

Operation

Exceptions

A8.6.55 LDMDB / LDMEA

Assembler syntax

Operation

Exceptions

A8.6.56 LDMIB / LDMED

Assembler syntax

Operation

Exceptions

A8.6.57 LDR (immediate, Thumb)

Assembler syntax

Operation

Exceptions

ThumbEE instruction

A8.6.58 LDR (immediate, ARM)

Assembler syntax

Operation

Exceptions

A8.6.59 LDR (literal)

Assembler syntax

Operation

Exceptions

A8.6.60 LDR (register)

Assembler syntax

Operation

Exceptions

A8.6.61 LDRB (immediate, Thumb)

Assembler syntax

Operation

Exceptions

A8.6.62 LDRB (immediate, ARM)

Assembler syntax

Operation

Exceptions

A8.6.63 LDRB (literal)

Assembler syntax

Operation

Exceptions

A8.6.64 LDRB (register)

Assembler syntax

Operation

Exceptions

A8.6.65 LDRBT

Assembler syntax

Operation

Exceptions

A8.6.66 LDRD (immediate)

Assembler syntax

Operation

Exceptions

A8.6.67 LDRD (literal)

Assembler syntax

Operation

Exceptions

A8.6.68 LDRD (register)

Assembler syntax

Operation

Exceptions

A8.6.69 LDREX

Assembler syntax

Operation

Exceptions

A8.6.70 LDREXB

Assembler syntax

Operation

Exceptions

A8.6.71 LDREXD

Assembler syntax

Operation

Exceptions

A8.6.72 LDREXH

Assembler syntax

Operation

Exceptions

A8.6.73 LDRH (immediate, Thumb)

Assembler syntax

Operation

Exceptions

A8.6.74 LDRH (immediate, ARM)

Assembler syntax

Operation

Exceptions

A8.6.75 LDRH (literal)

Assembler syntax

Operation

Exceptions

A8.6.76 LDRH (register)

Assembler syntax

Operation

Exceptions

A8.6.77 LDRHT

Assembler syntax

Operation

Exceptions

A8.6.78 LDRSB (immediate)

Assembler syntax

Operation

Exceptions

A8.6.79 LDRSB (literal)

Assembler syntax

Operation

Exceptions

A8.6.80 LDRSB (register)

Assembler syntax

Operation

Exceptions

A8.6.81 LDRSBT

Assembler syntax

Operation

Exceptions

A8.6.82 LDRSH (immediate)

Assembler syntax

Operation

Exceptions

A8.6.83 LDRSH (literal)

Assembler syntax

Operation

Exceptions

A8.6.84 LDRSH (register)

Assembler syntax

Operation

Exceptions

A8.6.85 LDRSHT

Assembler syntax

Operation

Exceptions

A8.6.86 LDRT

Assembler syntax

Operation

Exceptions

A8.6.87 LEAVEX

A8.6.88 LSL (immediate)

Assembler syntax

Operation

Exceptions

A8.6.89 LSL (register)

Assembler syntax

Operation

Exceptions

A8.6.90 LSR (immediate)

Assembler syntax

Operation

Exceptions

A8.6.91 LSR (register)

Assembler syntax

Operation

Exceptions

A8.6.92 MCR, MCR2

Assembler syntax

Operation

Exceptions

A8.6.93 MCRR, MCRR2

Assembler syntax

Operation

Exceptions

A8.6.94 MLA

Assembler syntax

Operation

Exceptions

A8.6.95 MLS

Assembler syntax

Operation

Exceptions

A8.6.96 MOV (immediate)

Assembler syntax

Operation

Exceptions

A8.6.97 MOV (register)

Assembler syntax

Operation

Exceptions

A8.6.98 MOV (shifted register)

Assembler syntax

Exceptions

A8.6.99 MOVT

Assembler syntax

Operation

Exceptions

A8.6.100 MRC, MRC2

Assembler syntax

Operation

Exceptions

A8.6.101 MRRC, MRRC2

Assembler syntax

Operation

Exceptions

A8.6.102 MRS

Assembler syntax

Operation

Exceptions

A8.6.103 MSR (immediate)

Assembler syntax

Operation

Exceptions

Usage

A8.6.104 MSR (register)

Assembler syntax

Operation

Exceptions

Usage

A8.6.105 MUL

Assembler syntax

Operation

Exceptions

A8.6.106 MVN (immediate)

Assembler syntax

Operation

Exceptions

A8.6.107 MVN (register)

Assembler syntax

Operation

Exceptions

A8.6.108 MVN (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.109 NEG

Assembler syntax

Exceptions

A8.6.110 NOP

Assembler syntax

Operation

Exceptions

A8.6.111 ORN (immediate)

Assembler syntax

Operation

Exceptions

A8.6.112 ORN (register)

Assembler syntax

Operation

Exceptions

A8.6.113 ORR (immediate)

Assembler syntax

Operation

Exceptions

A8.6.114 ORR (register)

Assembler syntax

Operation

Exceptions

A8.6.115 ORR (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.116 PKH

Assembler syntax

Operation

Exceptions

A8.6.117 PLD, PLDW (immediate)

Assembler syntax

Operation

Exceptions

A8.6.118 PLD (literal)

Assembler syntax

Operation

Exceptions

A8.6.119 PLD, PLDW (register)

Assembler syntax

Operation

Exceptions

A8.6.120 PLI (immediate, literal)

Assembler syntax

Operation

Exceptions

A8.6.121 PLI (register)

Assembler syntax

Operation

Exceptions

A8.6.122 POP

Assembler syntax

Operation

Exceptions

A8.6.123 PUSH

Assembler syntax

Operation

Exceptions

A8.6.124 QADD

Assembler syntax

Operation

Exceptions

A8.6.125 QADD16

Assembler syntax

Operation

Exceptions

A8.6.126 QADD8

Assembler syntax

Operation

Exceptions

A8.6.127 QASX

Assembler syntax

Operation

Exceptions

A8.6.128 QDADD

Assembler syntax

Operation

Exceptions

A8.6.129 QDSUB

Assembler syntax

Operation

Exceptions

A8.6.130 QSAX

Assembler syntax

Operation

Exceptions

A8.6.131 QSUB

Assembler syntax

Operation

Exceptions

A8.6.132 QSUB16

Assembler syntax

Operation

Exceptions

A8.6.133 QSUB8

Assembler syntax

Operation

Exceptions

A8.6.134 RBIT

Assembler syntax

Operation

Exceptions

A8.6.135 REV

Assembler syntax

Operation

Exceptions

A8.6.136 REV16

Assembler syntax

Operation

Exceptions

A8.6.137 REVSH

Assembler syntax

Operation

Exceptions

A8.6.138 RFE

A8.6.139 ROR (immediate)

Assembler syntax

Operation

Exceptions

A8.6.140 ROR (register)

Assembler syntax

Operation

Exceptions

A8.6.141 RRX

Assembler syntax

Operation

Exceptions

A8.6.142 RSB (immediate)

Assembler syntax

Operation

Exceptions

A8.6.143 RSB (register)

Assembler syntax

Operation

Exceptions

A8.6.144 RSB (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.145 RSC (immediate)

Assembler syntax

Operation

Exceptions

A8.6.146 RSC (register)

Assembler syntax

Operation

Exceptions

A8.6.147 RSC (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.148 SADD16

Assembler syntax

Operation

Exceptions

A8.6.149 SADD8

Assembler syntax

Operation

Exceptions

A8.6.150 SASX

Assembler syntax

Operation

Exceptions

A8.6.151 SBC (immediate)

Assembler syntax

Operation

Exceptions

A8.6.152 SBC (register)

Assembler syntax

Operation

Exceptions

A8.6.153 SBC (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.154 SBFX

Assembler syntax

Operation

Exceptions

A8.6.155 SDIV

Assembler syntax

Operation

Exceptions

Overflow

A8.6.156 SEL

Assembler syntax

Operation

Exceptions

A8.6.157 SETEND

Assembler syntax

Operation

Exceptions

A8.6.158 SEV

Assembler syntax

Operation

Exceptions

A8.6.159 SHADD16

Assembler syntax

Operation

Exceptions

A8.6.160 SHADD8

Assembler syntax

Operation

Exceptions

A8.6.161 SHASX

Assembler syntax

Operation

Exceptions

A8.6.162 SHSAX

Assembler syntax

Operation

Exceptions

A8.6.163 SHSUB16

Assembler syntax

Operation

Exceptions

A8.6.164 SHSUB8

Assembler syntax

Operation

Exceptions

A8.6.165 SMC (previously SMI)

A8.6.166 SMLABB, SMLABT, SMLATB, SMLATT

Assembler syntax

Operation

Exceptions

A8.6.167 SMLAD

Assembler syntax

Operation

Exceptions

A8.6.168 SMLAL

Assembler syntax

Operation

Exceptions

A8.6.169 SMLALBB, SMLALBT, SMLALTB, SMLALTT

Assembler syntax

Operation

Exceptions

A8.6.170 SMLALD

Assembler syntax

Operation

Exceptions

A8.6.171 SMLAWB, SMLAWT

Assembler syntax

Operation

Exceptions

A8.6.172 SMLSD

Assembler syntax

Operation

Exceptions

A8.6.173 SMLSLD

Assembler syntax

Operation

Exceptions

A8.6.174 SMMLA

Assembler syntax

Operation

Exceptions

A8.6.175 SMMLS

Assembler syntax

Operation

Exceptions

A8.6.176 SMMUL

Assembler syntax

Operation

Exceptions

A8.6.177 SMUAD

Assembler syntax

Operation

Exceptions

A8.6.178 SMULBB, SMULBT, SMULTB, SMULTT

Assembler syntax

Operation

Exceptions

A8.6.179 SMULL

Assembler syntax

Operation

Exceptions

A8.6.180 SMULWB, SMULWT

Assembler syntax

Operation

Exceptions

A8.6.181 SMUSD

Assembler syntax

Operation

Exceptions

A8.6.182 SRS

A8.6.183 SSAT

Assembler syntax

Operation

Exceptions

A8.6.184 SSAT16

Assembler syntax

Operation

Exceptions

A8.6.185 SSAX

Assembler syntax

Operation

Exceptions

A8.6.186 SSUB16

Assembler syntax

Operation

Exceptions

A8.6.187 SSUB8

Assembler syntax

Operation

Exceptions

A8.6.188 STC, STC2

Assembler syntax

Operation

Exceptions

A8.6.189 STM / STMIA / STMEA

Assembler syntax

Operation

Exceptions

A8.6.190 STMDA / STMED

Assembler syntax

Operation

Exceptions

A8.6.191 STMDB / STMFD

Assembler syntax

Operation

Exceptions

A8.6.192 STMIB / STMFA

Assembler syntax

Operation

Exceptions

A8.6.193 STR (immediate, Thumb)

Assembler syntax

Operation

Exceptions

ThumbEE instruction

A8.6.194 STR (immediate, ARM)

Assembler syntax

Operation

Exceptions

A8.6.195 STR (register)

Assembler syntax

Operation

Exceptions

A8.6.196 STRB (immediate, Thumb)

Assembler syntax

Operation

Exceptions

A8.6.197 STRB (immediate, ARM)

Assembler syntax

Operation

Exceptions

A8.6.198 STRB (register)

Assembler syntax

Operation

Exceptions

A8.6.199 STRBT

Assembler syntax

Operation

Exceptions

A8.6.200 STRD (immediate)

Assembler syntax

Operation

Exceptions

A8.6.201 STRD (register)

Assembler syntax

Operation

Exceptions

A8.6.202 STREX

Assembler syntax

Operation

Exceptions

Aborts and alignment

A8.6.203 STREXB

Assembler syntax

Operation

Exceptions

Aborts

A8.6.204 STREXD

Assembler syntax

Operation

Exceptions

Aborts and alignment

A8.6.205 STREXH

Assembler syntax

Operation

Exceptions

Aborts and alignment

A8.6.206 STRH (immediate, Thumb)

Assembler syntax

Operation

Exceptions

A8.6.207 STRH (immediate, ARM)

Assembler syntax

Operation

Exceptions

A8.6.208 STRH (register)

Assembler syntax

Operation

Exceptions

A8.6.209 STRHT

Assembler syntax

Operation

Exceptions

A8.6.210 STRT

Assembler syntax

Operation

Exceptions

A8.6.211 SUB (immediate, Thumb)

Assembler syntax

Operation

Exceptions

A8.6.212 SUB (immediate, ARM)

Assembler syntax

Operation

Exceptions

A8.6.213 SUB (register)

Assembler syntax

Operation

Exceptions

A8.6.214 SUB (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.215 SUB (SP minus immediate)

Assembler syntax

Operation

Exceptions

A8.6.216 SUB (SP minus register)

Assembler syntax

Operation

Exceptions

A8.6.217 SUBS PC, LR and related instructions

A8.6.218 SVC (previously SWI)

Assembler syntax

Operation

Exceptions

A8.6.219 SWP, SWPB

Assembler syntax

Operation

Exceptions

A8.6.220 SXTAB

Assembler syntax

Operation

Exceptions

A8.6.221 SXTAB16

Assembler syntax

Operation

Exceptions

A8.6.222 SXTAH

Assembler syntax

Operation

Exceptions

A8.6.223 SXTB

Assembler syntax

Operation

Exceptions

A8.6.224 SXTB16

Assembler syntax

Operation

Exceptions

A8.6.225 SXTH

Assembler syntax

Operation

Exceptions

A8.6.226 TBB, TBH

Assembler syntax

Operation

Exceptions

A8.6.227 TEQ (immediate)

Assembler syntax

Operation

Exceptions

A8.6.228 TEQ (register)

Assembler syntax

Operation

Exceptions

A8.6.229 TEQ (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.230 TST (immediate)

Assembler syntax

Operation

Exceptions

A8.6.231 TST (register)

Assembler syntax

Operation

Exceptions

A8.6.232 TST (register-shifted register)

Assembler syntax

Operation

Exceptions

A8.6.233 UADD16

Assembler syntax

Operation

Exceptions

A8.6.234 UADD8

Assembler syntax

Operation

Exceptions

A8.6.235 UASX

Assembler syntax

Operation

Exceptions

A8.6.236 UBFX

Assembler syntax

Operation

Exceptions

A8.6.237 UDIV

Assembler syntax

Operation

Exceptions

A8.6.238 UHADD16

Assembler syntax

Operation

Exceptions

A8.6.239 UHADD8

Assembler syntax

Operation

Exceptions

A8.6.240 UHASX

Assembler syntax

Operation

Exceptions

A8.6.241 UHSAX

Assembler syntax

Operation

Exceptions

A8.6.242 UHSUB16

Assembler syntax

Operation

Exceptions

A8.6.243 UHSUB8

Assembler syntax

Operation

Exceptions

A8.6.244 UMAAL

Assembler syntax

Operation

Exceptions

A8.6.245 UMLAL

Assembler syntax

Operation

Exceptions

A8.6.246 UMULL

Assembler syntax

Operation

Exceptions

A8.6.247 UQADD16

Assembler syntax

Operation

Exceptions

A8.6.248 UQADD8

Assembler syntax

Operation

Exceptions

A8.6.249 UQASX

Assembler syntax

Operation

Exceptions

A8.6.250 UQSAX

Assembler syntax

Operation

Exceptions

A8.6.251 UQSUB16

Assembler syntax

Operation

Exceptions

A8.6.252 UQSUB8

Assembler syntax

Operation

Exceptions

A8.6.253 USAD8

Assembler syntax

Operation

Exceptions

A8.6.254 USADA8

Assembler syntax

Operation

Exceptions

A8.6.255 USAT

Assembler syntax

Operation

Exceptions

A8.6.256 USAT16

Assembler syntax

Operation

Exceptions

A8.6.257 USAX

Assembler syntax

Operation

Exceptions

A8.6.258 USUB16

Assembler syntax

Operation

Exceptions

A8.6.259 USUB8

Assembler syntax

Operation

Exceptions

A8.6.260 UXTAB

Assembler syntax

Operation

Exceptions

A8.6.261 UXTAB16

Assembler syntax

Operation

Exceptions

A8.6.262 UXTAH

Assembler syntax

Operation

Exceptions

A8.6.263 UXTB

Assembler syntax

Operation

Exceptions

A8.6.264 UXTB16

Assembler syntax

Operation

Exceptions

A8.6.265 UXTH

Assembler syntax

Operation

Exceptions

A8.6.266 VABA, VABAL

Assembler syntax

Operation

Exceptions

A8.6.267 VABD, VABDL (integer)

Assembler syntax

Operation

Exceptions

A8.6.268 VABD (floating-point)

Assembler syntax

Operation

Exceptions

A8.6.269 VABS

Assembler syntax

Operation

Exceptions

A8.6.270 VACGE, VACGT, VACLE,VACLT

Assembler syntax

Operation

Exceptions

A8.6.271 VADD (integer)

Assembler syntax

Operation

Exceptions

A8.6.272 VADD (floating-point)

Assembler syntax

Operation

Exceptions

A8.6.273 VADDHN

Assembler syntax

Operation

Exceptions

A8.6.274 VADDL, VADDW

Assembler syntax

Operation

Exceptions

A8.6.275 VAND (immediate)

A8.6.276 VAND (register)

Assembler syntax

Operation

Exceptions

A8.6.277 VBIC (immediate)

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.278 VBIC (register)

Assembler syntax

Operation

Exceptions

A8.6.279 VBIF, VBIT, VBSL

Assembler syntax

Operation

Exceptions

A8.6.280 VCEQ (register)

Assembler syntax

Operation

Exceptions

A8.6.281 VCEQ (immediate #0)

Assembler syntax

Operation

Exceptions

A8.6.282 VCGE (register)

Assembler syntax

Operation

Exceptions

A8.6.283 VCGE (immediate #0)

Assembler syntax

Operation

Exceptions

A8.6.284 VCGT (register)

Assembler syntax

Operation

Exceptions

A8.6.285 VCGT (immediate #0)

Assembler syntax

Operation

Exceptions

A8.6.286 VCLE (register)

A8.6.287 VCLE (immediate #0)

Assembler syntax

Operation

Exceptions

A8.6.288 VCLS

Assembler syntax

Operation

Exceptions

A8.6.289 VCLT (register)

A8.6.290 VCLT (immediate #0)

Assembler syntax

Operation

Exceptions

A8.6.291 VCLZ

Assembler syntax

Operation

Exceptions

A8.6.292 VCMP, VCMPE

Assembler syntax

Operation

Exceptions

NaNs

A8.6.293 VCNT

Assembler syntax

Operation

Exceptions

A8.6.294 VCVT (between floating-point and integer, Advanced SIMD)

Assembler syntax

Operation

Exceptions

A8.6.295 VCVT, VCVTR (between floating-point and integer, VFP)

Assembler syntax

Operation

Exceptions

A8.6.296 VCVT (between floating-point and fixed-point, Advanced SIMD)

Assembler syntax

Operation

Exceptions

A8.6.297 VCVT (between floating-point and fixed-point, VFP)

Assembler syntax

Operation

Exceptions

A8.6.298 VCVT (between double-precision and single-precision)

Assembler syntax

Operation

Exceptions

A8.6.299 VCVT (between half-precision and single-precision, Advanced SIMD)

Assembler syntax

Operation

Exceptions

A8.6.300 VCVTB, VCVTT (between half-precision and single-precision, VFP)

Assembler syntax

Operation

Exceptions

A8.6.301 VDIV

Assembler syntax

Operation

Exceptions

A8.6.302 VDUP (scalar)

Assembler syntax

Operation

Exceptions

A8.6.303 VDUP (ARM core register)

Assembler syntax

Operation

Exceptions

A8.6.304 VEOR

Assembler syntax

Operation

Exceptions

A8.6.305 VEXT

Assembler syntax

Operation

Exceptions

A8.6.306 VHADD, VHSUB

Assembler syntax

Operation

Exceptions

A8.6.307 VLD1 (multiple single elements)

Assembler syntax

Operation

Exceptions

A8.6.308 VLD1 (single element to one lane)

Assembler syntax

Operation

Exceptions

A8.6.309 VLD1 (single element to all lanes)

Assembler syntax

Operation

Exceptions

A8.6.310 VLD2 (multiple 2-element structures)

Assembler syntax

Operation

Exceptions

A8.6.311 VLD2 (single 2-element structure to one lane)

Assembler syntax

Operation

Exceptions

A8.6.312 VLD2 (single 2-element structure to all lanes)

Assembler syntax

Operation

Exceptions

A8.6.313 VLD3 (multiple 3-element structures)

Assembler syntax

Operation

Exceptions

A8.6.314 VLD3 (single 3-element structure to one lane)

Assembler syntax

Alignment

Operation

Exceptions

A8.6.315 VLD3 (single 3-element structure to all lanes)

Assembler syntax

Alignment

Operation

Exceptions

A8.6.316 VLD4 (multiple 4-element structures)

Assembler syntax

Operation

Exceptions

A8.6.317 VLD4 (single 4-element structure to one lane)

Assembler syntax

Operation

Exceptions

A8.6.318 VLD4 (single 4-element structure to all lanes)

Assembler syntax

Operation

Exceptions

A8.6.319 VLDM

Assembler syntax

Operation

Exceptions

A8.6.320 VLDR

Assembler syntax

Operation

Exceptions

A8.6.321 VMAX, VMIN (integer)

Assembler syntax

Operation

Exceptions

A8.6.322 VMAX, VMIN (floating-point)

Assembler syntax

Operation

Exceptions

Floating-point maximum and minimum

A8.6.323 VMLA, VMLAL, VMLS, VMLSL (integer)

Assembler syntax

Operation

Exceptions

A8.6.324 VMLA, VMLS (floating-point)

Assembler syntax

Operation

Exceptions

A8.6.325 VMLA, VMLAL, VMLS, VMLSL (by scalar)

Assembler syntax

Operation

Exceptions

A8.6.326 VMOV (immediate)

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.327 VMOV (register)

Assembler syntax

Operation

Exceptions

A8.6.328 VMOV (ARM core register to scalar)

Assembler syntax

Operation

Exceptions

A8.6.329 VMOV (scalar to ARM core register)

Assembler syntax

Operation

Exceptions

A8.6.330 VMOV (between ARM core register and single-precision register)

Assembler syntax

Operation

Exceptions

A8.6.331 VMOV (between two ARM core registers and two single-precision registers)

Assembler syntax

Operation

Exceptions

A8.6.332 VMOV (between two ARM core registers and a doubleword extension register)

Assembler syntax

Operation

Exceptions

A8.6.333 VMOVL

Assembler syntax

Operation

Exceptions

A8.6.334 VMOVN

Assembler syntax

Operation

Exceptions

A8.6.335 VMRS

Assembler syntax

Operation

Exceptions

A8.6.336 VMSR

Assembler syntax

Operation

Exceptions

A8.6.337 VMUL, VMULL (integer and polynomial)

Assembler syntax

Operation

Exceptions

A8.6.338 VMUL (floating-point)

Assembler syntax

Operation

Exceptions

A8.6.339 VMUL, VMULL (by scalar)

Assembler syntax

Operation

Exceptions

A8.6.340 VMVN (immediate)

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.341 VMVN (register)

Assembler syntax

Operation

Exceptions

A8.6.342 VNEG

Assembler syntax

Operation

Exceptions

A8.6.343 VNMLA, VNMLS, VNMUL

Assembler syntax

Operation

Exceptions

A8.6.344 VORN (immediate)

A8.6.345 VORN (register)

Assembler syntax

Operation

Exceptions

A8.6.346 VORR (immediate)

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.347 VORR (register)

Assembler syntax

Operation

Exceptions

A8.6.348 VPADAL

Assembler syntax

Operation

Exceptions

A8.6.349 VPADD (integer)

Assembler syntax

Operation

Exceptions

A8.6.350 VPADD (floating-point)

Assembler syntax

Operation

Exceptions

A8.6.351 VPADDL

Assembler syntax

Operation

Exceptions

A8.6.352 VPMAX, VPMIN (integer)

Assembler syntax

Operation

Exceptions

A8.6.353 VPMAX, VPMIN (floating-point)

Assembler syntax

Operation

Exceptions

A8.6.354 VPOP

Assembler syntax

Operation

Exceptions

A8.6.355 VPUSH

Assembler syntax

Operation

Exceptions

A8.6.356 VQABS

Assembler syntax

Operation

Exceptions

A8.6.357 VQADD

Assembler syntax

Operation

Exceptions

A8.6.358 VQDMLAL, VQDMLSL

Assembler syntax

Operation

Exceptions

A8.6.359 VQDMULH

Assembler syntax

Operation

Exceptions

A8.6.360 VQDMULL

Assembler syntax

Operation

Exceptions

A8.6.361 VQMOVN, VQMOVUN

Assembler syntax

Operation

Exceptions

A8.6.362 VQNEG

Assembler syntax

Operation

Exceptions

A8.6.363 VQRDMULH

Assembler syntax

Operation

Exceptions

A8.6.364 VQRSHL

Assembler syntax

Operation

Exceptions

A8.6.365 VQRSHRN, VQRSHRUN

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.366 VQSHL (register)

Assembler syntax

Operation

Exceptions

A8.6.367 VQSHL, VQSHLU (immediate)

Assembler syntax

Operation

Exceptions

A8.6.368 VQSHRN, VQSHRUN

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.369 VQSUB

Assembler syntax

Operation

Exceptions

A8.6.370 VRADDHN

Assembler syntax

Operation

Exceptions

A8.6.371 VRECPE

Assembler syntax

Operation

Exceptions

Newton-Raphson iteration

A8.6.372 VRECPS

Assembler syntax

Operation

Exceptions

Newton-Raphson iteration

A8.6.373 VREV16, VREV32, VREV64

Assembler syntax

Operation

Exceptions

A8.6.374 VRHADD

Assembler syntax

Operation

Exceptions

A8.6.375 VRSHL

Assembler syntax

Operation

Exceptions

A8.6.376 VRSHR

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.377 VRSHRN

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.378 VRSQRTE

Assembler syntax

Operation

Exceptions

Newton-Raphson iteration

A8.6.379 VRSQRTS

Assembler syntax

Operation

Exceptions

Newton-Raphson iteration

A8.6.380 VRSRA

Assembler syntax

Operation

Exceptions

A8.6.381 VRSUBHN

Assembler syntax

Operation

Exceptions

A8.6.382 VSHL (immediate)

Assembler syntax

Operation

Exceptions

A8.6.383 VSHL (register)

Assembler syntax

Operation

Exceptions

A8.6.384 VSHLL

Assembler syntax

Operation

Exceptions

A8.6.385 VSHR

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.386 VSHRN

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.387 VSLI

Assembler syntax

Operation

Exceptions

A8.6.388 VSQRT

Assembler syntax

Operation

Exceptions

A8.6.389 VSRA

Assembler syntax

Operation

Exceptions

A8.6.390 VSRI

Assembler syntax

Operation

Exceptions

A8.6.391 VST1 (multiple single elements)

Assembler syntax

Operation

Exceptions

A8.6.392 VST1 (single element from one lane)

Assembler syntax

Operation

Exceptions

A8.6.393 VST2 (multiple 2-element structures)

Assembler syntax

Operation

Exceptions

A8.6.394 VST2 (single 2-element structure from one lane)

Assembler syntax

Operation

Exceptions

A8.6.395 VST3 (multiple 3-element structures)

Assembler syntax

Operation

Exceptions

A8.6.396 VST3 (single 3-element structure from one lane)

Assembler syntax

Alignment

Operation

Exceptions

A8.6.397 VST4 (multiple 4-element structures)

Assembler syntax

Operation

Exceptions

A8.6.398 VST4 (single 4-element structure from one lane)

Assembler syntax

Operation

Exceptions

A8.6.399 VSTM

Assembler syntax

Operation

Exceptions

A8.6.400 VSTR

Assembler syntax

Operation

Exceptions

A8.6.401 VSUB (integer)

Assembler syntax

Operation

Exceptions

A8.6.402 VSUB (floating-point)

Assembler syntax

Operation

Exceptions

A8.6.403 VSUBHN

Assembler syntax

Operation

Exceptions

A8.6.404 VSUBL, VSUBW

Assembler syntax

Operation

Exceptions

A8.6.405 VSWP

Assembler syntax

Operation

Exceptions

A8.6.406 VTBL, VTBX

Assembler syntax

Operation

Exceptions

A8.6.407 VTRN

Assembler syntax

Operation

Exceptions

A8.6.408 VTST

Assembler syntax

Operation

Exceptions

A8.6.409 VUZP

Assembler syntax

Operation

Exceptions

Pseudo-instruction

A8.6.410 VZIP

Assembler syntax

Operation

Exceptions

Pseudo-instructions

A8.6.411 WFE

Assembler syntax

Operation

Exceptions

A8.6.412 WFI

Assembler syntax

Operation

Exceptions

A8.6.413 YIELD

Assembler syntax

Operation

Exceptions

ThumbEE

A9.1 The ThumbEE instruction set

A9.1.1 ThumbEE state transitions

A9.1.2 Null checking

A9.1.3 Instructions with modifications

A9.1.4 IT block and check handlers

A9.2 ThumbEE instruction set encoding

A9.2.1 16-bit ThumbEE instructions

A9.3 Additional instructions in Thumb and ThumbEE instruction sets

A9.3.1 ENTERX, LEAVEX

Assembler syntax

Operation

Exceptions

A9.4 ThumbEE instructions with modified behavior

A9.4.1 LDR (register)

Assembler syntax

Operation

Exceptions and checks

A9.4.2 LDRH (register)

Assembler syntax

Operation

Exceptions and checks

A9.4.3 LDRSH (register)

Assembler syntax

Operation

Exceptions and checks

A9.4.4 STR (register)

Assembler syntax

Operation

Exceptions and checks

A9.4.5 STRH (register)

Assembler syntax

Operation

Exceptions and checks

A9.5 Additional ThumbEE instructions

A9.5.1 CHKA

Assembler syntax

Operation

Exceptions and checks

Usage

A9.5.2 HB, HBL

Assembler syntax

Operation

Exceptions

Usage

A9.5.3 HBLP

Assembler syntax

Operation

Exceptions

A9.5.4 HBP

Assembler syntax

Operation

Exceptions

A9.5.5 LDR (immediate)

Assembler syntax

Operation

Exceptions and checks

A9.5.6 STR (immediate)

Assembler syntax

Operation

Exceptions and checks

System Level Architecture

The System Level Programmers’ Model

B1.1 About the system level programmers’ model

B1.2 System level concepts and terminology

B1.2.1 Privilege, mode, and state

Privilege

Mode

State

B1.2.2 Exceptions

Terminology for describing exceptions

B1.3 ARM processor modes and core registers

B1.3.1 ARM processor modes

Notes on the ARM processor modes

Pseudocode details of mode operations

B1.3.2 ARM core registers

Writing to the PC

Pseudocode details of ARM core register operations

B1.3.3 Program Status Registers (PSRs)

The Current Program Status Register (CPSR)

The Saved Program Status Registers (SPSRs)

Format of the CPSR and SPSRs

Accessing the execution state bits

Non-maskable fast interrupts

Use of the A, F, and Mode bits by the Security Extensions

Pseudocode details of PSR operations

B1.4 Instruction set states

B1.4.1 Exceptions and instruction set state

B1.4.2 Unimplemented instruction sets

B1.5 The Security Extensions

B1.5.1 Security states

Changing from Secure to Non-secure state

Pseudocode details of Secure state operations

B1.5.2 Impact of the Security Extensions on the modes and exception model

B1.6 Exceptions

B1.6.1 Exception vectors and the exception base address

Vectored interrupt support

Operation

B1.6.2 Exception priority order

B1.6.3 Exception entry

Instruction set state on exception entry

CPSR M field and A, I, and F mask bit values on exception entry

CPSR.E bit value on exception entry

B1.6.4 Exception return

Alignment of exception returns

Exception return to an unsupported instruction set state

B1.6.5 Exception-handling instructions

B1.6.6 Control of exception handling by the Security Extensions

Control of aborts by the Security Extensions

Control of FIQs by the Security Extensions

Control of IRQs by the Security Extensions

B1.6.7 Low interrupt latency configuration

B1.6.8 Wait For Event and Send Event

WFE wake-up events

The Event Register

The Send Event instruction

The Wait For Event instruction

Pseudocode details of the Wait For Event lock mechanism

B1.6.9 Wait For Interrupt

Using WFI to indicate an idle state on bus interfaces

Pseudocode details of Wait For Interrupt

B1.6.10 Reset

B1.6.11 Undefined Instruction exception

Conditional execution of undefined instructions

B1.6.12 Supervisor Call (SVC) exception

B1.6.13 Secure Monitor Call (SMC) exception

B1.6.14 Prefetch Abort exception

B1.6.15 Data Abort exception

Effects of data-aborted instructions

The ARM abort model

B1.6.16 IRQ exception

B1.6.17 FIQ exception

B1.7 Coprocessors and system control

B1.7.1 CP15 System Control coprocessor registers

B1.7.2 Access controls on CP0 to CP13

B1.8 Advanced SIMD and floating-point support

B1.8.1 Enabling Advanced SIMD and floating-point support

Pseudocode details of enabling the Advanced SIMD and VFP extensions

B1.8.2 Advanced SIMD and VFP extension system registers

Register map of the Advanced SIMD and VFP extension system registers

Accessing the Advanced SIMD and VFP extension system registers

B1.8.3 The Floating-Point Exception Register (FPEXC)

B1.8.4 Context switching with the Advanced SIMD and VFP extensions

B1.8.5 VFP support code

Asynchronous bounces, serialization, and VFP exception barriers

Interactions with the ARM architecture

Interrupts

B1.8.6 VFP subarchitecture support

B1.9 Execution environment support

B1.9.1 Thumb Execution Environment

ThumbEE and the Security Extensions

Aborts, exceptions, and checks

B1.9.2 Jazelle direct bytecode execution

Extension of the PC to 32 bits

Exception handling in the Jazelle extension

Jazelle state configuration and control

Jazelle OS Control Register (JOSCR)

EJVM operation

Trivial implementation of the Jazelle extension

Jazelle state

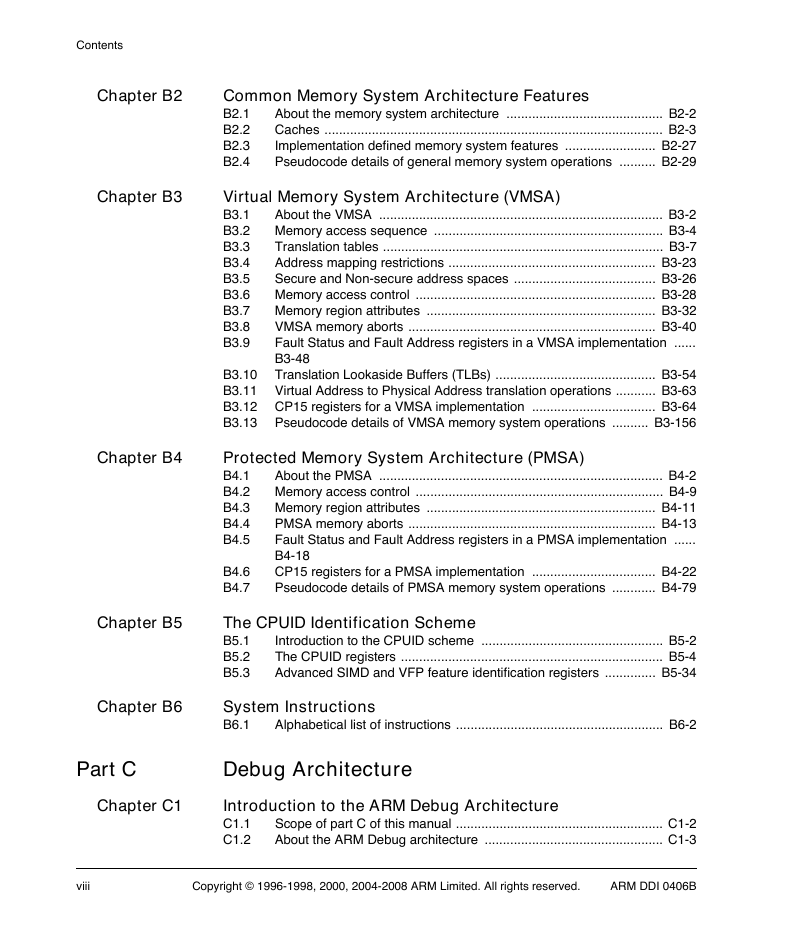

Common Memory System Architecture Features

B2.1 About the memory system architecture

B2.1.1 Form of the memory system architecture

B2.1.2 Memory attributes

B2.1.3 Levels of cache

B2.2 Caches

B2.2.1 Cache identification

Identifying the cache resources in ARMv7

B2.2.2 Cache behavior

General behavior of the caches

Behavior of the caches at reset

Behavior of Preload Data (PLD, PLDW) and Preload Instruction (PLI) with caches

Cache lockdown

B2.2.3 Cache enabling and disabling

B2.2.4 Cache maintenance functionality

Terms used in describing cache operations

ARMv7 cache maintenance operations

The ARMv7 abstraction of the cache hierarchy

B2.2.5 The interaction of cache lockdown with cache maintenance

Additional cache functions for the implementation of lockdown

B2.2.6 Branch predictors

Branch prediction maintenance operations

Behavior of the branch predictors at reset

B2.2.7 Ordering of cache and branch predictor maintenance operations

B2.2.8 Multiprocessor effects on cache maintenance operations

Base ARMv7 architecture

Multiprocessing Extensions

B2.2.9 System-level caches

B2.3 Implementation defined memory system features

B2.3.1 ARMv7 CP15 register support for implementation defined features

B2.4 Pseudocode details of general memory system operations

B2.4.1 Memory data type definitions

B2.4.2 Basic memory accesses

B2.4.3 Interfaces to memory system specific pseudocode

B2.4.4 Aligned memory accesses

B2.4.5 Unaligned memory accesses

B2.4.6 Reverse endianness

B2.4.7 Exclusive monitors operations

B2.4.8 Access permission checking

B2.4.9 Default memory access decode

B2.4.10 Data Abort exception

Virtual Memory System Architecture (VMSA)

B3.1 About the VMSA

B3.2 Memory access sequence

B3.2.1 FCSE translation

B3.2.2 Translation from MVA to PA using the translation tables

B3.2.3 Enabling and disabling the MMU

B3.3 Translation tables

B3.3.1 Translation table entry formats

First-level descriptors

Second-level descriptors

Additional requirements for translation tables

B3.3.2 Translation table base registers

B3.3.3 Translation table walks

Reading a first-level translation table

Reading a second-level translation table

The full translation flow for Sections, Supersections, Small pages and Large pages

B3.3.4 Changing translation table attributes

B3.3.5 The access flag

Software management of the access flag

Hardware management of the access flag

Changing the access flag enable

B3.4 Address mapping restrictions

B3.4.1 Requirements for instruction caches

B3.4.2 Instruction cache maintenance operations by MVA

B3.5 Secure and Non-secure address spaces

B3.5.1 The effect of the Security Extensions on the cache operations

B3.6 Memory access control

B3.6.1 Access permissions

Simplified access permissions model

B3.6.2 The Execute Never (XN) attribute and instruction prefetching

B3.6.3 Domains

B3.7 Memory region attributes

B3.7.1 The alternative descriptions of the Memory region attributes

B3.7.2 C, B, and TEX[2:0] encodings without TEX remap

Cacheable memory attributes

B3.7.3 Memory region attribute descriptions when TEX remap is enabled

Interpretation of the NOSn fields in the PRRR

SCTLR.TRE, SCTLR.M, and the effect of the MMU remap registers

The OS managed translation table bits

B3.7.4 The effect of the Security Extensions on TEX remapping

B3.8 VMSA memory aborts

B3.8.1 MMU faults

Fault-checking sequence

Alignment fault

External abort on a translation table walk

Translation fault

Access Flag fault

Domain fault

Permission fault

B3.8.2 External aborts

External abort on instruction fetch

External abort on data read or write

External abort on a translation table walk

Behavior of external aborts on a translation table walk caused by a VA to PA translation

Parity error reporting

B3.8.3 Prioritization of aborts

B3.9 Fault Status and Fault Address registers in a VMSA implementation

B3.9.1 About the Fault Status and Fault Address registers

B3.9.2 Data Abort exceptions

B3.9.3 Prefetch Abort exceptions

B3.9.4 Fault Status Register encodings for the VMSA

Reserved encodings in the IFSR and DFSR encodings tables

B3.9.5 Distinguishing read and write accesses on Data Abort exceptions

B3.9.6 Provision for classification of external aborts

B3.9.7 The Domain field in the DFSR

B3.9.8 Auxiliary Fault Status Registers

B3.10 Translation Lookaside Buffers (TLBs)

B3.10.1 Global and non-global regions in the virtual memory map

B3.10.2 TLB matching

TLB block size

B3.10.3 TLB behavior at reset

B3.10.4 TLB lockdown

B3.10.5 TLB maintenance

The interaction of TLB maintenance operations with TLB lockdown

The effect of the Security Extensions on the TLB maintenance operations

TLB maintenance operations and the memory order model

Synchronization of changes of ASID and TTBR

Multiprocessor effects on TLB maintenance operations

B3.11 Virtual Address to Physical Address translation operations

B3.12 CP15 registers for a VMSA implementation

B3.12.1 Organization of the CP15 registers in a VMSA implementation

Summary of CP15 register descriptions in a VMSA implementation

B3.12.2 General behavior of CP15 registers

Read-only bits in read/write registers

Unpredictable and undefined behavior for CP15 accesses

Reset behavior of CP15 registers

B3.12.3 Effect of the Security Extensions on the CP15 registers

Banked CP15 registers

Restricted access CP15 registers

Configurable access CP15 registers

Common CP15 registers

Secure CP15 registers

The CP15SDISABLE input

Access to registers in Monitor mode

B3.12.4 Changes to CP15 registers and the memory order model

B3.12.5 Meaning of fixed bit values in register diagrams

B3.12.6 CP15 c0, ID codes registers

B3.12.7 c0, Main ID Register (MIDR)

Accessing the MIDR

B3.12.8 c0, Cache Type Register (CTR)

Accessing the CTR

B3.12.9 c0, TCM Type Register (TCMTR)

Accessing the TCMTR

B3.12.10 c0, TLB Type Register (TLBTR)

Accessing the TLBTR

B3.12.11 c0, Multiprocessor Affinity Register (MPIDR)

Multi-threading approach to lowest affinity levels, Multiprocessing Extensions

Recommended use of the MPIDR

Accessing the MPIDR

B3.12.12 c0, Cache Size ID Registers (CCSIDR)

Accessing the currently selected CCSIDR

B3.12.13 c0, Cache Level ID Register (CLIDR)

Accessing the CLIDR

B3.12.14 c0, Implementation defined Auxiliary ID Register (AIDR)

Accessing the AIDR

B3.12.15 c0, Cache Size Selection Register (CSSELR)

Accessing CSSELR

B3.12.16 CP15 c1, System control registers

B3.12.17 c1, System Control Register (SCTLR)

Reset value of the SCTLR

Accessing the SCTLR

B3.12.18 c1, Implementation defined Auxiliary Control Register (ACTLR)

Accessing the ACTLR

B3.12.19 c1, Coprocessor Access Control Register (CPACR)

Accessing the CPACR

B3.12.20 c1, Secure Configuration Register (SCR)

Accessing the SCR

B3.12.21 c1, Secure Debug Enable Register (SDER)

Accessing the SDER

B3.12.22 c1, Non-Secure Access Control Register (NSACR)

Accessing the NSACR

B3.12.23 CP15 c2 and c3, Memory protection and control registers

B3.12.24 CP15 c2, Translation table support registers

c2, Translation Table Base Register 0 (TTBR0)

c2, Translation Table Base Register 1 (TTBR1)

c2, Translation Table Base Control Register (TTBCR)

B3.12.25 c3, Domain Access Control Register (DACR)

Accessing the DACR

B3.12.26 CP15 c4, Not used

B3.12.27 CP15 c5 and c6, Memory system fault registers

B3.12.28 CP15 c5, Fault status registers

c5, Data Fault Status Register (DFSR)

c5, Instruction Fault Status Register (IFSR)

c5, Auxiliary Data and Instruction Fault Status Registers (ADFSR and AIFSR)

B3.12.29 CP15 c6, Fault Address registers

c6, Data Fault Address Register (DFAR)

c6, Instruction Fault Address Register (IFAR)

B3.12.30 CP15 c7, Cache maintenance and other functions

B3.12.31 CP15 c7, Cache and branch predictor maintenance functions

Data formats for the cache and branch predictor operations

Accessing the CP15 c7 cache and branch predictor maintenance operations

B3.12.32 CP15 c7, Virtual Address to Physical Address translation operations

c7, Physical Address Register (PAR) and VA to PA translations

Accessing the PAR and the VA to PA translation operations

VA to PA translation when the MMU is disabled

B3.12.33 CP15 c7, Miscellaneous functions

CP15 c7, Data and Instruction Barrier operations

CP15 c7, No Operation (NOP)

B3.12.34 CP15 c8, TLB maintenance operations

About the TLB maintenance operations

Accessing the CP15 c8 TLB maintenance operations

B3.12.35 CP15 c9, Cache and TCM lockdown registers and performance monitors

B3.12.36 CP15 c10, Memory remapping and TLB control registers

The implementation defined TLB control operations

B3.12.37 CP15 c10, Memory Remap Registers

c10, Primary Region Remap Register (PRRR)

c10, Normal Memory Remap Register (NMRR)

B3.12.38 CP15 c11, Reserved for TCM DMA registers

B3.12.39 CP15 c12, Security Extensions registers

B3.12.40 c12, Vector Base Address Register (VBAR)

Accessing the VBAR

B3.12.41 c12, Monitor Vector Base Address Register (MVBAR)

Accessing the MVBAR

B3.12.42 c12, Interrupt Status Register (ISR)

Accessing the ISR

B3.12.43 CP15 c13, Process, context and thread ID registers

B3.12.44 c13, FCSE Process ID Register (FCSEIDR)

Accessing the FCSEIDR

B3.12.45 c13, Context ID Register (CONTEXTIDR)

Using the CONTEXTIDR

Accessing the CONTEXTIDR

B3.12.46 CP15 c13 Software Thread ID registers

Accessing the Software Thread ID registers

B3.12.47 CP15 c14, Not used

B3.12.48 CP15 c15, Implementation defined registers

B3.13 Pseudocode details of VMSA memory system operations

B3.13.1 Alignment fault

B3.13.2 FCSE translation

B3.13.3 Address translation

B3.13.4 Domain checking

B3.13.5 TLB operations

B3.13.6 Translation table walk

Protected Memory System Architecture (PMSA)

B4.1 About the PMSA

B4.1.1 Protection regions

B4.1.2 Subregions

B4.1.3 Overlapping regions

B4.1.4 The background region

Using the default memory map as a background region

B4.1.5 Enabling and disabling the MPU

Behavior when the MPU is disabled

Behavior of an implementation that does not include an MPU

B4.1.6 Finding the minimum supported region size

B4.2 Memory access control

B4.2.1 Access permissions

The Execute Never (XN) attribute and instruction prefetching

B4.3 Memory region attributes

B4.3.1 C, B, and TEX[2:0] encodings

Cacheable memory attributes

B4.4 PMSA memory aborts

B4.4.1 MPU faults

Alignment fault

Background fault

Permission fault

The MPU fault checking sequence

B4.4.2 External aborts

External abort on instruction fetch

External abort on data read or write

Parity error reporting

B4.4.3 Prioritization of aborts

B4.5 Fault Status and Fault Address registers in a PMSA implementation

B4.5.1 About the Fault Status and Fault Address registers

B4.5.2 Data Abort exceptions

B4.5.3 Prefetch Abort exceptions

B4.5.4 Fault Status Register encodings for the PMSA

Reserved encodings in the IFSR and DFSR encodings tables

B4.5.5 Distinguishing read and write accesses on Data Abort exceptions

B4.5.6 Provision for classification of external aborts

B4.5.7 Auxiliary Fault Status Registers

B4.6 CP15 registers for a PMSA implementation

B4.6.1 Organization of the CP15 registers in a PMSA implementation

Summary of CP15 register descriptions in a PMSA implementation

B4.6.2 General behavior of CP15 registers

Read-only bits in read/write registers

Unpredictable and undefined behavior for CP15 accesses

Reset behavior of CP15 registers

B4.6.3 Changes to CP15 registers and the memory order model

B4.6.4 Meaning of fixed bit values in register diagrams

B4.6.5 CP15 c0, ID codes registers

B4.6.6 c0, Main ID Register (MIDR)

Accessing the MIDR

B4.6.7 c0, Cache Type Register (CTR)

Accessing the CTR

B4.6.8 c0, TCM Type Register (TCMTR)

Accessing the TCMTR

B4.6.9 c0, MPU Type Register (MPUIR)

Accessing the MPUIR

B4.6.10 c0, Multiprocessor Affinity Register (MPIDR)

Recommended use of the MPIDR

Accessing the MPIDR

B4.6.11 c0, Cache Size ID Registers (CCSIDR)

Accessing the currently selected CCSIDR

B4.6.12 c0, Cache Level ID Register (CLIDR)

Accessing the CLIDR

B4.6.13 c0, Implementation defined Auxiliary ID Register (AIDR)

Accessing the AIDR

B4.6.14 c0, Cache Size Selection Register (CSSELR)

Accessing CSSELR

B4.6.15 CP15 c1, System control registers

B4.6.16 c1, System Control Register (SCTLR)

Reset value of the SCTLR

Accessing the SCTLR

B4.6.17 c1, Implementation defined Auxiliary Control Register (ACTLR)

Accessing the ACTLR

B4.6.18 c1, Coprocessor Access Control Register (CPACR)

Accessing the CPACR

B4.6.19 CP15 c2 and c3, Not used on a PMSA implementation

B4.6.20 CP15 c4, Not used

B4.6.21 CP15 c5 and c6, Memory system fault registers

B4.6.22 CP15 c5, Fault status registers

c5, Data Fault Status Register (DFSR)

c5, Instruction Fault Status Register (IFSR)

c5, Auxiliary Data and Instruction Fault Status Registers (ADFSR and AIFSR)

B4.6.23 CP15 c6, Fault Address registers

c6, Data Fault Address Register (DFAR)

c6, Instruction Fault Address Register (IFAR)

B4.6.24 CP15 c6, Memory region programming registers

c6, Data Region Base Address Register (DRBAR)

c6, Instruction Region Base Address Register (IRBAR)

c6, Data Region Size and Enable Register (DRSR)

c6, Instruction Region Size and Enable Register (IRSR)

c6, Data Region Access Control Register (DRACR)

c6, Instruction Region Access Control Register (IRACR)

c6, MPU Region Number Register (RGNR)

B4.6.25 CP15 c7, Cache maintenance and other functions

B4.6.26 CP15 c7, Cache and branch predictor maintenance functions

Data formats for the cache and branch predictor operations

Accessing the CP15 c7 cache maintenance operations

B4.6.27 CP15 c7, Miscellaneous functions

CP15 c7, Data and Instruction Barrier operations

CP15 c7, No Operation (NOP)

B4.6.28 CP15 c8, Not used on a PMSA implementation

B4.6.29 CP15 c9, Cache and TCM lockdown registers and performance monitors

B4.6.30 CP15 c10, Not used on a PMSA implementation

B4.6.31 CP15 c11, Reserved for TCM DMA registers

B4.6.32 CP15 c12, Not used on a PMSA implementation

B4.6.33 CP15 c13, Context and Thread ID registers

B4.6.34 c13, Context ID Register (CONTEXTIDR)

Accessing the CONTEXTIDR

B4.6.35 CP15 c13 Software Thread ID registers

Accessing the Software Thread ID registers

B4.6.36 CP15 c14, Not used

B4.6.37 CP15 c15, Implementation defined registers

B4.7 Pseudocode details of PMSA memory system operations

B4.7.1 Alignment fault

B4.7.2 Address translation

B4.7.3 Default memory map attributes

The CPUID Identification Scheme

B5.1 Introduction to the CPUID scheme

B5.1.1 Organization of the CPUID registers

B5.1.2 General features of the CPUID registers

B5.2 The CPUID registers

B5.2.1 CP15 c0, Processor Feature registers

c0, Processor Feature Register 0 (ID_PFR0)

c0, Processor Feature Register 1 (ID_PFR1)

Accessing the Processor Feature registers

B5.2.2 c0, Debug Feature Register 0 (ID_DFR0)

Accessing the ID_DFR0

B5.2.3 c0, Auxiliary Feature Register 0 (ID_AFR0)

Accessing the ID_AFR0

B5.2.4 CP15 c0, Memory Model Feature registers

c0, Memory Model Feature Register 0 (ID_MMFR0)

c0, Memory Model Feature Register 1 (ID_MMFR1)

c0, Memory Model Feature Register 2 (ID_MMFR2)

c0, Memory Model Feature Register 3 (ID_MMFR3)

Accessing the Memory Model Feature registers

B5.2.5 CP15 c0, Instruction Set Attribute registers

Instruction set descriptions in the CPUID scheme

Summary of Instruction Set Attribute register attributes

c0, Instruction Set Attribute Register 0 (ID_ISAR0)

c0, Instruction Set Attribute Register 1 (ID_ISAR1)

c0, Instruction Set Attribute Register 2 (ID_ISAR2)

c0, Instruction Set Attribute Register 3 (ID_ISAR3)

c0, Instruction Set Attribute Register 4 (ID_ISAR4)

c0, Instruction Set Attribute Register 5 (ID_ISAR5)

Accessing the Instruction Set Attribute registers

B5.3 Advanced SIMD and VFP feature identification registers

B5.3.1 Floating-point System ID Register (FPSID)

B5.3.2 Media and VFP Feature registers

Media and VFP Feature Register 0 (MVFR0)

Media and VFP Feature Register 1 (MVFR1)

B5.3.3 Accessing the Advanced SIMD and VFP feature identification registers

System Instructions

B6.1 Alphabetical list of instructions

B6.1.1 CPS

Assembler syntax

Operation

Exceptions

Hint instructions

B6.1.2 LDM (exception return)

Assembler syntax

Operation

Exceptions

B6.1.3 LDM (user registers)

Assembler syntax

Operation

Exceptions

B6.1.4 LDRBT, LDRHT, LDRSBT, LDRSHT, and LDRT

B6.1.5 MRS

Assembler syntax

Operation

Exceptions

B6.1.6 MSR (immediate)

Assembler syntax

Operation

Exceptions

E bit

B6.1.7 MSR (register)

Assembler syntax

Operation

Exceptions

E bit

B6.1.8 RFE

Assembler syntax

Operation

Exceptions

B6.1.9 SMC (previously SMI)

Assembler syntax

Operation

Exceptions

B6.1.10 SRS

Assembler syntax

Operation

Exceptions

B6.1.11 STM (user registers)

Assembler syntax

Operation

Exceptions

B6.1.12 STRBT, STRHT, and STRT

B6.1.13 SUBS PC, LR and related instructions

Assembler syntax

Operation

Exceptions

B6.1.14 VMRS

Assembler syntax

Operation

Exceptions

B6.1.15 VMSR

Assembler syntax

Operation

Exceptions

Debug Architecture

Introduction to the ARM Debug Architecture

C1.1 Scope of part C of this manual

C1.2 About the ARM Debug architecture

C1.2.1 Invasive debug

Description of invasive debug features

C1.2.2 Non-invasive debug

Trace

Sample-based profiling

Performance monitors

C1.2.3 Major differences between the ARMv6 and ARMv7 Debug architectures

C1.2.4 Summary of the ARM debug component descriptions

C1.3 Security Extensions and debug

C1.4 Register interfaces

Invasive Debug Authentication

C2.1 About invasive debug authentication

Debug Events

C3.1 About debug events

C3.2 Software debug events

C3.2.1 Breakpoint debug events

Generation of Breakpoint debug events

Debug event generation conditions defined by the DBGBCR

IVA comparisons for Debug event generation

IVA comparisons and instruction length

Context ID comparisons for Debug event generation

Additional considerations for IVA mismatch breakpoints

Additional conditions for linked BRPs

C3.2.2 Watchpoint debug events

Synchronous and Asynchronous Watchpoint debug events

C3.2.3 BKPT Instruction debug events

C3.2.4 Vector Catch debug events

Vector catch debug events and vectored interrupt support

C3.2.5 Memory addresses

C3.2.6 Unpredictable behavior on Software debug events

Debug exceptions in abort handlers

Debug events in the debug monitor

Monitor debug-mode vector catch on Secure Monitor Call

Possible effect of the Security Extensions on FIQ vector catch

C3.2.7 Pseudocode details of Software debug events

Debug events

Breakpoints and Vector Catches

Watchpoints

C3.3 Halting debug events

C3.4 Generation of debug events

C3.5 Debug event prioritization

Debug Exceptions

C4.1 About debug exceptions

C4.1.1 Debug exception on Breakpoint, BKPT Instruction or Vector Catch debug events

C4.1.2 Debug exception on Watchpoint debug event

C4.2 Effects of debug exceptions on CP15 registers and the DBGWFAR

Debug State

C5.1 About Debug state

C5.2 Entering Debug state

C5.2.1 Effect of entering Debug state on CP15 registers and the DBGWFAR

C5.2.2 Asynchronous aborts and entry to Debug state

Behavior in ARMv7

Behavior in ARMv6

C5.3 Behavior of the PC and CPSR in Debug state

C5.4 Executing instructions in Debug state

C5.4.1 Writing to the CPSR in Debug state

MRS and MSR instructions in Debug state, in v6.1 Debug and v7 Debug

C5.4.2 Data-processing instructions with the PC as the target in Debug state

C5.5 Privilege in Debug state

C5.5.1 Accessing registers and memory in Debug state

C5.5.2 Altering CPSR privileged bits in Debug state

Being in Debug state when invasive halting debug is not permitted

C5.5.3 Changing the SCR.NS bit in Debug state

C5.5.4 Coprocessor and Advanced SIMD instructions in Debug state

Instructions for CP0 to CP13, and Advanced SIMD instructions

Instructions for CP14 and CP15

C5.6 Behavior of non-invasive debug in Debug state

C5.7 Exceptions in Debug state

C5.7.1 Undefined Instruction and Data Abort exceptions in Debug state in v6 Debug

C5.8 Memory system behavior in Debug state

C5.8.1 Access to specific cache management functions in Debug state

v7 Debug restrictions on instruction cache invalidation in Secure User debug

C5.8.2 Debug state Cache and MMU Control Registers

C5.9 Leaving Debug state

Debug Register Interfaces

C6.1 About the debug register interfaces

C6.1.1 Processor interface to the debug registers

C6.1.2 External interface to the debug registers

C6.1.3 The Debug Communications Channel (DCC)

C6.2 Reset and power-down support

C6.2.1 Debug guidelines for systems with energy management capability

C6.2.2 Power domains and debug