CAN FD Controller Module

1.0 Introduction

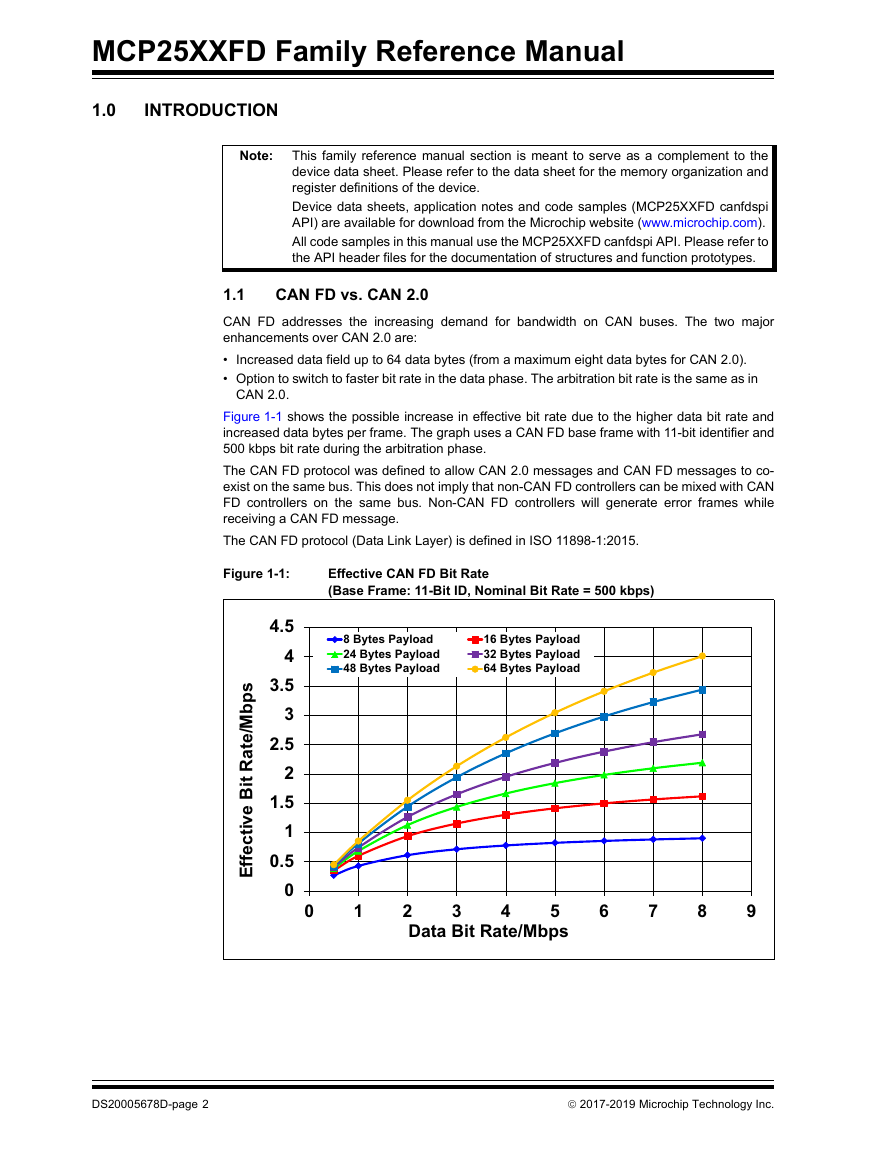

1.1 CAN FD vs. CAN 2.0

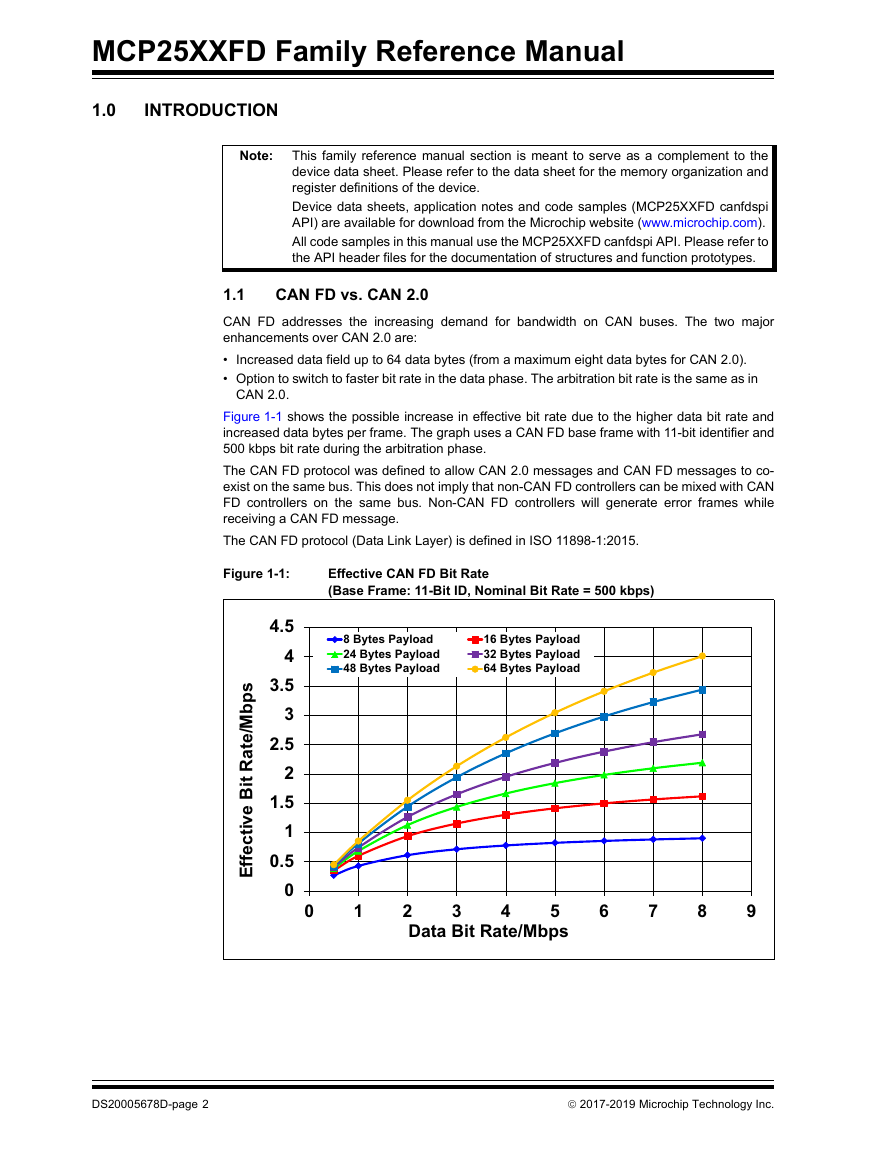

Figure 1-1: Effective CAN FD Bit Rate (Base Frame: 11-Bit ID, Nominal Bit Rate = 500 kbps)

1.2 Features

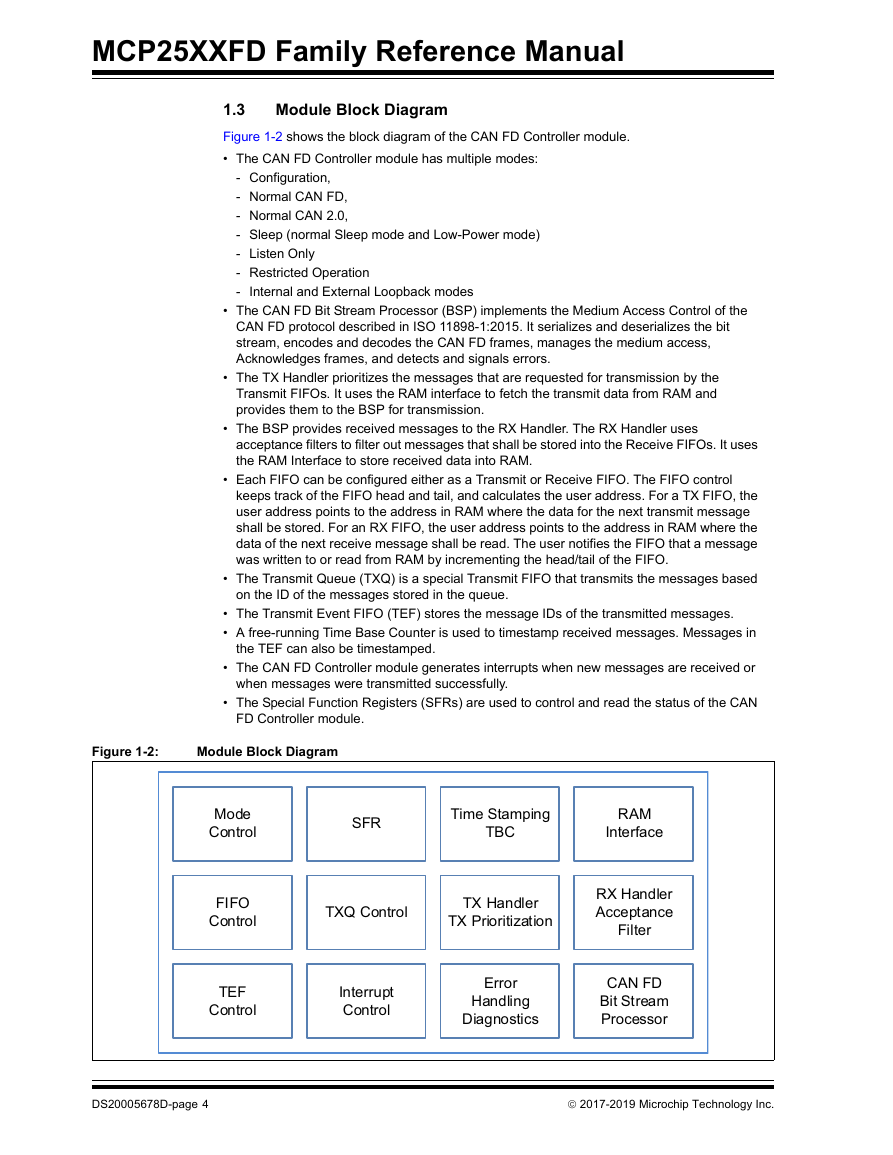

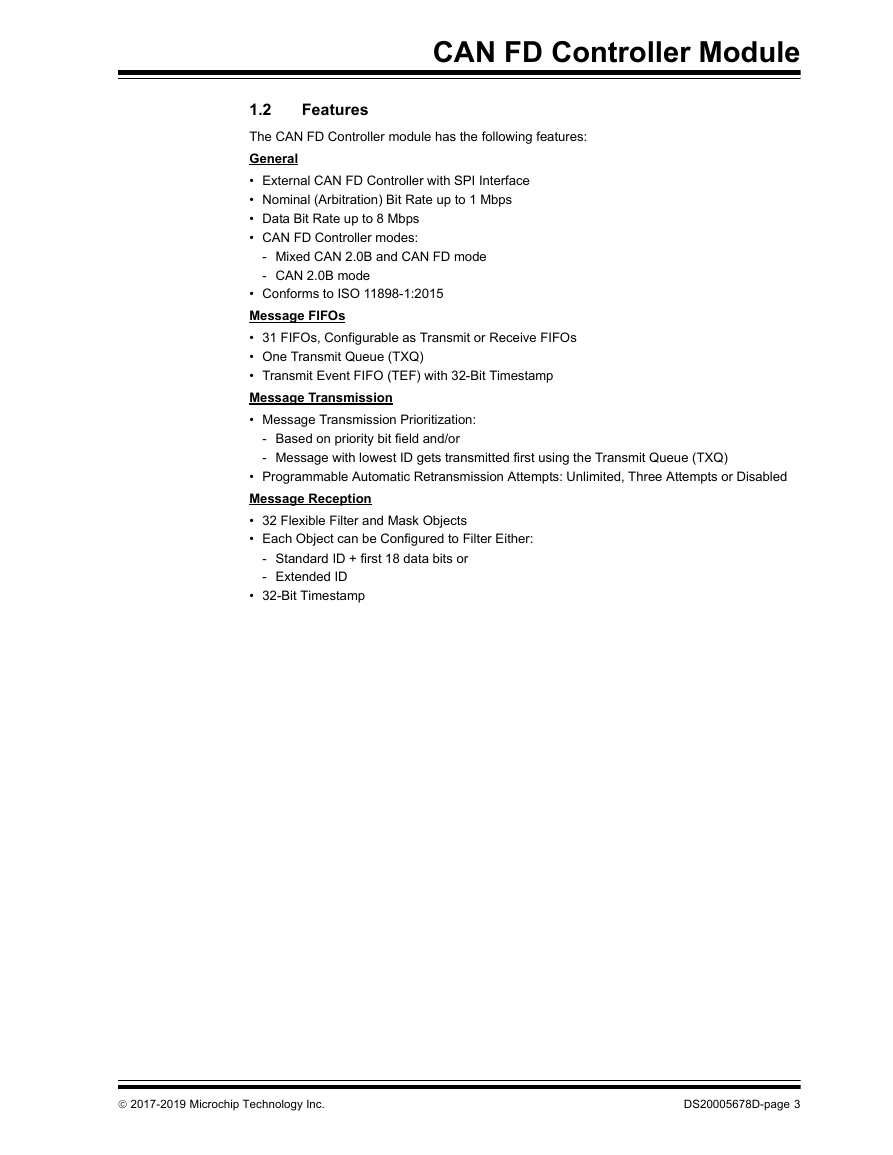

1.3 Module Block Diagram

Figure 1-2: Module Block Diagram

1.4 CAN FD Message Frames

1.4.1 ISO vs. Non-ISO CRC

Figure 1-3: General Data Frame

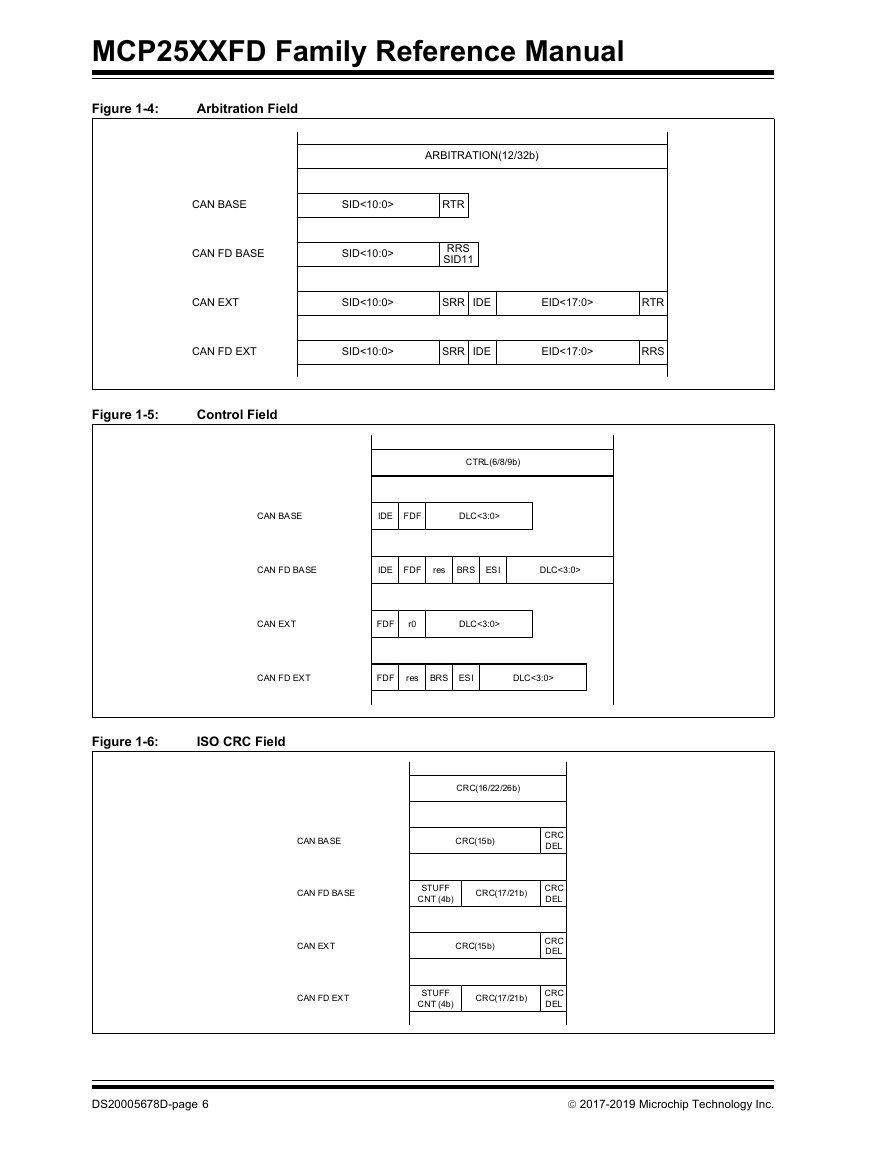

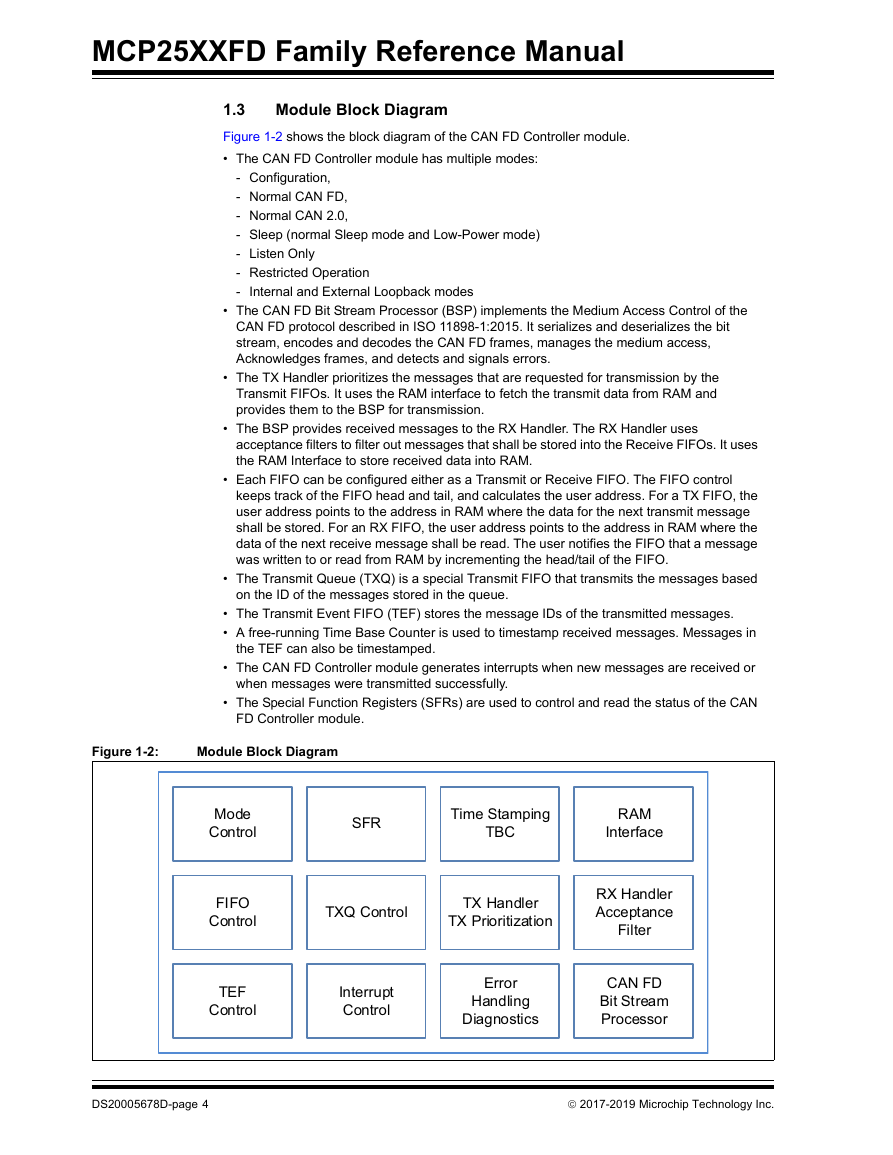

Figure 1-4: Arbitration Field

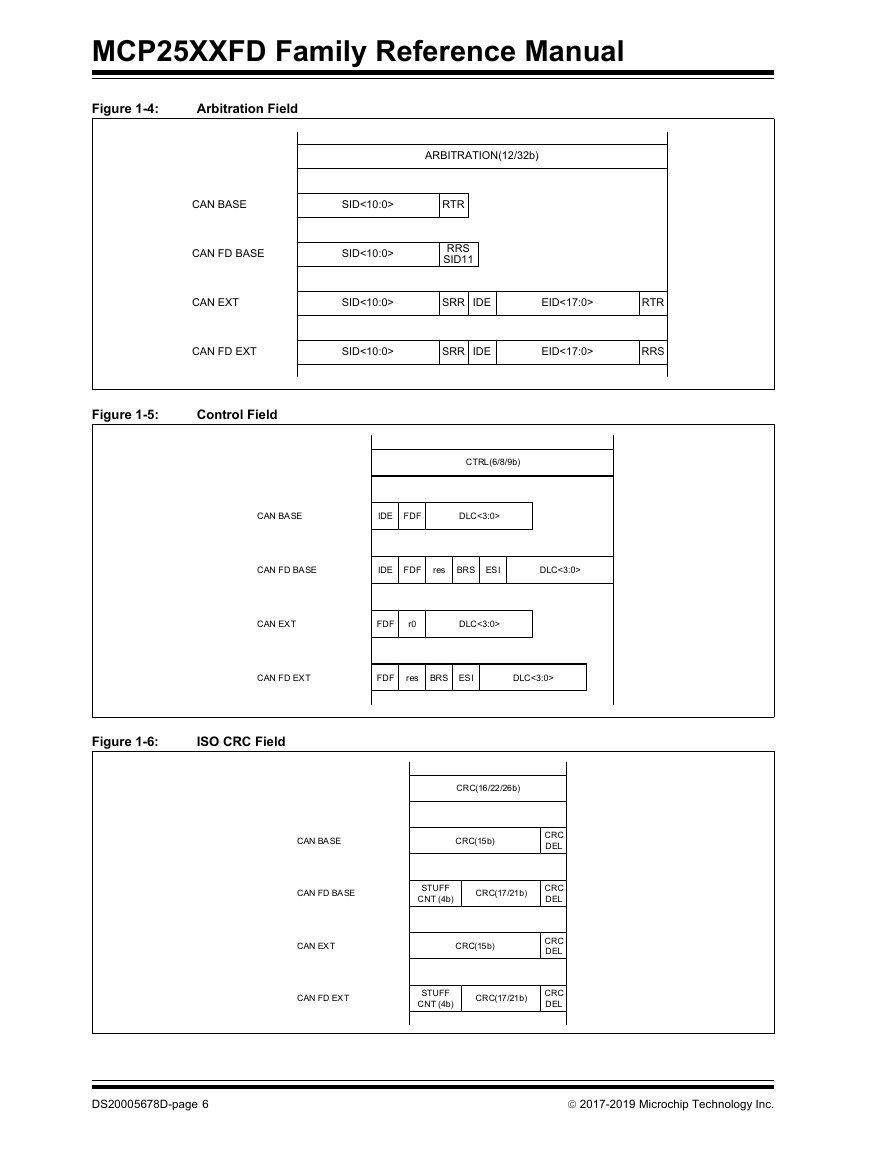

Figure 1-5: Control Field

Figure 1-6: ISO CRC Field

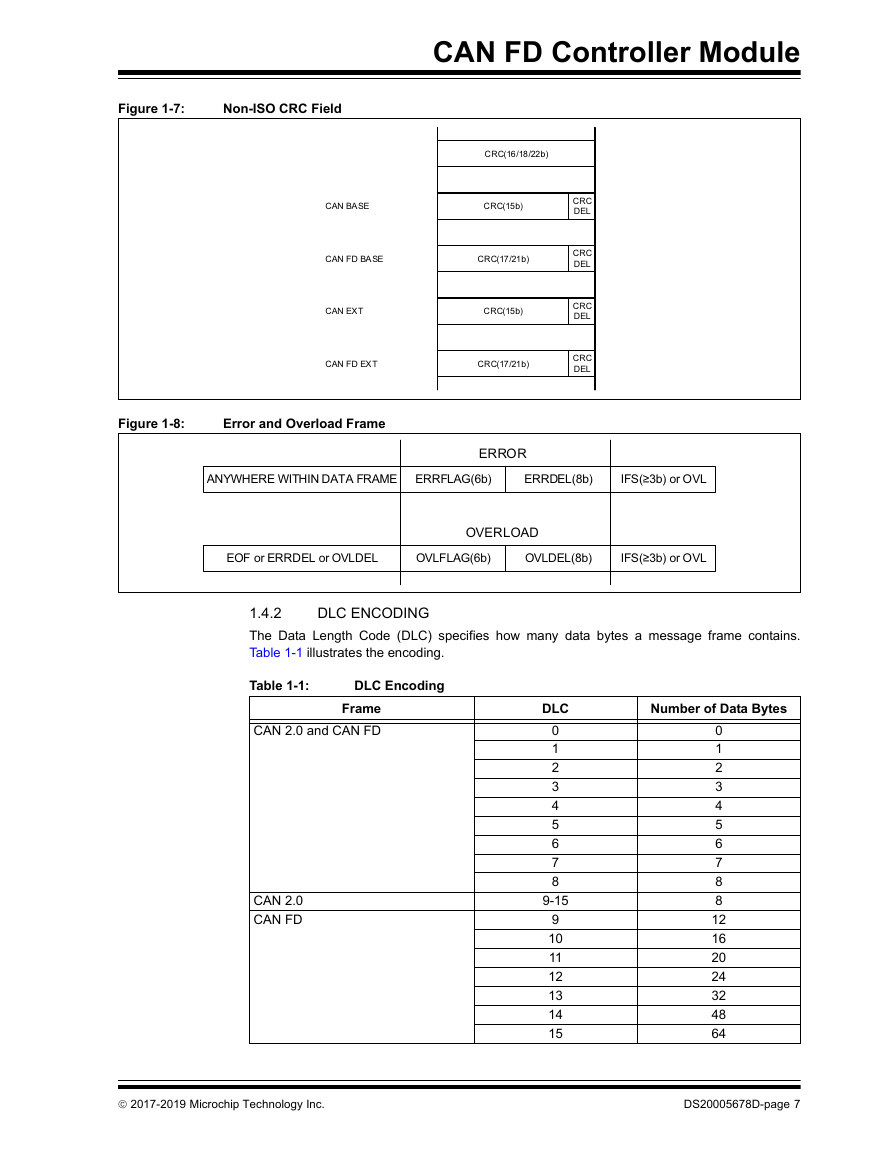

Figure 1-7: Non-ISO CRC Field

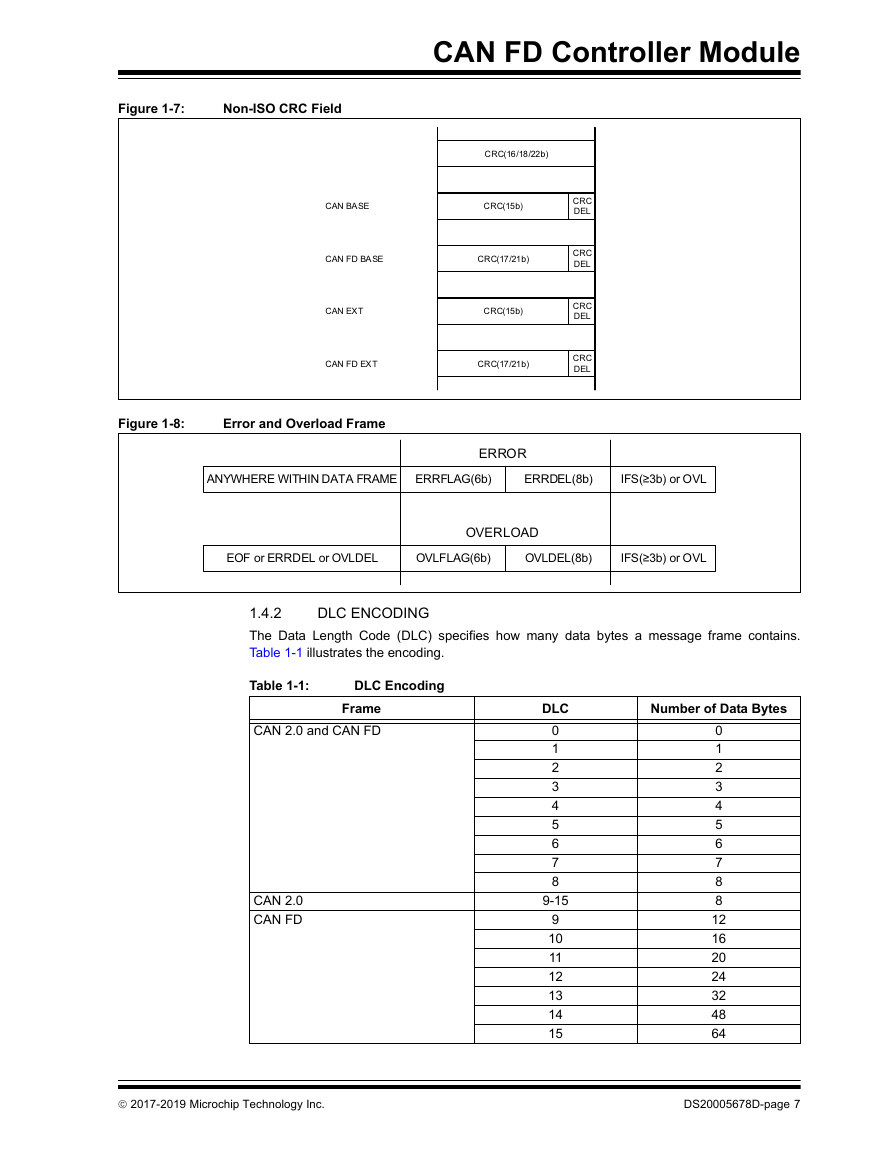

Figure 1-8: Error and Overload Frame

1.4.2 DLC Encoding

Table 1-1: DLC Encoding

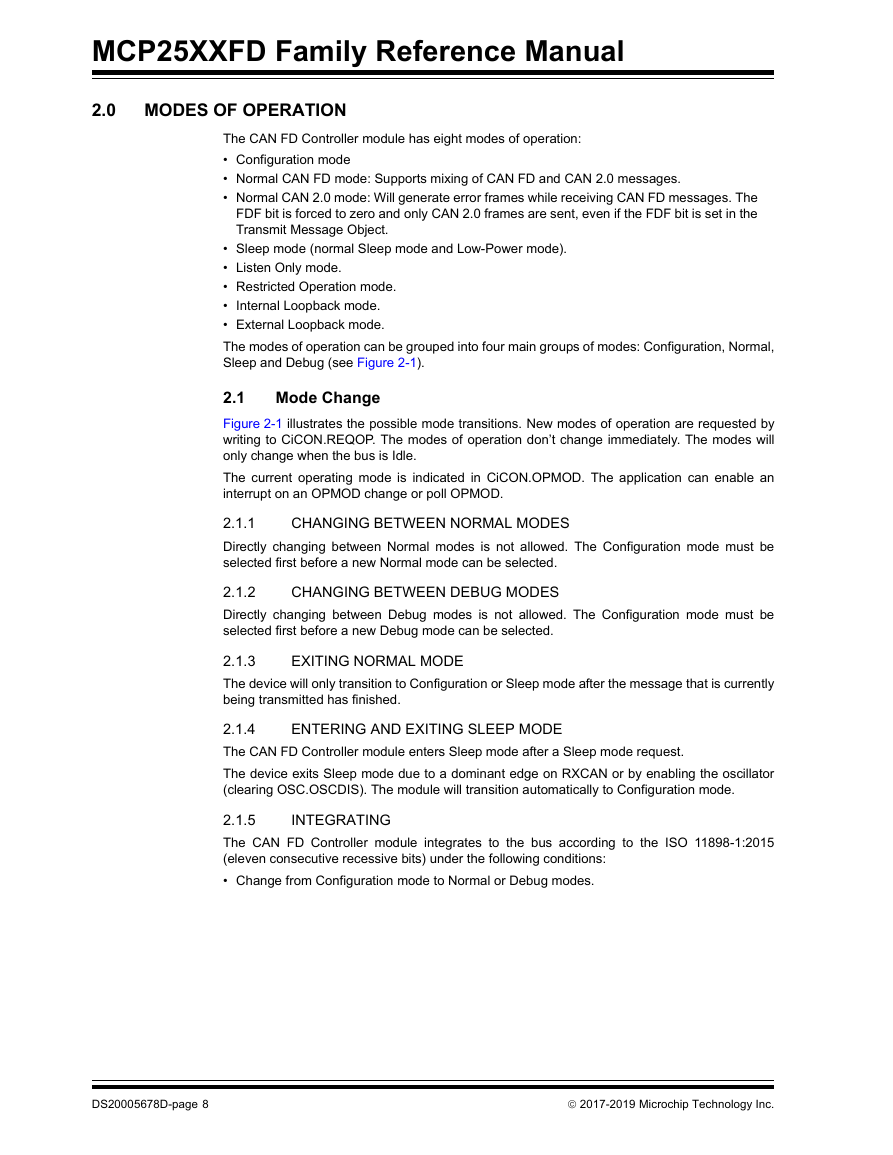

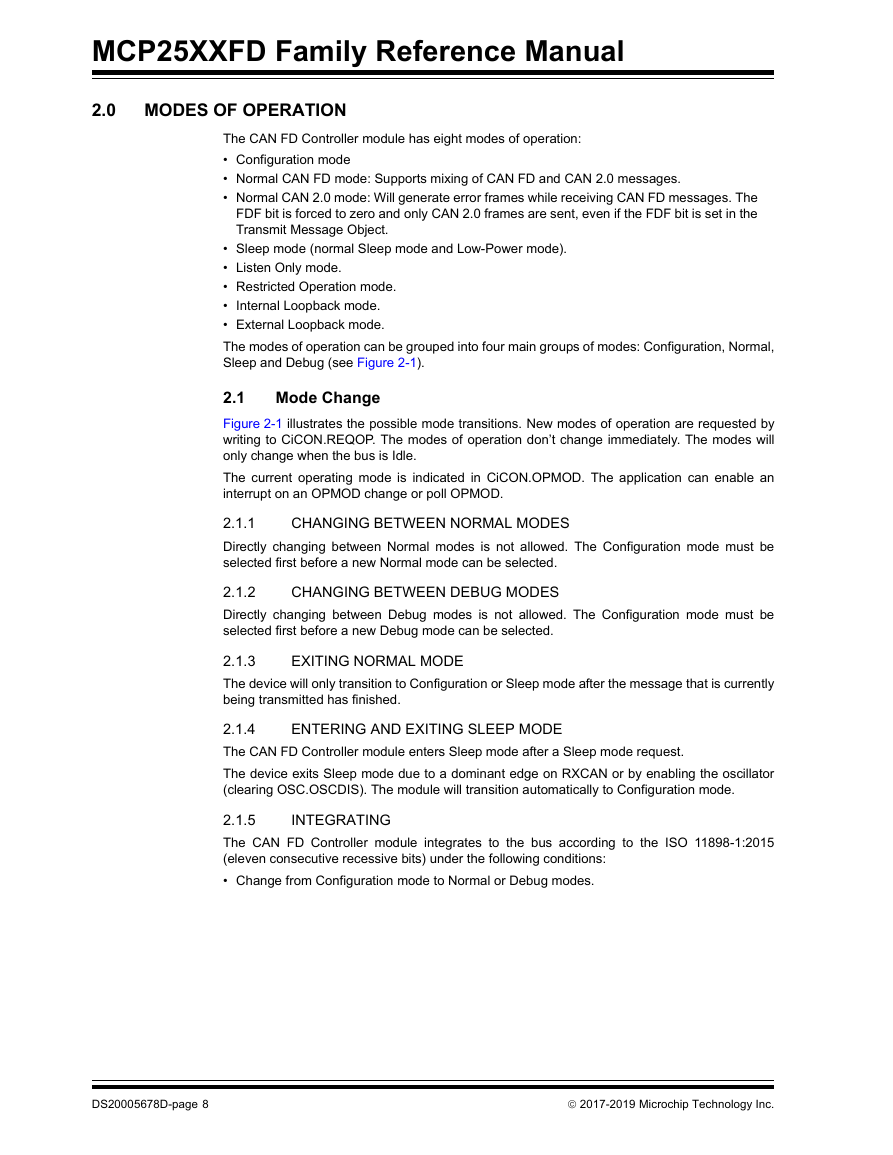

2.0 Modes of Operation

2.1 Mode Change

2.1.1 Changing Between Normal Modes

2.1.2 Changing Between Debug Modes

2.1.3 Exiting Normal Mode

2.1.4 Entering and Exiting Sleep Mode

2.1.5 Integrating

Figure 2-1: Modes of Operation

2.2 Configuration Mode

2.3 Normal Modes

2.3.1 Normal CAN FD Mode

2.3.2 Normal CAN 2.0 Mode

2.4 Sleep Mode(1,2)

2.4.1 Exiting Sleep mode

2.5 Low-Power Mode (LPM)(1,2,3)

2.5.1 Exiting LPM

2.6 Debug Modes

2.6.1 Listen Only Mode

2.6.2 Restricted Operation Mode

2.6.3 Loopback Mode

3.0 Configuration

3.1 Oscillator Configuration

3.1.1 Crystal/Resonator Selection

Figure 3-1: MCP251XFD Oscillator Block Diagram

3.2 Input/Output Pin Configuration

3.3 CAN Configuration

3.3.1 ISO CRC Enable

3.3.2 Protocol Exception Disable

3.3.3 Wake-up Filter

3.3.4 Restriction of Transmission Attempts

3.3.5 Error State Indicator (ESI) in Gateway Mode

3.3.6 Mode Selection in Case of System Error

3.3.7 Reserving Message Memory for TX Queue and Transmit Event FIFO

3.4 CAN FD Bit Time Configuration

Equation 3-1: Nominal Bit Rate/Time

Equation 3-2: Data Bit Rate/Time

Equation 3-3: Nominal Time Quanta

Equation 3-4: Data Time Quanta

Figure 3-2: Partition of Bit Time

Equation 3-5: Number of NTQ in a NBT

Equation 3-6: Number of DTQ in a DBT

Table 3-1: Nominal Bit Rate Configuration Ranges

Table 3-2: Data Bit Rate Configuration Ranges

3.4.1 Sample Point

Equation 3-7: Nominal Sample Point (%)

Equation 3-8: Data Sample Point (%)

3.4.2 Propagation Delay

Equation 3-9: Maximum Propagation Delay

Figure 3-3: Propagation Delay

3.4.3 Transmitter Delay Compensation (TDC)

Equation 3-10: Secondary Sample Point

Figure 3-4: Measurement of Transceiver Delay (TDCV)

3.4.4 Synchronization

3.4.5 Synchronization Jump Width

3.4.6 Oscillator Tolerance

Equation 3-11: Oscillator Tolerance

Equation 3-12: Condition 1

Equation 3-13: Condition 2

Equation 3-14: Condition 3

Equation 3-15: Condition 4

Equation 3-16: Condition 5

3.4.7 Recommendations for Bit Time Configuration

3.4.8 Bit Time Configuration Example

Table 3-3: Step-by-Step Nominal Bit Rate Configuration

Table 3-4: Step-by-Step Data Bit Rate Configuration

Table 3-5: Bit Time Register Initialization (500k/2M)

3.5 Message Memory Configuration

Figure 3-5: Message Memory Organization

3.5.1 Transmit Event FIFO Configuration

3.5.2 Transmit Queue Configuration

3.5.3 Transmit FIFO Configuration

3.5.4 Receive FIFO Configuration

3.5.5 Calculation of Required Message Memory

Equation 3-17: Size of TEF

Equation 3-18: Size of TXQ

Equation 3-19: Size of FIFOs

Equation 3-20: Total RAM Usage

3.6 Configuration Code Example

Example 3-1: Basic Configuration

Example 3-2: Initialize RAM, Select Normal Mode

4.0 Message Transmission

4.1 Transmit Message Object

4.2 Loading Messages into a Transmit FIFO

Equation 4-1: Address of Next Message Object

4.3 Loading Messages Into the Transmit Queue

TABLE 4-1: Transmit message object (TXQ AND TX FIFO)

4.4 Requesting Transmission of a Message in a Transmit FIFO

4.5 Requesting Transmission of a Message in the Transmit Queue

4.6 CiTXREQ Register

4.7 Transmit Priority

4.7.1 Transmit Priority of Messages Inside a FIFO

4.7.2 Transmit Priority of Messages Inside the TXQ

4.7.3 Transmit Priority Based on ID

4.8 Transmit Bandwidth Sharing

4.9 Retransmission Attempts

4.9.1 Retransmission Attempts Disabled

4.9.2 Three Retransmission Attempts

4.9.3 Unlimited Retransmissions

4.10 Aborting a Transmission

4.11 Remote Transmit Request

4.12 Mismatch of DLC and Payload Size During Transmission

4.13 Transmit State Diagram

Figure 4-1: Transmit State Diagram

4.14 Resetting a Transmit FIFO

4.15 Resetting the Transmit Queue (TXQ)

4.16 Message Transmission Code Example

Example 4-1: Transmit Message from TX FIFO

5.0 Transmit Event FIFO

5.1 Reading a TEF Object

Equation 5-1: Address of Next TEF Object

5.2 Resetting the Transmit Event FIFO (TEF)

TABLE 5-1: Transmit Event FIFO Object

5.3 TEF Code Example

Example 5-1: Reading a Message from the TEF

6.0 Message Filtering

6.1 Filter Configuration

6.2 Filtering a Received Message

Figure 6-1: Message Filtering Flow

6.2.1 Filtering Standard or Extended Frames

6.2.2 Mask Bits

Figure 6-2: Filter Match

6.2.3 Filtering on Data Bytes

6.2.4 12-Bit Standard ID

Table 6-1: Data Byte Filter Configuration

Figure 6-3: CAN Operation with DeviceNet™ Filtering

6.3 Filter Configuration Code Example

Example 6-1: Filter Configuration to Match a Standard Frame Range

7.0 Message Reception

7.1 Receive Message Object

7.1.1 Reading a Receive Message Object

Equation 7-1: Address of next Message Object

TABLE 7-1: Receive message object

7.2 Receive State Diagram

Figure 7-1: Receive State Diagram

7.3 Resetting an RX FIFO

7.4 Mismatch of DLC and Payload Size During Reception

7.5 Message Reception Code Example

Example 7-1: Receiving a Message

8.0 FIFO Behavior

Table 8-1: Example FIFO Configuration

8.1 FIFO Status Flags

8.1.1 TX FIFO Status Flags

8.1.2 RX FIFO Status Flags

8.1.3 TXQ Status Flags

8.1.4 TEF Status Flags

8.2 Transmit FIFO Behavior

Figure 8-1: FIFO 1 – Initial State

Figure 8-2: FIFO 1 – First Message Loaded

Figure 8-3: FIFO 1 – First Message Transmitted

Figure 8-4: FIFO 1 – Three More Messages Loaded

Figure 8-5: FIFO 1 – FIFO Fully Loaded

Figure 8-6: FIFO 1 – FIFO Fully Transmitted

8.3 Receive FIFO Behavior

Figure 8-7: FIFO 2 – Initial State

Figure 8-8: FIFO 2 – First Message Received

Figure 8-9: FIFO 2 – First Message Read

Figure 8-10: FIFO 2 – Half Full

Figure 8-11: FIFO 2 – FIFO Almost Full

Figure 8-12: FIFO 2 – FIFO Full

Figure 8-13: FIFO 2 – FIFO Overflow

Figure 8-14: FIFO 2 – Two More Messages Read

8.4 Transmit Queue Behavior

Figure 8-15: TXQ – Initial State

Figure 8-16: TXQ – First Message Loaded

Figure 8-17: TXQ – First Message Transmitted

Figure 8-18: TXQ – Next Message Loaded

Figure 8-19: TXQ – Next Six Messages Loaded

Figure 8-20: TXQ – Full

8.5 Transmit Event FIFO Behavior

Figure 8-21: TEF – Initial State

Figure 8-22: TEF – First Transmit Message was Stored

Figure 8-23: TEF – First ID Read

Figure 8-24: TEF – Half Full

Figure 8-25: TEF – Almost Full

Figure 8-26: TEF – Full

Figure 8-27: TEF – Overflow

Figure 8-28: TEF – One More ID Read

9.0 Timestamping

Table 9-1: Reference Point

9.1 TBC Configuration Code Example

Example 9-1: Configuration of TBC

10.0 Interrupts

Figure 10-1: Interrupt Multiplexing

10.1 FIFO Individual Interrupts

10.1.1 Transmit Queue (TXQ) Interrupts

10.1.2 Receive FIFO Interrupt – RFIF

10.1.3 Transmit FIFO Interrupt – TFIF

10.1.4 Receive FIFO Overrun Interrupt – RXOVIF

10.1.5 Transmit FIFO Attempt Interrupt – TXATIF

10.1.6 Transmit Event FIFO Interrupt – TEFIF

10.2 MCP25XXFD SPI CRC Interrupts

10.3 MCP25XXFD RAM ECC Interrupts

10.4 FIFO Combined Interrupts

10.5 Main Interrupts

10.5.1 Invalid Message Interrupt – IVMIF

10.5.2 Wake-up Interrupt – WAKIF

10.5.3 CAN Bus Error Interrupt – CERRIF

10.5.4 CAN Mode Change Interrupt – MODIF

10.5.5 CAN Time Base Counter Interrupt – TBCIF

10.5.6 System Error Interrupt – SERRIF

10.5.7 SPI CRC Interrupt – SPICRCIF

10.5.8 ECC Interrupt – ECCIF

10.6 Interrupt Handling

10.6.1 Interrupt Lookup Table

10.6.2 Interrupt Status Registers

10.7 Interrupt Flags

Table 10-1: Interrupt Flags

10.8 Interrupt Configuration and Handling Code Examples

Example 10-1: Configuration of Interrupts

Example 10-2: Using TX Interrupt Pin to Check if TXQ is Ready for Transmission

Example 10-3: Using RX Interrupt Pin to Check if FIFO 2 Contains a New Message

11.0 Error Handling

Figure 11-1: Error States

11.1 Recovery from Bus Off State

12.0 Appendix A: MCP25XXFD CAN FD SPI API

12.1 Introduction

12.2 Abstraction Model

Figure 12-1: Hardware Abstraction Model

12.3 Getting Started with the SPI Communication

12.3.1 SPI Initialization Code Example

Example 12-1: SPI Initialization Function

12.3.2 SPI Data Transfer Code Example

Example 12-2: SPI Data Transfer Function

12.3.3 SPI Read and Write Access Functions

Example 12-3: SPI Access Functions

12.3.4 Verification of the SPI Communication

Example 12-4: Verifying SPI Communication Using RAM Access

Example 12-5: Verifying SPI Communication Using Register Access

13.0 Related Documents

14.0 Revision History

Revision D (May 2019)

Revision C (April 2019)

Revision B (May 2018)

Revision A (September 2017)

Worldwide Sales and Service

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc