RDA5981C IEEE 802.11b/g/n MCU WIFI Rev1.1

PRELIMINARY

DATA SHEET

Revision: 1.1

Release date: 10 Feb 2017

RDA5981C

IEEE802.11b/g/n MCU WIFI

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced,

or disclosed in whole or in part without prior written permission of RDA. Page 1 of 16

�

RDA5981C IEEE 802.11b/g/n MCU WIFI Rev1.1

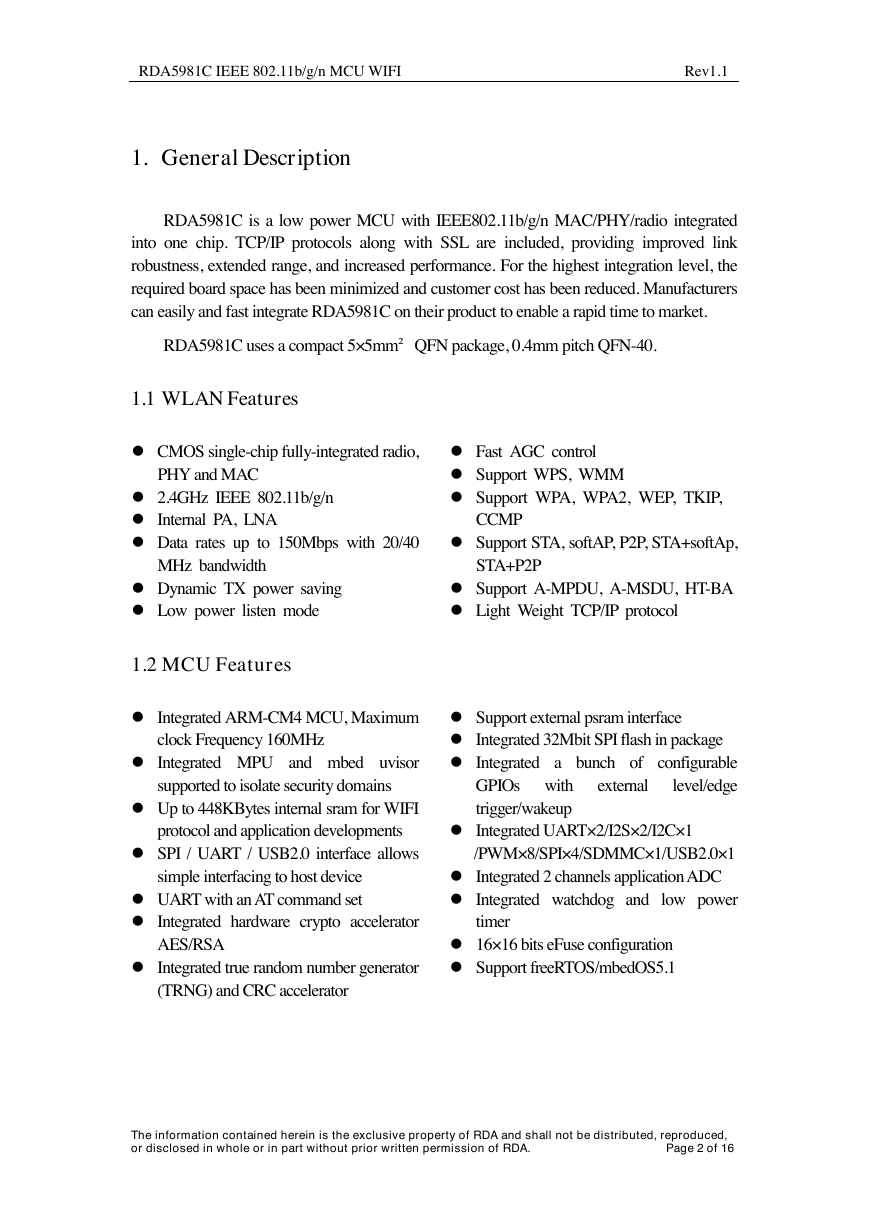

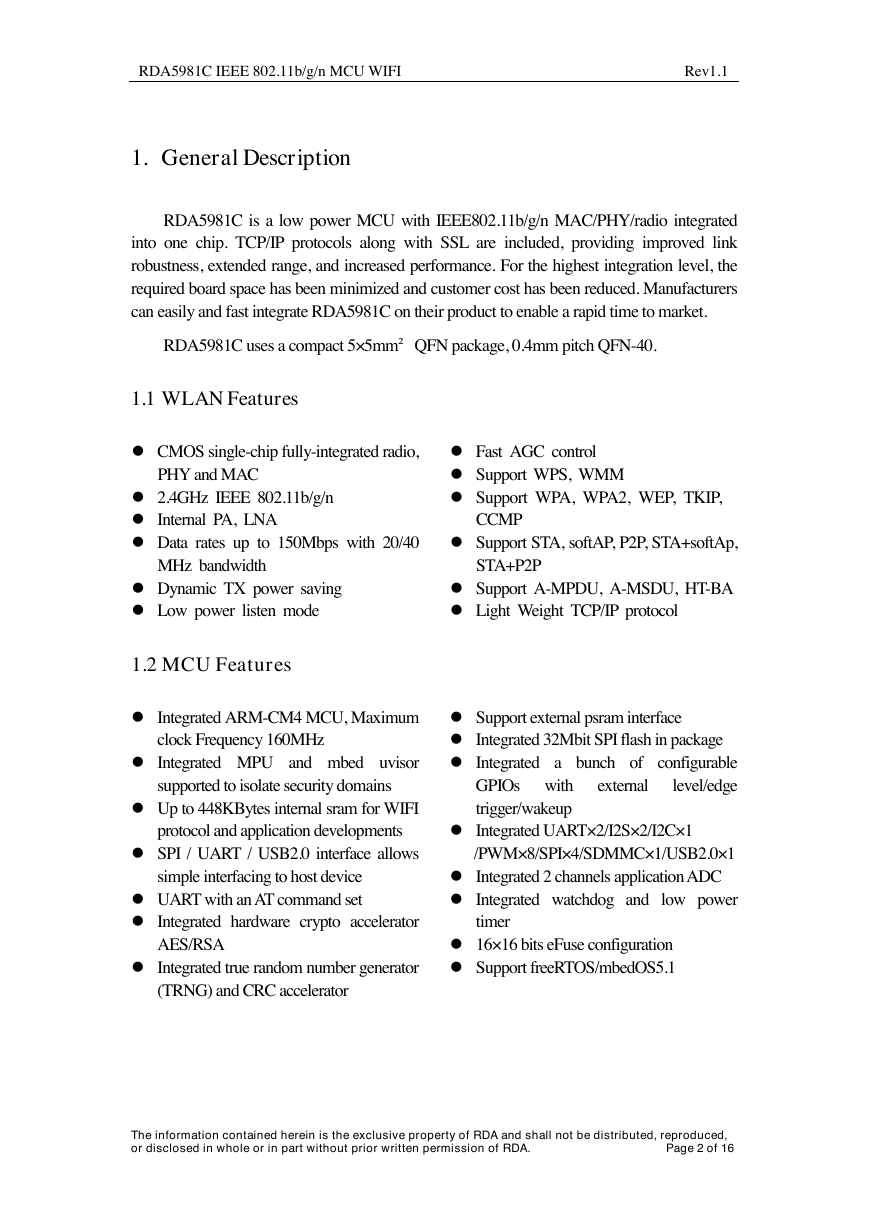

1. General Description

RDA5981C is a low power MCU with IEEE802.11b/g/n MAC/PHY/radio integrated

into one chip. TCP/IP protocols along with SSL are included, providing improved link

robustness, extended range, and increased performance. For the highest integration level, the

required board space has been minimized and customer cost has been reduced. Manufacturers

can easily and fast integrate RDA5981C on their product to enable a rapid time to market.

RDA5981C uses a compact 5×5mm² QFN package, 0.4mm pitch QFN-40.

1.1 WLAN Features

CMOS single-chip fully-integrated radio,

PHY and MAC

2.4GHz IEEE 802.11b/g/n

Internal PA, LNA

Data rates up to 150Mbps with 20/40

MHz bandwidth

Dynamic TX power saving

Low power listen mode

Fast AGC control

Support WPS, WMM

Support WPA, WPA2, WEP, TKIP,

CCMP

Support STA, softAP, P2P, STA+softAp,

STA+P2P

Support A-MPDU, A-MSDU, HT-BA

Light Weight TCP/IP protocol

1.2 MCU Features

Integrated ARM-CM4 MCU, Maximum

clock Frequency 160MHz

Integrated MPU and mbed uvisor

supported to isolate security domains

Up to 448KBytes internal sram for WIFI

Support external psram interface

Integrated 32Mbit SPI flash in package

Integrated a bunch of configurable

level/edge

external

GPIOs with

trigger/wakeup

protocol and application developments

Integrated UART×2/I2S×2/I2C×1

SPI / UART / USB2.0 interface allows

simple interfacing to host device

UART with an AT command set

Integrated hardware crypto accelerator

AES/RSA

Integrated true random number generator

(TRNG) and CRC accelerator

/PWM×8/SPI×4/SDMMC×1/USB2.0×1

Integrated 2 channels application ADC

Integrated watchdog and low power

timer

16×16 bits eFuse configuration

Support freeRTOS/mbedOS5.1

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced,

or disclosed in whole or in part without prior written permission of RDA. Page 2 of 16

�

RDA5981C IEEE 802.11b/g/n MCU WIFI Rev1.1

1.3 Applications

IOT devices

Smart home

Wi-Fi speaker/home audio

Smart watch

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced,

or disclosed in whole or in part without prior written permission of RDA. Page 3 of 16

�

RDA5981C IEEE 802.11b/g/n MCU WIFI Rev1.1

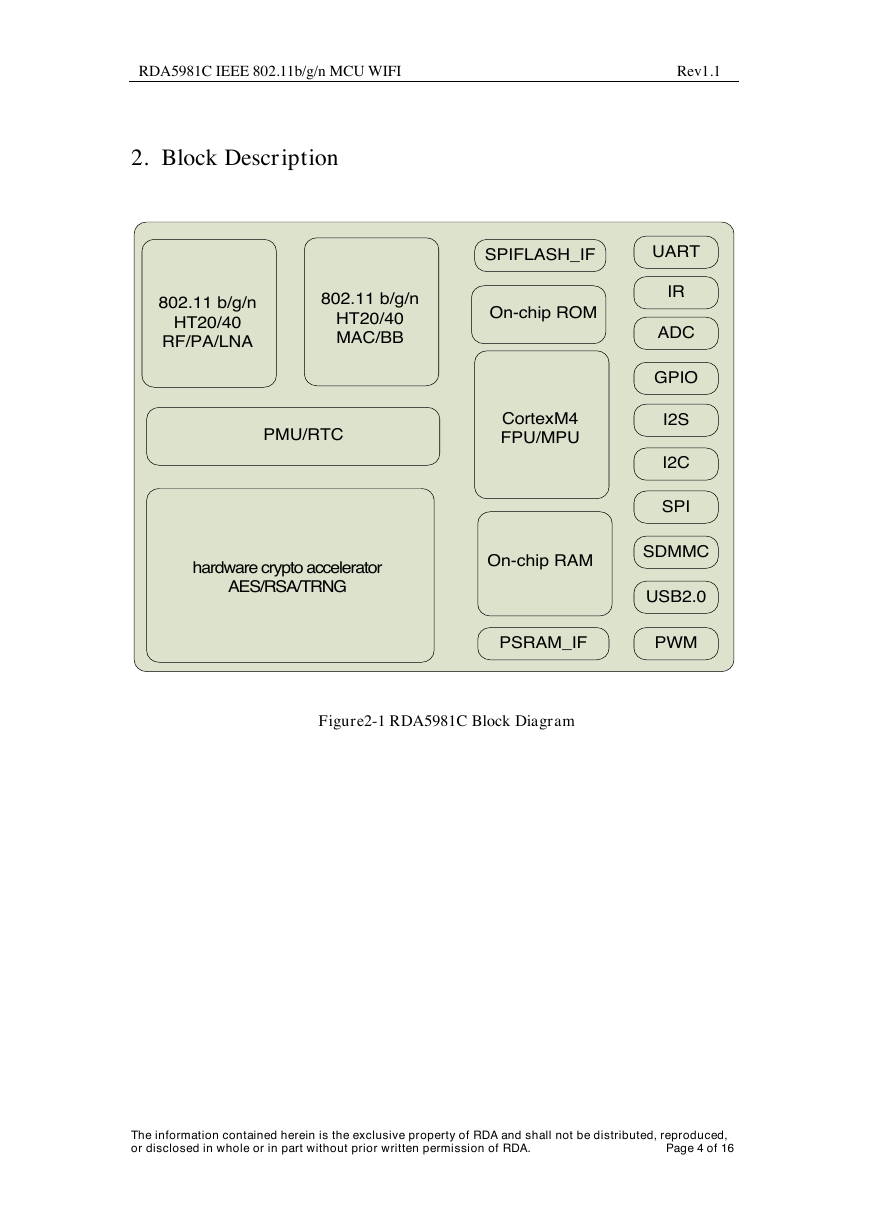

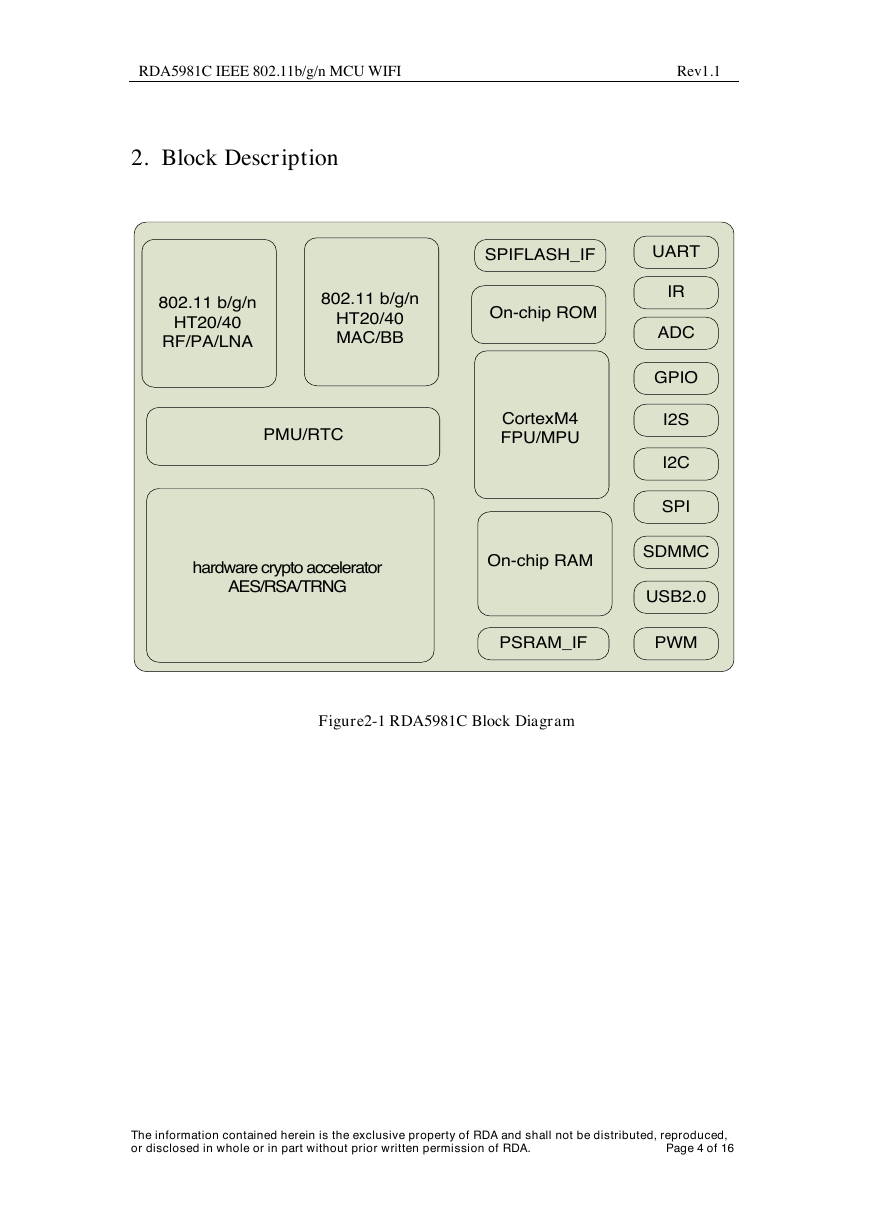

2. Block Description

Figure2-1 RDA5981C Block Diagram

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced,

or disclosed in whole or in part without prior written permission of RDA. Page 4 of 16

UARTCortexM4FPU/MPUOn-chip ROMOn-chip RAM802.11 b/g/nHT20/40MAC/BB802.11 b/g/nHT20/40RF/PA/LNAPMU/RTChardware crypto accelerator AES/RSA/TRNGIRADCGPIOI2SI2CSPISDMMCUSB2.0PWMPSRAM_IFSPIFLASH_IF�

RDA5981C IEEE 802.11b/g/n MCU WIFI Rev1.1

3. Functional Description

3.1 Memory System

RDA5981C integrates ROM, internal RAM and SPI nor flash to provide

applications with a variety of memory requirements.

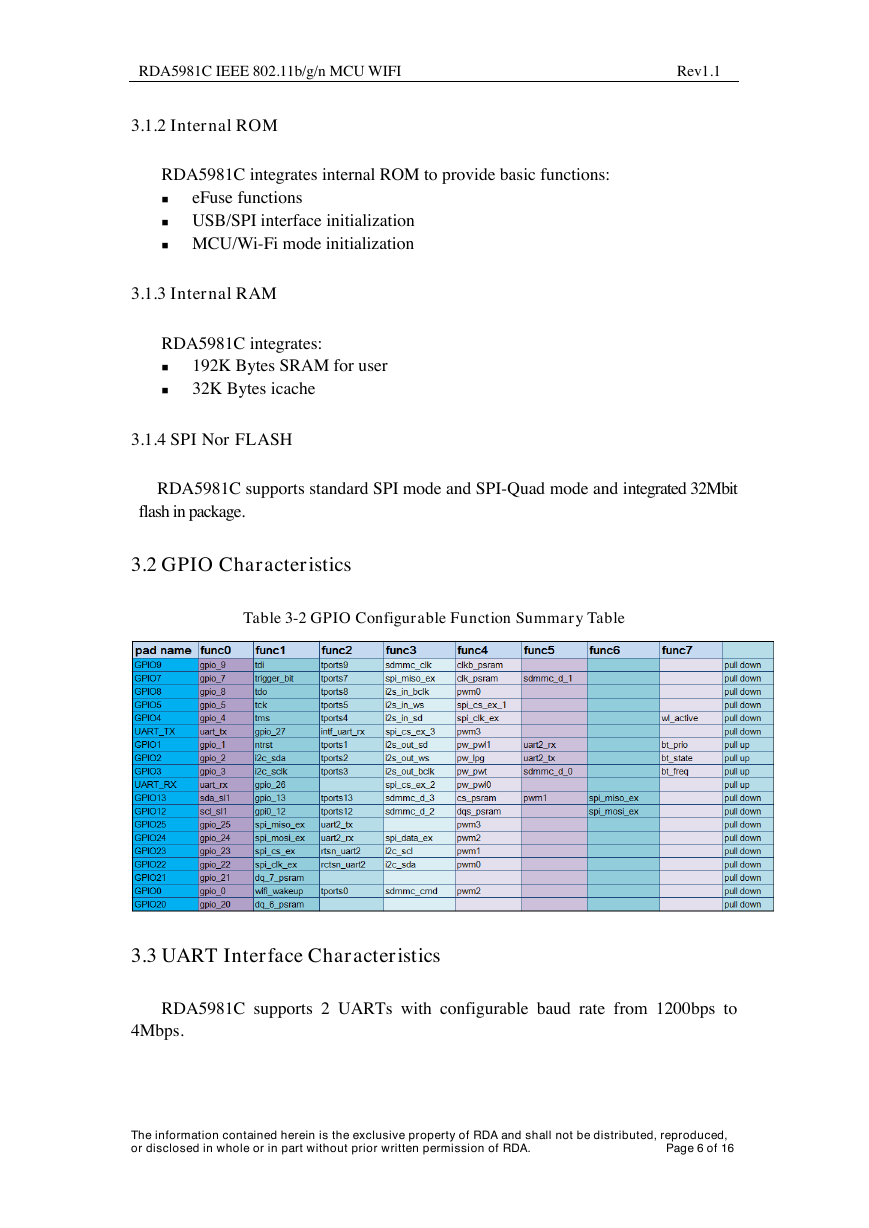

3.1.1 Memory Map

Table 3-1 RDA5981C Memory Map

Component

Address Range

Size

comments

MEMORY

BOOT_ROM 0x0000_0000-0x0000_FFFF

I_SRAM

0x0010_0000-0x0011_FFFF

D_SRAM

0x0018_0000-0x001A_7FFF

0x1000_0000-0x13FF_EFFF data

0x1400_0000 - 0x15FF_FFFF FLASH data

32M

0x1800_0000-0x1FFF_FFFF I-cache

PSRAM

FLASH

I-cache

LOGIC

SCU

GPIO

0x40000000-0x40000FFF

0x40001000-0x40001FFF

TIMER

0x40002000-0x40002FFF

I2C_master

0x40003000-0x40003FFF

PWM

0x40004000-0x40004FFF

PSRAM_CFG 0x40005000-0x40005FFF

SDMMC

0x40006000-0x40006FFF

I2C

0x40010000-0x40010FFF

UART1

0x40012000-0x40012FFF

AHB_EXIF

0x40013000-0x40013FFF

WIFI_PA

0x40020000-0x40021FFF

WIFI_CE

0x40022000-0x40022FFF

WLAN_MON 0x40024000-0x40027FFF

SDIO

USB

0x40030000-0x40030FFF

0x40031000-0x40031FFF

MEMC0

0x40100000-0x4017FFFF

UART2

0x40180000-0x40180FFF

DMA_CFG

0x40181000-0x40181FFF

64K

128K

160K

64M

4K

4K

4K

4K

4K

4K

4K

4K

4K

4K

8K

4K

20K

4K

4K

512k

4K

4K

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced,

or disclosed in whole or in part without prior written permission of RDA. Page 5 of 16

�

RDA5981C IEEE 802.11b/g/n MCU WIFI Rev1.1

3.1.2 Internal ROM

RDA5981C integrates internal ROM to provide basic functions:

eFuse functions

USB/SPI interface initialization

MCU/Wi-Fi mode initialization

3.1.3 Internal RAM

RDA5981C integrates:

192K Bytes SRAM for user

32K Bytes icache

3.1.4 SPI Nor FLASH

RDA5981C supports standard SPI mode and SPI-Quad mode and integrated 32Mbit

flash in package.

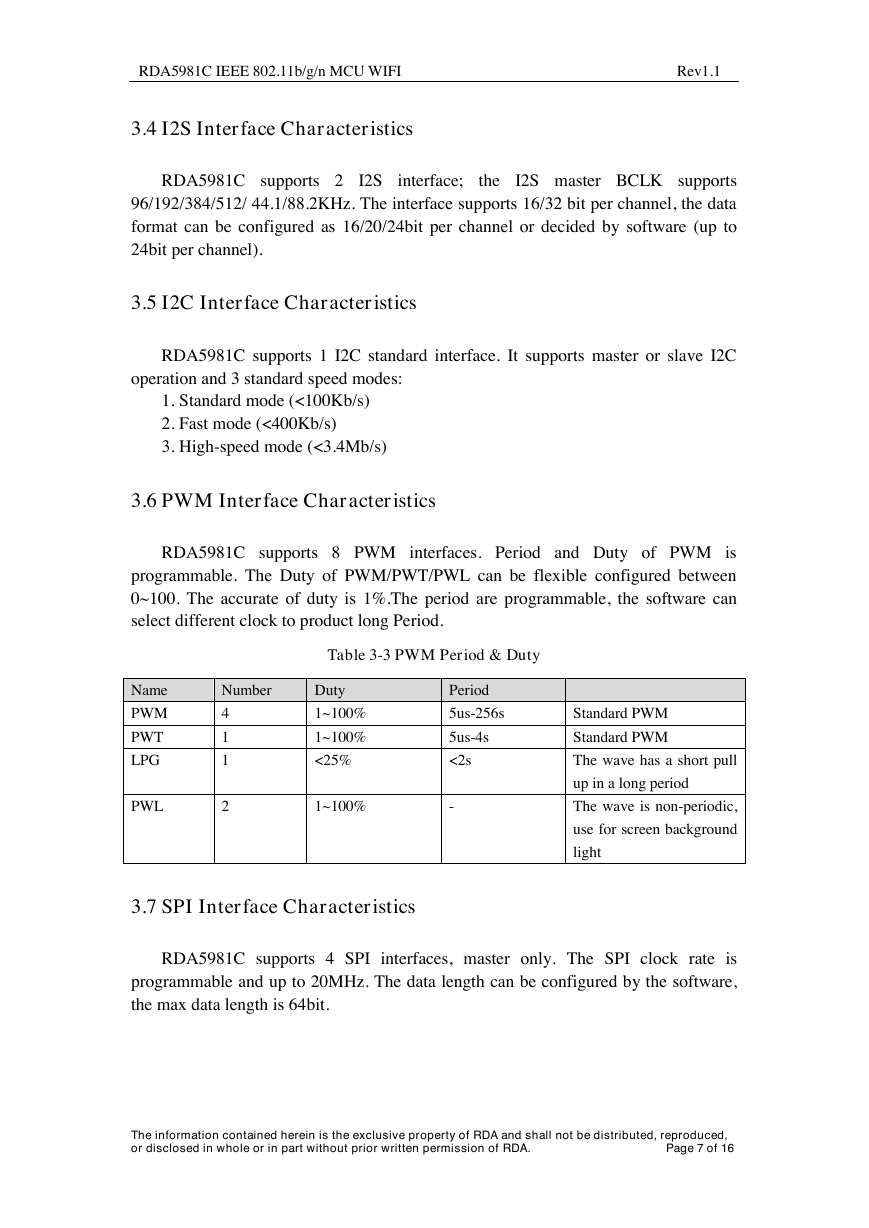

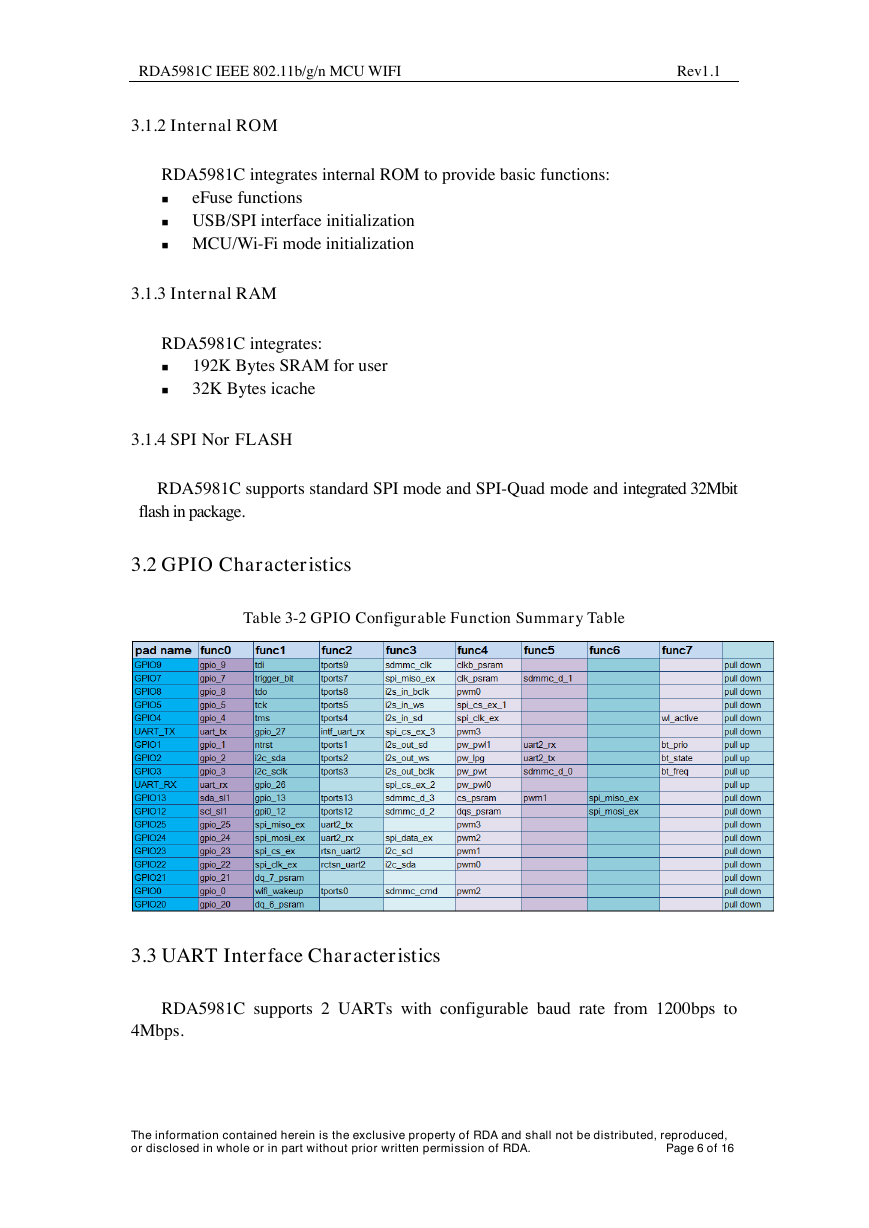

3.2 GPIO Characteristics

Table 3-2 GPIO Configurable Function Summary Table

3.3 UART Interface Characteristics

RDA5981C supports 2 UARTs with configurable baud rate from 1200bps to

4Mbps.

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced,

or disclosed in whole or in part without prior written permission of RDA. Page 6 of 16

�

RDA5981C IEEE 802.11b/g/n MCU WIFI Rev1.1

3.4 I2S Interface Characteristics

RDA5981C supports 2 I2S

the I2S master BCLK supports

96/192/384/512/ 44.1/88.2KHz. The interface supports 16/32 bit per channel, the data

format can be configured as 16/20/24bit per channel or decided by software (up to

24bit per channel).

interface;

3.5 I2C Interface Characteristics

RDA5981C supports 1 I2C standard interface. It supports master or slave I2C

operation and 3 standard speed modes:

1. Standard mode (<100Kb/s)

2. Fast mode (<400Kb/s)

3. High-speed mode (<3.4Mb/s)

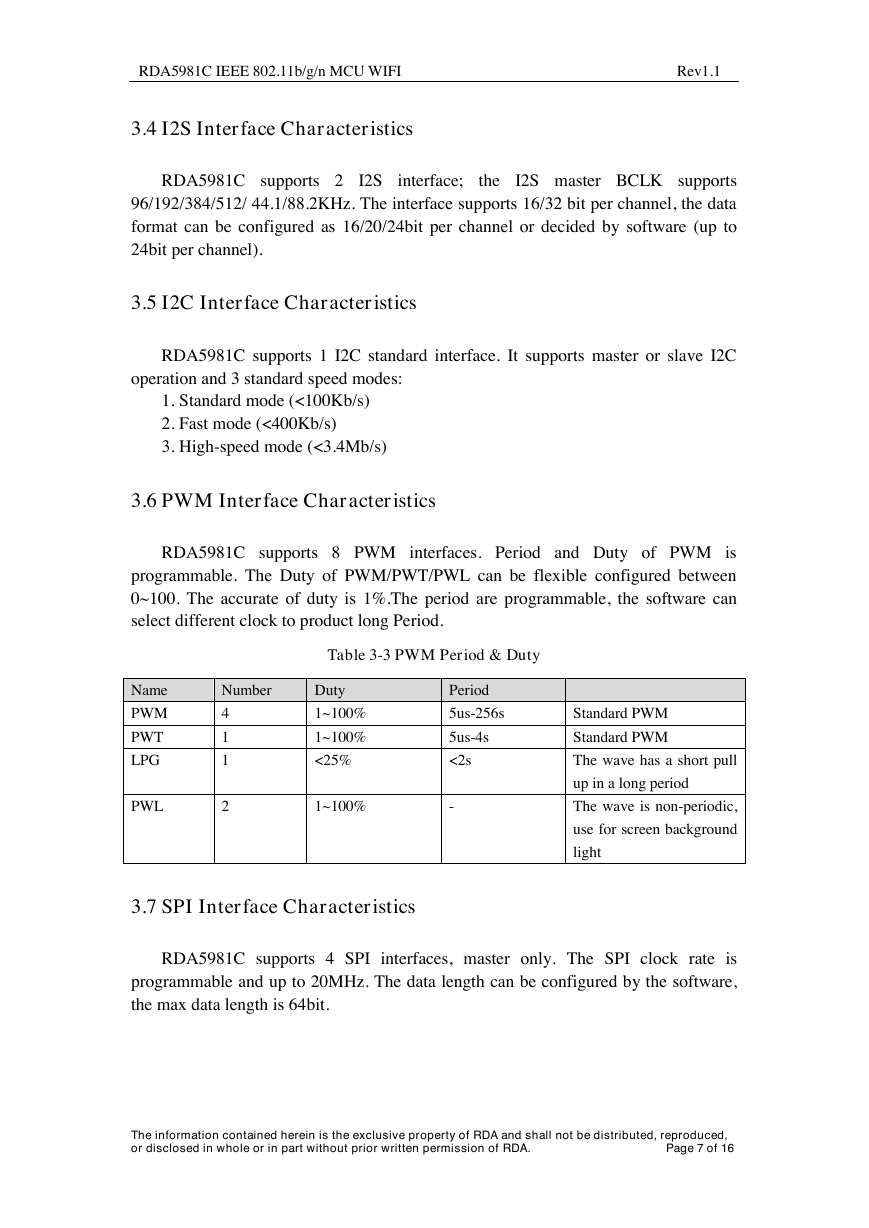

3.6 PWM Interface Characteristics

RDA5981C supports 8 PWM interfaces. Period and Duty of PWM is

programmable. The Duty of PWM/PWT/PWL can be flexible configured between

0~100. The accurate of duty is 1%.The period are programmable, the software can

select different clock to product long Period.

Table 3-3 PWM Period & Duty

Name

Number

Duty

PWM

PWT

LPG

PWL

4

1

1

2

1~100%

1~100%

<25%

Period

5us-256s

5us-4s

<2s

1~100%

-

Standard PWM

Standard PWM

The wave has a short pull

up in a long period

The wave is non-periodic,

use for screen background

light

3.7 SPI Interface Characteristics

RDA5981C supports 4 SPI interfaces, master only. The SPI clock rate is

programmable and up to 20MHz. The data length can be configured by the software,

the max data length is 64bit.

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced,

or disclosed in whole or in part without prior written permission of RDA. Page 7 of 16

�

RDA5981C IEEE 802.11b/g/n MCU WIFI Rev1.1

3.8 SDMMC Interface Characteristics

RDA5981C supports 1 SDMMC interface.

3.9 USB Interface Characteristics

RDA5981C supports USB interface.

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced,

or disclosed in whole or in part without prior written permission of RDA. Page 8 of 16

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc