《一步一步学 ZedBoard & Zynq》系列第二篇,目的是为了学习不使用 ARM PS 情况下,只对 Zynq PL 的编程方法,同时学习

Xilinx PlanAhead 工具的使用方法

更多更新请关注我的博客:@超群天晴 http://www.cnblogs.com/surpassal/

硬件平台:Digilent ZedBoard

开发环境:Windows XP 32 bit

软件: XPS 14.2 +PlanAhead 14.2

新建工程 LAB2

项目设置中,需要将芯片选为 Zynq

�

选择文件类型为 verilog,名称就 ledwater

�

之后会提示引脚信息,默认空就可以,随后可以通过 verilog 代码来实现。

进入 ISE 后,添加源文件,内容如下

1.

/*

2. 《一步一步学 ZedBoard & Zynq》些列第二篇:使用 Zynq 的 PL 做流水灯

3.

2012 年 9 月 11 日 10:31:13

4. 超群天晴

5.

*/

6.

7.

module ledwater(

8.

input BTNU,

9.

input GCLK,

10.

output [7:0] LD

11.

);

12.

wire clk,rst;

13.

reg [7:0]

LD_reg;

14.

reg [31:0]

cnt;

�

15.

16.

assign clk = GCLK;

17.

assign rst = ~BTNU;

18.

assign LD = LD_reg;

19.

20.

always@(posedge clk or negedge rst)

21.

begin

22.

if(rst==1'b0)begin

23.

LD_reg <= 8'b1000_0000;

24.

cnt <= 32'b0;

25.

end

26.

else begin

27.

if (cnt == 32'd25000000)begin

28.

cnt <= 32'b0;

29.

LD_reg <=(LD_reg>>1)|(LD_reg<<7);

30.

end

31.

else begin

32.

cnt <= cnt + 32'b1;

33.

end

34.

end

35.

end

36.

37.

endmodule

复制代码

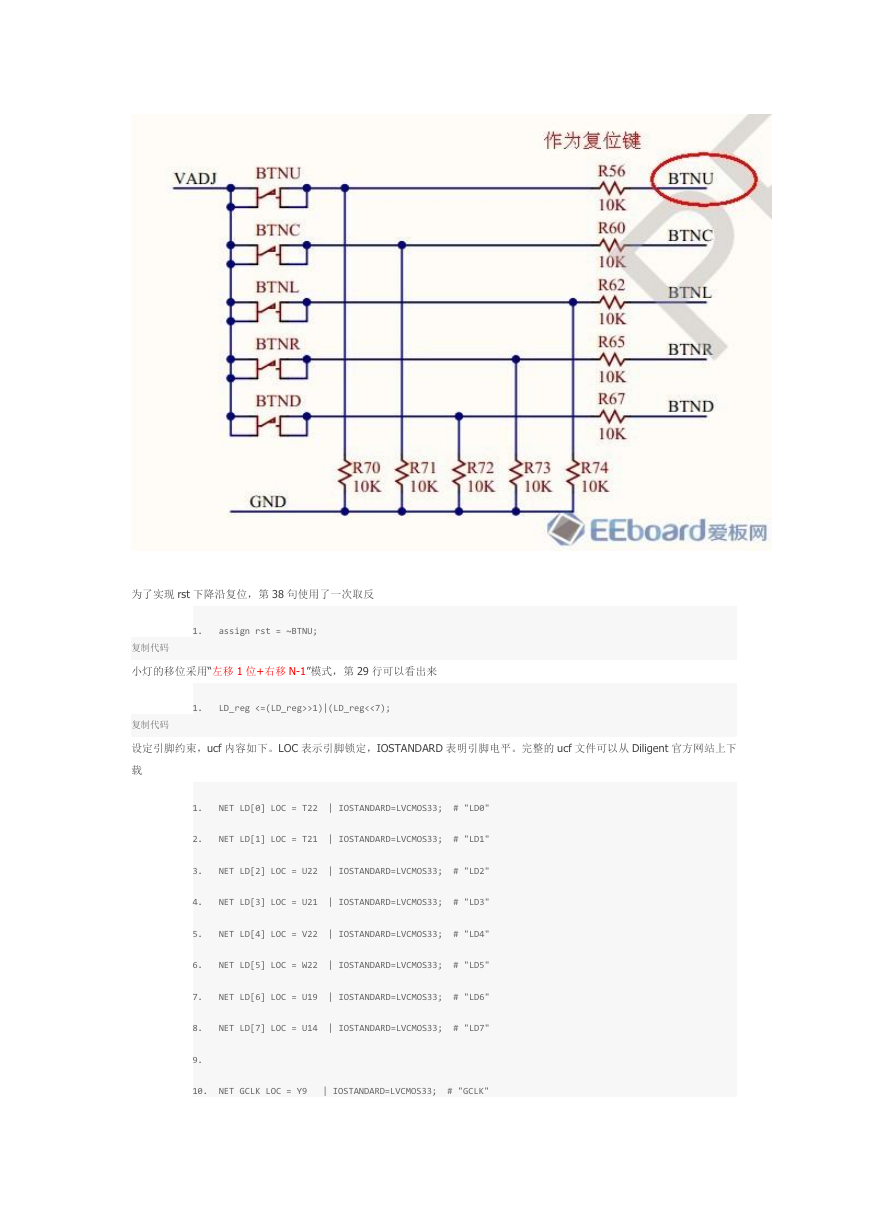

这里设定 BTNU 为复位,GCLK 是时钟

查看 ZedBoard 的原理图,可以知道 BTNU 默认是低电平。

�

为了实现 rst 下降沿复位,第 38 句使用了一次取反

1.

assign rst = ~BTNU;

复制代码

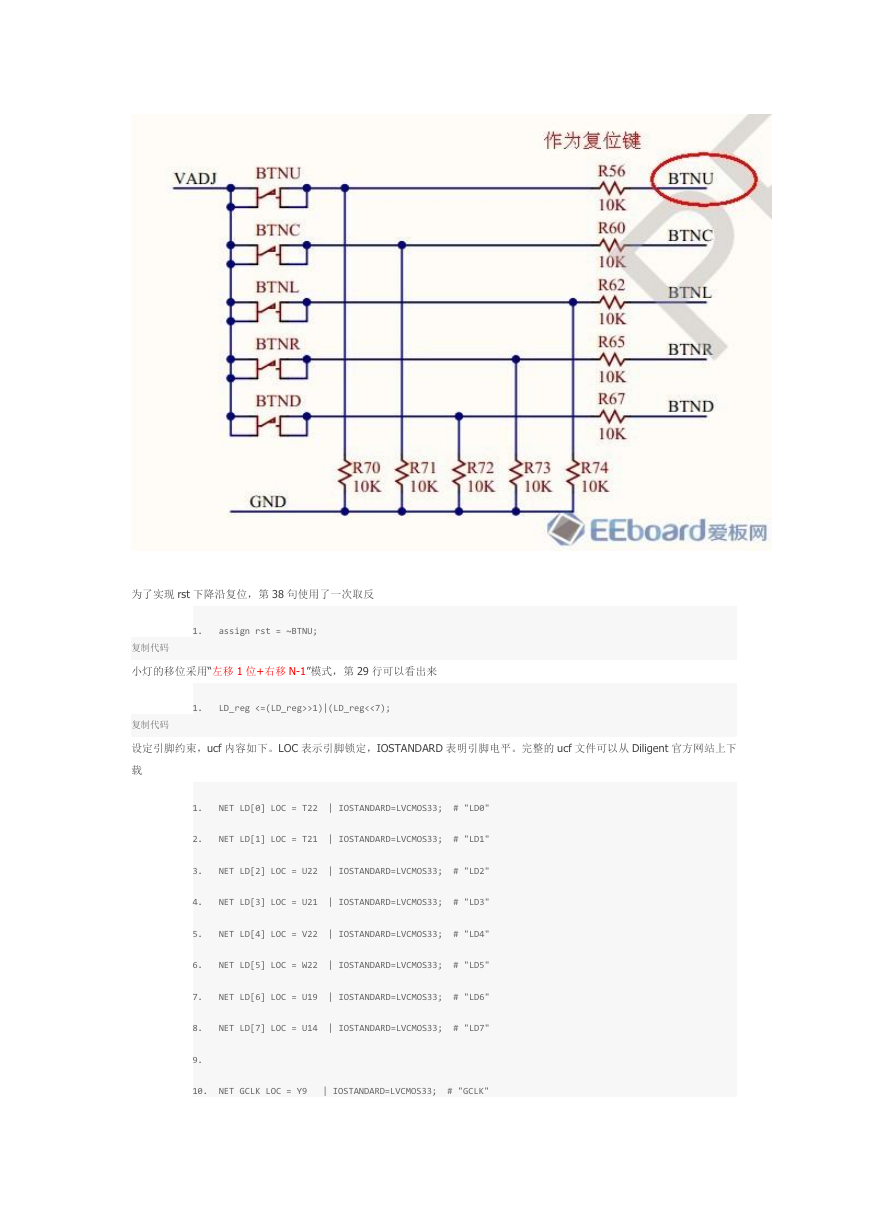

小灯的移位采用“左移 1 位+右移 N-1”模式,第 29 行可以看出来

1.

LD_reg <=(LD_reg>>1)|(LD_reg<<7);

复制代码

设定引脚约束,ucf 内容如下。LOC 表示引脚锁定,IOSTANDARD 表明引脚电平。完整的 ucf 文件可以从 Diligent 官方网站上下

载

1.

NET LD[0] LOC = T22 | IOSTANDARD=LVCMOS33; # "LD0"

2.

NET LD[1] LOC = T21 | IOSTANDARD=LVCMOS33; # "LD1"

3.

NET LD[2] LOC = U22 | IOSTANDARD=LVCMOS33; # "LD2"

4.

NET LD[3] LOC = U21 | IOSTANDARD=LVCMOS33; # "LD3"

5.

NET LD[4] LOC = V22 | IOSTANDARD=LVCMOS33; # "LD4"

6.

NET LD[5] LOC = W22 | IOSTANDARD=LVCMOS33; # "LD5"

7.

NET LD[6] LOC = U19 | IOSTANDARD=LVCMOS33; # "LD6"

8.

NET LD[7] LOC = U14 | IOSTANDARD=LVCMOS33; # "LD7"

9.

10.

NET GCLK LOC = Y9

| IOSTANDARD=LVCMOS33; # "GCLK"

�

11.

NET BTNU LOC = T18 | IOSTANDARD=LVCMOS18; # "BTNU"

复制代码

使用 PlanAhead I/O pin planing(post synthesis)可以看到引脚约束的结果

下载之后能看到板子上 LD0~LD7 流水效果

�

�

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc